Delft University of Technology

#### Integrated Transceiver Circuits for Catheter-Based Ultrasound Probes and Wearable Ultrasound Patches

Tan, M.

DOI 10.4233/uuid:d24a4cbc-8b64-4c1d-992c-990f4b89d40f

**Publication date** 2022

**Document Version** Final published version

**Citation (APA)** Tan, M. (2022). Integrated Transceiver Circuits for Catheter-Based Ultrasound Probes and Wearable Ultrasound Patches. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:d24a4cbc-8b64-4c1d-992c-990f4b89d40f

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy** Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# Integrated Transceiver Circuits for Catheter-Based Ultrasound Probes and Wearable Ultrasound Patches

Mingliang Tan

# Integrated Transceiver Circuits for Catheter-Based Ultrasound Probes and Wearable Ultrasound Patches

Dissertation

for the purpose of obtaining the degree of doctor

at Delft University of Technology

by the authority of the Rector Magnificus, Prof.dr.ir. T.H.J.J. van der Hagen

chair of the Board for Doctorates

to be defended publicly on

Tuesday 13 September 2022 at 12:30 o'clock

by

Mingliang TAN

Master of Science in Electrical Engineering, Delft University of Technology, The Netherlands born in Anging, Anhui Province, P.R. China This dissertation has been approved by the promotors.

Composition of the doctoral committee:

| Rector Magnificus,      | chairman                                 |

|-------------------------|------------------------------------------|

| Dr.ir. M.A.P. Pertijs   | Delft University of Technology, promotor |

| Prof. dr. ir. R. Dekker | Delft University of Technology, promotor |

Independent members:

| Prof. dr. ir. W. A.Serdijn     | Delft University of Technology                 |

|--------------------------------|------------------------------------------------|

| Prof. dr. M. Kraft             | Katholieke Universiteit Leuven, Belgium        |

| Prof. dr. P. Tortoli           | Università degli Studi di Firenze, Italy       |

| Dr. ir. P. Harpe               | Eindhoven University of Technology             |

| Dr. ir. J.G. Bosch             | Erasmus Medical Center                         |

| Prof. dr. ir. L.C.N. de Vreede | Delft University of Technology, reserve member |

This thesis work was supported by ULIMPIA, a labelled PENTA project endorsed by EUREKA under PENTA cluster number E!9911

ISBN: 978-94-6423-954-6 Copyright © 2022 by Mingliang TAN

All rights reserved. No part of this publication may be reproduced or distributed in any form or by any other means, or stored in a database or retrieval system, without the prior written permission of the author.

Printed by Proefschrift Maken | www.proefschriftmaken.nl

### Table of Contents

| CHAF  | TER 1 INTRODCUTION                                   | 1      |

|-------|------------------------------------------------------|--------|

| 1.1   | Motivation                                           | 1      |

| 1.1.  | l Catheter-Based Ultrasound                          |        |

| 1.1.2 | 2 Wearable Ultrasound                                | 4      |

| 1.2   | ASICs for Catheter-based Ultrasound Probes           | 5      |

| 1.3   | ASICs for Wearable Ultrasound Patches                | 7      |

| 1.4   | Thesis Organization                                  | 8      |

| Refer | ences                                                | 10     |

| CHAF  | TER 2 TRANSMIT BEAMFORMER WIT                        | H ±30V |

| BIPO  | LAR HIGH-VOLTAGE PULSERS                             | 17     |

| 2.1   | Introduction                                         | 17     |

| 2.2   | System Architecture                                  |        |

| 2.3   | Bipolar Pulser Design                                |        |

| 2.3.  | 1 Switch Configurations with Bidirectional Isolation | 21     |

| 2.3.2 | 2 Floating-Gate Driver                               | 22     |

| 2.3.3 |                                                      |        |

| 2.3.4 | 4 Complete Bipolar Pulser                            | 24     |

| 2.4   | Circuit Implementation Details                       |        |

| 2.4.  | 1 Supply Domains                                     |        |

| 2.4.2 | 2 Level Shifters                                     | 26     |

| 2.4.3 | 3 TX Beamforming Logic                               |        |

| 2.4.4 | 4 Shared Digital Logic                               | 29     |

| 2.5   | Experimental Results                                 |        |

| 2.5.  | 1 Experimental Prototype                             |        |

| 2.5.2 | 2 Electrical Measurement Results                     | 31     |

| 2.5.3 | 3 Acoustical Measurement Results                     |        |

| 2.6  | Conclusions                                            |        |

|------|--------------------------------------------------------|--------|

| Refe | prences                                                | 40     |

| СНА  | PTER 3 LOW-NOISE TRANSIMPEDANCE                        |        |

|      | LIFIER WITH EMBEDDED TIME-GAIN                         | 1      |

|      | IPENSATION                                             |        |

|      |                                                        |        |

| 3.1  | Introduction                                           |        |

| 3.2  | Comparison of TGC Circuits                             |        |

| 3.3  | Architecture of the TIA with TGC                       | 50     |

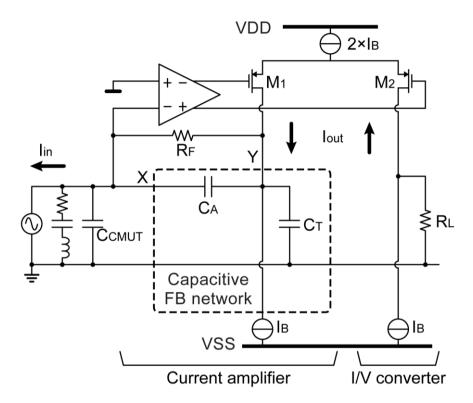

| 3.3  | Current Amplifier based TIA                            | 50     |

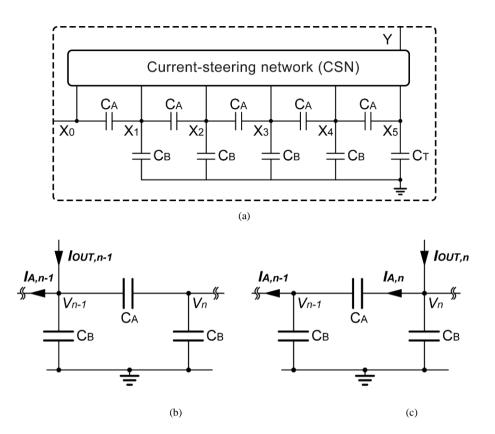

| 3.3  | 2.2 Capacitive Ladder Feedback Network                 | 51     |

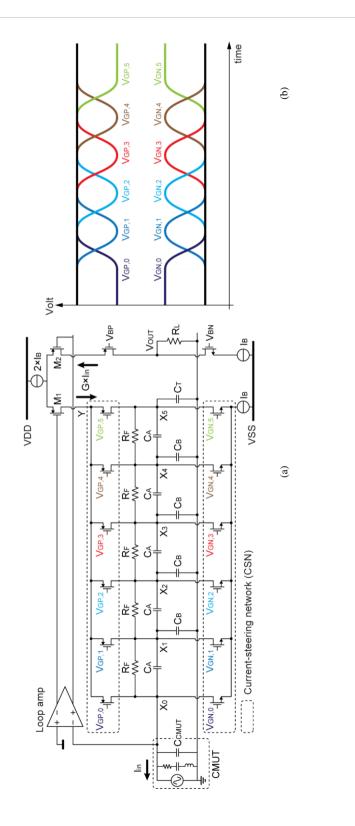

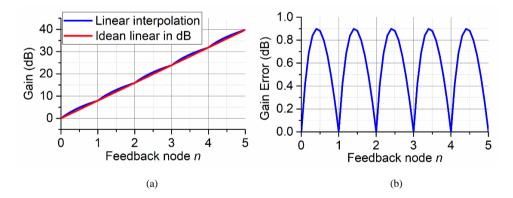

| 3.3  | B.3         Interpolation by means of Current Steering | 54     |

| 3.3  | 8.4 Noise Analysis                                     |        |

| 3.4  | Circuit Implementation                                 | 55     |

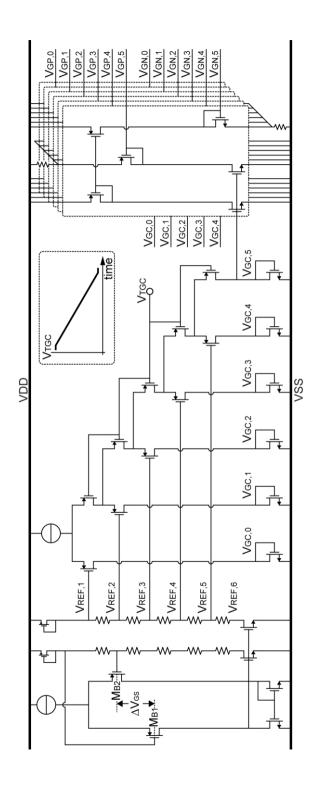

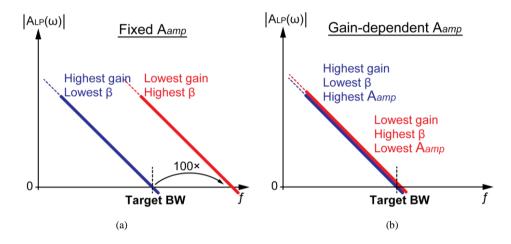

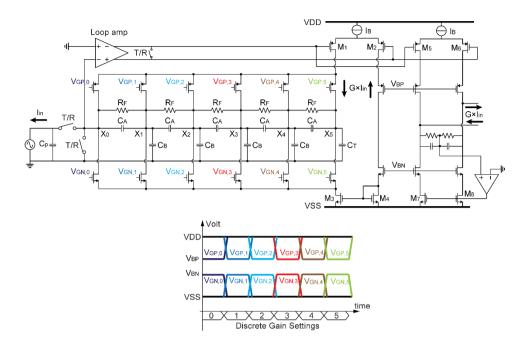

| 3.4  | .1 Gain-Control Circuit                                | 55     |

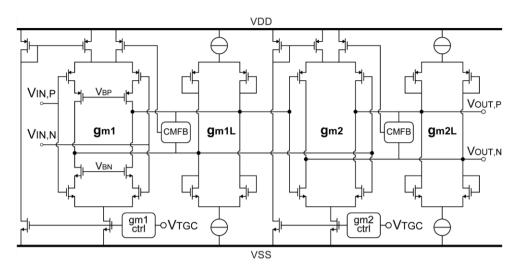

| 3.4  | .2 Loop Amplifier Design                               |        |

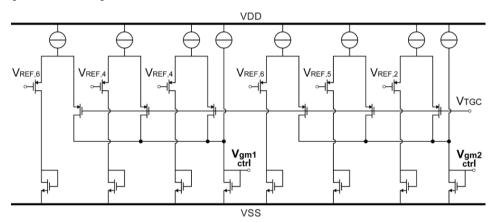

| 3.4  | .3 Transconductance-Control Circuit                    | 59     |

| 3.5  | Experimental Results                                   | 60     |

| 3.5  | 5.1 Experimental Prototype                             | 60     |

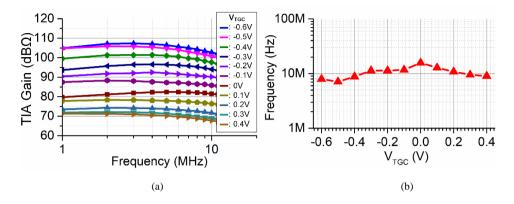

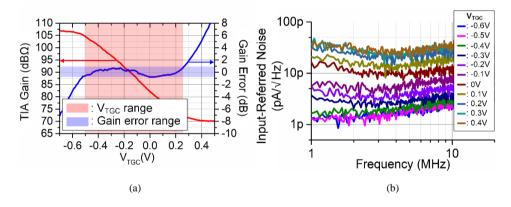

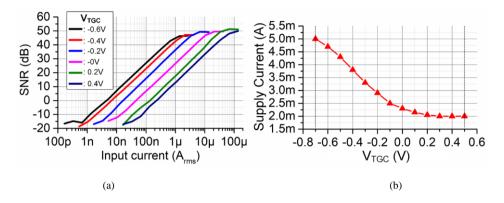

| 3.5  | 5.2 Electrical Characterization Results                | 60     |

| 3.5  | Acoustical Experiments                                 |        |

| 3.6  | Conclusion                                             | 66     |

| Refe | rences                                                 | 67     |

|      |                                                        |        |

|      | PTER 4 FRONT-END ASIC WITH HIGH-V                      | OLIAGE |

|      | NSMIT SWITCHING AND RECEIVE                            | 70     |

| DIGI | TIZAZTIO                                               |        |

| 4.1  | Introduction                                           | 73     |

| 4.2  | System Architecture                                    | 76     |

| 4.2  | 2.1 Transducer Array                                   | 76     |

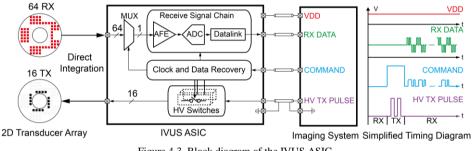

| 4.2.2                                                                                                         | 2 ASIC Architecture                                                                                                                                                                                                                                                                                                                                                                                   | 78     |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

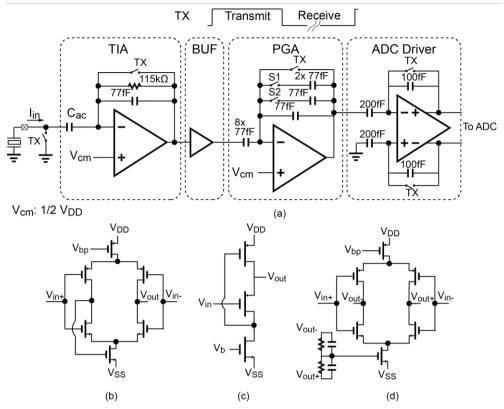

| 4.3                                                                                                           | Circuit Implementation                                                                                                                                                                                                                                                                                                                                                                                | 80     |

| 4.3.                                                                                                          | 1 Analog Front-End                                                                                                                                                                                                                                                                                                                                                                                    |        |

| 4.3.2                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                       |        |

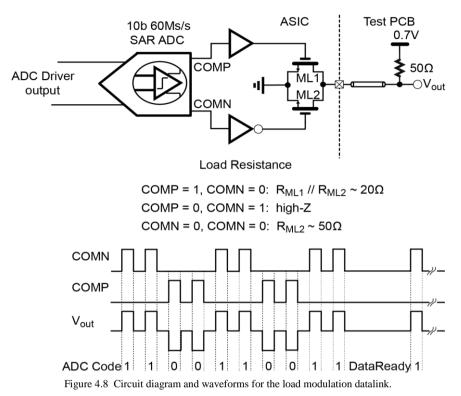

| 4.3.3                                                                                                         | 3 Load-Modulation Datalink                                                                                                                                                                                                                                                                                                                                                                            |        |

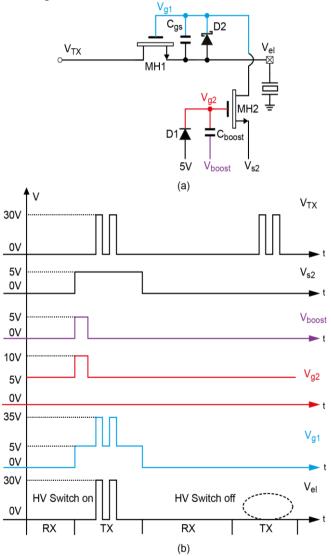

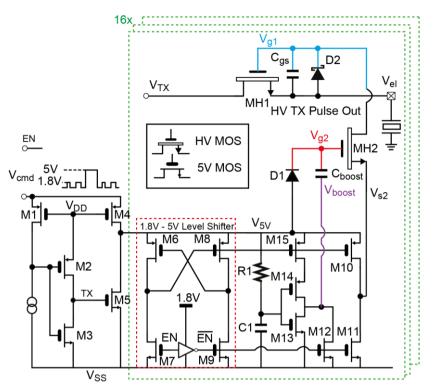

| 4.3.4                                                                                                         | 4 High-Voltage Bootstrapped Switch                                                                                                                                                                                                                                                                                                                                                                    |        |

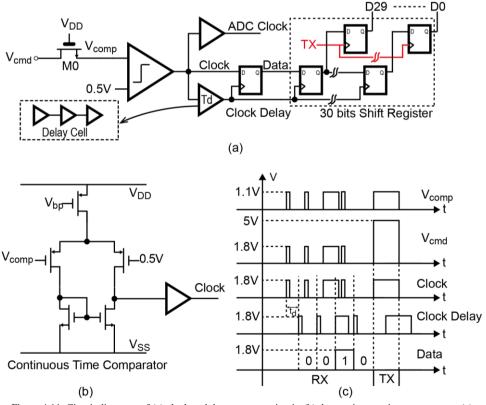

| 4.3.                                                                                                          | 5 Clock and Data Recovery Circuit                                                                                                                                                                                                                                                                                                                                                                     | 89     |

| 4.4                                                                                                           | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 4.4.                                                                                                          | 1 Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                  | 91     |

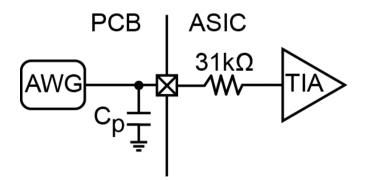

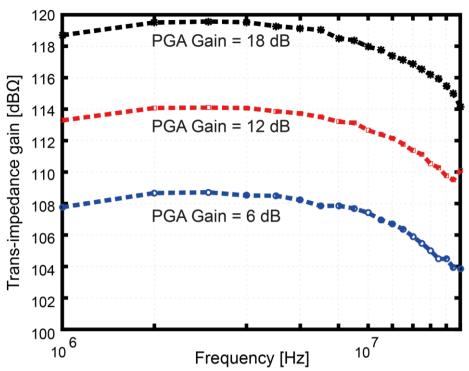

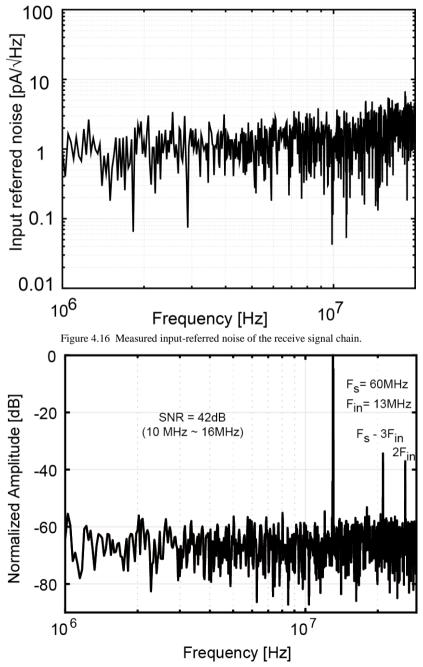

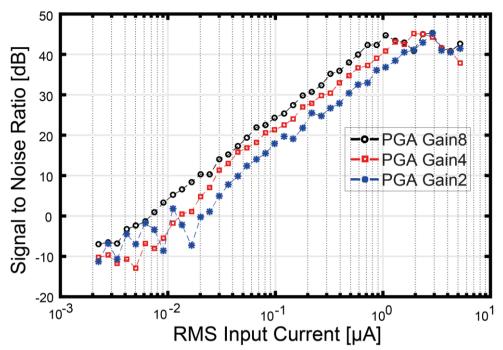

| 4.4.2                                                                                                         | 2 Electrical Measurements                                                                                                                                                                                                                                                                                                                                                                             | 94     |

| 4.4.3                                                                                                         | 3 Acoustic Measurements                                                                                                                                                                                                                                                                                                                                                                               |        |

| 4.5                                                                                                           | Conclusion                                                                                                                                                                                                                                                                                                                                                                                            |        |

| Refer                                                                                                         | rences                                                                                                                                                                                                                                                                                                                                                                                                | 100    |

| Refer                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| CHAF                                                                                                          | PTER 5 LOW-POWER RECONFIGURAB                                                                                                                                                                                                                                                                                                                                                                         | LE     |

| TRAN                                                                                                          | NSCEIVER ASIC FOR WEARABLE ULTR                                                                                                                                                                                                                                                                                                                                                                       | ASOUND |

|                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| PATC                                                                                                          | CHES                                                                                                                                                                                                                                                                                                                                                                                                  |        |

|                                                                                                               | CHES                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| <b>PATC</b><br>5.1                                                                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                          |        |

|                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| 5.1<br>5.2                                                                                                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                          |        |

| 5.1<br>5.2<br>5.2.                                                                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                          |        |

| 5.1<br>5.2<br>5.2.1<br>5.2.1                                                                                  | Introduction<br>System Architecture<br>1 Transducer Characteristics                                                                                                                                                                                                                                                                                                                                   |        |

| 5.1<br>5.2<br>5.2.1<br>5.2.1<br>5.2.1                                                                         | Introduction<br>System Architecture<br>1 Transducer Characteristics<br>2 Reconfigurable HV Pulsers                                                                                                                                                                                                                                                                                                    |        |

| 5.1<br>5.2<br>5.2.1<br>5.2.1<br>5.2.1                                                                         | Introduction<br>System Architecture<br>1 Transducer Characteristics<br>2 Reconfigurable HV Pulsers<br>3 Reconfigurable Low-Noise Amplifiers                                                                                                                                                                                                                                                           |        |

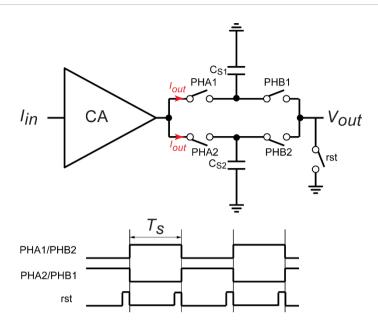

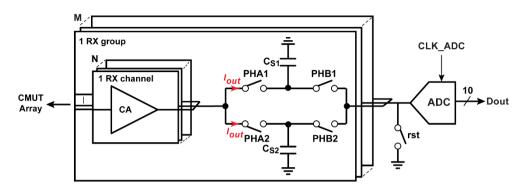

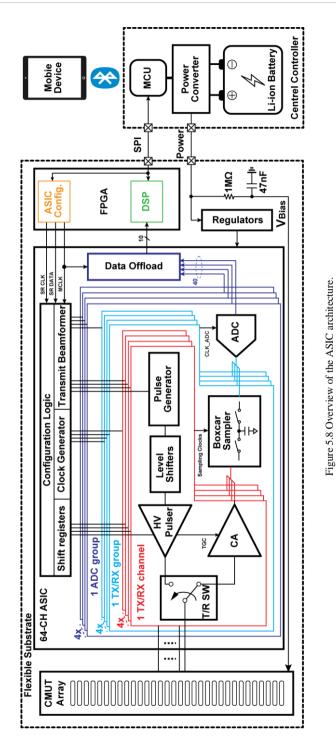

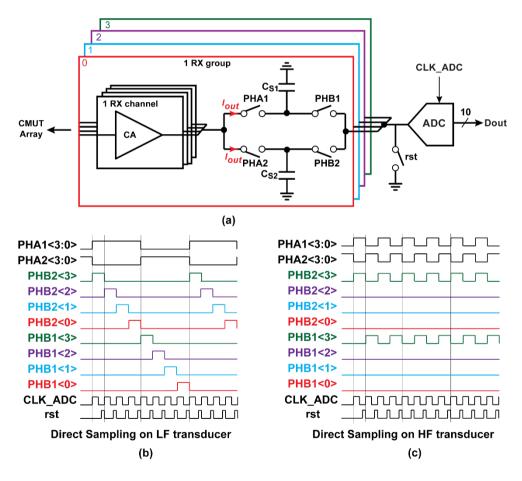

| 5.1<br>5.2<br>5.2.<br>5.2.<br>5.2.<br>5.2.                                                                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                          |        |

| 5.1<br>5.2<br>5.2.<br>5.2.<br>5.2.<br>5.2.<br>5.2.                                                            | Introduction<br>System Architecture<br>1 Transducer Characteristics<br>2 Reconfigurable HV Pulsers<br>3 Reconfigurable Low-Noise Amplifiers<br>4 Reconfigurable Digitization<br>Circuit Implementation<br>1 ASIC Architecture                                                                                                                                                                         |        |

| 5.1<br>5.2<br>5.2.<br>5.2.<br>5.2.<br>5.2.<br>5.2.<br>5.3<br>5.3.                                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                          |        |

| 5.1<br>5.2<br>5.2.<br>5.2.<br>5.2.<br>5.2.<br>5.3<br>5.3.<br>5.3.                                             | Introduction         System Architecture         1 Transducer Characteristics         2 Reconfigurable HV Pulsers         3 Reconfigurable Low-Noise Amplifiers         4 Reconfigurable Digitization         Circuit Implementation         1       ASIC Architecture         2       Low-Noise Current Amplifier         3       Sampling Network                                                   |        |

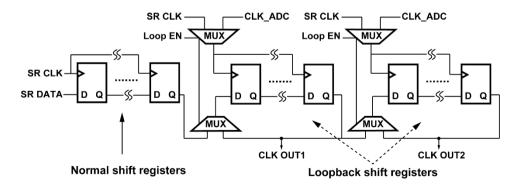

| 5.1<br>5.2<br>5.2.<br>5.2.<br>5.2.<br>5.2.<br>5.2.<br>5.3.<br>5.3.                                            | Introduction         System Architecture         1 Transducer Characteristics         2 Reconfigurable HV Pulsers         3 Reconfigurable Low-Noise Amplifiers         4 Reconfigurable Digitization         Circuit Implementation         1         ASIC Architecture         2         Low-Noise Current Amplifier         3         Sampling Network         4         Control Logic             |        |

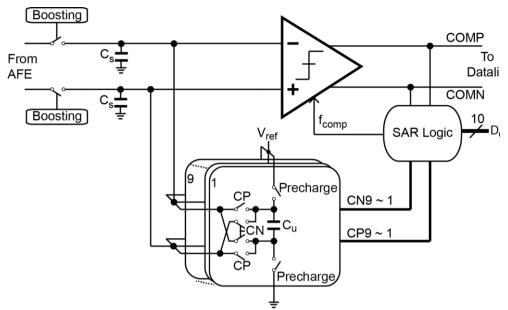

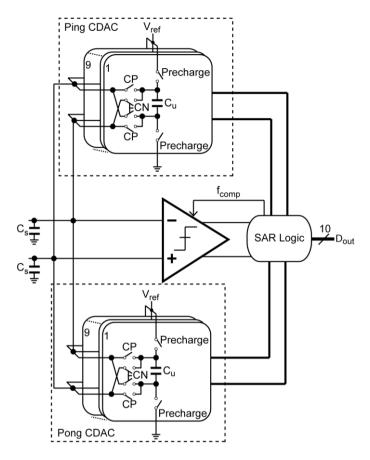

| 5.1<br>5.2<br>5.2.<br>5.2.<br>5.2.<br>5.2.<br>5.3<br>5.3.<br>5.3.<br>5                                        | Introduction         System Architecture         1 Transducer Characteristics         2 Reconfigurable HV Pulsers         3 Reconfigurable Low-Noise Amplifiers         4 Reconfigurable Digitization         Circuit Implementation         1       ASIC Architecture         2       Low-Noise Current Amplifier         3       Sampling Network         4       Control Logic         5       ADC |        |

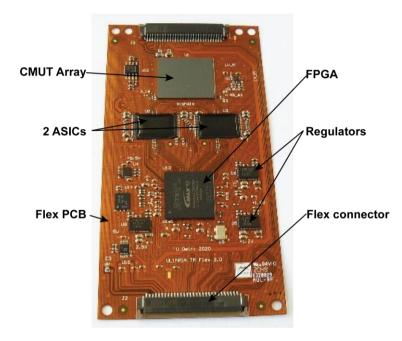

| 5.1<br>5.2<br>5.2.1<br>5.2.1<br>5.2.1<br>5.2.1<br>5.2.1<br>5.2.1<br>5.3.1<br>5.3.1<br>5.3.1<br>5.3.1<br>5.3.1 | Introduction         System Architecture         1 Transducer Characteristics         2 Reconfigurable HV Pulsers         3 Reconfigurable Low-Noise Amplifiers         4 Reconfigurable Digitization         Circuit Implementation         1 ASIC Architecture         2 Low-Noise Current Amplifier         3 Sampling Network         4 Control Logic         5 ADC                               |        |

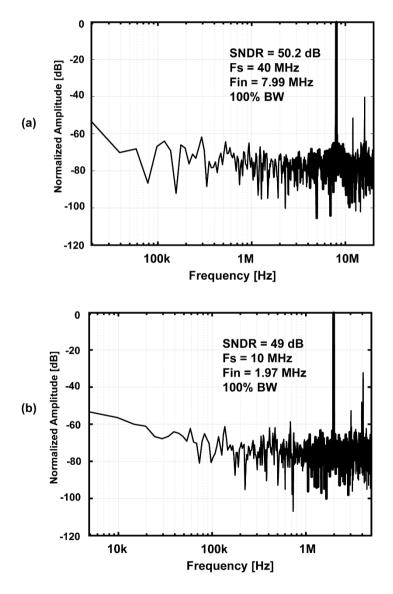

| 5.4  | .2 Electrical Characterization Results |     |

|------|----------------------------------------|-----|

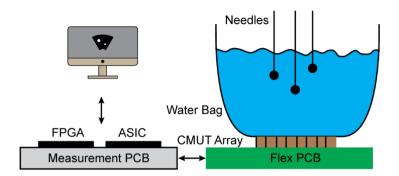

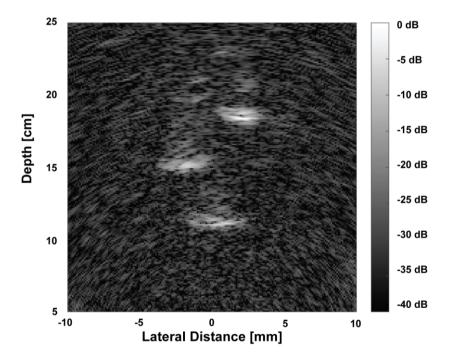

| 5.4  | .3 Acoustical Experiments              |     |

| 5.5  | Conclusion                             |     |

| Refe | rences                                 |     |

| CHA  | PTER 6 CONCLUSIONS                     |     |

| 6.1  | Main Contributions                     |     |

| 6.2  | General Conclusions                    |     |

| 6.3  | Future Work                            |     |

| Refe | rences                                 |     |

| SUM  | MARY                                   | 143 |

| SAM  | ENVATTING                              | 147 |

| LIST | OF ABBREVIATIONS                       | 151 |

| LIST | OF PUBLICATIONS                        | 155 |

| ACK  | NOWLEDGEMENTS                          | 157 |

| ABO  | UT THE AUTHOR                          |     |

### **CHAPTER 1**

## INTRODUCTION

#### 1.1 Motivation

Ultrasound imaging for medical diagnostic was first introduced in 1947 by Austrian neurologist Karl Theo Dussik [1]. After decades of developments, ultrasound imaging is a well-established imaging modality in clinical practice [2]. The diagnosis of cardiovascular diseases (CVDs) also benefits from the developments of medical ultrasound. CVDs are a general designation of a group of disorders related to the heart and blood vessels, such as coronary heart disease and congenital heart disease. According to the World Health Organization (WHO), approximately 17.9 million people died from CVDs in 2016, which is around 1/3 of all global deaths [3]. To reduce the death rate, early diagnosis and treatment are crucial. Surgical treatment and early diagnosis both rely on a good understanding of the pathophysiology of CVDs by visualizing the heart and its vasculature. Compared to imaging modalities like nuclear scintigraphy, magnetic resonance imaging (MRI), computed tomography (CT), ultrasound imaging is safe and cost-effective and can provide real-time images to guide percutaneous interventional procedures with a reduced procedure time [4].

Conventionally, ultrasound imaging is performed using a handheld probe connected to a cartbased imaging system. For instance, a transthoracic echocardiography (TTE) probe is placed on the chest of the patient to visualize the heart [5]. However, due to the limited penetration depth and interference of the ribs and lungs, the image quality provided by TTE is in some cases not sufficient to obtain clear cardiac structures. To enable minimally-invasive procedures which require long, thin, and flexible tubes or catheters threaded into the heart,

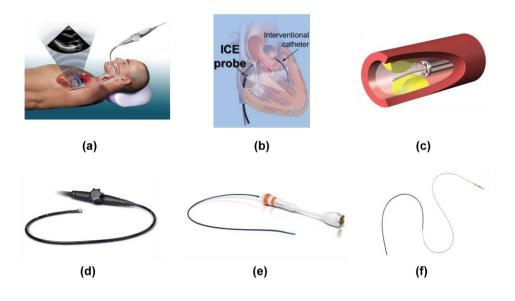

Figure 1.1 Conceptual diagram of (a) transesophageal echocardiography (figure reproduced from piedmontcardiovascular.com); (b) intra-cardiac echocardiography (ICE); (c) intravascular ultrasound (IVUS); (d) TEE probe (Oldelft Ultrasound, the Netherlands); (e) ICE catheter (Siemens ACUSON AcuNav ICE catheter); (f) IVUS catheter (Philips Eagle Eye)

ultrasound images obtained closer to the heart or even from inside the heart are essential for the doctors to have a clearer picture on the heart condition during the procedures. As such, an ultrasound probe that is mounted on the tip of the catheter, *a.k.a.* catheter-based probe, is necessary, which, however, brings technical challenges in terms of electronics, catheter assemble, etc.

In addition to its application in the diagnosis of CVDs, ultrasound imaging has also great potential in applications that need continuous monitoring, such as bladder-volume monitoring [6], overnight monitoring of sleep apnea events [7], treatment of chronic wounds [8]. For such monitoring applications, conventional handheld probes that are connected to a bulky and expensive cart-based imaging system controlled by a well-trained sonographer are not suitable. In recent years, portable probes connecting with mobile devices have been introduced as an alternative [9, 10]. However, due to their limited battery capacity, such devices can only serve for diagnosis during several hours. Moreover, they still require manual operation. To monitor body parameters continuously without aid from caretakers, wearable ultrasound patches (WUPs) are a promising solution. Compared to wearable body patches based on electrocardiography (ECG) or photoplethysmography (PPG) [11], which measure surface parameters on the skin, WUPs allow for monitoring of health parameters inside the

human body. To build a patch that can be worn on the body for days, efforts in miniaturizing conventional handheld probes are needed.

The focus of this thesis is to utilize integrated circuit (IC) technology in combination with advanced ultrasound transducers to address the shared challenge of catheter-based ultrasound probes and WUP devices, which is the need to interface with an array of transducer elements using compact low-power electronics integrated in the device. To do so, various circuit and system design techniques will be proposed.

#### 1.1.1 Catheter-Based Ultrasound

In contrast with a TTE probe which is placed on the patient's chest, in a transesophageal echocardiography (TEE) probe, shown in Figure 1.1a, a long gastroscopic tube is used to guide the ultrasound transducer into the esophagus through the throat of the patient. Since the human heart is physically close to the wall of the esophagus, this approach reduces the attenuation, so that a better cardiac image can be obtained. However, to operate the TEE probe, sedation or general anesthesia is required and the image quality of the far-field part in the anterior heart is limited [12-13].

To have an even closer "look" at the heart, a minimally-invasive imaging modality called intra-cardiac echocardiography (ICE) has been developed [14-16]. As shown in Figure 1.1b, the ultrasound transducer array is mounted at the tip of a long, thin, and flexible catheter that is threaded into the heart through the blood vessels. Compared to TEE, ICE only requires conscious sedation and local anesthesia, leading to a shorter procedure time [17]. Since an ICE probe is located inside the heart and works at a higher frequency than TTE (~7 MHz), the image quality is similar or better than that of TEE [18]. However, the small catheter size (8-10 Fr) brings challenges in ultrasound transducer fabrication and catheter assembly.

To obtain images inside the arteries of the heart, another minimally-invasive imaging modality has been proposed, called intravascular ultrasound (IVUS) [19, 20]. IVUS, shown in Figure 1.1c is also based on a flexible catheter but with a smaller diameter and higher operation frequency, hence offering higher imaging resolution. Conventional side-looking (SL) IVUS catheters contain a single-element transducer at the tip of the catheter that is mechanically rotated to obtain cross-sectional images of the artery [20]. To avoid mechanical rotation, which may lead to imaging artifacts, a circular transducer array placed around the catheter tip has been proposed such that the acoustic beam can be steered electronically [21]. However, SL-IVUS probes are not suitable for imaging of vessels that are filled with atherosclerotic lesions, so-called chronic total occlusions (CTO) [22]. For imaging of CTOs, forward-looking (FL) IVUS probes have been developed to obtain images in front of the probe tip. In [23-25], the use of a single-element transducer that is mechanically rotated around the catheter axis to obtain 2-D images has been proposed. To mitigate the sensitivity

to motion artifacts, 2-D transducer arrays have been applied to obtain 3-D volumetric images without mechanical rotation, leading to 3-D FL-IVUS probes [26-27].

The small diameter of the catheters used for ICE and IVUS brings several challenges. First, connecting a 1-D or 2-D transducer array with an imaging system through the long and thin catheter shaft is challenging and labor-intensive. As in many cases the number transducer elements exceeds the number of cables that can be accommodated, efforts are required in reducing the cable-count using application-specific integrated circuits (ASICs) close to the transducer array at the catheter tip [14, 28-30]. Moreover, these ASICs also serve to mitigate the loading effect of the cables, which, when directly connected to small transducer elements, would lead to a significant reduction in signal-to-noise ratio [31]. Since these ASICs need to operate with the stringent size constraints and temperature limitations of a catheter, low-power and compact integrated circuits are required. In this thesis, various techniques at the system and circuit level will be proposed to address these challenges. Their effectiveness has been demonstrated by several prototypes, which will be discussed in the following chapters.

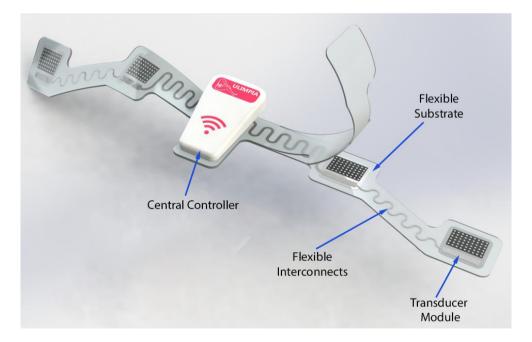

#### 1.1.2 Wearable Ultrasound

Wearable body patches allow for continuous monitoring of body vital parameters and thus have been used by hospitals and caretakers. However, conventional body patches focus on surface body parameters, for instance, IMEC's ECG body patch monitors the heart rate by measuring the electric signals on the skin [11]. Since ultrasound can penetrate the human body harmlessly, a wearable ultrasound patch (WUP) can be used to monitor health-related parameters deep inside the body, opening up various interesting applications: monitoring of the bladder volume [6], measurement of blood pressure [32], therapy of chronic wounds [8] and measurement of the blood flow [33].

Since the WUPs are intended to operate for several days on the surface of the human body, they should be:

- Comfortable: The wearing comfort of a patient is a very subjective item, which can be affected by many factors, for instance, the physical feel of the wearable device and concerns about being embarrassed [34]. WUPs should be small, light, and flexible.

- Conformal: The patch should be made conformal to provide angular coverage over the contact area such that proper acoustic contact can be maintained in the presence of natural movement of the body.

- Energy-efficient: Attached to the surface of the human body, a WUP gets its power from a battery. Due to the limited size and weight of the WUP, the capacity of the

battery would also be very limited. To facilitate continuous monitoring, the electronics in the WUP should be extremely energy efficient.

• Wireless: To enable continuous monitoring, without being restricted the daily movements of the patients, WUPs should be wirelessly controlled and read out.

Efforts towards WUPs have been mainly focused on the design of conformal ultrasound transducer arrays, implemented by either flexible and stretchable materials or conventional rigid transducers mounted on top of a flexible substrate. In [35], a flexible transducer array based on polyvinylidene fluoride (PVDF) is implemented for non-destructive evaluation (NDE) applications. However, PVDF transducers tend to have a relatively low transmit efficiency, limiting their usage in pulse-echo-based imaging. Further developments have been made in flexible piezoelectric micromachined ultrasound transducers (PMUTs) [36] and flexible capacitive micromachined ultrasound transducers (CMUTs) [37]. Both designs are integrated on top of a flexible polydimethylsiloxane (PDMS) substrate for insulation and acoustic impedance matching. In [32], a conformal transducer array based on rigid 1-3 composite piezoelectric materials with soft structural components is proposed for continuous monitoring of blood pressure. Another approach proposed in [38] employs a diced rigid PZT array on top of a Flex PCB to make the device conformal.

Although the abovementioned designs have shown promising results towards future WUP devices, the front-end electronics are still based on bulky and power-hungry off-the-shelf ICs. For instance, in [39], a Verasonics imaging system is applied to connect with a flexible transducer array via cables. The challenges in designing flexible front-end energy- and area-efficient electronics have not been addressed. In this thesis, we present a WUP prototype which integrates transceiver ASICs and a transducer array on a flexible substrate. The proposed low-power ASIC architecture allows for a battery-powered prototype whose effectiveness has been demonstrated electrically and acoustically.

#### 1.2 ASICs for Catheter-based Ultrasound Probes

In a conventional ICE or IVUS probe, the transducer is mounted at the tip of the catheter and connected to an imaging system through a bundle of micro-coaxial cables with a length of ~2 meters [26, 40, 41]. The high-voltage (HV) excitation signals (tens of Volts) provided by the imaging system and the low-voltage (LV) echo signals (several micro-Volts) received by the transducer are both transferred through these long coaxial cables, leading to signal attenuation and distortion. Application-specific integrated circuits (ASICs) integrated closely to the transducer array have been used to reduce these loading effects [28, 42].

Apart from reducing the loading effect of the micro-coaxial cables, ASICs have also been used to reduce the number of cables. For 3-D ICE or 3-D IVUS, a 2-D transducer array with tens or hundreds of elements is needed [26, 40, 41]. Connecting each of them with a micro-

coaxial cable is challenging, labor-intensive, and would lead to a cable bundle that is hard to accommodate in a catheter shaft. The cable-count reduction is done in the ASIC by means of multiplexing [43-46], sub-array beamforming [29, 47], column-row-parallel addressing [48-49], or row-by-row connections [50-51].

There are several challenges in the design and integration of ASICs at the tip of an ultrasound catheter. First, the connections between the ASIC and a 2-D transducer array with a large number of elements are still complex. To address this interconnection challenge, different ASIC-transducer integration schemes have been proposed in recent years. The first approach is to place the ASIC and transducer on the same printed circuit board (PCB) on which transducer elements are connected to the ASIC via PCB traces [52-53]. However, the parasitic capacitance introduced by these connections will introduce SNR degradation and crosstalk. To mitigate these problems, an interposer layer has been employed for the interconnection in [14, 48, 54]. The transducer elements are vertically routed to the ASIC inputs with short interconnects, which reduces the parasitic capacitance significantly. However, this approach requires fine-pitch PCB or interposer technology to create small enough vias for vertical routing. Another approach is to directly integrate the transducer array on top of a pitch-matched ASIC through flip-chip bonding [55-56], a custom metallic interconnect layer [57], or monolithic integration [9, 42].

A second challenge is that the small dimensions of IVUS and ICE catheters impose constraints on the available area for the ASIC. For instance, a typical diameter of an IVUS catheter is less than 2 mm [19, 21], implying that the ASIC dimensions are limited to even less than that. Squeezing the front-end electronics in such a small area is very challenging.

Third, to transfer the echo signals to the imaging system in a robust manner through microcoaxial cables with large parasitic capacitance, analog cable drivers can be used to match the cable's characteristic impedance for sufficient bandwidth and low signal distortion. However, analog signals are usually sensitive to crosstalk and environmental interference. To avoid that, on-chip ADCs have been implemented to locally digitize the received signals and then transfer a robust digital bit stream to the system side through the micro-coaxial cables [58-59]. However, it is challenging to design the ADC and the datalink that transfers the bit stream within the stringent power and area budget of a catheter-based probe.

The abovementioned challenges in implementing catheter-based probes call for innovations in:

- Compact ASIC-transducer integration schemes to minimize parasitic.

- Compact, low-power HV pulsers and LNAs with TGC functionality to meet the stringent area- and power-consumption budget.

- Power and area-efficient in-probe ADCs and datalink designs to enable robust bit stream transmission through micro-coaxial cables.

In this thesis, two ASIC prototypes will be presented that address these objectives and have been implemented and integrated with transducer arrays for ICE (chapter 2 and 3) probes and FL-IVUS (chapter 4).

#### **1.3** ASICs for Wearable Ultrasound Patches

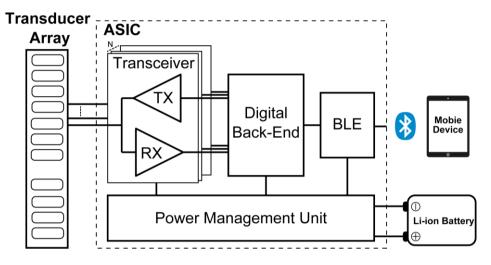

Figure 1.2 Block diagram of an ASIC for a wearable ultrasound body patch

To date, most research on WUPs has focused on the design of flexible or stretchable transducer arrays, which have been characterized using an external imaging system rather than employing electronics integrated in the patch [32, 36, 39, 60-61]. Other WUPs employ discrete commercial ICs integrated with the transducer array on top of a flexible substrate [6, 33, 38, 62-64]. However, due to the limited size and battery capacity of a WUP, it is not realistic to apply conventional off-the-shelf electronics with significant area- and power-consumption overhead. As such, an ASIC optimized in area and power is desirable. Ideally, the ASIC should be designed as a system-on-chip (SoC) in which various building blocks are included. Figure 1.2 shows a block diagram of such an ASIC. It includes an ultrasound transceiver interfacing with the transducer array, a digital back-end processing the echo signal, a power management unit (PMU) providing the ASIC power, and a Bluetooth low-energy (BLE) module communicating with mobile devices. The ASIC, which is directly powered by a battery, is integrated with the transducer array on top of a flexible substrate, e.g., a flexible PCB.

The design of ASICs for WUPs is still a largely unexplored research area. Compared to the ASICs for catheter-based probes, the ASICs for WUPs share similar challenges in terms of ASIC-transducer integration, i.e. limitations in dimensions and power consumption, and the

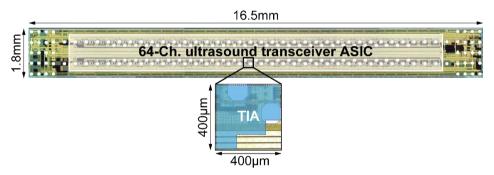

need for on-chip digitization, calling for innovations in system and circuit implementations. This is addressed in chapter 5 of this thesis, which describes an ASIC with 64 reconfigurable transceiver channels, designed as part of a technology platform for ultrasound patches. The ASIC is able to interface with different types of transducer array, such as a low-frequency (2.5 MHz) CMUT array for a bladder monitoring patch and a higher frequency (8 MHz) CMUT array for a blood-pressure sensing patch.

#### **1.4** Thesis Organization

The organization of this thesis is as follows.

Chapter 2 presents a 64-channel transmit beamformer with programmable bipolar pulsers for catheter-based ultrasound probes. The transmit beamformer is programmed and configured through a single clock and data line to steer and focus an ultrasound beam at an angle and depth that is defined in the imaging system. The compact HV pulser design includes an RZ switch that has been constructed such that it can also serve as T/R switch. A new floating-gate driver that uses only a single HV transistor provides level-shifting functionality to turn on and off the MOS transistors in the switch. Thus, the number of HV transistors and passive components required is reduced. Electrical and acoustical experimental results obtained in combination with a 64 element CMUT array successfully demonstrate the functionality of the HV pulser and TX beamformer.

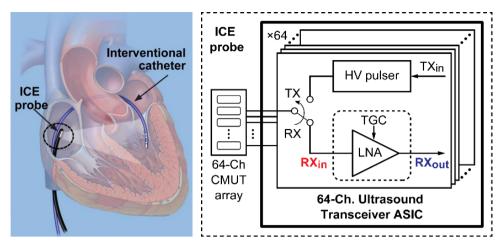

Chapter 3 extends the transmit beamformer discussed in the previous chapter with receive functionality to realize a transceiver ASIC designed for ICE. This includes LNAs to amplify the echo signals and TGC to reduce their dynamic range. The chapter gives an overview of existing TGC circuits with a discussion of their advantages and limitations. Then system architecture and circuit techniques are presented to implement an LNA with built-in TGC functionality, as a more compact and power-efficient alternative to conventional solutions with a separate LNA and TGC amplifier. The operation principle of the proposed TGC scheme is described with an analytical analysis of the capacitive feedback network. Electrical measurements demonstrate continuous gain control to within  $\pm 1$  dB. Imaging results obtained using a prototype employing a 64-element CMUT array demonstrate the effectiveness of the proposed techniques, showing that the proposed topology is a promising solution for ultrasound ASICs.

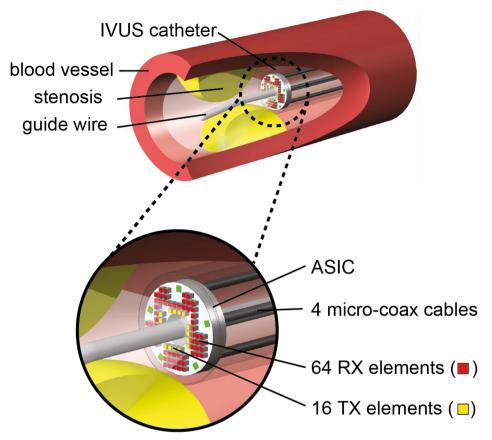

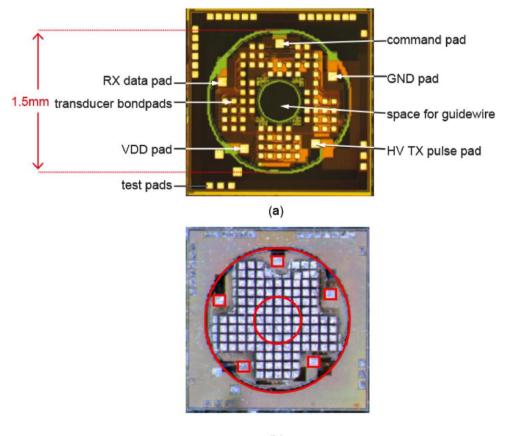

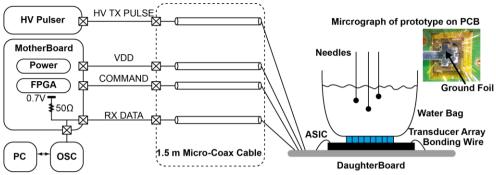

In chapter 4, a front-end ASIC targeted for a forward-looking IVUS imaging probe is presented. The ASIC interfaces with 16 TX elements and 64 RX elements using only four 1.5-m micro-coaxial cables. A PZT-on-ASIC integration scheme has been applied in this prototype with the ASIC being fabricated in a donut shape, allowing the catheter's guidewire to pass through a hole in the middle of the chip. To minimize the number of cables, a multi-functional mixed-voltage command scheme is applied that merges power supply, clock and data on a single cable. Moreover, load-modulation-based data transmission is proposed as an

efficient way to return digitized echo signals to an imaging system, and HV multiplexing to perform synthetic-aperture imaging. The effectiveness of these techniques has been successfully demonstrated in a 3D ultrasound imaging experiment.

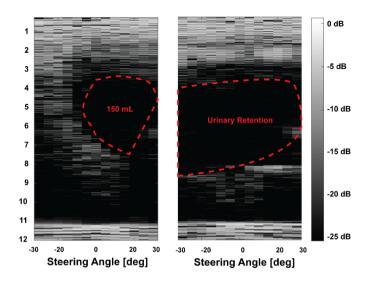

Chapter 5 presents a reconfigurable front-end ASIC for wearable ultrasound patches. The ASIC includes 64 transceivers channels that can be reconfigured to interface with different transducer elements with different center frequencies (2 MHz to 8 MHz) and capacitance (20 pF to 120 pF) by dynamically parallelizing transceiver channels. A reconfigurable sampling network is employed such that one ADC can digitize multiple RX channels for a low-frequency transducer and a single RX channel for a high-frequency transducer. Electrical measurements demonstrate the functionality of the ASIC. A wearable prototype of a bladdermonitoring patch, with ASIC, transducer array, and peripheral building blocks integrated on top of a flexible PCB, has been successfully evaluated acoustically using a bladder phantom.

Chapter 6 concludes the thesis by highlighting the main contributions and the main findings. Suggestions for future improvement and research are also presented.

#### References

- [1] I. Edler, and K. Lindstrom, "The history of echocardiography," *Ultrasound in Medicine & Biology*, vol. 30, no. 12, pp. 1565-1644, Dec. 2004.

- P. N. Wells, "Ultrasound imaging," *Physics in Medicine & Biology*, vol. 51, no. 13, pp. R83, 2006.

- [3] World Health Organization. (May 2017). Cardiovascular Diseases (CVDs). [Online]. Available: https://www.who.int/health-topics/cardiovascular-diseases#tab=tab\_1

- [4] D. H. Sheafor, E. K. Paulson, C. M. Simmons, D. M. DeLong, and R. C. Nelson, "Abdominal percutaneous interventional procedures: Comparison of CT and US guidance," *Radiology*, vol. 207, no. 3, pp. 705-710, Jun. 1998.

- [5] G. S. Hillis and P. Bloomfield, "Basic transthoracic echocardiography," *British Medical Journal*, vol. 330, no. 7505, pp. 1432–1436, Jun. 2005.

- [6] P. G. van Leuteren, B. A. de Vries, G. C. J. de Joode-Smink, B. ten Haken, T. P. V. M. de Jong, and P. Dik, "URIKA, continuous ultrasound monitoring for the detection of a full bladder in children with dysfunctional voiding: a feasibility study," *Biomedical Physics & Engineering Express*, vol. 3, no. 1, Feb. 2017.

- [7] C. K. Weng, J. W. Chen, P. Y. Lee, and C. C. Huang, "Implementation of a Wearable Ultrasound Device for the Overnight Monitoring of Tongue Base Deformation during Obstructive Sleep Apnea Events," *Ultrasound in Medicine & Biology*, vol. 43, no. 8, pp. 1639-1650, Aug. 2017.

- [8] W. H. Lyu, Y. J. Ma, S. Y. Chen, H. B. Li, P. Wang, Y. Chen, and X. Feng, "Flexible Ultrasonic Patch for Accelerating Chronic Wound Healing," *Advanced Healthcare Materials*, vol. 10, no. 19, Oct. 2021.

- [9] N. Sanchez, K. L. Chen, C. Chen, D. McMahill, S. Hwang, J. Lutsky, J. Yang, L. W. Bao, L. K. Chiu, G. Peyton, H. Soleimani, B. Ryan, J. R. Petrus, Y. J. Kook, T. S. Ralston, K. G. Fife, and J. M. Rothberg, "An 8960-Element Ultrasound-on-Chip for Point-of-Care Ultrasound," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, vol. 64, pp. 480-482, 2021.

- [10] Koninklijke Philips N.V, the Netherlands, Philips Lumify Handheld Probe [Online]. Available: https://www.philips.nl/healthcare/product/HC795005/lumify.

- [11] IMEC, Disposable health patch [Online]. Available: https://www.imecint.com/en/circuitry-sensor-hubs/disposable-health-patch

- [12] E. A. Fisher, J. A. Stahl, J. H. Budd, and M. E. Goldman, "Transesophageal echocardiography: Procedures and clinical application," *J. Am. Coll. Cardiol.*, vol. 18, no. 5, pp. 1333–1348, Nov. 1991.

- [13] A. P. W. Lee, Y. Y. Lam, G. W. K. Yip, R. M. Lang, Q. Zhang, and C. M. Yu, "Role of real time three-dimensional transesophageal echocardiography in guidance of interventional procedures in cardiology," *Heart*, vol. 96, no. 18, pp. 1485-1493, Sep. 2010.

- [14] D. Wildes et al., "4-D ICE: A 2-D Array Transducer With Integrated ASIC in a 10-Fr Catheter for Real-Time 3-D Intracardiac Echocardiography," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 63, no. 12, pp. 2159–2173, Dec. 2016.

- [15] Z. M. Hijazi, K. Shivkumar, and D. J. Sahn, "Intracardiac echocardiography during interventional and electrophysiological cardiac catheterization," *Circulation*, vol. 119, no. 4, pp. 587–596, Feb. 2009.

- [16] T. Bartel et al., "Intracardiac Echocardiography Is Superior to Conventional Monitoring for Guiding Device Closure of Interatrial Communications," *Circulation*, vol. 107, no. 6, pp. 795–797, Feb. 2003.

- [17] T. Bartel, S. Müller, A. Biviano, and R. T. Hahn, "Why is intracardiac echocardiography helpful? Benefits, costs, and how to learn," *European Heart Journal*, vol. 35, no. 2, pp. 69–76, Jan. 2014.

- [18] E. Anter, J. Silverstein, C. M. Tschabrunn, A. Shvilkin, C. I. Haffajee, P. J. Zimetbaum, A. E. Buxton, M. E. Josephson, E. Gelfand, and W. J. Manning, "Comparison of intracardiac echocardiography and transesophageal echocardiography for imaging of the right and Left atrial appendages," *Heart Rhythm*, vol. 11, no. 11, pp. 1890-1897, Nov. 2014.

- [19] H. M. Garcia-Garcia, M. A. Costa, and P. W. Serruys, "Imaging of coronary atherosclerosis: intravascular ultrasound," *European Heart Journal*, vol. 31, no. 20, pp. 2456-2469c, Oct. 2010.

- [20] R. A. Nishimura, W. D. Edwards, C. A. Warnes, G. S. Reeder, D. R. Holmes, A. J. Tajik, and P. G. Yock, "Intravascular ultrasound imaging: in vitro validation and pathologic correlation," *Journal of the American College of Cardiology*, vol. 16, no. 1, pp. 145-154, 1990.

- [21] M. ODonnell, M. J. Eberle, D. N. Stephens, J. L. Litzza, K. SanVicente, and B. M. Shapo, "Synthetic phased arrays for intraluminal imaging of coronary arteries," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 44, no. 3, pp. 714-721, May. 1997.

- [22] G. W. Stone, D. E. Kandzari, R. Mehran, A. Colombo, R. S. Schwartz, S. Bailey, I. Moussa, P. S. Teirstein, G. Dangas, D. S. Baim, M. Selmon, B. H. Strauss, H. Tamai, T. Suzuki, K. Mitsudo, O. Katoh, D. A. Cox, A. Hoye, G. S. Mintz, E. Grube, L. A. Cannon, N. J. Reifart, M. Reisman, A. Abizaid, J. W. Moses, M. B. Leon, and P. W. Serruys, "Percutaneous recanalization of chronically occluded coronary arteries A consensus document Part I," *Circulation*, vol. 112, no. 15, pp. 2364-2372, Oct 11. 2005.

- [23] J. L. Evans, K. H. Ng, M. J. Vonesh, B. L. Kramer, S. N. Meyers, T. A. Mills, B. J. Kane, W. N. Aldrich, Y. T. Jang, P. G. Yock, Arterial imaging with a new forward-viewing intravascular ultrasound catheter, I. Initial studies, *Circulation*, vol. 89, pp. 712-7, Feb. 1994.

- [24] K. H. Ng, J. L. Evans, M. J. Vonesh, S. N. Meyers, T. A. Mills, B. J. Kane, W. N. Aldrich, Y. T. Jang, P. G. Yock, M. D. Rold, Arterial imaging with a new forward-viewing intravascular ultrasound catheter, II. Three-dimensional reconstruction and display of data, *Circulation*, vol. 89, pp. 718-23, Feb. 1994.

- [25] D. T. Raphael, X. Li, J. Park, R. M. Chen, H. Chabok, A. Barukh, Q. F. Zhou, M. Elgazery, and K. K. Shung, "20 MHz Forward-imaging single-element beam steering with an internal rotating variable-angle reflecting surface: Wire phantom and ex vivo pilot study," *Ultrasonics*, vol. 53, no. 2, pp. 561-569, Feb. 2013.

- [26] E. D. Light, and S. W. Smith, "Two dimensional arrays for real time 3D intravascular ultrasound," *Ultrasonic Imaging*, vol. 26, no. 2, pp. 115-128, Apr. 2004.

- [27] E. D. Light, J. F. Angle, and S. W. Smith, "Real-time 3-D ultrasound guidance of interventional devices," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 55, no. 9, pp. 2066-2078, Sep. 2008.

- [28] G. Gurun, C. Tekes, J. Zahorian, T. Xu, S. Satir, M. Karaman, J. Hasler, and F. L. Degertekin, "Single-Chip CMUT-on-CMOS Front-End System for Real-Time Volumetric IVUS and ICE Imaging," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 61, no. 2, pp. 239-250, Feb. 2014.

- [29] C. Chen et al., "A Front-End ASIC With Receive Sub-array Beamforming Integrated With a 32 × 32 PZT Matrix Transducer for 3-D Transesophageal Echocardiography," *IEEE J. Solid-State Circuits*, vol. 52, no. 4, pp. 994–1006, Apr. 2017.

- [30] W. C. Black, and D. N. Stephens, "CMOS Chip for Invasive Ultrasound Imaging," *IEEE J. Solid-State Circuits*, vol. 29, no. 11, pp. 1381-1387, Nov. 1994.

- [31] T. Mateo, N. Senegond, C. Meynier, D. Gross, P. Vince, M. L. Tan, E. Kang, and M. Pertijs, "A 1-D CMUT transducer with front-end ASIC in a 9 French catheter for Intracardiac Echocardiography: Acoustic and Imaging evaluation," in *Proc. IEEE Ultrasonics Symposium (IUS)*, pp. 1-8, 2020.

- [32] C. H. Wang, X. S. Li, H. J. Hu, L. Zhang, Z. L. Huang, M. Y. Lin, Z. R. Zhang, Z. N. Yin, B. Huang, H. Gong, S. Bhaskaran, Y. Gu, M. Makihata, Y. X. Guo, Y. S. Lei, Y. M. Chen, C. F. Wang, Y. Li, T. J. Zhang, Z. Y. Chen, A. P. Pisano, L. F. Zhang, Q. F. Zhou, and S. Xu, "Monitoring of the central blood pressure waveform via a conformal ultrasonic device," *Nature Biomedical Engineering*, vol. 2, no. 9, pp. 687-695, Sep. 2018.

- [33] I. Song, J. Yoon, J. Kang, M. Kim, W. S. Jang, N. Y. Shin, and Y. Yoo, "Design and Implementation of a New Wireless Carotid Neckband Doppler System with Wearable Ultrasound Sensors: Preliminary Results," *Applied Sciences-Basel*, vol. 9, no. 11, Jun. 2019.

- [34] J. F. Knight, and C. Baber, "A tool to assess the comfort of wearable computers," *Human Factors*, vol. 47, no. 1, pp. 77-91, Spr. 2005.

- [35] D. J. Powell, and G. Hayward, "Flexible Ultrasonic Transducer Arrays for Nondestructive Evaluation Applications - Part II: Performance Assessment of Different Array Configurations," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 43, no. 3, pp. 393-402, May. 1996.

- [36] J. H. Lee, I. J. Cho, K. Ko, E. S. Yoon, H. H. Park, and T. S. Kim, "Flexible piezoelectric micromachined ultrasonic transducer (pMUT) for application in brain stimulation," *Microsystem Technologies-Micro-and Nanosystems-Information Storage and Processing Systems*, vol. 23, no. 7, pp. 2321-2328, Jul. 2017.

- [37] X. F. Zhuang, D. S. Lin, O. Oralkan, and B. T. Khuri-Yakub, "Fabrication of flexible transducer arrays with through-wafer electrical interconnects based on trench refilling with PDMS," *Journal of Microelectromechanical Systems*, vol. 17, no. 2, pp. 446-452, Apr. 2008.

- [38] V. Pashaei, P. Dehghanzadeh, G. Enwia, M. Bayat, S. J. A. Majerus, and S. Mandal, "Flexible Body-Conformal Ultrasound Patches for Image-Guided Neuromodulation," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 14, no. 2, pp. 305-318, Apr. 2020.

- [39] C. H. Wang, B. Y. Qi, M. Y. Lin, Z. R. Zhang, M. Makihata, B. Y. Liu, S. Zhou, Y. H. Huang, H. J. Hu, Y. Gu, Y. M. Chen, Y. S. Lei, T. Lee, S. Chien, K. I. Jang, E. B. Kistler, and S. Xu, "Continuous monitoring of deep-tissue haemodynamics with stretchable ultrasonic phased arrays," *Nature Biomedical Engineering*, vol. 5, no. 7, pp. 749-758, Jul. 2021.

- [40] E. D. Light, S. F. Idriss, P. D. Wolf, and S. W. Smith, "Real-time three-dimensional intracardiac echocardiography," *Ultrasound in Medicine & Biology*, vol. 27, no. 9, pp. 1177-1183, Sep. 2001.

- [41] W. Lee, S. F. Idriss, P. D. Wolf, and S. W. Smith, "A miniaturized catheter 2-D array for real-time, 3-D intracardiac echo cardiography," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 51, no. 10, pp. 1334-1346, Oct. 2004.

- [42] G. Gurun, P. Hasler, and F. L. Degertekin, "Front-End Receiver Electronics for High-Frequency Monolithic CMUT-on-CMOS Imaging Arrays," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 58, no. 8, pp. 1658-1668, Aug. 2011.

- [43] J. T. Yen, and S. W. Smith, "Real-time rectilinear 3-D ultrasound using receive mode multiplexing," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 51, no. 2, pp. 216-226, Feb. 2004.

- [44] D. F. Lemmerhirt, X. Cheng, O. D. Kripfgans, M. Zhang, and J. B. Fowlkes, "A fullypopulated 32×32 CMUT-in-CMOS array," in *Proc. IEEE Ultrasonics Symposium* (*IUS*), 2010, pp. 559–562.

- [45] S. Tamano, T. Kobayashi, S. Sano, K. Hara, J. Sakano, and T. Azuma, "3D ultrasound imaging system using fresnel ring array & high voltage multiplexer IC," in *Proc. IEEE Ultrasonics Symposium (IUS)*, 2004, Montreal, Canada, 2004, vol. 1, pp. 782–785.

- [46] R. Fisher et al., "Reconfigurable arrays for portable ultrasound," in *Proc. IEEE Ultrasonics Symposium (IUS)*, 2005., Rotterdam, The Netherlands, 2005, vol. 1, pp. 495–499.

- [47] B. Savord and R. Solomon, "Fully sampled matrix transducer for real time 3D ultrasonic imaging," in *Proc. IEEE Ultrasonics Symposium (IUS)*, 2003, pp. 945–953.

- [48] K. Chen, H. Lee, and C. G. Sodini, "A Column-Row-Parallel ASIC Architecture for 3-D Portable Medical Ultrasonic Imaging," *IEEE J. Solid-State Circuits*, vol. 51, no. 3, pp. 738–751, Mar. 2016.

- [49] T. L. Christiansen, M. F. Rasmussen, J. P. Bagge, L. N. Moesner, J. A. Jensen, and E. V. Thomsen, "3-D Imaging Using Row-Column-Addressed Arrays With Integrated Apodization-Part II: Transducer Fabrication and Experimental Results," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 62, no. 5, pp. 959-971, May. 2015.

- [50] S. J. Jung, J. K. Song, and O. K. Kwon, "Three-Side Buttable Integrated Ultrasound Chip With a 16 x 16 Reconfigurable Transceiver and Capacitive Micromachined Ultrasonic Transducer Array for 3-D Ultrasound Imaging Systems," *IEEE Trans. on Electron Devices*, vol. 60, no. 10, pp. 3562-3569, Oct. 2013.

- [51] E. Kang, Q. Ding, M. Shabanimotlagh, P. Kruizinga, Z. Y. Chang, E. Noothout, H. J. Vos, J. G. Bosch, M. D. Verweij, N. de Jong, and M. A. P. Pertijs, "A Reconfigurable Ultrasound Transceiver ASIC With 24 x 40 Elements for 3-D Carotid Artery Imaging," *IEEE J. Solid-State Circuits*, vol. 53, no. 7, pp. 2065-2075, Jul. 2018.

- [52] M. W. Rashid, T. Carpenter, C. Tekes, A. Pirouz, G. Jung, D. Cowell, S. Freear, M. Ghovanloo, and F. L. Degertekin, "Front-End Electronics for Cable Reduction in Intracardiac Echocardiography (ICE) Catheters," *Proc. IEEE Ultrasonics Symposium (IUS)*, pp. 1-4, 2016.

- [53] J. Lim, C. Tekes, F. L. Degertekin, and M. Ghovanloo, "Towards a Reduced-Wire Interface for CMUT-Based Intravascular Ultrasound Imaging Systems," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 11, no. 2, pp. 400-410, Apr. 2017.

- [54] A. Bhuyan, J. W. Choe, B. C. Lee, I. O. Wygant, A. Nikoozadeh, O. Oralkan, and B. T. Khuri-Yakub, "Integrated Circuits for Volumetric Ultrasound Imaging With 2-D CMUT Arrays," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 7, no. 6, pp. 796-804, Dec. 2013.

- [55] I. O. Wygant, N. S. Jamal, H. J. Lee, A. Nikoozadeh, O. Oralkan, M. Karaman, and B. T. Khuri-Yakub, "An Integrated Circuit With Transmit Beamforming Flip-Chip Bonded to a 2-D CMUT Array for 3-D Ultrasound Imaging," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 56, no. 10, pp. 2145-2156, Oct. 2009.

- [56] I. O. Wygant, X. Zhuang, D. T. Yeh, O. Oralkan, A. S. Ergun, M. Karaman, and B. T. Khuri-Yakub, "Integration of 2D CMUT arrays with front-end electronics for volumetric ultrasound imaging," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 55, no. 2, pp. 327-342, Feb. 2008.

- [57] C. Chen, S. B. Raghunathan, Z. L. Yu, M. Shabanimotlagh, Z. Chen, Z. Y. Chang, S. Blaak, C. Prins, J. Ponte, E. Noothout, H. J. Vos, J. G. Bosch, M. D. Verweij, N. de Jong, and M. A. P. Pertijs, "A Prototype PZT Matrix Transducer With Low-Power Integrated Receive ASIC for 3-D Transesophageal Echocardiography," *IEEE Trans. Ultrason. Ferroelectr. Freq. Control*, vol. 63, no. 1, pp. 47-59, Jan. 2016.

- [58] M. C. Chen, A. P. Perez, S. R. Kothapalli, P. Cathelin, A. Cathelin, S. S. Gambhir, and B. Murmann, "A Pixel-Pitch-Matched Ultrasound Receiver for 3D Photoacoustic Imaging with Integrated Delta-Sigma Beamformer in 28nm UTBB FDSOI," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, pp. 456-456, 2017.

- [59] C. Chen, Z. Chen, D. Bera, E. Noothout, Z. Y. Chang, M. L. Tan, H. J. Vos, J. G. Bosch, M. D. Verweij, N. de Jong, and M. A. P. Pertijs, "A Pitch-Matched Front-End ASIC With Integrated Subarray Beamforming ADC for Miniature 3-D Ultrasound Probes," *IEEE J. Solid-State Circuits*, vol. 53, no. 11, pp. 3050-3064, Nov. 2018.

- [60] H. C. Liu, J. J. Geng, Q. F. Zhu, L. Zhang, F. X. Wang, T. Chen, and L. N. Sun, "Flexible Ultrasonic Transducer Array with Bulk PZT for Adjuvant Treatment of Bone Injury," *Sensors*, vol. 20, no. 1, Jan. 2020.

- [61] H. J. Hu, X. Zhu, C. H. Wang, L. Zhang, X. S. Li, S. Lee, Z. L. Huang, R. M. Chen, Z. Y. Chen, C. F. Wang, Y. Gu, Y. M. Chen, Y. S. Lei, T. J. Zhang, N. Kim, Y. X. Guo, Y. Teng, W. B. Zhou, Y. Li, A. Nomoto, S. Sternini, Q. F. Zhou, M. Pharr, F. L. di Scalea, and S. Xu, "Stretchable ultrasonic transducer arrays for three-dimensional imaging on complex surfaces," *Science Advances*, vol. 4, no. 3, Mar. 2018.

- [62] I. AlMohimeed, and Y. Ono, "Ultrasound Measurement of Skeletal Muscle Contractile Parameters Using Flexible and Wearable Single-Element Ultrasonic Sensor," *Sensors*, vol. 20, no. 13, Jul. 2020.

- [63] S. Shomaji, P. Dehghanzadeh, A. Roman, D. Forte, S. Bhunia, and S. Mandal, "Early Detection of Cardiovascular Diseases Using Wearable Ultrasound Device," *IEEE Consumer Electronics Magazine*, vol. 8, no. 6, pp. 12-21, Nov-Dec. 2019.

- [64] D. K. Piech, J. E. Kay, B. E. Boser, and M. M. Maharbiz, "Rodent Wearable Ultrasound System for Wireless Neural Recording," in *Proc. Annual International Conference of the Ieee Engineering in Medicine and Biology Society (EMBC)*, pp. 221-225, 2017.

### **CHAPTER 2**

# TRANSMIT BEAMFORMER WITH ±30V BIPOLAR HIGH-VOLTAGE PULSERS

This chapter is based on the publication: M. Tan, E. Kang, J. S. An, Z. Y. Chang, P. Vince, T. Mateo, N. Senegond, and M. A. P. Pertijs "A 64-channel transmit beamformer with ±30-V bipolar high-voltage pulsers for catheter-based ultrasound probes," IEEE J. Solid-State Circuits, vol. 55, no. 7, pp. 1796–1806, 2020.

#### 2.1 Introduction

Ultrasound imaging is a safe, cost-effective, and widely-used imaging modality for the diagnosis and treatment of cardiovascular conditions. Miniaturized ultrasound devices mounted at the tip of a catheter or endoscope are becoming increasingly important as they can provide better image quality than external hand-held probes, for instance, to guide minimally-invasive cardiac interventions [1]. A prime example is intra-cardiac echocardiography (ICE) probes, which generate ultrasound images from inside the heart using a transducer array mounted at the tip of a catheter [2]. The image construction relies on the transmission of acoustic waves and post-processing of the reflected echo signals. The acoustic waves are generated by exciting the elements of the transducer array with voltage pulses. Typically, these pulses are timed such that an acoustic beam is formed that is focused and steered at a particular angle. Different pulse timing in successive pulse-echo cycles allows the beam to scan the region of interest to form an image. Since the acoustic signal will be significantly attenuated as it propagates through tissue, high-voltage (HV) pulses (with

amplitudes of tens of volts) are required to generate enough pressure so that the overall signal-to-noise ratio is sufficiently high at the largest imaging depth [3].

In most commercial ICE catheters, the elements in the transducer array are connected to transmit (TX) and receive (RX) circuitry in an imaging system through long micro-coax cables. Given the signal attenuation caused by such cables and difficulties of the cable assembly, application-specific integrated circuits (ASICs) have been integrated closely to the transducer array to reduce the number of cables and increase the signal-to-noise ratio by locally amplifying the echo signals [4]–[9].

An important challenge in the design of such in-probe ASICs is that the required HV TX circuitry cannot be implemented in standard CMOS technologies. This applies to the HV pulsers as well as to the transmit/receive (T/R) switches needed to protect the low-voltage (LV) RX circuitry during pulse transmission. Therefore, HV BCD technologies are usually adopted in which HV MOS transistors are available [4], [5], [8]. Such transistors, however, tend to occupy a large die area while the available area is limited in catheter-based devices. This calls for a compact pulser and T/R SW design.

Unipolar pulsers have been applied (which can only generate positive HV pulses), as they can be implemented using a small number of HV transistors [10], [11]. However, this comes with several disadvantages. In contrast with the bipolar pulses commonly generated by conventional imaging systems, unipolar pulses contain more low-frequency out-of-band energy, and thus lead to lower SNR for the same peak-to-peak amplitude [12]. Moreover, many image-enhancing techniques, such as pulse inversion and coded excitation, are easier to implement using bipolar pulses [13]. Therefore, it is worthwhile to design an on-chip bipolar pulser although the architecture is more complicated.

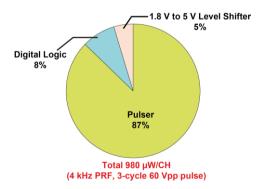

An added benefit of using bipolar pulsing is that it can reduce the dynamic power consumption of the pulser by at best a factor of 2 compared to a unipolar pulser with the same peak-to-peak output voltage, provided a return-to-zero (RZ) pulser is used[14]. This is an important advantage, since the overall power consumption of the ASIC should be minimized to avoid tissue over-heating.

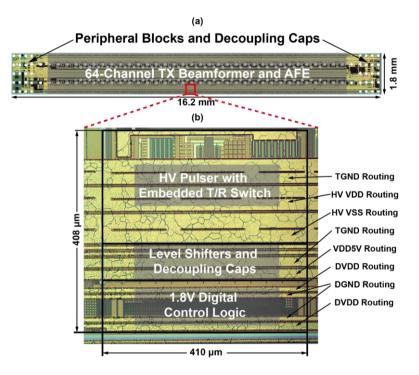

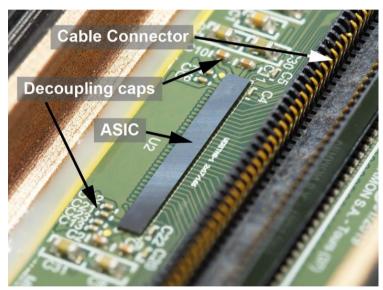

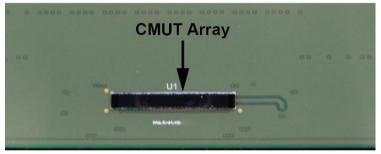

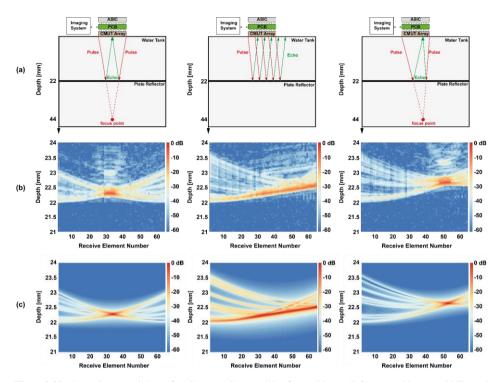

In this chapter, we present a front-end ASIC for a 64-element transducer array that includes an on-chip transmit beamformer and programmable bipolar pulsers. The chapter extends on our previous work [15], [16], in which the bipolar pulser has been described. Here, we present a complete ASIC intended for a CMUT-based 2D ICE probe. With a width of less than 2 mm, the ASIC is suitable for catheter integration and directly connects to the transducer elements in a pitch-matched fashion through a PCB interposer. The ASIC only needs two low-voltage differential signaling (LVDS) clock and data lines to program the on-chip transmit beamformer. Electrical and acoustical measurement results are presented that successfully show the functionality of the bipolar pulser and the complete TX beamformer. This chapter is organized as follows. Section 2.2 describes the system architecture. Section 2.3 discusses the design of the bipolar pulser, while Section 2.4 presents details of the circuit implementation. Sections 2.5 and 2.6 present the experimental results and conclusions.

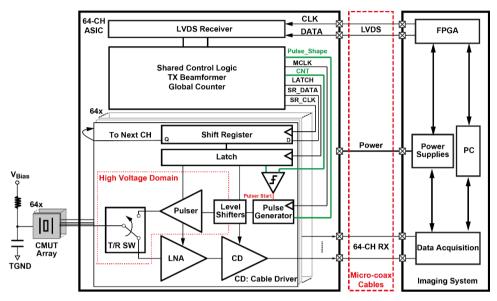

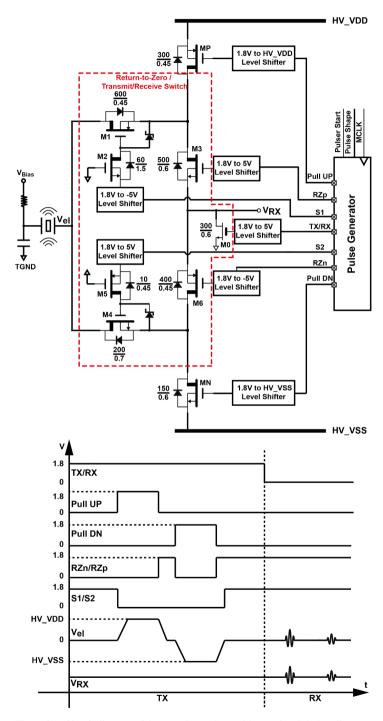

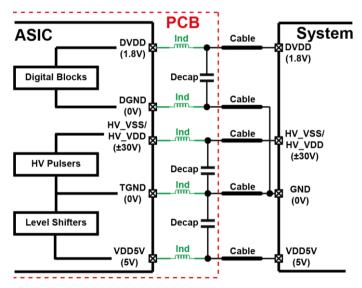

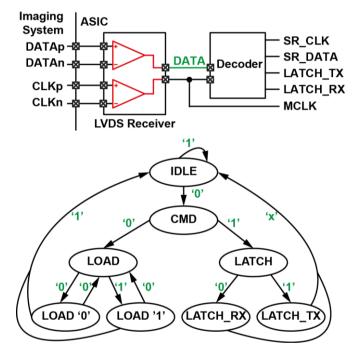

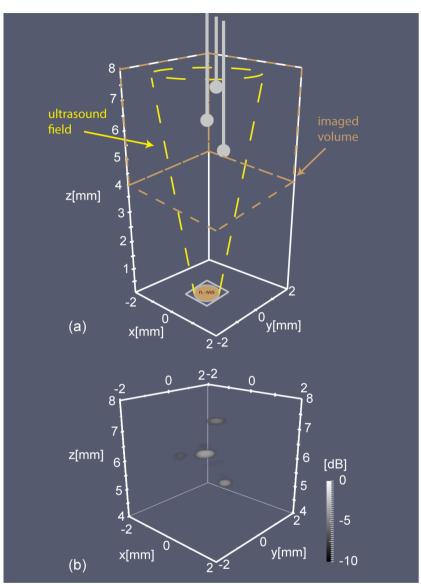

Figure 2.1. System Architecture

#### 2.2 System Architecture

Figure 2.1 shows a block diagram of the proposed system. It consists of a 64-element CMUT transducer array, a front-end ASIC and the imaging system. The elements of the transducer array are directly connected to channels of the ASIC at the tip of the catheter, while a bundle of micro-coax cables ( $\sim 2$ -m long) is used to connect the ASIC with the imaging system.

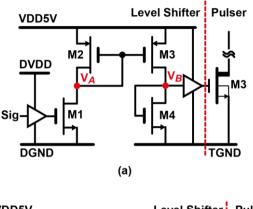

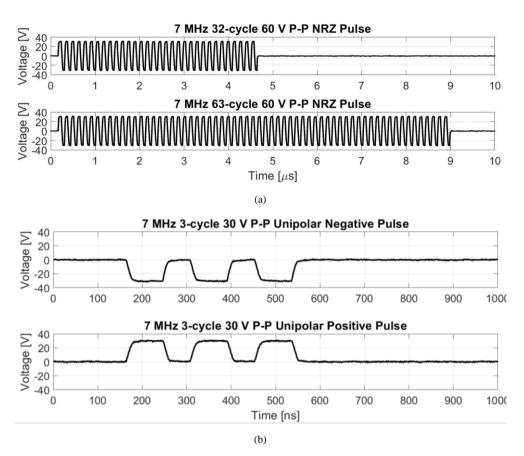

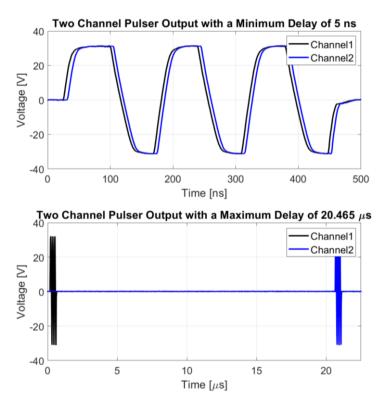

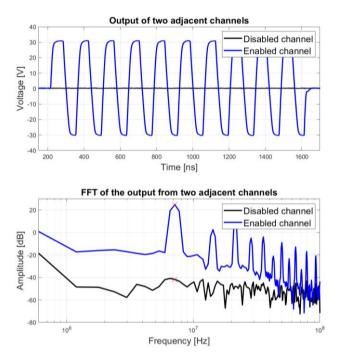

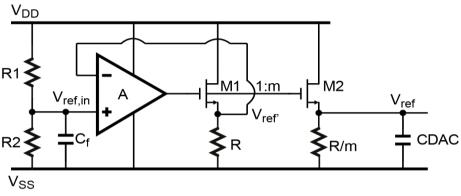

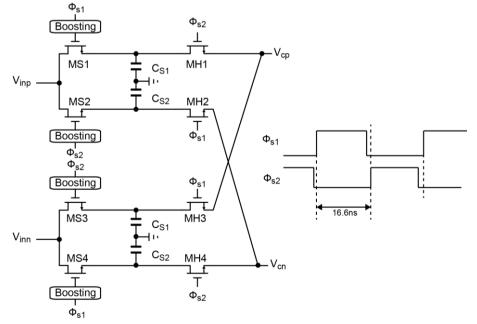

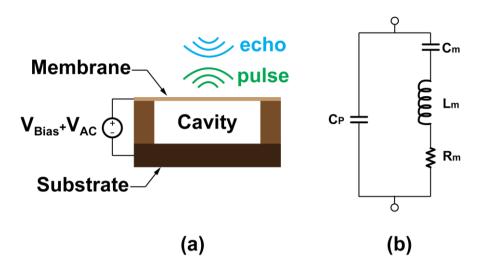

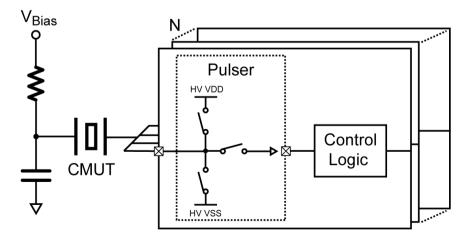

We employ a CMUT transducer array with a center frequency of 7.5 MHz, targeting ICE applications [9], [11]. All the CMUT elements are DC-biased at  $V_{bias}$  and AC-coupled to the transducer ground (TGND) through a shared RC network. To interface with the CMUT elements, each channel of the ASIC contains a T/R switch, a HV TX pulser with associated level shifters and pulse generator, a low-noise amplifier (LNA), a cable driver (CD), and a latched shift register (SR) for the configuration.

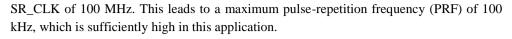

Clock and data are provided to the ASIC by an FPGA through LVDS signals, which are first converted to 1.8 V standard logic levels through an on-chip LVDS receiver. Then, shared control logic will generate a clock (SR\_CLK) and data (SR\_DATA) for the element-level SRs, a latch signal (LATCH) for the element-level latches, and a master clock (MCLK) and counter (CNT) for the timing control of the pulse generators. The SR of each channel

provides the configuration data for the RX amplifiers and HV pulsers, as well as a counter value, which is compared to CNT to define the start time of the pulse. The SRs are daisy-chained to allow the element-level configuration data to be loaded sequentially from the shared control logic. According to the loaded data in the SR, the pulse generator will generate low-voltage (LV) signals to control the HV pulser through the level shifters with a proper timing.

When the CMUT transducer element is excited by the HV pulses, ultrasonic waves are emitted into the medium. The resulting echo signals are amplified by the low-noise amplifiers (LNAs), which are connected to the transducer elements via the T/R switches after pulsing, and then transferred to the imaging system through micro-coax cables with the help of cable drivers (CD). The details of the LNA and CD are presented in [17]. The imaging system will record the echo signals and process them for image reconstruction.

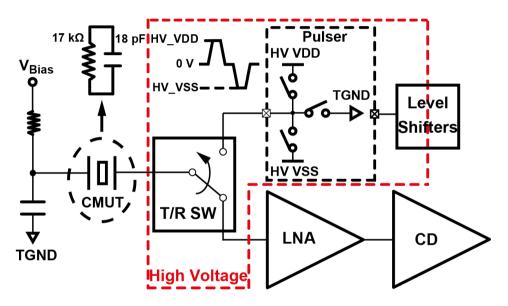

Figure 2.2. Simplified block diagram of a single transceiver channel of the ASIC.

#### 2.3 Bipolar Pulser Design

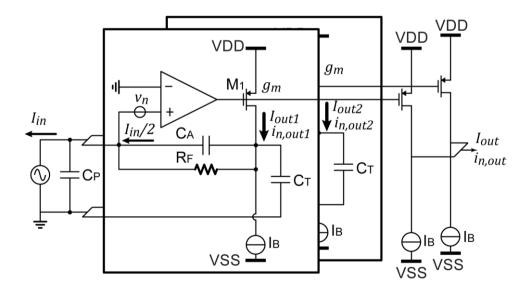

Figure 2.2 shows the simplified block diagram of a single ultrasound transceiver channel of the ASIC. To generate RZ bipolar pulses, the pulser consists of a pull-up switch that drives the CMUT transducer to a positive HV supply (HV\_VDD), a pull-down switch that drives it to a negative HV supply (HV\_VSS), and a RZ switch that pulls the transducer back to ground. The impedance of the CMUT element used in this work can be modelled as 18 pF//17 k $\Omega$ .

Figure 2.3. Overview of HV MOS configurations that can provide back-to-back isolation.

#### 2.3.1 Switch Configurations with Bidirectional Isolation

The RZ switch needs to provide bidirectional HV isolation, in the sense that when it is off, it should be able to handle both positive and negative voltage drop. Similarly, the T/R switch, which connects the transducer to the LNA during echo reception, needs to provide bidirectional HV isolation during pulsing. Two technology-related limitations of the HV MOS transistors in BCD technologies, the body diode and the limited gate-oxide breakdown voltage, increase the implementation complexity of the T/R switch and the RZ switch. The presence of the body diode implies that two back-to-back connected HV transistors are needed to provide bidirectional isolation. The relatively low gate-oxide breakdown voltage requires a more complicated gate-driver design compared to HV technologies with thick gate oxide.

Figure 2.3 shows the eight possible back-to-back configurations of HV NMOS and PMOS transistors. The body-diode orientation in configurations (a)-(d) is such that the middle node

between the transistors ( $V_{mid}$ ) swings up with the positive HV pulse, while in configurations (e)-(h) it swings down with the negative HV pulse. In all configurations, at least one of the sources of the transistors swings up and/or down with the HV pulse, implying that a HV gate driver is needed that keeps the gate-source voltage below the gate-oxide breakdown limit (5.5V in our technology). To prevent this HV floating-gate driver from having to operate at both positive and negative high voltages, configurations in which the source of the left-hand transistor connects to the transducer should be avoided. Driving the source of the right-hand transistor is easier if it connects to the low-voltage circuitry rather than to  $V_{mid}$ . This leaves configurations (a) and (e) as the preferred choice, both of which are applied in parallel in our implementation.

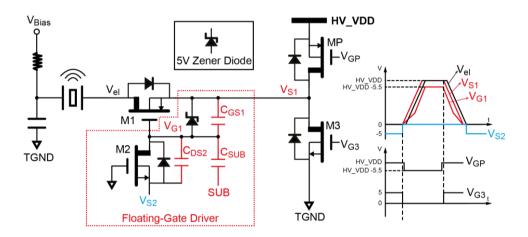

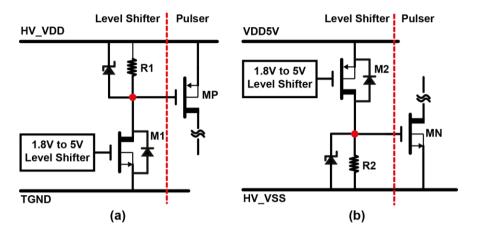

Figure 2.4. Circuit diagram of a high-side pulser employing the single-transistor HV floating-gate driver circuit.

#### 2.3.2 Floating-Gate Driver

In previous HV switch designs [5], [8], [18], bootstrapped gate drivers have been employed. However, they cannot be applied in an RZ switch, because they only allow the switch to be turned on when it is at ground level, while the RZ switch needs to be turned on when the pulser output is at HV\_VDD or HV\_VSS. Therefore, we propose a compact and energyefficient floating-gate driver that utilizes parasitic capacitance to control the gate-source voltage and requires only one additional small HV MOS transistor.

This circuit is shown in Figure 2.4, in the context of a unipolar (high-side) pulser. HV transistors MP and M1 are used to pull the transducer to HV\_VDD, while M1 and M3 together form the switch configuration of Figure 2.3a to provide the return-to-zero switching. The gate of MP is driven relative to HV\_VDD using a conventional level-shifter circuit. The gate of M1 is driven by our new gate-drive approach using transistor M2. Initially, to short

the transducer to ground, M3 and M1 are turned on. M1 is turned on through M2 by connecting M2's source to -5 V and its gate to ground, so that the gate of M1 is pulled to -5 V. Before the HV pulsing starts, the source of M2 is switched to ground, so that the gate of M1 is discharged to ground through the body diode of M2. After this, M2 is off and the gate of M1 floats. When MP is turned on and M3 is turned off, the voltage step on V<sub>S1</sub> will also create a step on the gate of M1 because of the capacitive divider formed by C<sub>GS1</sub> and C<sub>DS2</sub> + C<sub>SUB</sub>, where C<sub>SUB</sub> is the capacitance from the gate of M1 to the substrate. By properly sizing M2 to make C<sub>DS2</sub> + C<sub>SUB</sub> larger than C<sub>GS1</sub>, V<sub>GS1</sub> will increase, turning on M1 and thus allowing the transducer to be charged to HV\_VDD. A Zener diode prevents V<sub>GS1</sub> from exceeding the breakdown voltage. At the beginning of the RZ phase, MP is turned off and M3 is turned on, while M1 remains on. This discharges the transducer until V<sub>el</sub> reaches the threshold voltage of M1 of 0.7 V (~85 times smaller than the pulse peak-to-peak amplitude), thus realizing an almost complete RZ operation. Finally, the gate of M1 is pulled to -5 V through M1.

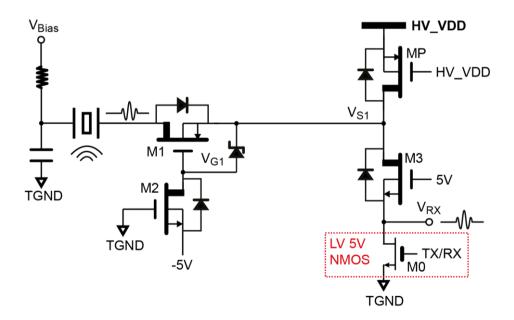

Figure 2.5. Circuit diagram of the high-side pulser with embedded T/R switch.

#### 2.3.3 Embedded T/R Switch

The circuit of Figure 2.4 can be extended with one additional low-voltage transistor M0 to allow it to act also as a T/R switch, as shown in Figure 2.5. This transistor is placed in series with the source of M3 and is turned on during the TX phase, allowing the circuit to operate

as before and preventing any feedthrough of the HV pulse from reaching the RX circuitry. Although M0 will increase the total series resistance for the RZ phase, it can be sized to have a low on-resistance compared to that of M1 and M3 without significantly affecting the total die area since it is an LV MOS transistor. During the TX phase, when the HV pulsing finishes and VS1 and VG1 are at ground level, M1, M3 and M0 are turned on to short the transducer to TGND. During the RX phase, M0 is turned off so that the received echo signal can pass through M1 and M3 to the LV receive circuitry. Since the parasitic capacitance of the LV transistor M0 is relatively small, the transient introduced by the switching of M0 is negligible. Turning on M1 through M2 requires the source of M2 to be -5 V, which is realized using a simple low-voltage charge-pump-based level shifter (see Section 2.4.2). Thus, only 4 HV transistors are used to implement HV pull-up, return-to-zero, and T/R switch functionality.

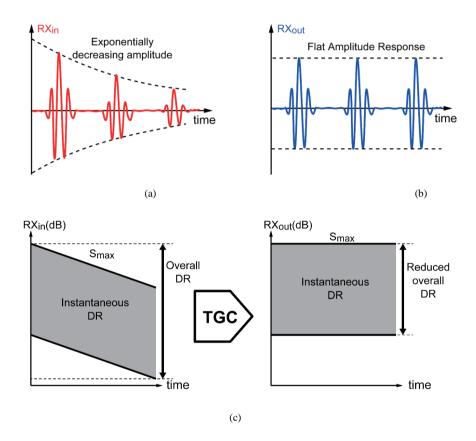

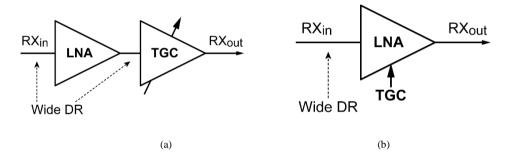

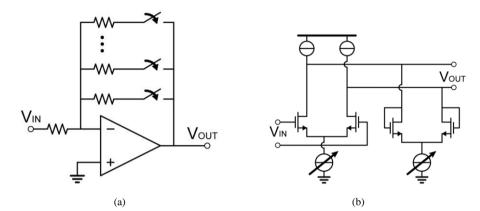

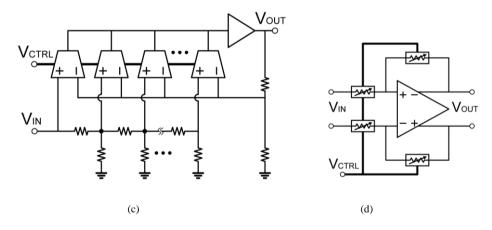

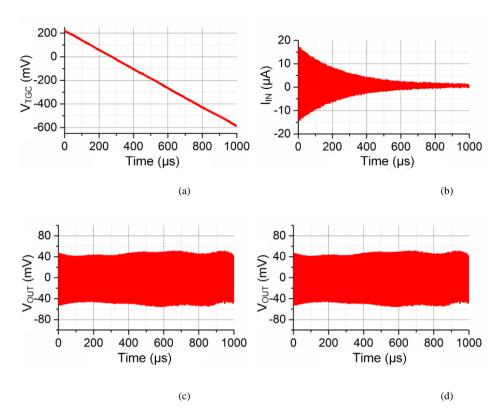

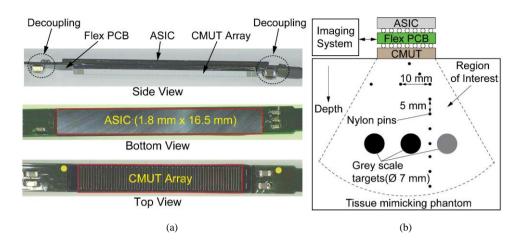

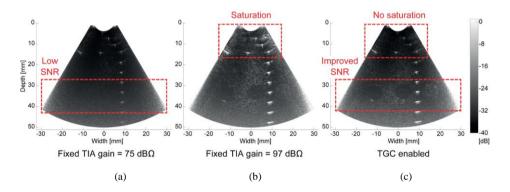

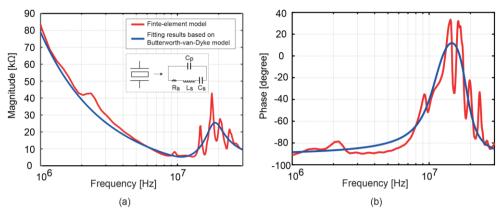

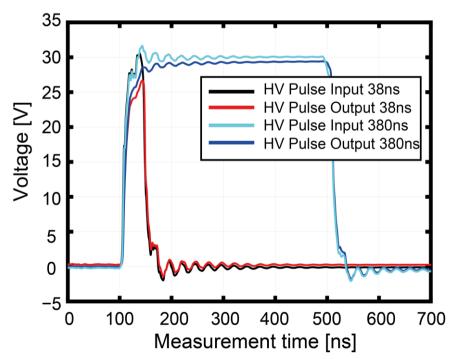

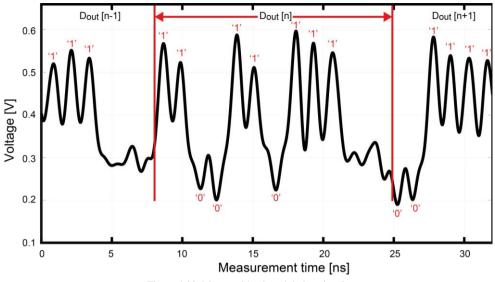

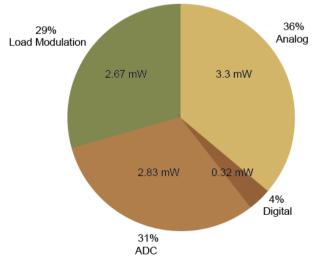

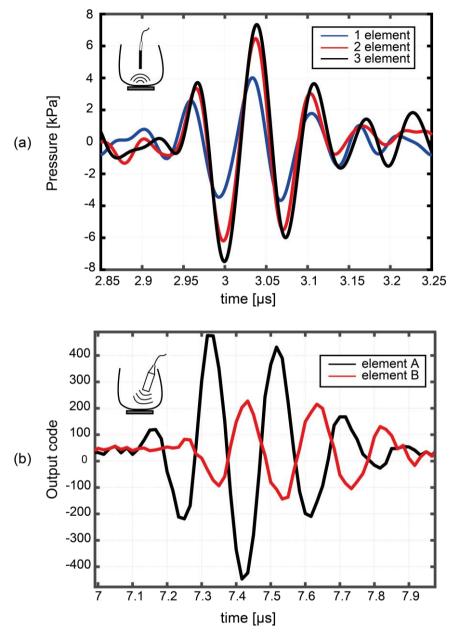

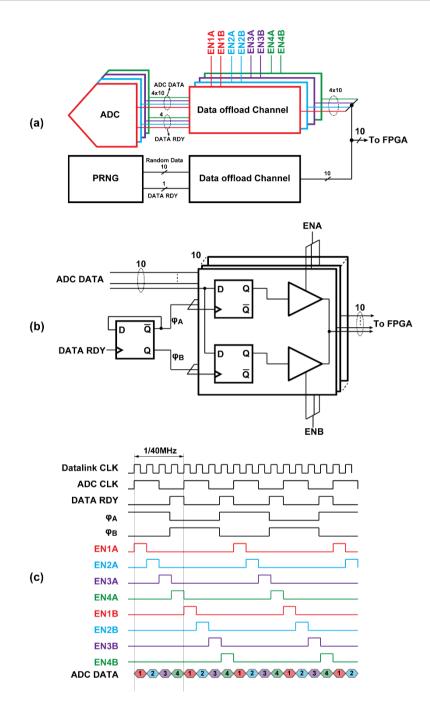

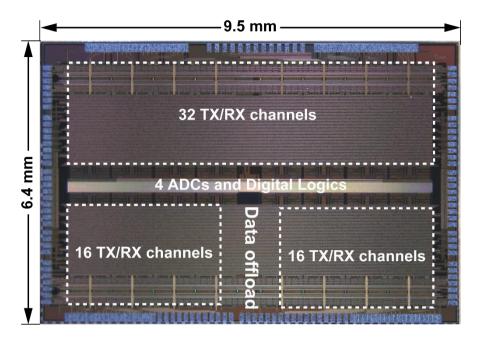

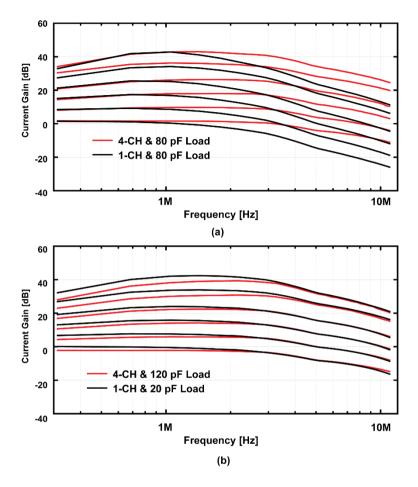

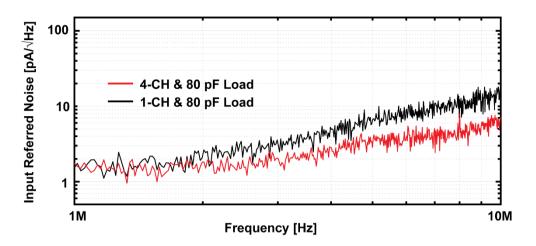

#### 2.3.4 Complete Bipolar Pulser