# Accelerating DNA basecalling of Nanopore reads on FPGAs

J. Haenen

# Accelerating DNA basecalling of Nanopore reads on FPGAs

by

# J. Haenen

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Tuesday October 17, 2023 at 10:00 AM.

Student number:4953266Project duration:February 13, 2023 – October 17, 2023Thesis committee:Prof. dr. H. P. Hofstee,TU Delft, supervisorDr. ir. Z. Al-Ars,TU DelftDr. J. P. Gonçalves,TU Delft

An electronic version of this thesis is available at http://repository.tudelft.nl/.

# Abstract

Genomics has revolutionized our understanding of evolution, hereditary diseases, and more. The advent of long-read DNA sequencers i.e. Oxford Nanopore Technologies' innovations, has opened many new research potentials in genomics. These sequencers produce significantly longer DNA reads, facilitating novel applications. However, this technological leap brings challenges, particularly in accurate basecalling which is the process of converting raw sequenced measurements into digital base pair sequences. While advances in basecalling accuracy have been steadily improving over the years, the computational intensity remains a bottleneck in genomic analysis workflows, demanding costly highend GPUs for probabilistic neural network models.

The main problem this thesis addresses is the implementation of an accelerated hardware solution for the compute-intensive process of basecalling long-read sequences. The thesis presents an FPGA-based implementation of the computationally demanding Long Short-Term Memory (LSTM) layers within the basecalling network known as Bonito. However, due to the lack of floating-point arithmetic units available on the FPGA, the FPGA implementation could not achieve competitive performance compared to GPUs.

While the FPGA implementation falls short of GPU performance, it serves as a possible stepping stone toward developing an ASIC solution for implementing the Bonito LSTM layers or potentially implementing the entire Bonito model. An ASIC implementation has the potential for superior performance up to 9 times faster than a GPU implementation while additionally being cost-effective. This suggests that ASICs hold promise as a future direction for accelerating long-read sequence basecalling, allowing for faster and more affordable genomics research.

# Preface

Working on this thesis presented a fair share of challenges and disappointments. Despite of this difficult journey I am very proud of the results we have achieved. It provided me with an opportunity to expand my knowledge about hardware design and genomics.

I would like to express my gratitude to all the participants who played a significant role in the results and completion of this thesis. At first I would like to express my gratitude to my supervisor Prof. Dr. Peter Hofstee for his guidance and support throughout this research. His knowledge and insights have been very valuable in shaping this work. Also I would like to thank Dr. Zaid Al-Ars, Tanveer Ahmad, and the whole ABS Group of TU Delft for their constructive discussions and contributions.

> J. Haenen The Hague, September 2023

# Contents

| 1 | 1.1       Problem definition and research questions         1.2       Thesis outline                                                                                                                                                                                                          | <b>1</b><br>2<br>2    |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 2 | 2.1       Short reads and long reads                                                                                                                                                                                                                                                          | <b>3</b> 3445566      |

| 3 | 3.1       State-of-the-art of basecalling         3.1.1       Recurrent neural networks         3.1.2       Convolutional neural networks         3.1.3       Transformers                                                                                                                    | 0<br>0<br>1           |

| 4 | STM accelerator design14.1Background of LSTMs14.2System architecture14.3Component design24.3.1Processing engines24.3.2Memory management34.3.3Control44.4Full system design4                                                                                                                   | 5<br>9<br>1<br>9<br>3 |

| 5 | Evaluation         4           5.1         Resource utilization         4           5.2         Performance         4           5.3         Validation         4                                                                                                                              | 5<br>6                |

| 6 | Discussion and performance projections       5         6.1 ASIC implementation.       5         6.1.1 FPGA hard-copy       5         6.1.2 Custom ASIC       55         6.2 Fixed-point analysis       55         6.3 Activation functions.       56         5.4 FPGA PCle interface       55 | 1<br>2<br>5<br>6      |

| 7 | Conclusions and recommendations       5         7.1 Conclusions.       5         7.2 Recommendation.       6                                                                                                                                                                                  | 9                     |

# Introduction

Genomics is an important field of science enabling research to understand better the evolution of humanity and other organisms to curing hereditary diseases and much more. With the advent of long-read DNA sequencers developed by i.e. Oxford Nanopore Technologies over the past decade, a new large step has been made in genome sequencing allowing for much larger preserved DNA reads up to 500 times longer than was possible before; ushering in a new generation of sequencing that allows for a multitude of new applications. However, with the introduction of new technology, there are always difficulties in the early stages which is not different for long-read sequencing. While improved greatly over the years, the accuracy of long-read sequencing has been a challenging facet where only recently accuracy has been high enough to be utilized for non-experimental genomics analysis.

Long-read sequencing can be subdivided into two phases: measuring the DNA using chemical processes, and converting the measured signals into digital representations of the base pairs of the measured DNA. The conversion of the measurement to the base pairs is called basecalling. While both phases contribute to the accuracy of long-read sequencing, the main challenge currently lies in the measurement output of the sequencer. Due to a multitude of factors, these measurements can not be deterministically converted to base pairs, therefore, requiring probabilistic models to perform these conversions. However, the problem is that due to the continued increase in accuracy over the years, these probabilistic models have become larger over those years, dramatically increasing computational intensity. Currently, basecalling has the longest process duration in long-read genomics analysis workflows while additionally requiring expensive high-end compute hardware to run those probabilistic models.

This thesis looks at accelerating the basecalling process for Oxford Nanopore Technology longread sequencers using FPGAs. The basecalling models are identified and one model, called Bonito, is selected to accelerate. The Bonito model has neural network layers, called long short-term memory (LSTM) layers, that take up the majority of the computing time of the models. This thesis provides an FPGA implementation for the LSTM layers that are present in the Bonito model. Moreover, the thesis analyzes the potential benefits of converting the FPGA implementation to an ASIC, which can theoretically achieve comparable results to high-end graphic cards.

## 1.1. Problem definition and research questions

The main problem this thesis addresses is the implementation of an accelerated hardware solution for the compute-intensive process of basecalling.

- To address this problem, we focus on answering the following research questions.

- 1. What are the main computational bottlenecks faced by basecalling applications?

- 2. What hardware architectures and designs are suitable for eliminating these bottlenecks?

- 3. What is the expected performance gain of using these architectures for our application?

# **1.2. Thesis outline**

Chapter 2 of the thesis looks at the background of the thesis project, discussion long-reads, and the long-read pipelines. Moreover, it discusses why it has been chosen to accelerate the basecalling process of the long-read pipelines. Chapter 3 first looks at the state of the art of long-read basecallers and discusses the reason for selecting the Bonito model. After that, it explores the Bonito and explains its architecture. Chapter 3 closes off by exploring the different possible methods to implement the Bonito model. Chapter 4 discusses LSTMs and outlines how the FPGA implementation of the LSTMs of the Bonito model is implemented. Chapter 5 evaluates FPGA implementation, the FPGA implementation is evaluated on three aspects: FPGA resource utilization, performance, and validity. Last, Chapter 6 discusses the potential of implementing the FPGA implementation on an ASIC and discusses other future avenues to be further researched or implemented to enhance the current implementation.

# 1.3. Contributions

This thesis has multiple contributions, these contributions are as follows:

- A state-of-the-art analysis of long-read basecalling implementations providing an overview of the development of basecallers.

- Documentation of the Bonito model and its inner workings which is not provided by the maintainer Oxford Nanopore Technology. Moreover, the models are evaluated for performance.

- An evaluation of possible implementation methods for Bonito on FPGAs.

- A VHDL implementation of the LSTM layers of the Bonito model. Compared to existing LSTM implementation in literature, this thesis implementation deals with significantly larger layer sizes and multiple layers.

- A evaluation of the VHDL implementation and a comparison to the GPU counterpart implementation of Bonito.

- A explorative study that looks at the possibilities and potentials of mapping this LSTM implementation to an ASIC.

# $\sum$

# Background

Since the end of the 20th century, the field of genomics has been on the rise, with various factors contributing to its development. First, it became evident that many diseases can be traced back to the malfunctioning of a single gene was largely incorrect. In almost all cases, there is a complex interaction of many different genes involved. With genomics, the focus shifted from solely examining individual genes to additionally studying the interconnectedness of genes [1].

A large field of genomics is sequencing, which is the process of determining the precise order of nucleotides in a DNA (bases A, C, T, and G) or RNA molecule (bases A, U, T, and G), to enable the study of genetic information and various biological processes. Currently, many facilities utilize 2nd generation sequencing, also known as short-read sequencing, which has been in existence since 2005. However, around 2014 Oxford Nanopore technology introduced a sequencer capable of reading much longer reads, approximately 50 to 500 times larger. This technology is referred to as long-read sequencing or 3rd generation sequencing. The longer reads provided by this technology offer numerous advantages in genomics. Nonetheless, long-read sequencing has presented several challenges that need to be addressed for its widespread viability and adoption in the field [1].

This chapter will first analyze the difference between short and long reads and the challenges of long reads. After that, the long read pipeline will be analyzed to identify potentials to use for acceleration on an FPGA (Field-Programmable Gate Array). Subsequently, a stage from the pipeline will be chosen to use for further acceleration.

# 2.1. Short reads and long reads

Long-read sequencing has emerged as a promising solution to address the main challenge encountered in short-read sequencing methodologies. By producing longer contiguous reads of the genome, long-read sequencing significantly simplifies the genome assembly process compared to short reads. Genome assembly refers to the reconstruction of all the fragmented pieces of the genome before they are separated from each other. Short reads typically consist of an average of 200 base pairs per read, while Oxford Nanopore long reads offer an average of 100 thousand base pairs per read. Considering the human genome, this implies that approximately 450 million short reads are required for assembly, whereas only 900 thousand long reads are needed [2]. The apparent advantage of long reads becomes evident as the genome is split into fewer DNA pieces, simplifying the puzzle of reassembling them into a complete genome, facilitating the correct alignment of long repeat sequence regions, and determining haplotypes [3]. A haplotype is a specific combination of genetic variations on a chromosome inherited as a unit [1].

However, long-read sequencing faced multiple challenges in its early stages, including being slow, error-prone, and expensive. Nevertheless, improvements have been made over the past decade [2]. In 2015, sequencers had an accuracy of approximately 60%, with large variability, making early genome assembly highly challenging or nearly impossible [4]. Today, state-of-the-art PacBio and Oxford Nanopore Technologies (ONT) sequencers have achieved an average accuracy of around 99% in their highest accuracy modes [2]. This improvement in accuracy has played a crucial role in enabling more reliable and efficient genome assembly using long-read sequencing technologies.

While long-read sequencing with current technology still suffers from not high enough accuracy, it is undoubtedly that with current trends long-read sequencing will replace short-read sequencing, and that short-read will mostly be applied with hybrid approaches [5][6][7].

## 2.2. The long-read pipeline

The long-read analysis can be viewed as a pipeline. However, there is not one definitive pipeline as there are multiple different applications to apply to the DNA sample. The following are the most common pipeline stages:

- DNA sample collection and preparation

- · Sequencing the DNA

- · Basecalling the sequenced data

- · Analysis

- Read alignment and variant analysis

- De novo genome assembly

While there are undoubtedly more analysis applications the listed workflow above is currently the most well-proven analysis method that benefits by using long-sequencing [2]. It is important to note that the first three steps (collecting/preparation, sequencing, and basecalling) are fundamental to the long read pipeline and are as such present in each pipeline no matter the application [2][8]. The following sections go more in-depth on the pipeline stages.

### 2.2.1. DNA sample collection

This is a bio-chemistry stage of the pipeline, which includes gathering the DNA, isolating it, and preparing it to be sequenced by the nanopore sequencer. This stage will be briefly described as it does fit entirely into the scope of the thesis.

Human DNA is gathered from patients or test subjects by often collecting their blood, however, other methods like saliva, muscle tissue, etc. are possible but less common. The blood of the patients is chemically cleaned by removing the red blood cells, as they contain no DNA, and keeping the white blood cells which do contain DNA. These white blood cells are destroyed with salt so that the DNA can come out and then the DNA is chemically isolated [9]. The process of isolating long-reads compared to short-reads is more complex as the isolation process has to be more delicate in long-reads. In long-reads, High Molecular Weight DNA Isolation (HMW-DNA) is applied to isolate the DNA, HMW-DNA allows for reads isolated in length over 50 kbases [10].

After the DNA is isolated, it has to be prepared by a technique called library preparation. This library preparation can be used for multiple applications but the main applications are:

- Applying motor and attachment proteins, these proteins help the DNA strains travel to the nanopores in the sequencer and attach to the pores, to be pulled through. To attach these proteins to the DNA, a piece of adapter DNA is attached to the DNA to be pulled through. This adapter DNA allows the proteins to attach to the DNA [11].

- **Barcoding** which is a cost-reducing technique where barcode sequence is added to the DNA, so that multiple patients' DNA can be batched to safe cost, and later after sequencing can be separated by looking for the barcode sequence for each patient in the result [12].

- **Chemically treat** the DNA to be reinforced to result in longer reads or by improving accuracy [11].

## 2.2.2. Sequencing DNA

Nanopore sequencers are long-read sequencers designed by Oxford Nanopore Technologies. While there is a lot of chemistry and physics involved in these sequencing techniques, a nanopore is essentially a hole where the DNA can be pulled through, see Figure 2.1. The DNA travels to the nanopore by means of the motor protein attached after sampling, when it arrives at the nanopore the DNA is caught and split from double-strand DNA (dsDNA) to single-strand DNA (ssDNA), after which one of the split strands is to be pulled through the pore [13]. The nanopore is pulled through the pore with speeds of around 260 base pairs per second (bps) or for bigger sequencers 400 bps. At the same time, a sensor attached on both sides of the nanopore measures the bases at the same sampling speed as the DNA goes through the pore, so 260 and 400 samples per second. This sensor runs a current through the DNA and by measuring the corresponding impedance of the DNA, this impedance can be converted into an analog signal as seen in Figure 2.1 [12]. Matching the rates of sampling and pulling remains a challenge as it leads to "blurry" measurements. The nanopores can be arranged in a 2-dimensional array allowing the nanopore sequencing process to be greatly parallelizable, greatly improving throughput.

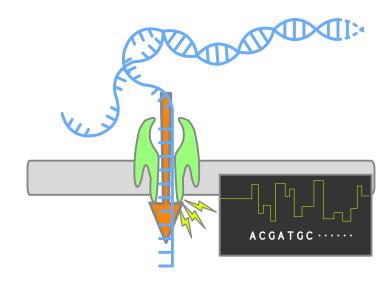

Figure 2.1: Visualization of DNA going through a nanopore and measured to an analog signal [14]

### 2.2.3. Basecalling

After the DNA has been sequenced, the raw sequenced data have to be basecalled. The output of the sequencer is an analog signal, which is not useful to analyze for DNA variations, etc. To make the sequenced data useful, it has to be converted to base pairs (A, C, T, G), as seen sketched in Figure 2.1, this process is called basecalling [13].

Compared to short-read sequencing, long-read basecalling is a much more challenging process. As mentioned before, this challenge mainly lies in the speed at which the DNA strain is pulled through the nanopore during sequencing. If the speed at the strain goes through the port is too high the signal of individual bases may influence the neighboring base pairs, conversely, if the speed is slow a stuttering signal is induced making it apparent as if there are multiple repeating bases even though there is only one. Therefore, this varying speed introduces non-deterministic results out of the sequencer requiring also probabilistic models and algorithms to process it [15].

Currently, this basecalling is the most computationally heavy process in the pipeline and is thus the slowest stage currently in the pipeline [2][8]. While it is very dependent on the hardware used to perform basecalling and not a lot of studies can be found on speed analysis, the time to basecall can lay between 5 to 10 hours which is significantly slower than sequencing [2][8]. There are efforts to perform real-time synchronous basecalling and sequencing, however, this will currently result in a loss of accuracy or using a lot more resources to keep up with the throughput of the sequencer [13]. For instance, the fully saturated nanopores on an Oxford Nanopore Promethion 48 (the largest nanopore sequencer) require

around 4 A100 GPUs using lower accuracy and 20 in the highest accuracy configuration [16][17]. This is very expensive and power consuming, totaling as of the time of writing at \$60,000 to \$300,000 in cost and 1200W to 6000W in power consumption [18], while the Promethion itself costs around \$600 [2].

### 2.2.4. Post-sequencing analysis

The following sections discuss a small sample of the main and most well-proven post-sequence analysis applications.

#### Read alignment and variant analysis

Variant calling is the process of finding variations by comparing the sequenced genome with a database of genomes. This is one of the primary applications of genome analysis [2].

However before the variations can be detected between samples and the database, the sample reads have to be aligned to the database reads, this process is called read alignment. In the initial stages of long-read analysis, this alignment used very complex and sensitive algorithms. However, the current reads are accurate enough that the current alignment process does not require complex algorithms and the process can be achieved relatively quickly and is most of the time baked-in with basecallers as a post-processing step [8]. Additionally, dynamic programming algorithms are introduced that allow base-by-base alignment [2].

There are a couple of main variations that can occur between the sample and database, these are isolated single nucleotide variations, insertions, deletions, and shortened and extended DNA repeat regions [19]. The process of variant calling has been improved significantly by using long-reads over short-reads as the longer-reads allow better detection of repetition length as those most often spanned over multiple short-reads, which makes the alignment with the reference genome unreliable and not feasible for short-read sequencing [2].

Traditionally variant calling has always been performed by comparing samples to databases, newer implementations also deploy deep-neural networks to detect variations which makes it connection-less to a database [20], which allows also the possibility of creating more portable devices. Current implementations have a runtime for variant calling ranging from 1 to 2 hours [8].

#### De novo genome assembly

De novo genome assembly is the process of reassembling the sequenced genome. This process is as mentioned before made easier by the long-read sequencing, as there are fewer reads necessary to reassemble the genome. The most applied technique to assemble genomes is by utilizing string graphs where entire reads are compared to each other using minimizers and MinHash techniques [2].

However, the challenges in this pipeline stage are not algorithmic but again depend more on the accuracy of the sequencer and basecalling process. Currently, most of the time in de novo assembly is spent on correcting the reads from the sequencer [21]. The process of assembling a telomere to telomere (begin to end of the chromosomes) genome error-free has only recently become possible by utilizing every possible new technique to improve read accuracies [2].

# 2.3. Basecalling challenges

Considering the discussed long-read pipeline, it seems that the most interesting part is the basecalling stage, due to its time bottleneck and accuracy implications. DNA preparation and sequencing clearly fall out of the domain of Computer Engineering, and thus pose little potential. However, compared to the post-sequencing analysis methods it seems that the main challenges still lay in the low accuracy of the basecalling and sequencing process, so by further improving the basecalling process a lot of post-sequencing analysis methods will benefit too. Additionally, this leads to another point that basecalling is the core stage of all long-read analysis, as all subsequent tools require a basecalled sequence, not the analog signal. Lastly, the basecalling process is currently very slow, it takes up a large chunk of the entire long-read pipeline. Therefore improving this part of the process by accelerating will be a great benefit for a lot of users of these pipelines.

# 3

# **Exploring basecallers**

This chapter will describe the exploration of basecallers. It will look at the state-of-the-art techniques used to perform basecalling, compare several basecalling solutions to each other, and end by selecting the most suitable basecaller to consider for acceleration. This selected basecalling solution will in turn be analyzed further to examine its bottlenecks and strengths. Finally, there will be looked at suitable methods to implement this selected basecaller on an FPGA.

# 3.1. State-of-the-art of basecalling

While discussing the pipeline, it was already mentioned that the process of basecalling for Oxford Nanopore sequencers is not a deterministic process. This is due to the fact that the sample interval and the speed that the DNA strain goes through are not always synchronous, resulting in base pair readings blurring other base pairs and stuttering resulting in false repetitions [15]. For this reason, the state-of-the-art implementations are currently exclusively built on stochastic or probabilistic models, being neural networks or hidden Markov models [2].

While numerous basecallers have been made in the past decade, only a few will be selected to be highlighted here to demonstrate and compare different architectures of neural networks. The current space of basecallers can be divided into 4 categories:

- Neural network implementations

- Recurrent neural networks

- Convolutional neural networks

- Transformers

- · Other implementations

- Hidden Markov models

### 3.1.1. Recurrent neural networks

A recurrent neural network (RNN) is an artificial neural network specifically designed to handle sequential or time series data. These deep learning algorithms are extensively employed for solving ordinal or temporal problems, including language translation, natural language processing (NLP), speech recognition, and image captioning [22]. The problem of basecalling can be closely mimicked to a speech recognition problem. Converting an analog signal to a sequence of speech-to-words for speech recognition is very similar to converting the analog signal from the nanopore sensor to bases (letters) A, C, T, G during sequencing [23].

What sets RNNs apart is their inherent "memory" capability, enabling them to leverage information from preceding inputs to impact the current input and output. In contrast to traditional deep neural networks that treat input and output as independent entities, recurrent neural networks rely on the previous elements within the sequence to determine their output [22].

Oxford Nanopore, in its initial stages, introduced three distinct models for their sequencing technology: Albacore, Guppy, and Scrappie. Among these models, Albacore was designed as the earliest (2017) and used a CPU implementation, while later (2018) Guppy and Scrappie were developed by using GPU implementations. Guppy was the most accurate while also being a stable model at the time, while Scrappie was more experimental and served as a testing ground for new features and enhancements that were being considered for integration into Guppy [24].

These implementations by Oxford Nanopore first used only a single layer of RNNs, which resulted in still very low read accuracy of around 88% [25]. This accuracy is too low to perform any useful post-sequencing analysis [2]. Around the same time Oxford Nanopore was developing its GPU implementations, another basecalling architecture was developed by Haotian Teng et al. called Chiron [26]. This architecture modeled a new architecture by introducing newer developments from the research of speech-to-text applications. Chiron combined deep learning with RNNs; this meant that the raw nanopore signal was first fed into convolutional neural network (CNN) layers before going into the RNN layers. By utilizing a CNN, the model extracts useful features of the raw signal instead of feeding just the signal into the RNN directly. By training the model, the CNN can be trained to extract features of the raw signal that provide better information to the RNN layer. Haotian Teng et al. state that using both CNN layers and RNN layers is crucial in basecalling networks otherwise accuracy will drop significantly [26].

Additionally, Chiron introduced a statistical post-processing layer called connectionist temporal classification (CTC) decoder to get to the final basecalled sequence output. The CTC decoder solves the variable speed problem of the DNA strain going through the nanopore better. Essentially what this layer adds is that a new label is added to the existing A, C, T, and G labels; this label is a null label that allows the RNN to output nothing if it is most likely that the input signal stuttered. With this new label, the CTC decoder predicts the most likely sequence given the output of the RNNs, however, it also takes previously predicted sequences into account [27]. While the accuracy increased, the model was however very slow; 100x slower than the Oxford Nanopore implementations [25]. However, Oxford Nanopore developed another model called Flappie based on Guppy that used the CTC decoder without the CNN layers [25]. Next to this, Flappie introduced a "flip-flop" mechanism which means that the output from a layer is reversed when it is put in the consecutive layer [28]. While the reason is never stated in literature why the exact reason for this "flip-flop" architecture is developed, it is most likely that this is due to the measurement of the sensor being bi-directional. This means that the DNA strain could have passed through the nanopore in either direction causing the sensor reading to be reversed. It is likely that continuously flipping the outputs between layers increases accuracy as it is analyzed from both directions. This model eventually replaced Scrappie in being the experimental line and Scrappie fell out of development [29]. A year into development, Flappie was also archived suggesting that it is most likely that it has been incorporated into Guppy [13][25], however due to Guppy being proprietary software it is impossible to be certain.

In 2020, Oxford Nanopore made an open-source version of a basecaller called Bonito/Dorado. Bonito and Dorado are the same model, the only difference is that Bonito is written in Python using PyTorch while Dorado is written in C++ [30][31]. For ease of reading only Bonito will be mentioned, however, most comments will apply to both and it will be specified when something is different for Dorado. While there is little to no literature attached to these models, by examining the commit history of the code repositories the model's development has been very analogous to the development mentioned earlier with Guppy and its experimental models (Flappie, Scrappie) [30]. However, the current implementation of Bonito has shifted in 2022 to a model very similar to that of Chiron, although the reason for this design shift is not documented it is clear that it is a good architecture as currently, Bonito is the most accurate basecalling model to date by achieving a read accuracy of 93% [32]. However, there are changes compared to the Chiron CNN-RNN-CTC architecture: the "flip-flop" mechanism from Flappie is introduced and the CTC layer has been changed to a conditional random field (CRF) decoder as a post-processing layer [30]. Instead of the CTC predicting the most likely sequence given the previous prediction, the CRF decoder is more granular predicting the most likely base given its neighboring bases [33]. This CRF is considered superior over CTC from benchmarking improving performance over 4% [32]. Altogether, Bonito is currently the leading basecalling tool available having little competition, Bonito's model is speculated to be copied over into Guppy [32]. It has high accuracy but is still considered slow [34], however, its higher accuracy enabled better post-sequencing analysis leading it to be the most popular [30].

#### 3.1.2. Convolutional neural networks

Other models try to perform basecalling by removing the RNN from the models and creating full CNN models. There are three prominent models developed, CasaulCall, URnano, and MinCall, that use full CNN networks which arose around 2020 [32]. The main problem these models tried to solve was that the RNN models were slow [35][36][37]. The main bottleneck lies in the recurrent nature of RNNs, meaning that the computation of the subsequent inference is dependent on the previous inference making unrolling and parallelization complex [35]. CNNs on the contrary are very parellizable making them in terms of speed very competitive, but they compromise on accuracy with MinCall having a very low 63% read accuracy, whilst CasaulCall and URnano having 88% and 90% accuracy respectively [32]. The read accuracies of URnano and CasaulCall were competitive at the time with URnano being on par with Guppy at the time [37].

CasaulCall and MinCall are very similar to the Bonito implementations with the RNN layers stripped away, the architectures are roughly a CNN-CTC network [35] [36]. URnano uses a slightly different approach instead of having the neural network outputting the sequence of bases, the neural network outputs a base mask. This base mask is fed into the label transformer algorithm which performs a per base conversion instead on a per sequence basis with CTC [37]. As seen with the CRF which also uses a more per-base approach, this approach leads apparently to better accuracy compared to CTC [32].

Currently, none of these three networks are in active use nor development, making the analysis from Haotian Teng et al. quite plausible that basecaller neural networks require both CNNs and RNNs [26]. The most likely reason for these models to be abandoned is that the accuracy is too low compared to RNN networks and in the case of URnano being actually 2x-3x slower than Guppy in 2020 [37].

## 3.1.3. Transformers

A transformer model is a type of neural network that acquires contextual understanding and meaning by analyzing the relationships among sequential data elements, such as the words in a sentence. Utilizing a set of mathematical techniques known as attention or self-attention, transformer models can discern subtle connections between remotely positioned elements within a sequence and can identify how they influence and rely on each other. These sophisticated algorithms enable the transformer to grasp long-range dependencies in the data, leading to more accurate contextual comprehension [38].

By this description, transformers seem quite similar to RNNs, however, solve some problems attached to RNNs. RNNs are trained sequentially, this leads to two problems that transformers do not suffer from. First, sequential training means that parallelizing the inference is more difficult for RNNs. Another problem in RNNs is exploding and vanishing gradients, due to the recurrent properties of RNNs training results in feedback loops. These feedback loops make it difficult to train RNNs as it is difficult to keep the gradients bounded as the gradients tend to explode to infinity or vanish to zero over time [39]. Due to the attention algorithms, transformers do not have a recurrent structure meaning they are highly parallelizable [40]. Moreover, this means that the aforementioned problems of RNNs do not apply to transformers [41]. Another benefit of transformers is that pre-trained models can easily be used for other tasks, resulting in less training time [41].

Currently, there are two prominent transformer models for basecalling SACall and CATCaller [32]. Both these models are based on a CNN-transformer-CTC model [42][43]. While SAcall is based on the transformer model, CATCaller is based on a lite-transformer model [32]. This lite-transformer is different in that the convolutions, called lightweight convolutions, in the transformer layer are sharing weights. These lightweight convolutions reduce the model complexity allowing lite-transformer models to be run on edge devices [44]. While these models claimed to be designed for speed, SACall is not faster than Guppy [42] and CATCaller claims to be 4x faster than SACall it does not make any speed comparison to Guppy [43] making comparisons very difficult. Accuracy-wise the transformer models seem to be not competitive. As from the benchmark result of Marc Pagès-Gallego et al., RNNs are superior to transformer models [32]. Since the transformer models are still using CTC decoders, these results might be more competitive if they use a CRF decoder instead as the current RNN basecallers.

#### 3.1.4. Hidden Markov models

Hidden Markov Models (HMM) are statistical models that relate a sequence of observations to a sequence of hidden states. It is useful for predicting future observations or classifying sequences based on the hidden process generating the data [45]. While a lot of literature claims that hidden Markov models were used as the first basecallers for long read analysis [2][25][26][32], it seems to be difficult to find any HMM implementations for basecallers. One HMM basecaller could be found called Nanocall [46]. The model is trained using Expectation Maximization (EM) which is very standard for HMMs. At the end of the HMM inference, Nanocall applies a Viterbi decoder to get the output. The Viterbi decoder is similar to a CTC decoder, however, it only considers the current sequence to predict the sequence output instead of including neighboring sequences [46]. The inference of HMMs and thus Nanocall are very lightweight computations compared to neural networks.

It seems however that hidden Markov models have completely fallen out of favor and current implementations have completely shifted towards neural networks. While hidden Markov models are easier to accelerate, the accuracy in basecalling with neural networks is much higher for neural networks than for hidden Markov models [2].

### 3.1.5. Choosing a model

After comparing and discussing different models and architectures, it was decided to choose the Bonito model to accelerate on an FPGA to demonstrate Fletcher and Tydi, two technologies developed by the Accelerated Big Data Systems (ABS) group from TU Delft. Fletcher is a framework that helps to integrate FPGA accelerators that use an Apache Arrow back-end [47]. Bonito switched over at the end of 2022 to the POD5 file format from the older FAST5 file format [30]. The POD5 file format stores data in Apache Arrow tables, this means that data is stored in a columnar format allowing for more efficient data readouts for acceleration purposes [48]. POD5 using Apache Arrow means that more tools are available, like Fletcher, as Apache Arrow is general-purpose and popular while FAST5 is just designed for Nanopore sequencing. Bonito is currently the only major basecaller using POD5 making it ideal to implement with Fletcher.

Next to the POD5 argument, Bonito is currently the most accurate basecalling solution while also relatively being speed competitive [32]. Bonito is also the most widely used next to Guppy but Bonito is an open-source basecaller and Guppy is proprietary making it impossible to know how Guppy is implemented exactly. Additionally, all the other basecallers from literature have no published source code or have been unmaintained for several years making it not compelling to create an accelerator from them. Additionally, full CNN models are not very suitable to accelerate on FPGAs as it is hard to beat GPUs with CNNs since GPUs have dedicated hardware for tensor calculus.

## 3.2. Deep-dive into Bonito

Since Bonito is the chosen model to accelerate, this section will dive deeper into the neural network components that Bonito consists of and benchmark the model to identify the most computationally heavy components of the network. After this analysis, multiple implementation options will be explored to decide the best way to implement the Bonito on an FPGA.

## 3.2.1. Analyzing Bonito

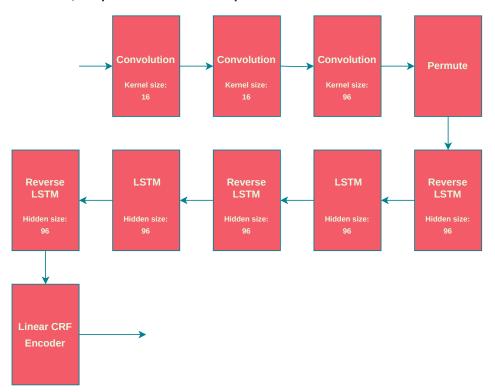

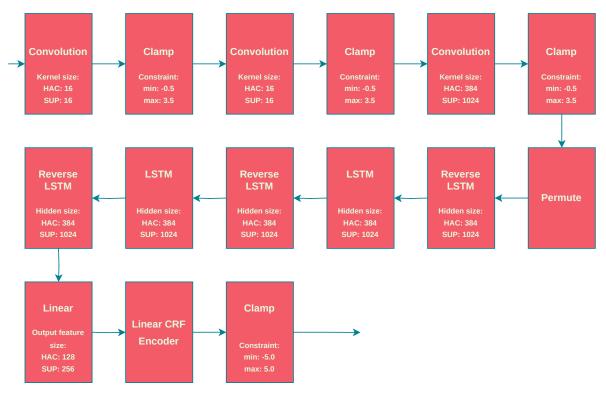

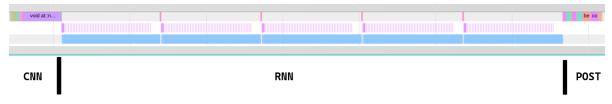

As mentioned before, Bonito is a model by Oxford Nanopore and it uses a CNN-RNN-CRF model. However, this classifier CNN-RNN-CRF does not describe the model completely as there are many more granular components present in the model. Moreover, Oxford Nanopore does not provide any literature or documentation about the design decision or how the model works, therefore, the model is *"reverse-engineered* in this section to provide such documentation. By delving into the config files of the models, it is possible to construct an overview of the model, as seen in Figure 3.2 [30]. There are three models provided by Bonito: Fast, High Accuracy, and Super Accuracy (presumed from the abbreviation SUP). The Fast and High-accuracy models can be used for real-time basecalling depending on the amounts of nanopores present in the sequencers (sequencer throughput) and the computational throughput of the basecaller. The super model is generally used in a catch-up mode meaning the output of the sequencer is buffered [13]. Moreover, there are two models for each accuracy model for a sequencing speed of 260 base pairs per second (bps) and 400 (bps), these models do not differ from each other architecturally, the only difference is that the weights are different.

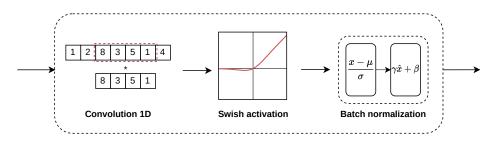

A convolutional block consists of multiple subfunctions, as seen in Figure 3.1. While the most computationally heavy and important part is the convolution, a batch normalization, and a swish activation function are performed after the convolution. The batch normalization is used to speed up training, it allows for faster training speeds by normalizing the output from the convolution to network-wide normalization making it not too high or too low to be processed by subsequent layers [39]. The swish activation function is not standard but is more recently becoming popular over the more standardized ReLU activation function [49]. Activation functions are often simple but very crucial to allow for non-linearity in the neural network as all other components like convolution, RNN, etc. are linear equations [39]. Swish is a type of sigmoid-weighted linear unit (SiLU) activation that looks like  $Swish(x) = x \cdot \sigma(\beta x)$  where  $\beta$  is a trainable parameter which allows for tweaking the linearity of the activation function; if  $\beta \rightarrow 0$ the function becomes linear by the increasing  $\beta$  the sigmoid function will be more pronounced. The convolutions are all 1-dimensional convolutions with a convolution kernel of size 16. As seen in Figure 3.2, the convolution sizes the input up to the size of the RNNs, starting from 1 and ending up at 96, 384, or 1024 depending on the model size.

Figure 3.1: Architecture of convolutional block in the Bonito models

The RNNs in the models are called LSTMs (long-short-term memory), LSTM is a variant of RNN as traditional RNNs are barely used anymore. Traditional RNNs suffer a lot from the vanishing gradient problem because they only keep track of short sequences and forget older inputs; this is called short-term memory. LSTMs add an additional long-term memory which allows older inputs to affect the current data thus meaning that these older gradients do not vanish. The long-short term memory allows LSTMs to analyze data on a granular scale but still can keep correlation between distant data [39]. The LSTMs have a size of 98 in the fast model, 384 in the high accuracy model, and 1024 in the super model; these sizes do not change between layers. As mentioned before with Flappie, Bonito also uses the *"flip-flop"* mechanism which means that the output will be reversed between layers.

After the LSTMs, the output is again reduced using a linear layer, also called a fully connected layer (FC). The reason for this fully connected layer is not clearly known due to the lack of documentation. Normally, FC layers let all inputs interact with each other to create more interdependency between the output of the previous layer, and the output is reduced back to the training labels. However, here the output goes into another linear layer, the linear CRF Encoder, which consists of an FC layer and a CRF encoder. The FC layer scales up the data so that the CRF encoder can output scores in a linear-chain CRF. This linear-chain CRF can be used to calculate the log probability of a particular (aligned) output sequence [50]. As a guess the first linear layer is to classify the output of the LSTMs for the CRF decoder as the first stage of the linear CRF decoder is also an identical linear layer, hence it does not make sense that it is to reduce data size for the CRF decoder.

Additionally, there are some small layers like clamp and permute that are not very computationally heavy. The clamp layer clamps the output between boundary values so that the output is not too large or too small for the next layers. These boundary values are defined in the model config and thus not trained. The permute layer turns the input tensor around axes, it is not very clear from documentation or literature why one would apply this layer, however.

### 3.2.2. Benchmarking Bonito

The amount of parameters seems to be heavily dependent on the size of the LSTMs used. The difference between models is only significant in the sizes of the LSTM. The super model has  $7 \times$  more parameters than the high accuracy model which in turn has  $14 \times$  more parameters than the fast model. To further attest to this claim, the model has been benchmarked. The benchmark was run on a server with an *Intel Xeon E5-2620* CPU and a *NVIDIA RTX 2080Ti* GPU. Figure 3.3 shows the trace of the

Fast: 427,984 parameters 260/400bps

HAC (High accuracy): 6,213,296 parameters 260/400bps

SUP (Super): 43,610,800 parameters 260/400bps

Figure 3.2: Overview of bonito models

runtime of a single inference through the Bonito model. The trace clearly shows that nearly all the processing time of the inference is spent on the RNN calculations, demonstrating clearly that the LSTM is the bottleneck in the calculations.

Figure 3.3: Trace of an inference of the Bonito network

Next to the trace, it is also interesting to see how the models compare to each other. The result of this benchmark can be seen in Table 3.1. Dorado has been chosen to be benchmarked as well and clearly from the table it is apparent that it is much faster than Bonito. This speed difference is not surprising, however, as mentioned by the maintainers of both Dorado is for practical use while Bonito is more for training purposes and model development and analysis [30][31]. This is mainly because of Bonito using Python which is easier to develop for and experiment with than C++ used by Dorado but Python being an interpreted language means it induces more overhead. The models between Dorado and Bonito are as said before equivalent. The super model is also significantly slower than the other models which scale not linearly with the number of model parameters. This indicates that computationally the throughput decreases faster for larger LSTM sizes.

|                     | Bo               | nito             | Dorado           |                     |  |  |

|---------------------|------------------|------------------|------------------|---------------------|--|--|

|                     | Duration (H:M:S) | Reads per second | Duration (H:M:S) | b) Reads per second |  |  |

| Fast model          | 00:24:53         | 53.6             | 00:03:09         | 424.5               |  |  |

| High accuracy model | 00:33:21         | 40.0             | 00:17:31         | 76.2                |  |  |

| Super model         | 03:00:41         | 7.4              | 01:46:32         | 12.6                |  |  |

## 3.2.3. Implementing Bonito

There are multiple avenues to explore to implement Bonito from scratch. The first possibility is to build the entire model from scratch in VHDL or Vivado High-Level Synthesis (HLS). While this would give the most control over the project's implementation, it would also be a lot of work and require a lot of research in each layer to understand how to implement it while also making it performant. AMD has however introduced over the years a lot of frameworks and tools to use to more easily implement neural networks on FPGAs, an example being FINN [51]. FINN is a tool that allows generating dataflow-style architectures on an FPGA based on pre-trained neural networks. While that description fits nicely with Bonito being a pre-trained model, there are some caveats as some layers are not supported mainly being RNNs. Since the core of the models are RNNs, this means that this makes FINN not feasible. Moreover, FINN does not support the swish activation function and CRF layer, however, this is much less of a concern since these are not very complicated layers; the CRF layer is essentially an FC layer, which is supported, with a quite lightweight scoring algorithm after it.

Next to FINN, there is still another tool available to help implement it called Vitis-AI, also by AMD. Vitis-AI is more of a blanket term for a collection of AI IPs, libraries, tools, and models. The main workflow of Vitis-AI is using a pre-built model from the so-called "*Model Zoo*" provided by AMD. This model can be adjusted to be more in line with the model to be implemented but this adjusting is very limited, so models may need to be nearly one-to-one and can differ only in size for some layers [52]. After selecting a good model implementation is quite easy, as the models from Model Zoo have already been deployed and tested on FPGAs. While Vitis AI states that RNNs are supported, all links leading to documentation and models on GitHub are broken. It seems that the RNNs from Vitis AI have been

dropped since going to version 3 in 2022. This means that using Vitis AI and Model Zoo is not possible to implement Bonito.

Before going all the way down to low-level hardware design VHDL/HLS, a last attempt was explored to use a higher-level approach by combining C $\lambda$ ash and HaskTorch. C $\lambda$ ash is a high-level synthesis language like Vivado HLS but instead of HLS using C++, it uses Haskell. Haskell in turn has a Torch implementation called HaskTorch which makes it easy to run Bonito in Haskell as Bonito is built using PyTorch which is a Torch implementation for Python. While running the model is possible, it seems to be very hard to make HaskTorch and C $\lambda$ ash work together as HaskTorch is designed really for CPU and GPU implementations. After a lot of trying this solution seemed to be also a dead end.

A final possibility without going to a from-scratch implementation is looking into the AMD VCK5000 Versal FPGA. Versal is an FPGA card specifically designed for neural network acceleration by offering special hardware blocks on the FPGA for neural networks. Access to this FPGA has been granted by the *Heterogeneous Accelerated Compute Clusters* at ETH Zürich to use for this project. While on the product it specifies that it can be used for CNNs and RNNs [53], if one looks deeper into the documentation there is no trace to be found about RNNs. The documentation only specifies how to use the special hardware blocks for CNNs and those blocks seem to only have CNN capabilities meaning that utilizing this FPGA for RNNs would be equivalent to any other FPGA of equal resource capability.

It seems now that every high-level implementation gets stuck on not being able to implement LSTMs, it seems to be important to explore why this limitation exists before starting a from-scratch implementation. While the lack of RNN support in models can be due to the higher popularity of full CNN networks, there might also be more reasons for there being such low support. After research, it seems that the internal storage (SRAM) of the FPGA seems to be the main bottleneck on FPGAs. This means that a lot of the time LSTM implementation needs to stream from DRAM which is significantly slower [54][55]. Therefore, it is important to find out the means to make this memory management work on an FPGA, but for that first, a better understanding must be acquired to find out why LSTMs are more memory intensive than i.e. CNNs.

This also marks a turning point in the thesis that the focus shifts away from creating a demonstrator using Fletcher and Tydi to implementing the LSTM part of Bonito. The decision was made to only focus on the LSTM because clearly there is a bottleneck that potentially can be solved but also the LSTM has a lot less research compared to other layers i.e. CNN, FC, etc. CNNs for instance can be easily generated so by dropping the Fletcher and Tydi part not a lot of interesting research potentials remain there.

4

# LSTM accelerator design

This chapter will examine the entire design process of implementing the LSTM layers of Bonito on an FPGA. First, the LSTM layer will be analyzed theoretically to understand the workings of LSTMs. After that, an FPGA will be selected for use in implementation based on the requirements imposed by the LSTM layer. Before going into the low-level implementation of the hardware components, first an abstract overview is shown of the design system architecture and the components will be abstractly outlined. After the overview, each component will be described in more detail including design challenges and iterations.

## 4.1. Background of LSTMs

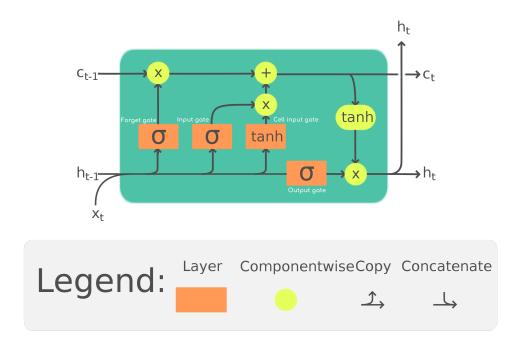

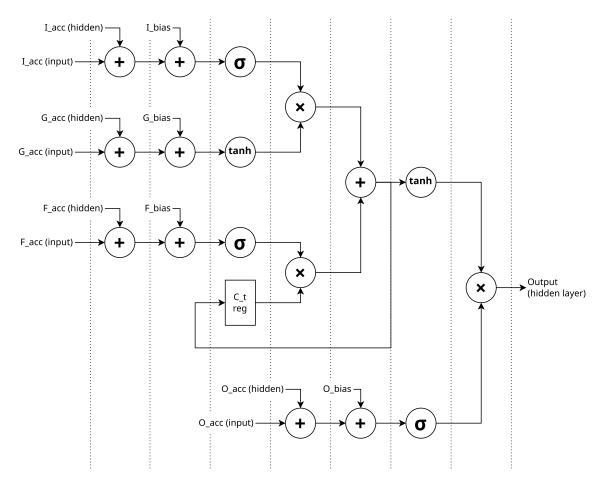

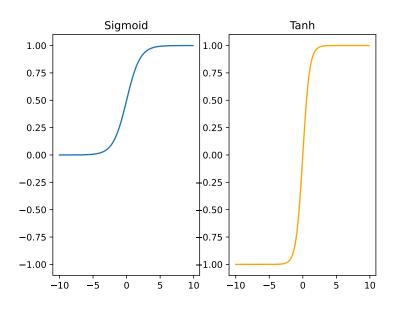

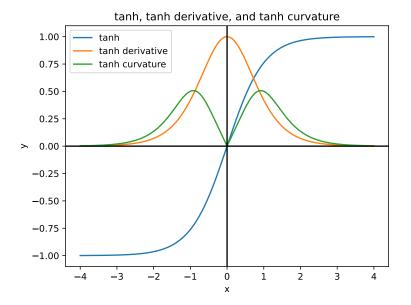

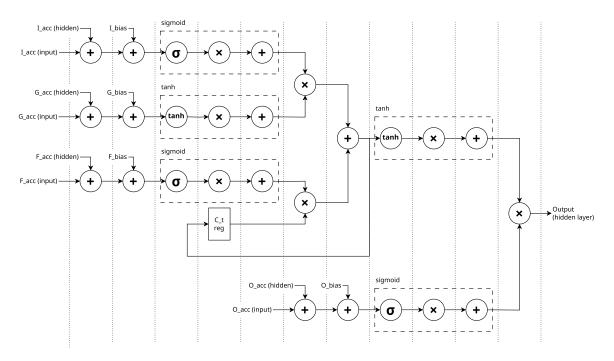

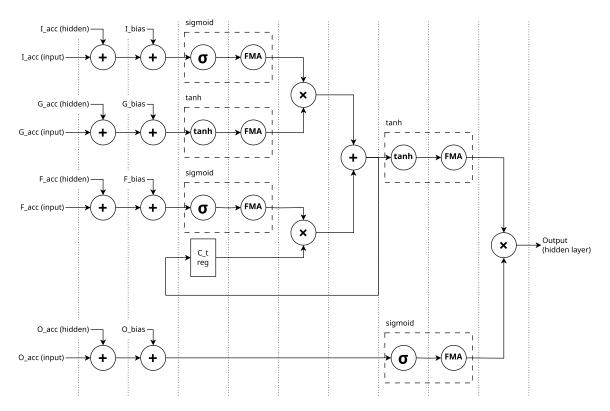

Long-term short-term memory (LSTM) is a variant of RNN that can overcome the vanishing gradient problem. Instead of an RNN only having short-term memory hidden layer  $(h_t)$ , LSTMs additionally add a long-term memory called cell state  $(c_t)$  to the neuron. The long term memory is used to store information over longer time steps. The hidden layer  $h_t$  and the cell state  $c_t$  are the recursive components of the LSTM meaning that at the next inference, they are reinserted into the LSTM cell; see Figure 4.1. The long-term memory is updated by a function of a forget gate  $f_t$  and an input gate  $i_t$ . The forget gate decides which information from the previous long-term memory should be ignored and which should be kept. The input gate combined with the cell input gate  $\tilde{c}_t$  determines which information from the cell state  $c_t$ . The hidden layer  $h_t$ , the short-term memory, is a function of the long-term memory. The cell input gate  $\tilde{c}_t$  is often denoted in code as  $g_t$  due to the tilde and confusion with the cell state  $c_t$ . The hidden layer  $h_t$ , the short-term memory, is a function of the long-term memory  $c_t$  and an output gate  $o_t$ . The output gate decides how much the short-term memory and input information should be outputted. LSTM uses both sigmoid and hyperbolic tangent activation functions [56].

The input  $x_t$ , hidden layer  $h_t$ , and cell state are vectors. The hidden layer and the cell state vectors have to be always equal in size and they parameterize the output size of the LSTM. The input vector can differ from the hidden layer and the cell state vectors denoting the input size. Whilst Figure 4.1 only shows the activation function  $\sigma$  or tanh, the gates' decision-making cannot only be performed by these functions as they are not parameterizable, meaning they cannot be altered and trained. Therefore, before the activation each gate performs an inner product between a weight vector stored in the gate and the input and hidden vector. After the inner product optionally a bias vector can be added to the product result [56].

Whilst the inputs of the cells are vectors, the cells themselves produce a scalar value. Therefore, there have to be as many cells equal to the output size of the LSTM to obtain the full output vectors. By combining all those cells together, the inner products of the gates of each cell combined can be modeled as a matrix-vector multiplication for each gate. The resulting gate equations can be seen in Equation 4.1 to 4.4, which shows that there are 8 matrix-vector multiplications; 4 multiplications between the input vector and input weights and 4 between the hidden vector and hidden weights. These weight matrices have dimensions of *hidden\_size × input\_size* and *hidden\_size × hidden\_size* for the input weights and hidden weights respectively. Subsequently, the gates use a hyperbolic tangent or a sigmoid (Equation 4.7) to bind the vector output of the matrix-vector multiplication to the interval

Figure 4.1: Visualization of an LSTM cell [57]

(-1, 1) and (0, 1) respectively. Equation 4.5 and 4.6 show the equations to get the final short-term memory  $h_t$  (output) and long-term memory  $c_t$ . These equations use Hadamard products  $(\bigcirc)$  which is an element-wise product between the gate vectors. This is because, in a cell after the gate operations, all operations are using local values of the cell therefore when combining multiple cells this results in a Hadamard product [56].

$$i_t = \sigma(W_{i \ input} x_t + W_{i \ hidden} h_{t-1} + b_i) \tag{4.1}$$

$$f_t = \sigma(W_{f\_input}x_t + W_{f\_hidden}h_{t-1} + b_f)$$

(4.2)

$$\tilde{c}_t = tanh(W_{\tilde{c}\_input}x_t + W_{\tilde{c}\_hidden}h_{t-1} + b_{\tilde{c}})$$

(4.3)

$$o_t = \sigma(W_{o\_input}x_t + W_{o\_hidden}h_{t-1} + b_o)$$

$$(4.4)$$

$$c_t = f_t \odot c_{t-1} + i_t \odot \tilde{c}_t \tag{4.5}$$

$$h_t = o_t \odot tanh(c_t) \tag{4.6}$$

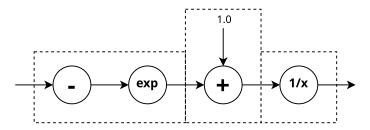

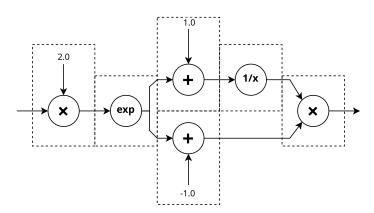

$$\sigma(x) = \frac{1}{1 + e^{-x}}$$

(4.7)

These equations above demonstrate well why this layer is significantly more compute-intensive compared to a convolutional layer. By analyzing the equations by counting atomic operations, where the activation functions are considered atomic but the matrix-vector multiplications are split into a multiplication and an addition, it is possible to see how intensive it is. The number of operations in a matrix-vector multiplication is n(2m-1), for the Bonito model the input size is equal to the hidden/output size, therefore, this simplifies to  $2n^2 - n$  where n is the layer size, scaling this up to 8 the matrix-vector multiplications this results in  $16n^2 - 8n$  cycles for the 8 matrix-vector multiplications. After that, there are per cell 4 bias additions, 5 activation functions, 3 multiplications (Hadamard product), and 1 addition; since these are per cell these operations are all equal to n resulting in 13n. Combining the results each inference has  $16n^2 + 5n$  operations, meaning that there are 16.9 million atomic operations for each inference in the Bonito super model where the layer size is 1024.

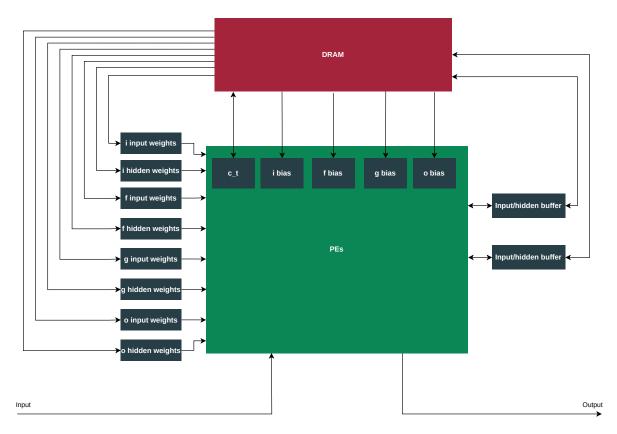

#### Memory requirements and FPGA selection

In terms of FPGA implementation, the most important thing to validate before implementing anything is if these weights, biases, etc. can be stored and accessed timely at all in FPGAs. As seen from the theoretical analysis of the LSTM layer, the memory requirements are quite demanding, especially for FPGAs where on-chip storage is scarce, of around 50MB on a high-end FPGA (*AMD Alveo U250*) [58]; compare that to a high-end CPU having 290MB (*AMD Ryzen Threadripper PRO 5995WX*) [59] and a high-end GPU having 70MB (*NVIDIA A100*) [60]. However, off-chip storage on FPGA is often plenty, but the bandwidth is in turn limited on the off-chip memory.

For an LSTM to function, there are ten different data stores required: an input data store, a hidden/output data store, and eight weight data stores for each gate. The hidden and input data sizes are equal since in the Bonito model the input and hidden vector dimensions are the same. Using the knowledge of the LSTM and Bonito, the memory requirements per LSTM layer can be calculated as seen in Table 4.1. The input/hidden storage size seems to be very high for a single vector input and output, as for a single 1024 vector the storage should only be 2KB. However, the table value is different as most often in neural networks the input is batched into multiple vectors making the input essentially a matrix. In Bonito, this batch is additionally split into chunks. This chunking is not a simple further subdivision of the reads from the sequencer, this is because, with the chunks, the neighboring chunks overlap partially with each other. Due to the lack of documentation on Bonito, the exact reason for this overlap is not clear. Bonito has for all its models specified a chunk size of 1.000 with an overlap of 50. This chunk size is used in Table 4.1 to determine the memory requirements of the input and hidden storage, the batch size would multiply this number even further however the batch size numbers lay above 100 which would move up the memory requirements over 100MB of on-chip memory which is practically impossible on an FPGA at the time of writing.

Table 4.1: Memory requirements of a Bonito LSTM layer (16 bits)

| Model       | Input/Hidden Size | Input & Hidden Storage (MB) | Weight Storage (MB) |

|-------------|-------------------|-----------------------------|---------------------|

| Super model | 1024              | 4.0                         | 16.8                |

| HAC model   | 384               | 1.5                         | 2.4                 |

| Fast Model  | 98                | 0.38                        | 0.15                |

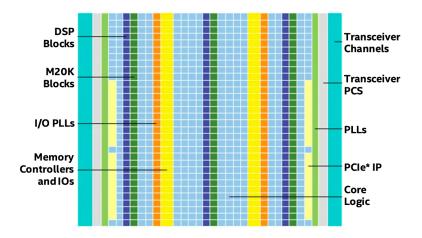

With the memory requirement available, selecting an FPGA to implement for is possible. After researching, it seems that there are two main FPGA contenders for the implementation, those being: the *AMD Alveo U280* and the *AMD VCK5000 Versal*. Table 4.2 shows the corresponding memory specification of these FPGAs. The reason for them being the main contenders is that the Alveo U280 is the FPGA with the most internal memory available at the *Quantum & Computer Engineering Cluster* at TU Delft while the Versal as mentioned before is available via the *Heterogeneous Accelerated Compute Clusters* at ETH Zürich which enables easier implementation of the other layers of Bonito for future work.

Table 4.2: Memory specification of the AMD Alveo U280 [61] and AMD VCK5000 Versal [53]

|                                | Alveo U280 | VCK5000 Versal |

|--------------------------------|------------|----------------|

| Internal SRAM (MB)             | 41         | 24             |

| Internal SRAM bandwidth (TB/s) | 30         | 24             |

| External DDR (GB)              | 32         | 16             |

| External DDR bandwidth (GB/s)  | 38         | 103            |

| External HBM (GB)              | 8          | N/A            |

| External HBM bandwidth (GB/s)  | 460        | N/A            |

Since the first target is to implement the Super model of Bonito, none of these FPGAs can internally store 5 layers of this model. However, with the Alveo U280, it is possible to deploy a double buffering scheme for the weight memories. This double buffering means that whilst one layer is calculated the next layer is loaded in, this prevents the calculations from stalling between layer calculations due to the weights fetching from DRAM. The Alveo additionally offers an HBM which is DRAM memory with a higher bandwidth which can help by loading the next layer weights during calculations faster. However,

due to the large chunk size, it is expected that the normal DDR memory is fast enough. For double buffering, there is only a need for  $2 \times 16.8 + 4 = 37.6MB$  of storage since the input and hidden/output storage can be flipped after each layer. Considering this, the choice for FPGA has fallen on the Alveo U280.

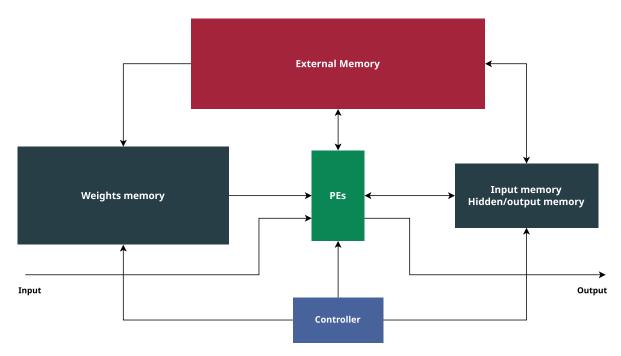

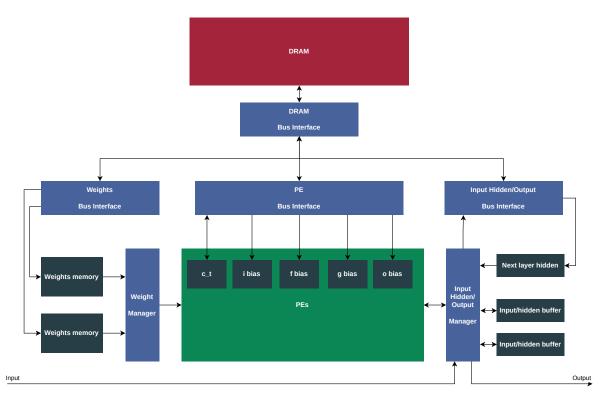

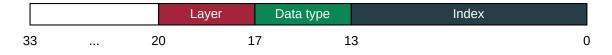

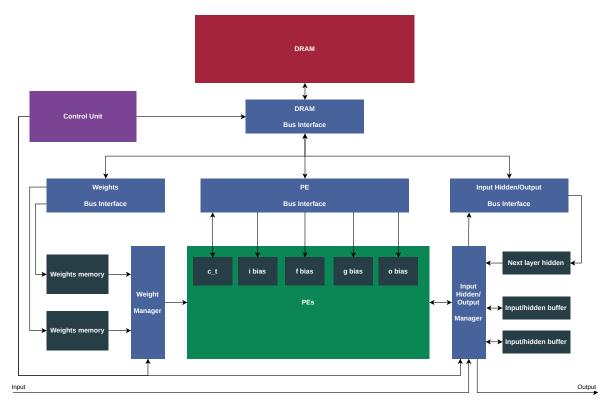

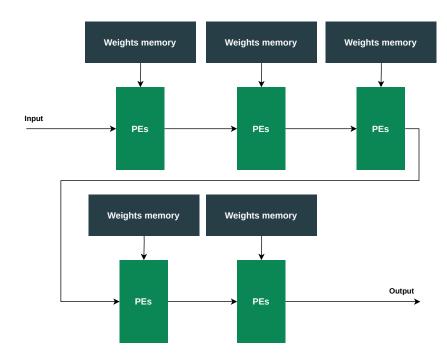

# 4.2. System architecture

Before starting an implementation, an initial abstract system architecture is laid out. An overview of this abstract architecture can be seen in Figure 4.2. This architecture is based on the implementation using a layer-for-layer approach; as mentioned in the memory requirement exploration, the only way to implement the Super model of bonito on the available FPGAs is by using a layer-for-layer approach. This layer-for-layer approach entails that for each subsequent layer, the weights have to be read from an external memory. However, an LSTM layer is additionally stateful, meaning that the calculations are dependent on a state determined from previous calculations. The state in the LSTM layer consists evidently of the long-term memory/cell state ( $c_t$ ) and short-term memory/hidden state ( $h_t$ ). This state calculations in the layers. Consequently, on a layer transition, the state of the new layer should be read from the external memory while the state of the finished layer should be written back to the external memory. Next to the weights being loaded in, the biases of the gates in the LSTM cells should additionally be loaded into cells from the external memory.

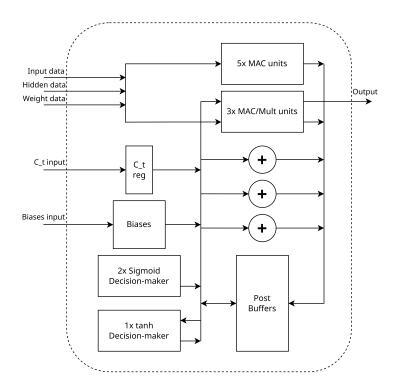

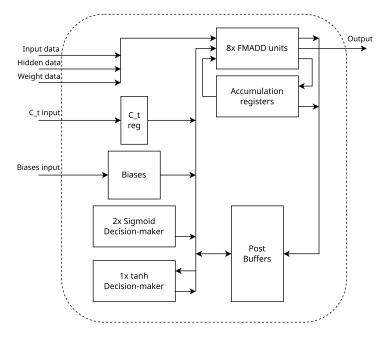

The following list abstractly outlines each component from the overview in Figure 4.2:

- **Processing Engines (PEs)**: The PEs are the computational units of the implementation each PE will be equivalent to an LSTM cell. The PEs additionally store the biases and the cell state.

- External memory: This is an off-chip memory, the memory type DDR or HBM memory will be decided upon later depending on the computational throughput of the implementation. The external memory will store all the accompanied data for each layer: the weights, the biases, and the layer state.

- Input/Output stream: These are not necessarily components but the input of the first LSTM layer

is streamed in from outside the FPGA and subsequently the output of the last layer is streamed

out of the FPGA. The streams are both possible input/output of the PEs.

- Input and hidden/output memory: This is on-chip memory, this memory consists of two memories an input memory and a hidden/output memory. An input vector from the input memory will be fed to the PEs and the output vector of the PEs will be written to the hidden/output memory, with exceptions in the first and last layer as mentioned before. Additionally to the input vector,

the last output vector will be reinserted into the PEs as a hidden vector, hence the name of the memory hidden/output memory. The input and hidden/output memory will not be a fixed memory but more a functionality applied to 2 memories. The reason being that the output of one layer is the input of another layer, this means that the hidden/output memory will function as an input layer in a subsequent layer and for the input memory vice versa.

• **Controller**: The controller is an over-arching component that enables synchronization between data transfers from the various memories, i.e. the weights input of the PEs should be synchronized with the corresponding input and hidden data put into the PEs. Moreover, it keeps track of when to switch between layers and commands the necessary components to retrieve the next layer data (weights, state, and biases) from the external memory while additionally managing that the state is written back to the external memory.

The architecture is designed from scratch as there is not a lot of literature on LSTM implementation on FPGA, and the ones that exist are of very small sizes. An architecture that exists that inspired this project's design a little bit is an LSTM implementation by H. Wang et al. [62], however, their architecture is different in a couple of aspects:

- 1. They only use a one-layer model therefore the entire switching out on layer transitions is not present.

- Their LSTM layer is a bi-directional layer meaning that the input data is analyzed from both directions in the layer. This is not present in the Bonito model, however, the computational approach can be applied to a uni-directional LSTM as the computational approach is the same in both directions.

Besides this, their implementation inspired the architecture on a computational level but everything is essentially designed from scratch.

# 4.3. Component design

This section examines how the previously outlined components in the system architecture are implemented. The design process of the implementation is split into three sections:

- **Processing engines** which discusses the core LSTM calculating units and how they can be mapped to the hardware available in the chosen FPGA.

- **Memory management** which discusses the arrangement of the internal memories and external memories and how they are those memories can be connected to each other.

- **Control and final architecture** which discusses the final ensemble of all the components together. Moreover, it outlines the design of the control units that link and synchronize the memory management and PEs together.

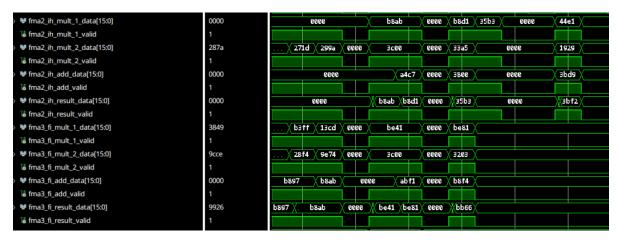

The FPGA implementation designed in this thesis is developed using the Xilinx Vivado toolchain, including simulations, synthesis, and implementation. All inter-component communication is designed using the AMBA AXI4 specification. AXI4 is used mainly due to it providing a consistent, fully specified, and popular component interface specification and additionally because all the IPs<sup>1</sup> of Xilinx in Vivado are designed using this component interface [63], thus allowing for easy communication between those IPs and self-made components. Moreover, the design process of each component has gone through the following list of design steps in nearly all cases:

- 1. Outlining design requirements of the component

- 2. Sketch on paper a basic architecture of the component

- 3. Implement the component in VHDL

- 4. Write a testbench in VHDL to test the validity of the component and check if it correctly interacts with other connected components by emulating those other components.

- 5. Synthesizing the component to obtain the resource consumption on the FPGA.

Naturally, these steps will be iterated over if redesigns are necessary due to possible excessive resource consumption. While additionally, these steps can be quite time-consuming as each little component has to be tested, it will result in much less work when finishing up the design in the end and ensuring the final validity of the design. Moreover, in VHDL testing a smaller design is orders of magnitude times faster than testing the whole design, so this will reduce the amount of test iterations of the complete final architecture.

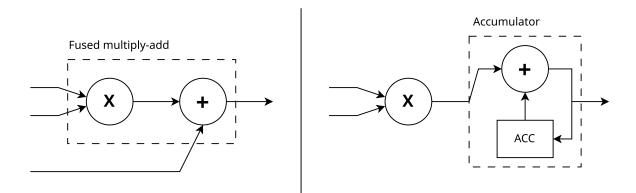

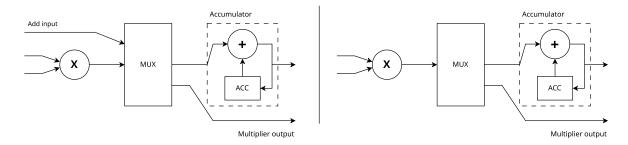

## 4.3.1. Processing engines

The processing engines are the core calculating part of the LSTM implementation. Processing engines (PEs) do not generally store the data to be processed but most often stream in data and subsequently stream out transformed output data, the exception being that the long-term memory is stored in the PEs, however, this is considered a state and not an output product. Before starting the implementation of the PEs, it is important to first take into consideration the data format to be used in the system architecture. After selecting a data format, there will be looked at ways of mapping the LSTM algorithm onto the selected FPGA given its constraints.

## Data format

The data format is a crucial design decision during FPGA development to try to obtain the right balance in resource consumption and accuracy. The Bonito model used a 32-bit floating-point, also called single precision, data format at the beginning of this thesis project. However, during the course of the thesis, this actually changed to using a 16-bit floating-point (half precision) data format. The arithmetic units of a GPU are mainly designed for floating point operations, while GPUs can perform integer operations this

<sup>&</sup>lt;sup>1</sup>IP stands for intellectual property, however in the context of Vivado it is better to interpret it primarily as a library component written by Xilinx (or any other company) that is additionally their intellectual property. In this thesis, it will mean a pre-made component of Xilinx unless stated otherwise.

is most often not at the same level of performance. Since there are very few restrictions on FPGAs, it is possible to utilize data formats other than floating-point, i.e. most predominantly fixed-point. In the fixed point format, as the name implies, the decimal point is fixed between an integer part and a decimal part, where both these parts have some amount of bits assigned to them. With a floating-point, the decimal point can float and consist of two parts: a fractional part and an exponent part which can be represented as *fraction*  $\times 2^{exponent}$ . Floating-point arithmetic has more accuracy as the representable range through the floating decimal point is much larger than that of fixed-point. However, the resulting hardware generated for floating-point arithmetic is often much larger than fixed point due to the following aspects:

- A floating-point operation often consists of multiple atomic arithmetic operations. For example in

a floating-point multiplication, the exponents have to be added while the fractional parts have to

be multiplied.

- Floating points have to be aligned. This can be in the case of an addition that the exponents

of the inputs should be aligned having to additionally shift the fractional part. Additionally, in the

output of a floating-point operation, the resulting fractional part has to be realigned so that the

most significant bit is equal to a 1.

- There might also be rounding circuitry. There are multiple rounding modes in floating-point, while

historically a truncation was applied resulting in no extra hardware, with the introduction of the

widely-used floating-point standard IEEE754 the default requires some rounding, however, there

is still the possibility for using different modes [64].

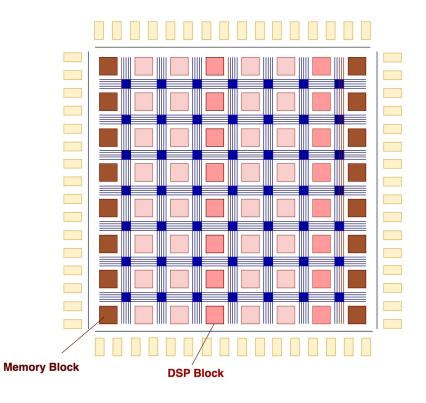

Conversely, in fixed-point arithmetic, these points are not present or less hardware-intensive [65]. Fixed-point addition and subtraction are equal algorithmically to integer addition and subtraction. Fixedpoint multiplication requires somewhat more hardware to perform multiplication, it can be done by doing integer multiplication however the output has to be scaled depending on the inputs. However, FPGAs, like the one used in this project, most often have dedicated hardware on-chip to perform fast arithmetic called digital signal processors (DSPs). These DSPs are fixed hardware blocks that cannot be reconfigured and are generally faster and more resource efficient than if one would design something themselves using reconfigurable resources. These DSPs can perform fixed point arithmetic using little or no additional supporting reconfigurable resources, while this is certainly not the case with floating point [66]. Therefore, it is most often encouraged that designers would first explore the possibility of using fixed-point compared to floating-point. Typically in applications that are mapped from CPU or GPU implementations to FPGA, the CPU or GPU implementations use floating-point as that is by far the most common way on those platforms to implement real numbers. However, there is a high possibility that those numbers do not even require the large range provided by floating point, making them have a small or no error when they are converted into a fixed point format. For this reason, the same will be explored about the data of Bonito to verify if a conversion to fixed-point is possible.

To verify if converting the data in the Bonito network from half precision to fixed point requires not only the weight data from the LSTMs of Bonito but also the input data requires verifying. Getting the weight data out of the model is not hard as these are already separately stored. The data to be analyzed is retrieved from Bonito's super model, however, it is assumed that these results will not differ extremely for the HAC and fast model. Before doing any conversion, the original data is analyzed to determine the range of the data, see Table 4.3. The first thing to notice from the statistics of the original data is that the data is signed, this means that one bit in the fixed-point data format has to be reserved for a sign indicating positive and negative numbers. Furthermore, it is apparent that 95% of the weight data is in the order of magnitude of  $10^{-1}$ , while the maximum or minimum value does not exceed the value of 5. Utilizing this knowledge, using a fixed point representation of 16-bits with one sign bit, 3-bits for the integer part to allow for the values exceeding 4, and the rest (12-bits) for the fractional part seems for an optimal fixed-point format; this format can also be denoted as s16/12 for signed, a total of 16bits, and a 12-bit fractional part. The process of analyzing this conversion is performed by loading in the data in Python and using a library to convert the data to a fixed-point format, in this case s16/12. Then convert it back and subtract the absolute value of the conversion from the original to obtain the absolute error, as seen in Table 4.4. The results of the conversion are promising as 25% of weights have no error after conversion, except for the input weights of layer 1.

Table 4.3: Statistics of the original Bonito weight data

|         |         | Original  |       |       |        | Absolute |                 |              |          |              |                |

|---------|---------|-----------|-------|-------|--------|----------|-----------------|--------------|----------|--------------|----------------|

|         | Weights | Mean      | SD    | Max   | Min    | Mean     | 95th percentile | 3rd quartile | median   | 1st quartile | 5th percentile |

| Layer 0 | input   | -1.16E-03 | 0.093 | 1.555 | -2.240 | 6.81E-02 | 1.76E-01        | 9.42E-02     | 5.32E-02 | 2.45E-02     | 4.76E-03       |

|         | hidden  | -6.82E-04 | 0.148 | 3.109 | -2.453 | 1.09E-01 | 3.03E-01        | 1.50E-01     | 8.09E-02 | 3.67E-02     | 4.76E-03       |

| Layer 1 | input   | -3.61E-04 | 0.129 | 2.818 | -2.607 | 9.32E-02 | 2.61E-01        | 1.27E-01     | 6.90E-02 | 3.13E-02     | 6.06E-03       |

|         | hidden  | -1.36E-04 | 0.157 | 3.287 | -2.785 | 1.15E-01 | 3.18E-01        | 1.59E-01     | 8.68E-02 | 3.95E-02     | 6.06E-03       |

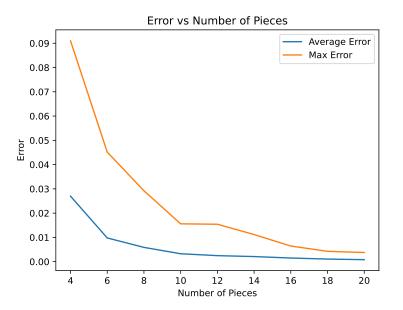

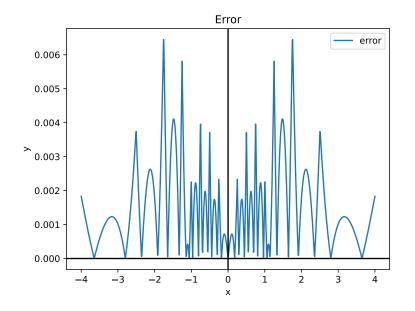

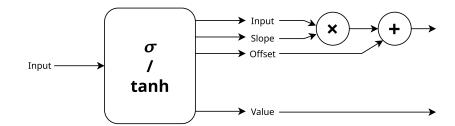

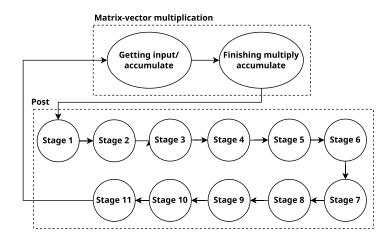

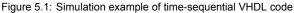

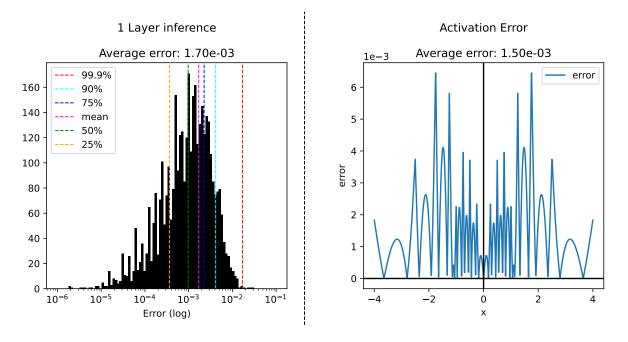

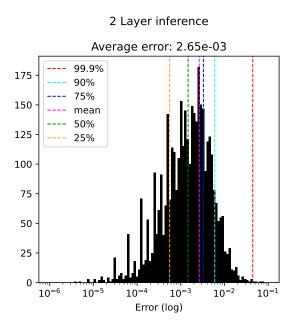

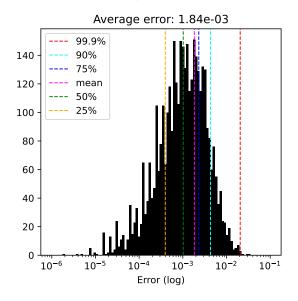

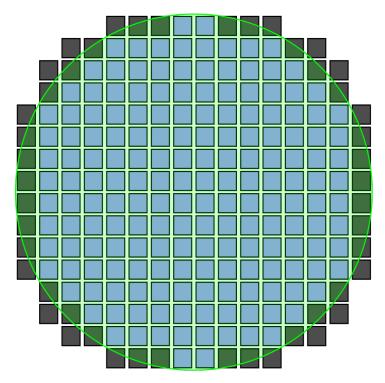

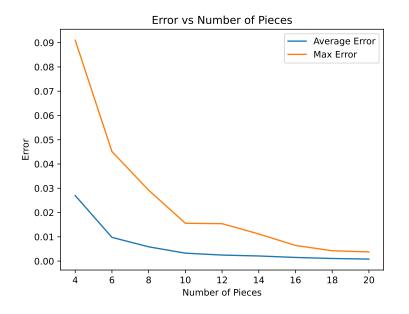

| Layer 2 | input   | 2.33E-04  | 0.125 | 4.859 | -2.973 | 9.01E-02 | 2.50E-01        | 1.23E-01     | 6.70E-02 | 3.06E-02     | 5.94E-03       |