High efficiency IBC solar cells with poly-Si implanted passivating contacts

Mohamad Hannan TU-Delft

# HIGH EFFICIENCY IBC SOLAR CELLS WITH POLY-SI IMPLANTED PASSIVATING CONTACTS

Ву

#### Mohamad Hannan

in partial fulfilment of the requirements for the degree of

#### **Master of Science**

at the Delft University of Technology,

to be defended publicly on Friday May 21st, 2021

Supervisor: Asso. Prof. dr. Olindo Isabella

Dr. Guangtao Yang

Thesis committee: Assoc. Prof. dr. Olindo Isabella, TU Delft (ESE-PVMD)

Prof.Dr Evan Gordon, TU Delft-EWI-ESE

Dr. Sten Vollebregt, TU Delft (ECTM)

Dr. Guangtao Yang, TU Delft (ESE,PVMD)

# Acknowledgement

First, I would like to thanks my parents: My mother Fatima you are the best! My father Ahmad you are always proud of me. My dear wife you support and motivate me in this hard period of my life, love you so much, and of course you also my lovely daughter ^\_^, without you I would have graduated earlier but you fill my life with love and hope! My family members, thanks a lot for all the kind messages and call. I want to thanks my friends who always here to offer their support. The kind-hearted people who make life more beautiful and peaceful.

I also want to show my appreciation to my supervisor Professor Olindo Isabella for giving me a chance to do my master thesis at the TU Delft PVMD group. Thanks for motivating us and be caring, and supportive. I want to express my gratitude to my daily supervisor, Dr. G Yang, I really appreciate your effort and help throughout my thesis. You are always patient, calm, and willing to help.

I would like to thanks the Netherlands! For making me feel safe and welcome after fleeing from Syria, for enabling me to pursue my education in such a prestigious university like TU-Delft, thanks for a lot of things! I will be forever grateful. I would like to thanks people who would never read this scientific report. You are in my heart and mind!

Mohamad Hannan

Amsterdam, May 2021

# **Abstract**

Crystalline silicon (c-Si) interdigitated back contacted (IBC) solar cell with poly-Si passivating contacts is one of the most promising approaches to achieve high conversion efficiency solar cells. The fabrication of IBC silicon-based solar cells provided by poly-Si passivating contacts is investigated in this thesis.

The passivating poly-Si contacts structure used in this work is based on an ultra-thin layer of t-SiO<sub>X</sub> with optimized poly-Si thicknesses of 250 nm and the implantation parameters of Phosphorous and Boron doping with 6e15 and 5e15 ions/cm² respectively, at a fixed implantation energy of 20 keV. The influence of the post-implantation annealing conditions is discussed with experimental results, obtained on symmetrical test structures with thermal SiOx/doped poly-Si on each side. The best-obtained passivation result for  $n^+$ -poly-Si contact was 728 mV at annealing conditions of 1050°C for 1 minute, while for the  $p^+$  poly-Si contact at the same annealing conditions 699 mV is obtained. To enhance the passivation, PECVD deposited SiN<sub>X</sub> capping layer and annealing in forming gas as hydrogenation processes are carried out. Then, FBC solar cells are fabricated to evaluate the electrical performances, in terms of passivation and carrier transport, of the poly-Si contacts structures, which are prepared with different annealing conditions, in terms of temperature and time. The results obtained from the FBC cells show that increasing the annealing temperature leads to an increase in the passivation thus the  $V_{OC}$ . The best-obtained  $V_{OC}$  was 706mV for the wafer annealed at 1050°C for 1 minute.

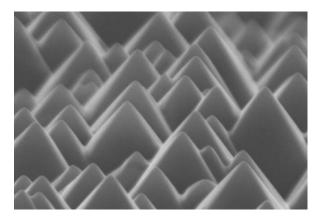

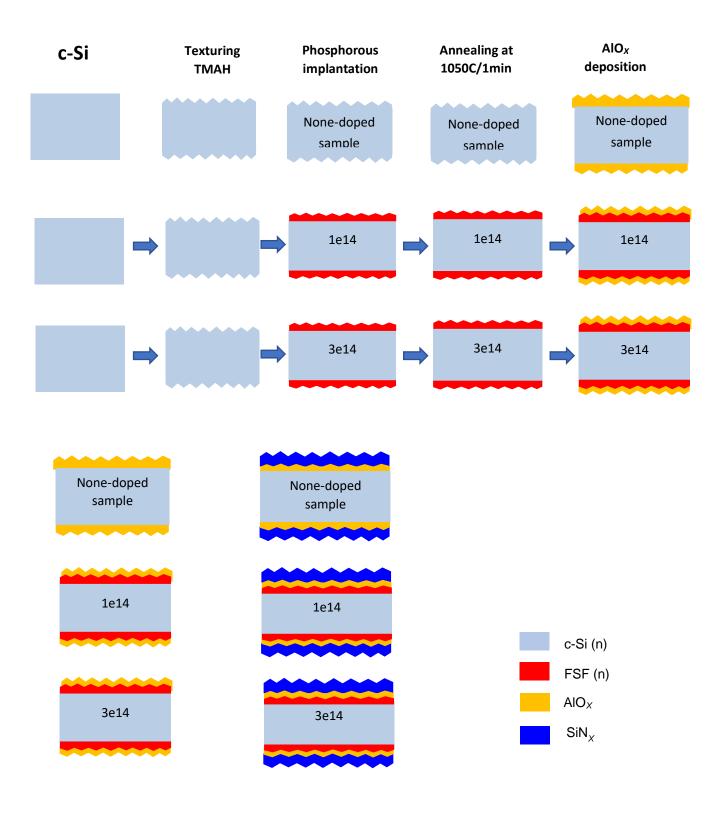

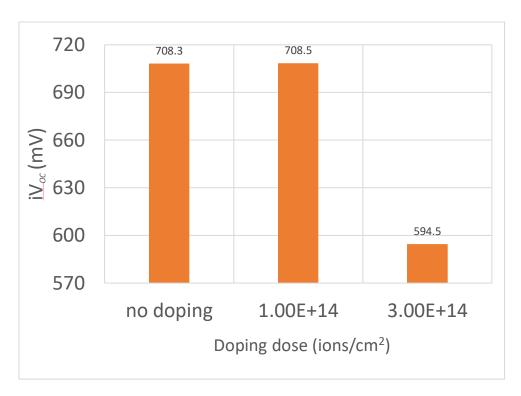

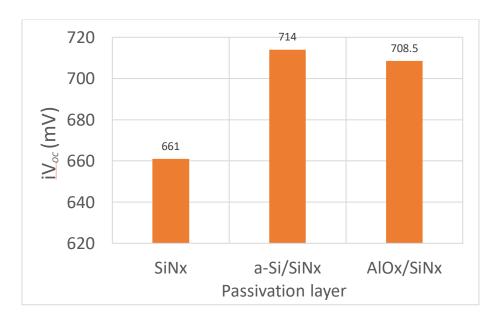

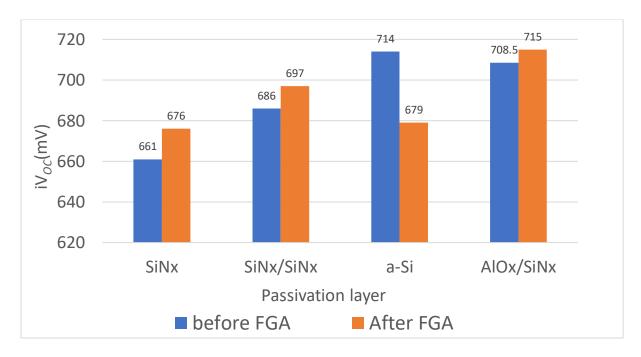

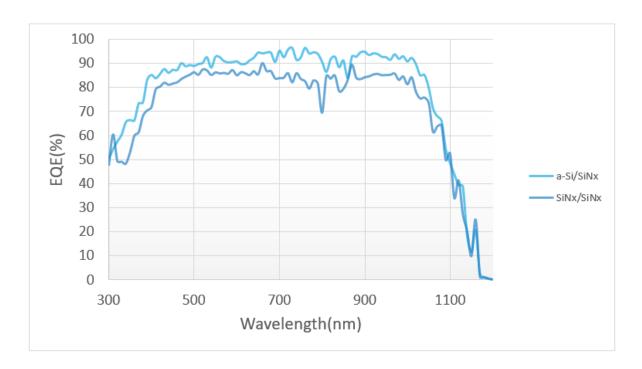

To enhance the optical properties of the IBC cells, the surface is textured and the influence of doping dose on passivation of the front surface field (FSF) is evaluated. Four different passivation stack layers  $SiN_X$ ,  $AlO_X/SiN_X$ , a-Si/SiN\_X, and double  $SiN_Y$  /SiN\_X are evaluated for FSF implanted with dose of 1e14 ions/cm². The best-obtained passivation result is from FSF sample passivated with a-Si/SiN\_X It shows excellent passivation property with  $iV_{OC}$  of 714 mV and a  $J_O$  of 7.5 fA/cm². while the other stacks show lower passivation of  $iV_{OC}$  708 mV for the  $AlO_X/SiN_X$  sample and  $iV_{OC}$  686 mV for the  $SiN_Y$  /SiN\_X sample. The influence of FGA on the FSF passivation quality is also evaluated. The results show that the sample passivated with a-Si/SiN\_X experienced a sharp decrease of 35 mV in the  $iV_{OC}$  after FGA due to the low thermal stability of the a-Si:H. On the other hand, other FSF samples with passivation stacks of  $SiN_X$ ,  $AlO_X/SiN_X$ , and  $SiN_X/SiN_X$  show a positive influence upon the FGA on their passivation quality as a result of the extra hydrogen diffusion during the FGA which saturates more defects on the c-Si surface.

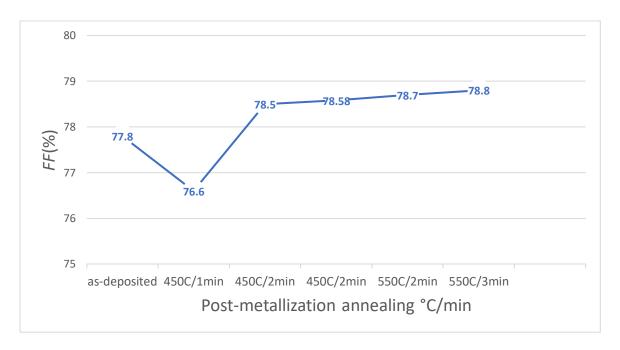

The implantation of the optimized thermal SiOx/ doped poly-Si structure and FSF with a-Si/SiN $_X$  passivating layer into the IBC solar cells leads to high-efficiency IBC solar cells. The record cell has a conversion efficiency of 21.04% and 22.15% after the post metallization annealing,  $V_{oc}$  of 681 mV, and FF of 78,9 with  $J_{sc}$  of 37.5 mA/cm<sup>2</sup>

# **CONTENTS**

| 4 | bstract                                                         | iv   |

|---|-----------------------------------------------------------------|------|

| L | Introduction                                                    | 1    |

|   | 1.1The working principle of solar cells                         |      |

|   | 1.2 Solar cell parameters                                       | 4    |

|   | 1.3 Loss mechanisms                                             | 6    |

|   | 1.3.1 Optical losses                                            | 6    |

|   | 1.3.2 Electrical losses                                         | 7    |

|   | 1.4 Surface passivation                                         | 8    |

|   | 1.5 Advanced design concepts in IBC solar cells                 | 9    |

|   | 1.5.1 Minimizing the optical losses                             | 10   |

|   | 1.5.2 Minimizing the electrical losses                          | 10   |

|   | 1.6 Thesis objectives                                           | . 11 |

|   | 1.7 Thesis outline                                              | . 11 |

| 2 | Experimental methods                                            | . 13 |

| 3 | Carrier selective passivating contacts                          | . 29 |

|   | 3.1 The passivation quality of poly-Si CSPC - a short review    | 19   |

|   | 3.1.1Chemicapassivation                                         | 20   |

|   | 3.1.2 Electric-field passivation                                | . 20 |

|   | 3.2 Experimental details                                        | . 23 |

|   | 3.3 the influence of annealing on the passivation quality       | . 25 |

|   | 3.4 The influence of hydrogenation on the passivation           | . 26 |

|   | 3.4.1 Hydrogenation tests results                               | . 28 |

|   | 3.5 Contact resistivity                                         | . 30 |

|   | 3.5.1 Transfer Length Measurement (TLM) and samples preparation | . 30 |

|   | 3.6 Summary                                                     | . 32 |

| 4 Front back contacted solar cells                                           | 35 |

|------------------------------------------------------------------------------|----|

| 4.1 Experimental details                                                     | 35 |

| 4.2 Cells' precursor performances                                            | 37 |

| 4.3 Suns-V <sub>oc</sub> measurement                                         | 37 |

| 4.4 I-V measurement                                                          | 39 |

| 4.5 Post-metallization annealing effect                                      | 43 |

| 4.6 Conclusion                                                               | 44 |

| 5 IBC solar cells: Front side optimization                                   | 47 |

| 5.1 The importance of engineering the front side of the IBC cell             | 47 |

| 5.2 Sheet resistance                                                         | 48 |

| 5.1 The importance of engineering the front side of the IBC cell             | 47 |

| 5.2 Sheet resistance                                                         | 48 |

| 5.3 Front surface field Passivation                                          | 50 |

| 5.3.1 evaluating the effect of doping dose on the FSF passivation            | 51 |

| 5.3.2 Different passivating layers                                           | 53 |

| 5.3.3 The effect of FGA on the front surface passivation                     | 56 |

| 5.4 Conclusion                                                               | 57 |

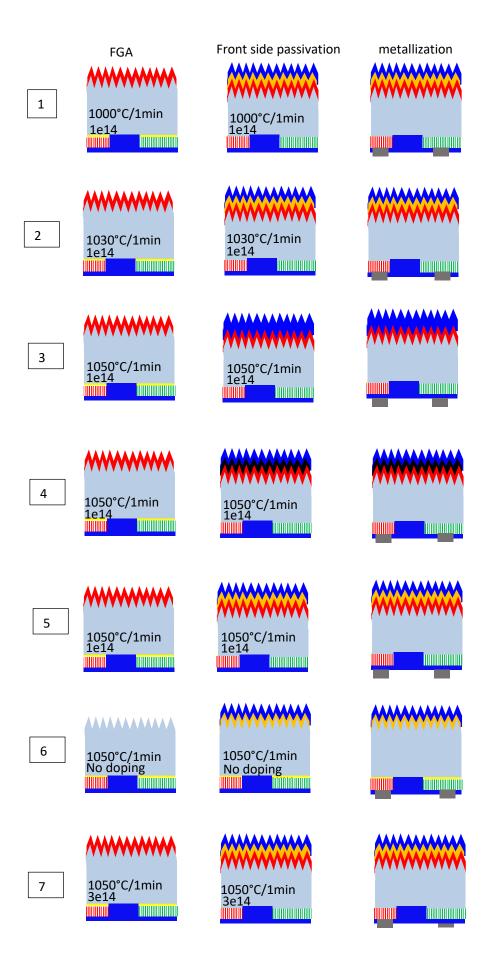

| 6 IBC solar cells: Fabrications and results                                  | 60 |

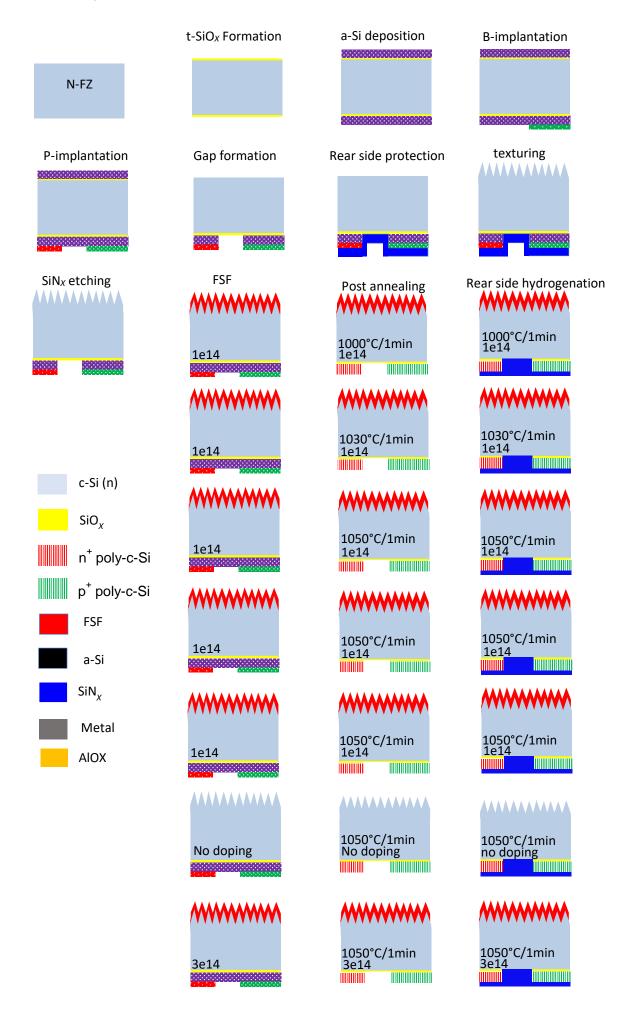

| 6.1 The flowchart for fabricating IBC solar cells                            | 60 |

| 6.2 Results and discussion                                                   | 66 |

| 6.3 The influence of the annealing temperature on the cells' performance     | 66 |

| 6.4 The influence of the surface passivating layer on the cells' performance | 48 |

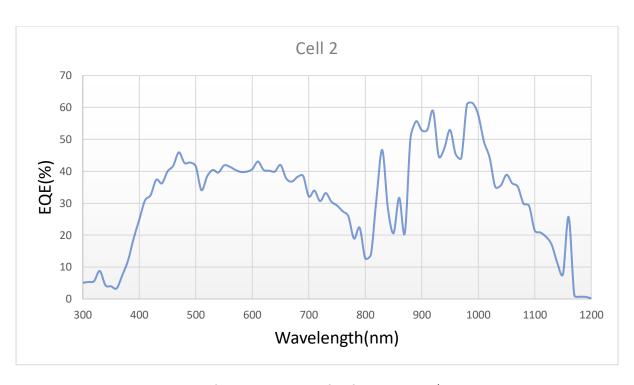

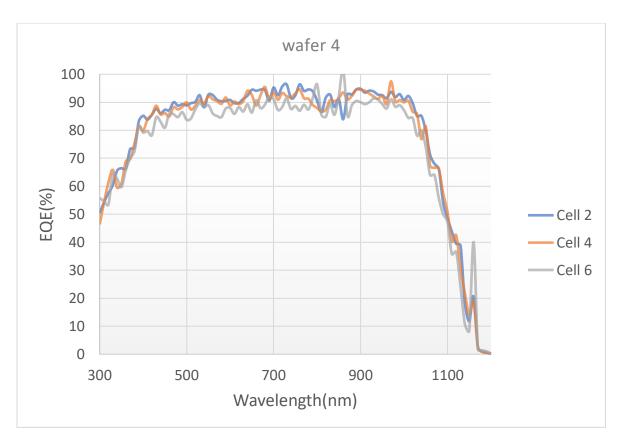

| 6.5 The optical performance of IBC solar cells                               | 69 |

| 6.6 The influence of FSF on the performance of the cells                     | 72 |

| 6.7 Post metallization annealing                                             | 73 |

| 6.8 Conclusion                                                               | 75 |

| 7 Conclusions and outlook                                                    | 78 |

| 7.1 Conclusions                                                              | 78 |

| 7.2 Outlook                                                                  | 79 |

| Bibliography                                                                 | 82 |

# Nomenclature

Poly-SiO<sub>X</sub> Oxygen Alloyed Polycrystalline Silicon

Poly-Si Polycrystalline Silicon

τeff Minority Carrier Lifetime

Eg Bandgap

η Conversion efficiency

EC Conduction Band

$\rho_{C}$  Specific Contact resistance

EV Valance Band

a-Si Amorphous Silicon

FBC Front and Back Contacted

Ag Silver

FF Fill Factor

Al Aluminum

FG Forming Gas

ALD Atomic Layer Deposition

FZ Float Zone

ARC Anti-reflection Coating

HF Hydrofluoric Acid

B Boron

HNO<sub>3</sub> Nitric Acid

BHF Buffer Hydrofluoric Acid

iV<sub>OC</sub> Implied open-circuit voltage

c-Si Crystalline Silicon

IBC Interdigitated Back Contact

CSPC Carrier Selective Passivating Contacts

ITO Indium Tin Oxide

TMAH Tetramethylammonium Hydroxide

J<sub>0</sub> Recombination Current Density

VOC Open-Circuit Voltage

JSC Short-circuit Current density

PECVD Plasma Enhanced Chemical Layer Deposition

LPCVD Low Pressure Chemical Vapor Deposition

PV Photovoltaics

NAOS Nitric Acid Oxidation of Silicon

Rs Series Resistance

N<sub>2</sub> Nitrogen

Rshunt Shunt Resistance

O<sub>2</sub> Oxygen

Cu Copper

P Phosphorous

ITO Indium Tin Oxide

SEM Scanning Electron Microscopy

J<sub>0</sub> Recombination Current Density

SRH Shockley-Read-Hall

JSC Short-circuit Current density

STC Standard Test Conditions

SiH4 Silane

SiN<sub>X</sub> Silicon Nitride

TCO Transparent Conducting Oxide

# INTRODUCTION

Plants satisfied their energy needs by Photosynthesis with sunshine and we live in an era where humankind seeks to satisfy their growing demands of energy by the sun as well which has been forever providing the planet with free light, warmth, and even life.

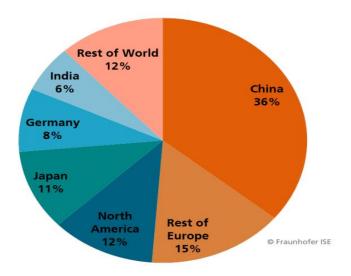

Nevertheless, 13% of the world population do not have access to electricity according to The International Energy Agency in 2016, IEA still expects the energy consumption to rise 50% in 2050 compared to the energy consumption level in 2019 where this growth is driven by the main industrial Asian countries like China and, Taiwan [2], thus, providing clean energy that fulfills the growing energy demand is crucial nowadays to stop the climate change which is directly related to the excessive use of the conventional energy source like Coal, Oil, and gas. IEA claimed a considerable drop of 7% in global CO2 as a consequence of the lockdown and measurement associated with the Covid-19 pandemic [1], where the United Nations Climate Change Conference that is held in Paris need to reach a Zero green gas emission in 2050 to meet their goal of keeping the temperature of the globe "well below 2°C above preindustrial levels and pursuing efforts to limit the temperature increase to 1.5°C above pre-industrial levels". Therefore, Solar energy comes in the center of the renewable energy sources to achieve the required shift to clean energy resources and meet the rapid energy demand. Due to the sharp decrease in the electricity generated by solar PV power plants where the LCOE reaches a record of 3.7ct€ / kWh, consistent rapid growth is witnessed in the cumulative PV installation globally to reach 584 GWP at the end of 2019[3]. China still leading the world in the solar market in both PV module production and PV plant installation with 36% of the PV global installed capacity.

Figure 1.1: The percentage of PV modules installed capacity per region [3].

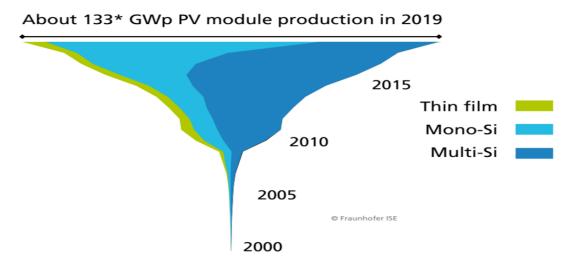

As the solar industry is still scaling up it is associated with a decrease in the production cost of PV modules. The thin-film PV modules still have a low share in the market while the Mono-crystalline Si PV modules gain more share in the market with 65% to become the largest technology even though multi-crystalline PV modules rolled the solar market in the beginning. The main advantages of solar energy are based on the properties of Silicon material since Silicon is abundant, non-toxic, durable, and shows very good performance stability in the long term. Because of the domination of silicon-based solar cells in the market, it still gains attention in research to enhance its conversion efficiency. The lab record mono-crystallin Si-based solar cell shows efficiency of 26.7% while its multi-crystalline counterpart shows a conversion efficiency of 22.3% [3]. The gradual increase in the conversion efficiency is attributed to the improvement in the material used to fabricate the cells and the new approaches that are used to quench the recombination losses in the cell besides the advanced design of the optical properties [4].

Figure 1.2: The annual PV production by technology [3].

# 1.1The working principle of solar cells

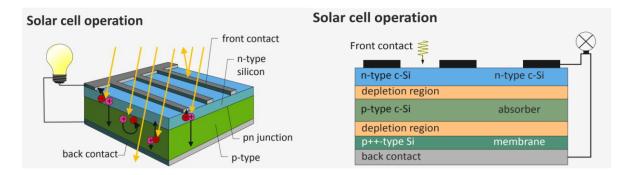

Basically, a solar cell is a device that generates useful electrical energy when it is exposed to a light source. What is called a photovoltaic effect is the cornerstone notion of this energy conversion where electromagnetic radiation is directly converted into electricity. In the following, it is explained how electricity is generated in a simple PN junction.

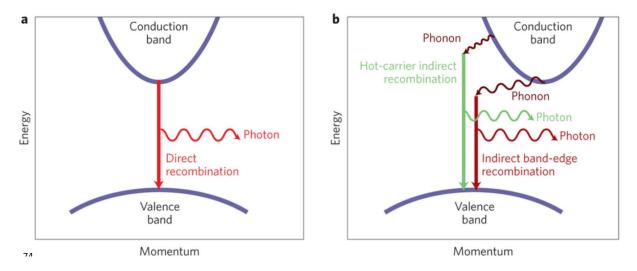

Generation of mobile charge carriers occurs in the absorption layer when it is illuminated by a light source. The photons' energy should be greater than the energy of the semiconductor's bandgap to excite an electron-hole pair from the conduction band. In an indirect bandgap semiconductor like silicon, momentum should be provided additionally to enable this generation.

Figure 1.3: A simplified representation of a silicon-based solar cell [5].

Figure 1.4: Illustration of the difference between (a) a direct bandgap semiconductor, and (b) an indirect bandgap semiconductor [6].

Separation of the free electron-hole pairs generated is crucial to make use of the absorbed energy, otherwise, these generated mobile charge carriers will recombine again and annihilate. The separation process is done by diffusion and drift current forming the transport mechanism over the depletion region in the P-N junction. After that, a collection process is required to build a useful electric current through an external circuit. A load is connected to the metal contacts of the solar cell where the collected electrons pass through one of the metal contacts to the external load and recombine with a hole at the other electrode.

## 1.2 Solar cell parameters

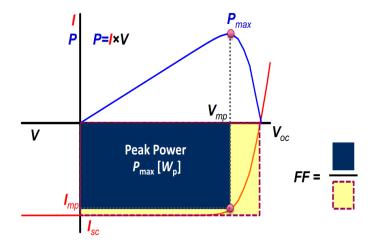

In order to define the performance of a solar cell, various properties of the cell have to be measured and characterized. The most important parameters are extracted from the JV-curve of an illuminated cell under standard test conditions which will be well defined in this section.

**Standard test conditions:** Researchers and manufacturers rate the output power and other parameters of a solar cell or a solar module at standard test conditions as following, cells temperature should be at 25  $^{\circ}$ C with no wind, while the light source simulator has to resemble a spectral shape similar to the AM1.5 air math spectrum and a total irradiance of 1000 W/m2.

**Conversion efficiency:** The conversion efficiency is the ratio between the output electric energy and the energy of incident light under standard test conditions which can be calculated by equation 1.1.

$$\eta = \frac{P_{max}}{P_{in}} = \frac{J_{sc}.V_{oc}.FF}{P_{in}}$$

1.1

Open circuit voltage ( $V_{oc}$ ): The open-circuit voltage ( $V_{oc}$ ) represents the maximum voltage a solar cell can generate since it is measured in the absence of the current flow through the cell and is given by equation 1.2

$$V_{OC} = \frac{k_B}{q} \ln \frac{J_{ph}}{J_0} + 1$$

1.2

Where  $(J_{PH})$  is the photogenerated current density,  $(J_0)$  is the saturation current density, and (q) is the elementary charge. The equation shows that higher irradiance increases the photogenerated current density  $(J_{PH})$  which leads to higher open-circuit voltage, while higher temperature causes a larger leakage current  $(J_0)$  thus lower  $(V_{OC})$ . The dark saturation current  $(J_0)$  is related as well to the recombination rate in the cell therefore, the open-circuit voltage is a key factor to determine the passivation quality of the cell.

-Short circuit current ( $I_{SC}$ ): The Short circuit current is measured at zero voltage; consequently, it is the maximum current that a solar cell can deliver. Generally, the short current density ( $I_{SC}$ ) is used instead

of the short circuit current ( $I_{SC}$ ) as it includes the unit area cm2 in its value. It is important to notice that photogenerated current ( $I_{PH}$ ) is equal to the short circuit current in ideal conditions, hence the optical properties of the solar cell such as absorption and reflection strongly affect the values of the photogenerated current and the short circuit current respectively.

Figure 1.5: Illustration of IV curve of an illuminated solar cell.

**Fill factor (FF):** The fill factor represents the rate between the maximum output power calculated at short circuit conditions and the maximum power measured at the operation point. See figure 1.2

Equation 1.1 shows that a higher fill factor causes higher conversion efficiency, as a result, it is commonly used to compare solar cells performance. To obtain a high fill factor, series resistance Rs should be minimized which consists of the silicon bulk resistance, the resistance of the metallic electrodes and, the resistance between the semiconductor and the metal. On the other hand, low shunt resistance deteriorates the value of the fill factor, which can be a result of a poor-quality wafer or a leakage current across the junction.

**External Quantum efficiency (EQE):** The external quantum efficiency is essential to analyze the optical properties of a solar cell and, determine the parasitic absorption. It represents the ratio between the number of collected charge carriers in the device to the number of the incident photons as shown in equation 1.3.

$$EQE = \frac{Electrons/sec}{Photons/sec} = \frac{I_{ph}(\lambda)}{e\Phi_{ph}(\lambda)}$$

1.3

Determining the external quantum efficiency under short circuit conditions is a common way to calculate accurately the short circuit current density (JSC).

### 1.3 Loss mechanisms:

Understanding the loss sources in solar cells enables us to design advanced solar cells and maximize the conversion efficiency of the device. The loss sources in solar cells can be categorized into optical and electrical losses.

# 1.3.1 Optical losses:

Optical losses can be divided into two main categories, spectral mismatch, and additional losses. The spectral mismatch is considered the main reason behind the efficiency limitation of a solar cell. This mismatch between the energy of incident photons and the bandgap energy of the semiconductor appears in two cases. The first one is when the photons have lower energy than the semiconductor bandgap, therefore, these photons cannot be utilized to excite electrons from the valence band to the conduction band. On the other hand, when these photons have higher energy than the material bandgap Eg, electron-hole pairs will be promoted but the rest of the photon's energy will be lost in a thermalization process as heat.

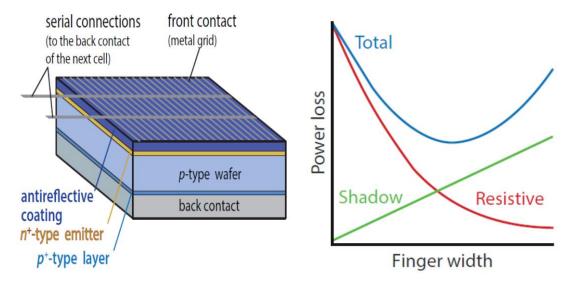

Figuer1.6 (left) illustration of the metal grid in FBC solar cells. (Right) finding the optimum width of the metallic fingers.

The additional optical losses are attributed to shading, reflection, and parasitic absorption. A precise design is required to form the metallic grid of the solar cell contacts to achieve minimal shading and low electric resistance, see figure 1.4. Commercial solar cells include an antireflective coating to reduce the loss due to reflection, while advanced solar cells adopt novel approaches such as surface texturing and light management engineering to define the optimum parameters of the device's layers such as thickness and reflective index to minimize the reflection and the parasitic losses.

#### 1.3.2 Electrical losses:

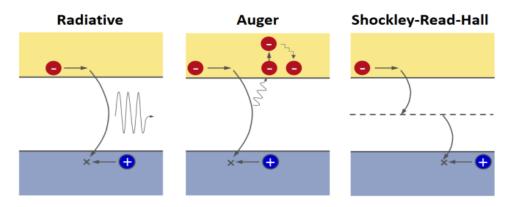

The failure to collect the generated charge carriers within the absorber layer leads to electrical loss which is mainly attributed to the recombination mechanisms in semiconductor materials. These mechanisms are surface recombination, radiative recombination, Shockley Read Hall (SRH) recombination, and Auger recombination.

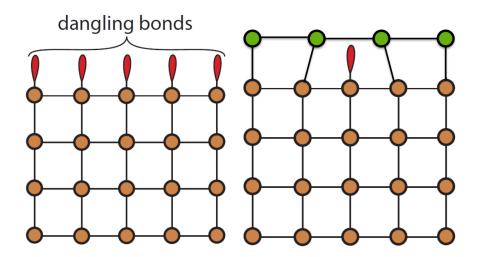

Surface recombination is a major concern of researchers to increase the conversion efficiency of solar cells as it causes a significant drop in solar cell passivation. Surface recombination is based mainly on the dangling bond at the surface of the semiconductor which can be considered as localized defects that may trap a free charge carrier.

Figure 1.7 Illustration diagram of the recombination types [6].

Radiative recombination occurs when a recombined electron-hole emits a photon after an electron returns to its valance band, therefore, it can be seen as an opposite to the generation process. This type of recombination is rare in an indirect bandgap semiconductor material like silicon thus, it can be neglected in silicon-based solar cells.

Auger recombination is a three-particle process since the momentum and energy of a recombined electron-hole pair moves to a third particle which can be an electron or hole. Auger recombination is dominant in an indirect semiconductor material and it strongly depends on the charge carrier density; hence it becomes more important at high doping level.

Shockley Read Hall (SRH) recombination is facilitated by defects in the silicon bulks or impurity atoms which introduce trap-states within the forbidden gap and facilitate the recombination process. The recent technologies used in silicon production result in high-quality silicon wafers with low bulk defects. The defects formed at the grain boundary of polycrystalline silicon are the main reason for the low efficiency compared to the mono-crystallin silicon solar cells since they induce a higher rate of SRH recombination.

# 1.4 Surface passivation:

Silicon-based solar cells suffer strongly from surface recombination as mentioned in section 1.4. therefore, researchers have developed two techniques to overcome this problem and minimize this loss. The first technique used is chemical passivation where a thin layer of a suitable material is deposited on the surface of a silicon wafer, see figure 1.6. The dangling bonds at the surface form covalent bonds with the atoms of the passivating material deposited, thus decrease the defect density and reduce the likelihood of the surface recombination. Material like silicon oxide, a-Si, and Aluminum oxide show excellent passivation results and will be discussed extensively in chapter 5 [7].

Figure 1.8 (a) Dangling bonds at the silicon surface. (b) covalent bonds after passivation.

Field-effect passivation is another used technique to reduce the loss caused by surface recombination. Introducing a heavily doped layer at the contact surface is a common practice to initiate an electric field that repels the minority charge carriers while allows the majority charge carriers generated to pass through.

Figure 1.9: Sketch of a front selective emitter and its band diagram.

For example, in a p-type silicon wafer the generated holes nearby the emitter will recombine instantaneously with electrons at the metal interface thus, the recombination rate will be extremely high at the surface. Introducing a high concentration of phosphorus just under the contacts initiates a field effect that repels holes and allows only electrons to pass to the emitter, see figure 1.9. The same trick is used at the back contact to enhance the selectivity and reduce the recombination rate. This approach is applicable in interdigitated back contact solar cells, since their contacts in the backside, while a more complicated approach is required in front/back contacted solar cells to avoid Auger recombination caused by the high doping level nearby the surface.

# 1.5 Advanced design concepts in IBC solar cells:

Light management engineering and developing new solar cell structures led to a significant increase in the conversion efficiency of up to 26 % of silicon-based solar cells [8]. This efficiency increase is based on decreasing the optical and the electrical losses in the cell as will be explained in this section.

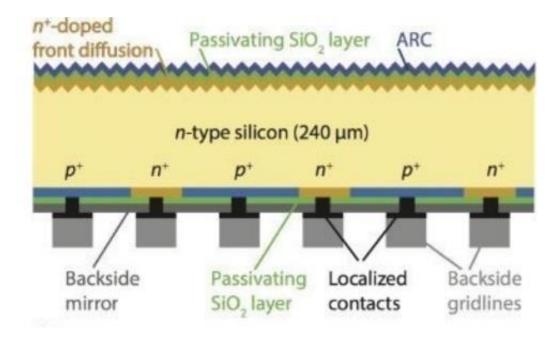

Figure 1.10: Sketch diagram of an IBC solar cell with carrier selective contacts [6].

# 1.5.1 Minimizing the optical losses:

The main visual difference between conventional solar cells and interdigitated back contact solar cells (IBC) is moving the metal contacts grid to the backside of the module. Depositing the metal contacts at the backside is costly because it increases and complicates the production steps but it has valuable advantages such as decrease the shading, allowing thicker contacts which reduce contact resistivity and eliminate Auger recombination.

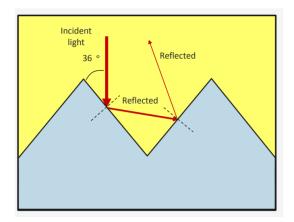

To enhance light absorption in the bulk, the surface is textured by a chemical etching process, and an anti-reflective coating layer is deposited on the surface. Usually, a silicon nitride layer is used as an anti-reflective coating with a thickness range from 50 to 100 nm. This layer is behind the common blue color of solar cells, and it is deposited through Plasma-enhanced chemical vapor deposition (PECVD) process at a certain temperature, and gas flow to achieve well-defined optical properties such as thickness, density, and refractive index.

# 1.5.2 Minimizing the electrical losses:

Beginning with the ohmic loss, contact resistivity plays a significant role in the series resistance of the solar cell and the Fill factor as a consequence. To reduce this resistance thicker metallic contacts are used without taking the shading effect into consideration since the contacts are in the backside in IBC solar cells. Aluminum is widely used in the mass production of solar cells thanks to price, whereas silver and copper have better conductivity thus lower loss but more expensive.

Carrier-selective passivating contacts (CSPCs) are becoming essential to overcome recombination loss at the contacts' interface. The fundamental characteristics of these contacts are providing effective carrier selectivity by creating sufficient band bending and introduce excellent interface passivation by treating the surface dangling bonds. Silicon oxide is a widely used material in the solar industry as a tunneling layer to provide chemical passivation and selectivity at the same time. It has a low fixed charge therefore it can be used in both n-type and p-type silicon wafers [9]. The growth condition of silicon oxides such as time and temperature is crucial to determine the thickness and the density of the created layer thus the passivation results. Generally, a hydrogenation step follows the deposition of the thermal silicon oxide by depositing a layer with a high hydrogen content to enhance the passivation during the annealing step. Materials like aluminum oxide (AlO<sub>x</sub>) and amorphous silicon (a-Si) are typically used in the hydrogenation process which will be discussed in detail in the front surface field chapter.

# 1.6 Thesis objective:

The objective of this thesis is to fabricate high-efficiency IBC solar cells with thermal-SiOx/ (doped) poly-Si as passivating contacts. The main research questions are as follows:

1-investigating the passivation quality of the poly-Si selective passivating contacts by using dry thermal silicon oxide as a tunneling layer instead of wet oxidation.

2-evaluating the influence of high-temperature annealing on the dry thermal silicon oxide.

3-Evaluating the passivation of the front side of the cell by utilizing different doping doses and different passivation layers.

4- Optimizing the hydrogenation steps after evaluating the effect of the forming gas annealing (FGA) on the front surface field, and the passivated contacts.

The results of aim 1 and 2 will be applied first to produce front/back contacted solar cells (FBC), while the outcome of 3 and 4 will be implemented directly to produce IBC solar cells.

#### 1.7 Thesis outline:

This thesis work consists of 6 main chapters, the second chapter provides a brief overview of the used technologies in the fabrication process and the measurement tools. In chapter 3 the theory behind the carrier selective contacts is first explained. then the fabrication process of the passivation test samples is detailed and results are discussed. The optimized poly-Si CSPCs in chapter 3 will be used to fabricate FBC solar cells. The fabrication process and the external parameters of these cells are measured and discussed in chapter 4. In chapter 5 the approach used to enhance the passivation of the front side of the cells is detailed and tested. while chapter 6 is assigned to explain the used flowchart to fabricate IBC solar cells and discuss the results. The report concludes with a discussion of the findings and recommendations to enhance the fabrication process and a road map to fabricate >23% IBC solar cells.

# Experimental methods

This chapter aims to give a brief explanation of the main used technologies in the fabrication process to fabricate the IBC solar cells.

In this project, phosphorous (n-type) doped crystalline silicon (c-Si) wafers manufactured by TOP-SIL are used. The wafer material properties are presented in table 2.1. The reason behind the choice of n-type wafers is motivated by two crucial properties. First, n-type have a higher bulk minority carrier lifetime because it has lower sensitivity to recombination. Second, p-type material suffers from oxygen impurities due to wafer fabrication, therefore n-type are more used to avoid the boron-oxygen related light-induced [6].

## Wafer properties:

In this work mono-crystalline, n-type silicon wafers manufactured by TOP-SIL are used during the fabrication process of the test samples and the IBC solar cells. The wafers properties are given in table 2.1. The choice of mono-crystalline silicon wafers is due to the absence of the grain boundary in the silicon to avoid the trap states at the edges which leads to a decrease in the lifetime of the carriers. The wafers are fabricated through the Float Zone process which is known for its low densities of impurities like oxygen and carbon. Phosphorous doped silicon wafer has desired advantages as they do not suffer from light-induced degradation like p-type wafers because of the absence of Oxygen and Boron, and also they are less sensitive to impurities like iron thus high-quality n-type silicon wafers are cheaper than their counterparts.

Table 2.1 c-Si material properties.

| Parameter  Doping  Thickness [μm] | Value    |  |  |  |  |

|-----------------------------------|----------|--|--|--|--|

| Doping                            | n-type   |  |  |  |  |

| Thickness [µm]                    | 260~300  |  |  |  |  |

| Orientation                       | <100>    |  |  |  |  |

| Diameter [mm]                     | 100 +/-2 |  |  |  |  |

| Resistivity [ ohm.cm]             | 1-5      |  |  |  |  |

# Standard cleaning:

Standard cleaning is the first step in any fabricating process to remove any probable organic and inorganic contamination. They conducted a standard cleaning process in Else Kooi Laboratory (EKL), which consists of four steps. At the first step, the wafers are immersed in a 99% HNO<sub>3</sub> solution for ten minutes then they are moved to the rinsing bath for five minutes where an automatic rinsing process is performed with deionized water. Then the wafers are immersed in a 68 % HNO<sub>3</sub> solution at 100°C for 10 minutes and after that, the rinsing process is carried out again and followed by a dry step. To avoid the formation of a native oxide layer before the formation of the aimed silicon oxide an extra cleaning process (Marangoni) is performed. In this step the wafers are immersed in a 0.55% hydrofluoric acid (HF) solution until the surface becomes hydrophobic then the wafers are rinsed with deionized water to flush the HF and at the last minute, isopropyl alcohol (IPA) is added for drying.

#### Thermal Oxide Growth:

In this work, an ultra-thin layer of Thermal Oxide t-SiO $_X$  is added as a tunneling layer. This layer is formed by dry thermal oxidation where the silicon wafers have entered a furnace at a temperature of 675°C for three minutes to enable the oxide growth with a thickness of 1.5 nm. The temperature and time are of significant importance to determine the thickness of the formed oxide. In this work, an Ellipsometry measurement is carried out to make sure that the formed oxide is in an acceptable thickness range between 1.4-1.5 nm. The formed Oxide is based on the reaction between the silicon and the Oxygen as shown in equation 2.1. This reaction takes place in a Tempress furnace where the chamber initially is filled with nitrogen with a gas flow of 6 SLM and when the furnace reaches the tuned value, Oxygen is added for a determined time duration with a gas flow of 0.6 SLM.

Si (s) + O2 (g)

$$\rightarrow$$

SiO2 (s) 2.1

To avoid any additional growth of the native oxide layer, the wafers are directly moved to the LPCVD furnace where the a-Si is deposited.

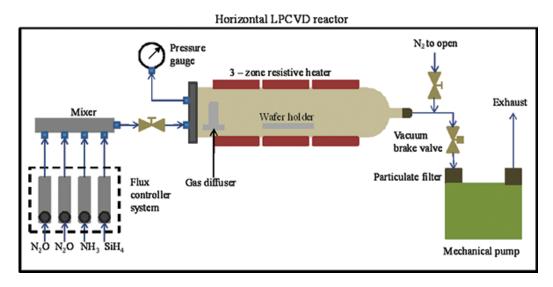

# Low-pressure chemical vapor deposition (LPCVD):

In order to deposit a thick a-Si layer, the Low-pressure chemical vapor deposition (LPCVD) technique is used as it results in a pure and high uniformity deposited layer [10]. The process is carried out under low pressure (10 mTorr to 1 Torr) thus it is performed with minimal diffusion of the reactant gasses. Firstly, the tube is evacuated and when the pressure reaches the tuned value, the tube starts heating up to the deposition temperature to enable the precursor gas decomposition [11]. In the used recipe a 250 nm of a-Si is deposited at 580°C with a calculated deposition rate of 2.2 nm/min.

Figure 2.1 Schematic of an LPCVD reactor [12]

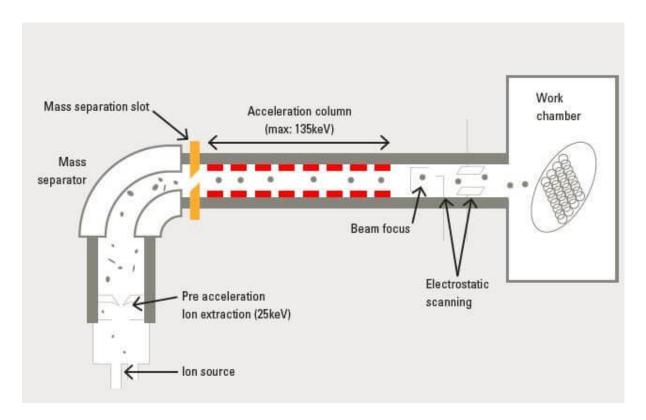

# Ion Implantation:

To fabricate n<sup>+</sup> and p<sup>+</sup> poly-Si layers, ion-implantation technology is used to dope the a-Si with Phosphorous and Boron respectively. Varian ion implanter is used in this work which enables a wide control on the doped layer as we can tune the implantation energy to achieve the desired doping depth and the doping dose. The dopants are created by plasma and accelerated by a magnetic field towards the surface of the aimed wafer. The ions with high energy can cause a defect in the wafer's

surface which is a drawback of this technology. The used parameters in the implantation are illustrated in table 2.3 and the diagram of the implanter is sketched in figure

Table 2.3: the used implantation variables in the thesis.

| Region      | lon type    | on type Doping Impla<br>dose(ions/cm²) |        |

|-------------|-------------|----------------------------------------|--------|

| <br>Emitter | Boron       | 5e15                                   | 20 keV |

| <br>BSF     | Phosphorous | 6e15                                   | 20 keV |

| FSF         | Phosphorous | 1e14 &3e14                             | 20 keV |

Figure: 2.3 Schematic of the ion-implantation technology [13].

# Plasma Enhanced Chemical Vapour Deposition:

Plasma Enhanced Chemical Vapour Deposition (PECVD) is commonly used to deposit a thin film of material from a gas state on a substrate as a solid-state. Passivating layers like a-Si and SiNX, which serve as anti-reflection coating and a capping layer for the hydrogenation treatment usually deposited through PECVD since it enables deposition at low temperature[14]. The machine chamber has two electrodes to create plasma when the Radiofrequency RF is on. To ignite the Plasma a highly energetic

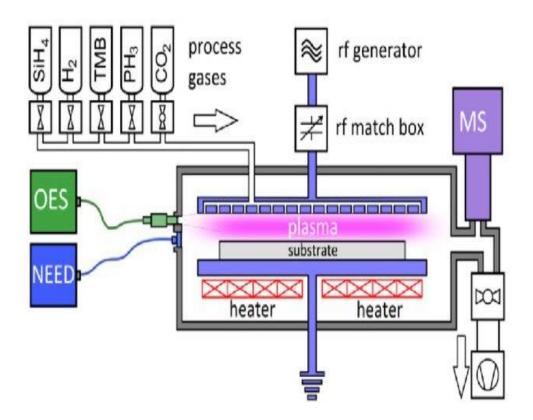

field across the electrodes in both sides of the chamber is placed. For Silicon nitride deposition a mix of Silane and Ammonia gasses are existed as reactants to obtain the required six. In this work, we use this technology in order to deposit a thick SiNX layer to protect the rear side of the cell during texturing process. It is also used in order to passivate the front side of the cells with materials like a-Si and SiNX. A schematic sketch of the PECVD process is given in figure 2.4.

Figure 2.4 Scheme of the PECVD tool[15]

# CARRIER SELECTIVE PASSIVATING CONTACT

In this chapter, the experimental details of fabricating and optimizing Carrier Selective Passivating Contacts (CSPC) are presented and explained. Firstly, the chemical passivation and the field-effect passivation are explained, then the influencing factors on each type are introduced and discussed. After that, the experimental process of the passivation test samples is detailed and sketched and followed by the results obtained at different annealing conditions. The Hydrogenation processes of FGA and  $SiN_X$  deposition used to enhance the passivation quality are introduced with the fabricating steps and followed by the passivation results discussion. Then the measurement steps of the contact resistivity used in this work are explained and the results are plotted for both the  $n^+$  poly-Si and the  $p^+$  poly-Si. Finally, the chapter concludes the results with a summary and the optimal findings to fabricate the poly-Si CSPC.

# 3.1 The passivation quality of poly-Si CSPC - a short review:

Carrier Selective Contacts can be made by several approaches such as introducing heavy doping region under the contacts, or by surface carrier modulation which is done by introducing a layer with large fixed charge density to function as an external potential source, or using a heterojunction between a silicon substrate and a wide bandgap material, etc.

The approach used to make Carrier Selective passivated Contacts in this work is to introduce an ultrathin tunneling layer of thermal  $SiO_X$  (< 2 nm) as a tunneling layer with a heavily doped poly-Si for the emitter contact and the back surface field contact. There are different fabricating parameters of these layers that influence the surface recombination and the carrier's collectivity, which will be discussed, such as the parameters used in the growth of the t-SiO<sub>X</sub>, the thickness of the poly-Si layers, the doping

dose for ion-implantation of poly-Si and the high-temperature annealing for activating/diffuse the dopants [16,17].

## 3.1.1 Chemical passivation:

Using  $SiO_X$  with doped poly-Si in the CSPCs plays an essential role to reduce the recombination current density,  $J_{0}$ , and provide the required chemical and electric field passivation which leads to achieving a solar cell efficiency over 26% [18,19], The t-SiO<sub>X</sub> layer has a chemical passivation function since it passivates the dangling bonds at the surface and minimizes the defect density at the c-Si/SiO<sub>X</sub> interface. Silicon Oxide has another advantage to separate the doped poly-Si layer from the c-Si bulk and prevent the epitaxial growth of the poly-Si layer during the high-temperature annealing step[16]. The  $SiO_X$  layer can be formed in different ways such as using wet chemical oxidation like nitric acid [20,21] or by or  $UV/O_3$  [16,23] or by dry thermal oxidation [16,22,23] as it is conducted in this work.

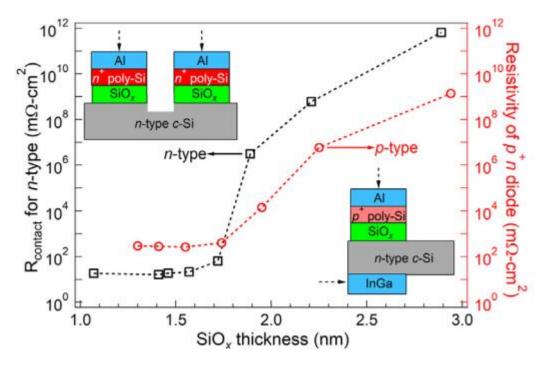

Silicon Oxide is a dielectric material; however, in the SiOx/doped poly-Si passivating contact structure, the charge carriers are transported from the c-Si to the poly-Si via two different transport mechanisms: tunneling, and through pin-holes as it provides direct pathways between the c-Si bulk and the poly-Si contacts [16,24]. The tunneling transport mechanism is effective and sufficient for ultra-thin  $SiO_X$  layer < 1.5 nm [24,25]. For thicker layer  $SiO_X$  (> 1.7 nm) the density of pin-holes in the oxide layer is vital and has to be optimized to achieve good conductivity, as insufficient pinholes density with poor tunneling transportation leads to high series resistivity (R<sub>S</sub>) and poor solar cell fill factor (*FF*), while In the other hand too much transport through pin-holes (i.e when the possibility of transport through pinholes >10<sup>-3</sup>) reduces the performance parameters of the solar cell such as *FF*,  $V_{OC}$ , and  $J_{SC}$  significantly[24]. To conclude, the optimal thickness of the silicon oxide layer has to achieve an ideal balance between the carrier transportation and chemical passivation besides that the doped poly-Si/SiO<sub>X</sub> stack has a positive impact to reduce the metallization-induced recombination[24].

## 3.1.2 Electric-field passivation:

Optimizing the Poly-Si layer has high importance to obtain an excellent passivation quality, therefore, many pieces of research were conducted to optimize its thickness, doping dose in case of ion implantation and the annealing temperature as these parameters together influence the doping profile of the  $n^+$  and  $p^+$  poly-Si passivating contacts since the field-effect passivation is based on this doping profile [21]. The doped poly-Si regions facilitate the electric field passivation by the band bending occurs at the poly-Si/SiO<sub>x</sub>/c-Si interfaces as shown in figure (3.1). The formed high-doping regions decrease the conductivity and the mobility of the minority carriers as a result of reducing the equilibrium concentration of the minorities thanks to the introduced difference in chemical potential by the doping with respect to c-Si bulk. While in the other hand, the increase in the majority's concentration leads to an increase of the majority carrier conductivity consequently obtaining a low contact resistivity [26].

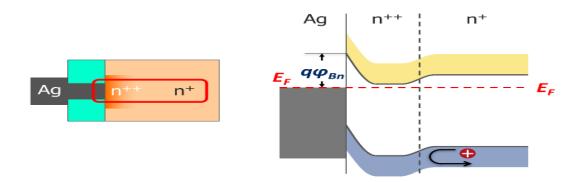

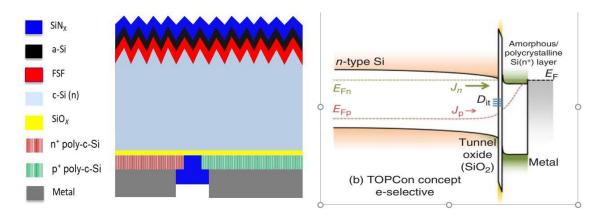

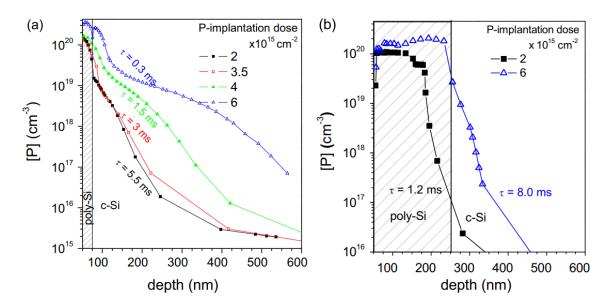

Figure 3.1: left: Schematic of a half-pitch IBC cell structure. Right: cell band diagram [36]

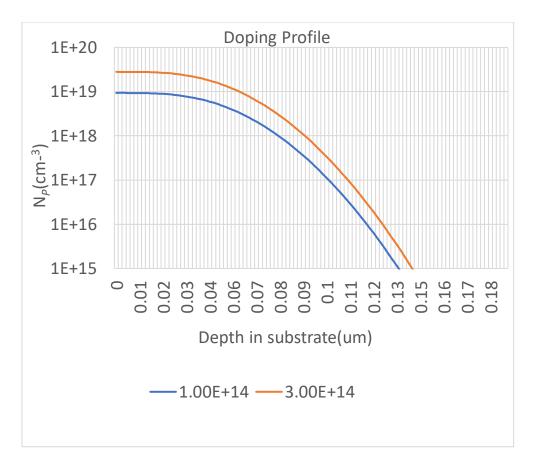

Generally, Electrochemical capacitance-voltage (ECV) is used to measure doping profiles in semiconductor layers where the measurement results show the carrier concentration and the profiling depth inside the materials [27]. The doping concentration increases with increasing the doping dose during the ion-implantation, and these implanted atoms will be activated and diffuse through the poly-Si in the annealing step at high temperatures. The annealing step is crucial to convert the deposited a-Si into poly-Si and to activate the dopants. This step is done usually in a furnace with a temperature range between 800 and 1050 °C. Besides the temperature parameters the annealing atmosphere also affects the passivation quality e.g., annealing in O2 atmosphere shows better passivation results according to G. Yang et al. than annealing in a nitrogen one [21]. Figure (3.4) illustrates the doping profiles of phosphorous at fixed implantation energy and annealing conditions but for two different thicknesses of poly-Si. It is seen that for different thicknesses different minority carrier lifetime obtained and the maximum of 5.5ms obtained for 75 nm of poly-Si was prepared with an ion implantation dose of 2E15 cm<sup>-2</sup> whereas, for a thicker layer of poly-Si like 250nm, a maximum lifetime of 8ms is obtained at a dose of 6E15 cm<sup>-2</sup>. This behavior is attributed to the fact that the more migrated implanted atoms to the c-Si bulk the lower the passivation because of insufficient or no band bending at the interface of the poly-Si/c-Si. On the other hand, confining the majority of the dopants in the poly-Si region will lead to efficient field-effect passivation based on the strong established band bending at the poly-Si/c-Si interface.

Figure 3.2: left: ECV measurement for P-doping profile for  $n^+$  poly-Si passivating contacts with a thickness of 75 nm prepared with an implantation energy of 20 KeV but different doping dose, and annealed at 850°C for 90 min in  $N_2$  at. Right: P-doping profile for poly-Si passivating contacts with a thickness of 250 nm prepared with an implantation energy of 20 KeV but different doping dose and annealed at 950°C for 5 min in  $N_2$ [21]

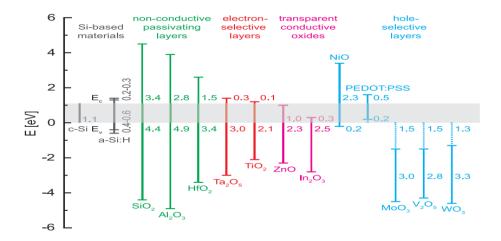

It is also important to give attention to the optical properties of the passivating material used in CSPC like  $SiO_X$ , Poly-Si, etc. Materials that have a close energy bandgap to c-Si like a-Si or poly-Si cause large absorption losses and lead to a decrease the  $J_{SC}$  and consequently the efficiency of the cell. Therefore, transparent passivating materials with wide-bandgap like  $SiN_X$  is stacked on  $AlO_X$  layer are usually used in the top side of the cell, whereas passivating materials with high absorption coefficients like poly-Si/SiO<sub>X</sub> are used at the back side [26,28]. However heavily doped poly-Si result in a free-carrier absorption (FCA) nevertheless they are used in the rear side [28].

Figure 3.3: Conduction and valence band of various materials with respect to c-Si. [26]

# 3.2 Experimental details

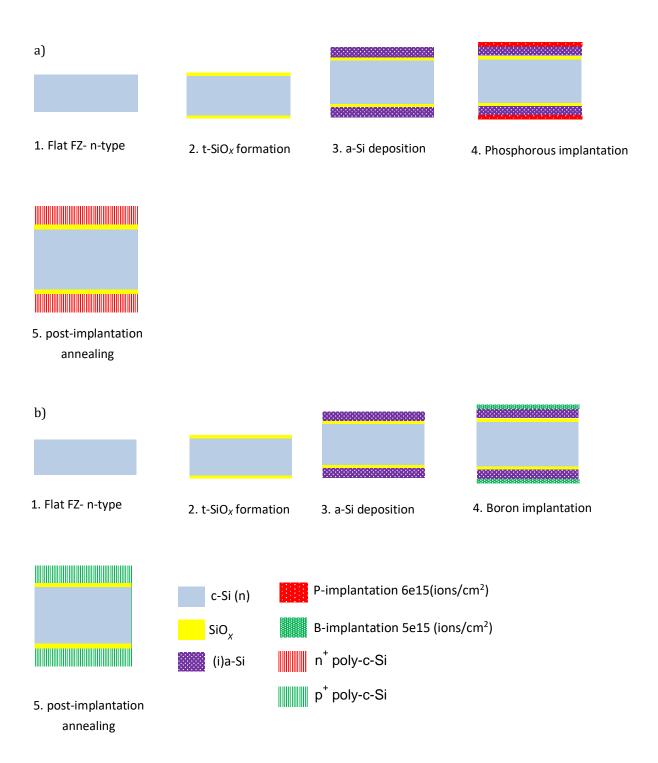

This section aims to explain the fabrication process of the symmetrical samples that are used to measure the passivation quality of the poly-Si passivating contacts. The flowchart used is visualized for better understanding in Figure 3.4, and explained as follows:

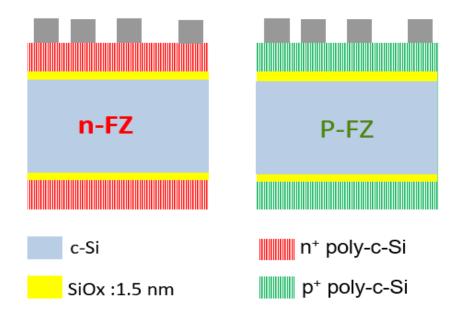

The wafers used in this test are n-type float-zone (FZ) c-Si wafers, double-side polished with a thickness of 280 um and <100> oriented. Firstly, the wafers pass through a standard cleaning process to remove any contaminants, then the Marangoni cleaning process to remove the thin oxide layer on the silicon surface. The t-SiO<sub>X</sub> is directly formed after Marangoni step by dry oxidation in the furnace at 675°C for three minutes, in an oxygen atmosphere. After that, a 250 nm thick intrinsic a-Si is deposited on both sides utilizing the Low-Pressure Chemical Vapor Deposition (LPCVD) technique. The next step is the ion implantation where Phosphorous and Boron are used to make the  $n^+$  poly-Si and  $p^+$  poly-Si layers with doping doses of 6e15 and 5e15(ions/cm²) consequently at a fixed implantation energy of 20 KeV via Varian ion implanter E500HP. Another standard cleaning process is performed after the implantation to remove any contamination or impurities caused by the implanter.

The last step is the high-temperature annealing which is conducted at different temperatures and time duration to crystallize the amorphous silicon layers and activate the dopants to form the final  $n^+$  polyc-Si and p+ poly-c-Si passivating contacts. The annealing conditions used are 950 °C for 5 minutes, 1000 °C for 1 minute, and 1050 °C for 1 minute, and all samples are annealed in an  $O_2$  atmosphere. It is worth mentioning that many optimized fabricating parameters such as doping dose, poly-Si thickness, etc. in this thesis project are token from previous projects at the PVMD group at TU-Delft, see table (3.1).

Figure 3.4: Schematic sketches of the steps used to process the passivation test samples: (a)  $n^+$  poly-SiO<sub>X</sub> test sample.

Table 3.1 The, ion implantation parameters, and post-implantation annealing conditions [21] used for optimized the n-type and p-type poly-Si passivating contacts with NAOS  $SiO_X$  and different poly-Si thicknesses

| Poly-Si       |                  |                   | Implantation    |                                                 | Annealing/Oxidation |               |                                | Passivation            |                                         |                          |

|---------------|------------------|-------------------|-----------------|-------------------------------------------------|---------------------|---------------|--------------------------------|------------------------|-----------------------------------------|--------------------------|

| n-/p-<br>type | Sample<br>number | Thickness<br>[nm] | Energy<br>[keV] | Dose<br>[ × 10 <sup>15</sup> cm <sup>-2</sup> ] | Temperature<br>[°C] | Time<br>[min] | N <sub>2</sub> /O <sub>2</sub> | τ <sup>b</sup><br>[ms] | J <sub>o</sub><br>[fA/cm <sup>2</sup> ] | iV <sub>oc</sub><br>[mV] |

| n-type        | 1                | 70                | ~               | ~                                               | 850                 | 90            | N <sub>2</sub>                 | 0.03                   | 1000                                    | 560                      |

| ••            | 2                | 75                | 20              | 2                                               | 850                 | 90            | N <sub>2</sub>                 | 5.5                    | 9.5                                     | 706                      |

|               | 3                | 75                | 20              | 3.5                                             | 850                 | 90            | $N_2$                          | 3                      | 21.5                                    | 694                      |

|               | 4                | 75                | 20              | 4                                               | 850                 | 90            | N <sub>2</sub>                 | 1.5                    | 51                                      | 684                      |

|               | 5                | 75                | 20              | 6                                               | 850                 | 90            | N <sub>2</sub>                 | 0.3                    | 228                                     | 637                      |

|               | 6                | 250               | 20              | 2                                               | 950                 | 5             | N <sub>2</sub>                 | 1.2                    | 48                                      | 679                      |

|               | 7                | 250               | 20              | 6                                               | 950                 | 5             | N <sub>2</sub>                 | 8                      | 9                                       | 721                      |

|               | 8                | 250               | 20              | 6                                               | 950                 | 5             | 02°                            | 11.8                   | 6                                       | 723                      |

| p-type        | 12               | 200               | 5               | 5                                               | 950                 | 5             | N <sub>2</sub>                 | 1.8                    | 25                                      | 695                      |

|               | 13               | 200               | 5               | 5                                               | 950                 | 15            | N <sub>2</sub>                 | 1.6                    | 33                                      | 690                      |

|               | 14               | 200               | 5               | 5                                               | 950                 | 30            | N <sub>2</sub>                 | 1.1                    | 65                                      | 677                      |

|               | 15               | 250               | 5               | 5                                               | 950                 | 5             | N <sub>2</sub>                 | 1.9                    | 30                                      | 692                      |

|               | 16               | 250               | 5               | 5                                               | 950                 | 5             | 02°                            | 3.8                    | 19                                      | 704                      |

# 3.3 the influence of annealing on the passivation quality

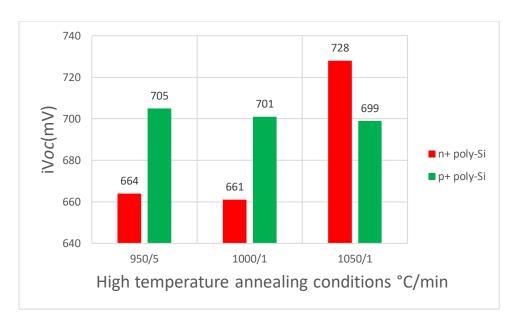

The best passivation quality achieved is 728mV for  $n^+$  poly-Si contact at annealing conditions of (1050 °C for 1 minute) and 705mV for  $p^+$  poly-Si contact at annealing condition of (950 °C for 5 minutes), whereas the  $p^+$  poly-Si contact at (1050 °C for 1 minute) annealed condition has the lowest iV $_{OC}$  with 6mV lower than the best  $p^+$  poly-Si contact result obtained for the sample annealed at (950 °C for 5 minutes). However, the difference is greater than 60 mV for  $n^+$  poly-Si contacts between the best and the lowest as a result of the differences between the doping profiles formed in each sample.

As all of the samples have the same chemical passivation layer. The difference in the passivation quality between the different samples annealed at different conditions is attributed mainly to the doping profile formed after the annealing step which did not provide a good field-effect passivation for the samples annealed at 950 °C for 5 minutes and at 1000°C for 1minute. Increasing the annealing temperature pushes the dopants to diffuse deeper in the c-Si surface as explained in section (3.1.2) which decreases the electrical field at the c-Si/SiOx/poly-Si interfaces and increases the Auger recombination at the c-Si surface. Thus, a balance should be found between the doping dose, the poly-Si thickness, and the annealing conditions to obtain the optimum doping profile for achieving the best field-effect passivation. It is noticeable that the passivation quality of the p<sup>+</sup> poly-Si contacts samples shows slighter variation than the n-type contacts samples. An ECV measurement would be very effective to analyze the doping profiles formed to evaluate the field-effect passivation at each annealing condition, however, this measurement was not available at the time of the project.

Figure 3.5: Passivation properties of symmetrical ( $n^+$ ) poly-Si samples and ( $p^+$ ) poly-Si samples after different annealing conditions.

# 3.4 The influence of hydrogenation on the passivation quality

In this section, the principles behind the hydrogenation processes that are used to enhance the passivation quality will be explained and the previously optimized fabrication parameters that influence the hydrogenation properties will be introduced and discussed. After that a schematic sketch of the symmetrical samples are used in the tests will be given and followed by the results of the hydrogenated  $p^+$ -poly-Si and the  $n^+$ -poly-Si contacts.

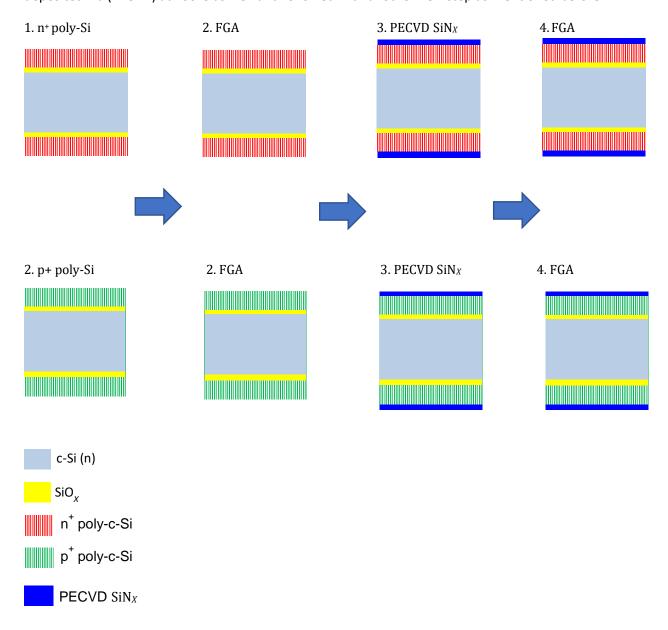

The hydrogen atoms included in a rich hydrogen content layer or available in the furnace atmosphere during a hydrogenating annealing step have a significant effect to increase the chemical passivation quality. Therefore, it can increase the  $iV_{OC}$  and the minority carrier's lifetime [29,30,31]. The deposited  $SiN_X$  layer can be considered as a hydrogen donor layer and the FGA step enables the Hydrogen atoms to diffuse in and passivate the dangling bonds of the silicon atoms at the c-Si surface that present trap states within the bandgap of the silicon at the bulk surface which could not be passivated by the  $SiO_X$  layer [32,33]. In this thesis work, to obtain the maximum passivation enhancement through hydrogenation, two processes are generally done. Firstly, the hydrogenation process through low-temperature annealing step in a furnace with a mixture of hydrogen and nitrogen atmosphere gases, at 400 °C for 30 minutes, which is normally referred to as forming gas annealing (FGA). after that, a capping layer of  $SiN_X$  has deposited through plasma enhanced chemical deposition (PECVD) technology, followed by another FGA step.

The samples used in this test are the same samples used to measure the passivation quality of the  $p^+$ -poly-Si contacts and the  $n^+$ -poly-Si contacts after the high-temperature annealing step. The samples then enter the furnace for 30 minutes at 400 °C where these parameters are already optimized in previous work at the group and show that the temperature is of significant importance as increasing the annealing temperature result in a decrease in the measured  $iV_{OC}$ . This reduction is attributed to the diffused hydrogen from the capping layer, it is also shown that increasing the annealing temperature to exceed the one used in the t-SiO<sub>X</sub> growth 700°C e.g. result in a dramatic decline in the  $iV_{OC}$ . The reported results for different annealing times show that the annealing time duration has almost no influence on the  $iV_{OC}$ , therefore it is decided to do the annealing at 400°C for 30 minutes which gives the highest obtained passivation quality [34]. After the FGA treatment, a 75 nm of SiN<sub>X</sub> is deposited via (PECVD) at 400°C as well and followed with another FGA step as mentioned before.

Figure 3.7: Schematic sketches of the hydrogenation treatment steps applied for  $n^+$  poly-SiO<sub>X</sub> test samples and  $p^+$  poly-SiO<sub>X</sub> test samples.

### 3.4.1 Hydrogenation tests results:

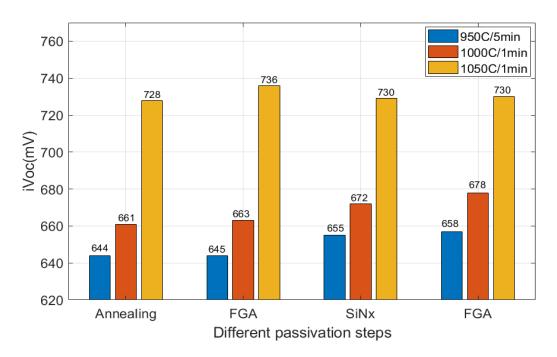

In the following figures the output passivation values for  $n^+$  poly-SiO<sub>X</sub> test samples and  $p^+$  poly-SiO<sub>X</sub> test samples which are sketched in figure 3.7, after the different hydrogenation steps are plotted.

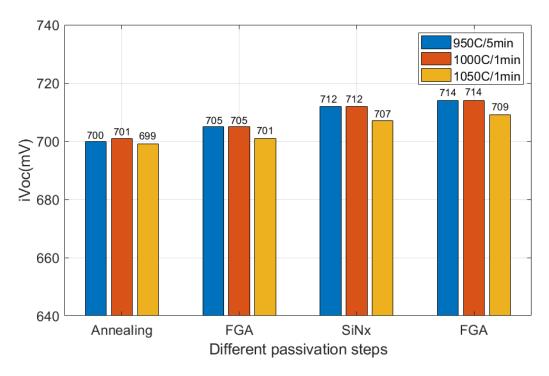

Figure 3.8: The passivation qualities of  $n^+$  poly-Si test samples prepared with different annealing conditions (950°C/5min,1000°C/1min, 1050°C/1min) as a function of the hydrogenation steps.

Figure 3.9 The passivation qualities of  $p^+$  poly-Si test samples prepared with different annealing conditions (950°C/5min,1000°C/1min, 1050°C/1min) as a function of the hydrogenation steps.

The results shown in figure (3.8) illustrate that the hydrogenation treatment generally was not effective to enhance the passivation quality for the samples annealed at (950°C/5min and  $1000^{\circ}$ C/1min) to exceed the 700mV for the n<sup>+</sup> poly-SiO<sub>x</sub> test samples. The passivation quality of the n<sup>+</sup> sample of the wafers annealed at 950°C/5min and  $1000^{\circ}$ C/1 min gradually enhanced through the SiN<sub>x</sub> deposition and the second FGA step, whereas both of them show no change in iV<sub>OC</sub> after the first FGA step. These results indicate that there was not enough hydrogen diffusion to passivate the trap states at SiO<sub>x</sub>/c-Si interface which leading to slight passivation quality changes. After the SiN<sub>x</sub> deposition both of them show an increase of around 10 mV in the iV<sub>OC</sub> value as a result of the improvement in the chemical passivation, in the other hand the wafer annealed at  $1050^{\circ}$ C/1min shows 8mV increase in the iV<sub>OC</sub> in by the first FGA step but negatively affected by the next two hydrogenation steps to reach at the end 730mV, this reduction can be caused by eventual contamination through the hydrogenation processes and needs further investigation.

The results of  $p^+$  poly-Si visualized in figure (3.9) show a gradual improvement for all the samples as a result of the chemical passivation, the best passivation obtained is 714mV for samples that are annealed at (950°C/5min and 1000°C/1min), Whereas the sample annealed at 1050°C/1min reach 709mV.

The hydrogenation findings out of this work show that the samples annealed at 1050°C/1min are the best candidate to fabricate the aimed IBC solar cells yet. However, the passivation quality obtained can be further optimized by conducting more tests with different fabricating parameters in terms of poly-Si thicknesses and the doping dose of the ion implantation.

#### 3.5 Contact resistivity:

Generally, the quality of the passivating contacts in c-Si solar cells is defined by the passivation quality which is evaluated usually by  $J_0$  or  $iV_{OC}$ . The influence of such contacts on the solar cells' series resistance can be evaluated by measuring their contact resistivity,  $\rho_C$ . For high conversion efficiency solar cells, it comes of significant importance to reduce both parameters  $J_0$  and  $\rho_C$  simultaneously for increasing the carrier selectivity. This will reduce the minority's conductivity thus reducing  $J_0$ , and raise the majority carrier's conductivity to minimize  $\rho_C$  at the same time [26].

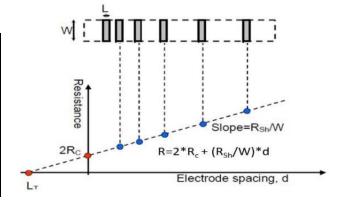

# 3.5.1 Transfer Length Measurement (TLM) and samples preparation:

To conduct the TLM measurement we fabricated symmetrical samples as shown in figure (3.10). The sample preparation follows the same process as the samples are fabricated for the passivation test, see section3.2. The same t-SiO<sub>X</sub> growth condition (675°C/3min) is used and the same deposition

parameters for the poly-Si of 250nm and implantation dose of 6e15(ions/cm2) for the P-doping and 5e15 (ions/cm2) for B-doping at a fixed implantation energy of 20keV, after that the samples divided to three groups to be annealed at three different annealing conditions ( $950^{\circ}$ C/5min,  $1000^{\circ}$ C/1min and,  $1050^{\circ}$ C/1min) similar to the conditions used for the passivation test. The following process is metallization which is done by depositing 2um of Aluminum by e-beam evaporation technique using a hard musk to obtain metallic fingers with different spacing. A p-type bulk is used to measure the contact resistivity for the p<sup>+</sup>poly-Si contacts to avoid the formation of a p-n junction that blocks the carrier's transportation through the t-SiO<sub>X</sub>.

Figure 3.10: Schematic of the TLM sample to measure the resistivity of n<sup>+</sup>-poly-Si and p<sup>+</sup>-poly-Si

Table (3.2) metal pads geometry

| Matalmad              | width (um)      | Length(um) |  |  |

|-----------------------|-----------------|------------|--|--|

| Metal pad             | 250             | 1000       |  |  |

| Spacing<br>parameters | Metal pad label | Space(um)  |  |  |

|                       | D1              | 650        |  |  |

|                       | D2              | 100        |  |  |

|                       | D3              | 1550       |  |  |

|                       | D4              | 2000       |  |  |

|                       | D5              | 2450       |  |  |

|                       | D6              | 2900       |  |  |

|                       | D7              | 3350       |  |  |

Figure 3.11: Illustration diagram of the TLM method.

The resistance is measured between each metal pad and the pad next to it, then the results are plotted against the spacing detailed in the table (3.2) to calculate  $R_c$  value which is twice the value of the intercept at the Y-axis, see figure (3.11) after that value calculated is used to find the contact resistivity  $\rho_C$  (m $\Omega$ .cm<sup>2</sup>)

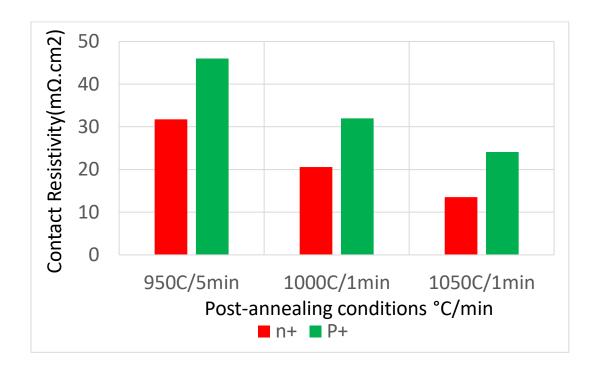

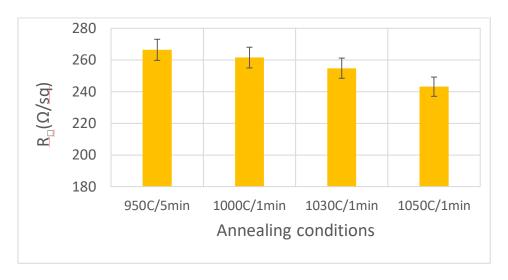

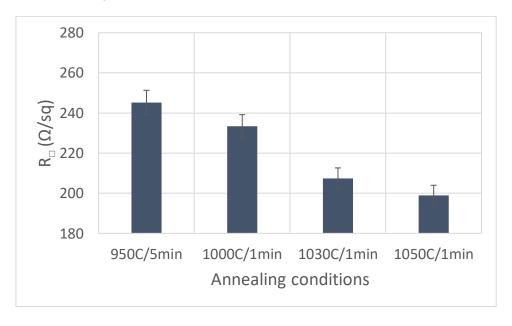

The results presented in figure (3.12) show that  $p^+$ -poly-Si contacts have higher resistivity than  $n^+$ -poly-Si contacts, while the main finding is that increasing the annealing temperature from 950°C to 1050°C almost decrease the contact resistivity to the half for both  $p^+$  and  $n^+$  contacts. However, the minimum contact resistivity obtained was  $13.5(m\Omega.cm^2)$  for  $n^+$  with an annealing condition of( $1050^\circ\text{C}/1\text{min}$ ) which is still high compared to results achieved by using NAOS  $SiO_X$  instead of t-SiO\_X [35]. The difference in the conductivity between the NAOS  $SiO_X$  and the t-SiO\_X is attributed to the fact that t-SiO\_X has a higher density than NAOS  $SiO_X$  thus the charge transport mechanisms through tunneling and pinholes in NAOS is more efficient. Our findings are consistent with the conclusion obtained by Z. Zhang et al [24]. that increasing the annealing temperature leads to form more pinholes thus, enable lower Rc. It worth to mention the structure of the samples used in the contact resistivity measurement is not 100% accurate, since part of the current will flow through the poly-Si layer. To obtain accurate contact resistivity of the poly-Si/bulk the poly-Si layer between the metals pad should be etched. For this project, the performed measurement gives acceptable results to indicate the influence of annealing temperature on the contact resistivity values.

Figure 3.12: Contact resistivity values of Al/ doped poly-Si /t-SiO<sub>X</sub> / c-Si at different annealing conditions in terms of temperature and duration.

#### 3.6 Summary:

Initially, the fabricated test samples aim to optimize the  $n^+$ -poly-Si and  $p^+$ -poly-Si contacts' structure to enable effective field-effect passivation associated with chemical passivation from the deposited SiN<sub>X</sub> and the FGA treatment. Three annealing conditions are tested: 950°C/5min,1000°C/1min, and 1050°C/1min, the sample annealed at 1050°C/1min condition show the best passivation quality for  $n^+$ -poly-Si contact. For  $p^+$  samples, all samples show close values for the passivation quality with a slight advantage to the sample annealed at 950° for 5 minutes. After that hydrogenation, tests are carried out and all the tested samples show a gradual enhancement in terms of the passivation quality since hydrogen effectively saturates the dangling bond of the silicon atoms at the interface. The best-obtained iV<sub>OC</sub> after the hydrogenation process are 730 and 709 mV for  $n^+$  and  $p^+$  contacts respectively for the wafer with post-implantation annealing condition of 1050°C/1min.

To evaluate the quality of the poly-Si contact for different annealing conditions, TLM measurement is carried out for both  $n^+$  and  $p^+$  contacts. The observed results show a decrease in the contacts' resistivity when increasing the annealing temperature since the high temperature forms more pinholes that improve the carrier transportation.

### FRONT BACK CONTACTED SOLAR CELLS

In this chapter, the same fabricating parameters used in the symmetrical passivation tests are used to fabricate Front Back contacted solar cells (FBC) solar cells to evaluate the performance of the optimized poly-Si CSPCs in a simple structure before utilizing them in the complex IBC solar cell's structure. On the FBC cells, Suns- $V_{\rm OC}$  measurement is carried out and is followed by I-V measurement to characterize the external solar cell's parameters. The influence of different annealing conditions on the passivation quality is investigated and the difference between the pseudo fill factor and the fill factor is discussed. Silver and Aluminum as rear metal contacts are utilized respectively and the effect of the postmetallization annealing treatment is evaluated after the Aluminum deposition.

#### 4.1 Experimental details:

The goal of FBC solar cells is to test the electrical performance of the optimized poly-Si passivating contacts with the fabricating parameters discussed in chapter 3, before using them in the fabrication of interdigitated back contacted solar cells (IBC), due to the simplicity of the flowchart of the FBC cells.

For this process n-type float-zone (FZ) c-Si wafers, double-side polished with a thickness of 280 um and <100> oriented are used as a bulk. Firstly, the new wafers are subjected to cleaning processes of standard cleaning and Marangoni cleaning process in HF to remove any contamination and avoid native oxide formation before the aimed thermal silicon oxide growth. After that, the wafers entered the furnace at 675°C to form the dry thermal oxidation tunneling layer on both surfaces for a time duration of three minutes. The step after that is to deposit a thick layer of 250nm of intrinsic a-Si on both sides by means of Low-Pressure Chemical Vapor Deposition (LPCVD) technique which takes 113 minutes as a deposition time while the whole process needs a few hours, then the wafers are ready for the ion implantation where the Phosphorous doped side forms the n<sup>+</sup>-poly-Si contact at the front side while the Boron doped side forms the p<sup>+</sup>-poly-Si contact at the rear side. The implantation parameters used are 6e15 and 5e15(ions/cm²) for Phosphorous and Boron consequently at a fixed implantation energy of 20 KeV which are the same implantation parameters used in fabricating the

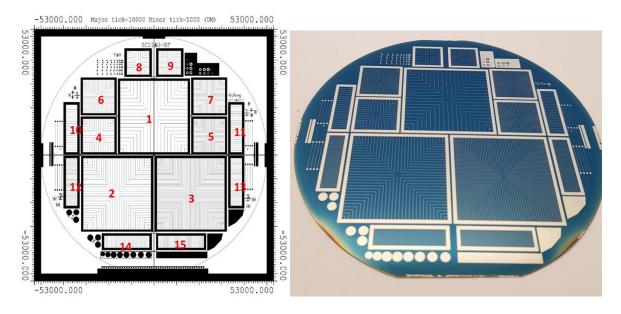

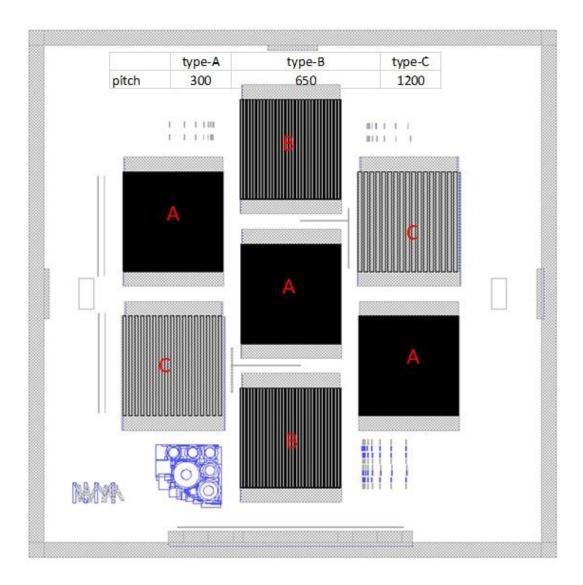

passivation quality test samples used in chapter 3. Post-implantation annealing step is carried out at three different time/temperature conditions of  $(950^{\circ}\text{C} / 5\text{min}, 1000^{\circ}\text{C} / 1\text{min})$  and  $1050^{\circ}\text{C} / 1\text{min})$  to enable the a-Si conversion to poly-Si and activate the dopants, then two hydrogenation treatments are conducted, first, a deposition of  $SiN_X$  of 75nm by PECVD on both sides and followed with FGA at  $400^{\circ}\text{C}$  for 30 minutes. The wafer was then immersed in a BHF bath to remove the  $SiN_X$  layer to prepare for the metallization deposition, where photolithography and lift-off process was utilized to form the front metallization grid and the rear contacts with help of the e-beam evaporation technology (PROVAC)to deposit 1 um of Silver on the top and 2 um on the rear side of the cell to form the front and back contacts. For the front side of the cell, the mask used to define the metallization geometry of the cell is shown in figure (4.1), the mask has four sizes of cells with different metallization cover percentage as detailed in table (4.1)

Figure 4.1 the mask used for the front side of the wafer and the wafer fabricated by this musk.

Table (4.1) Geometry specification of the lithography mask used to prepare metal grids for FBC cells

| Cell number | Area(cm2) | Number of fingers | Metal coverage (%) |  |

|-------------|-----------|-------------------|--------------------|--|

| 1           | 8.96      | 9                 | 1.93               |  |

| 2           | 8.96      | 14                | 2.96               |  |

| 3           | 8.96      | 29                | 6.02               |  |

| 4           | 1.96      | 6                 | 2.76               |  |

| 5           | 1.96      | 13                | 5.88               |  |

| 6           | 1.96      | 13                | 2.74               |  |

| 7           | 1.96      | 19                | 3.96               |  |

| 8           | 1         | 4                 | 2.52               |  |

| 9           | 1         | 9                 | 2.69               |  |

| 10          | 1         | 19                | 2.38               |  |

| 11          | 1         | 26                | 3.25               |  |

| 12          | 1         | 39                | 4.88               |  |

| 13          | 1         | 39                | 3.90               |  |

| 14          | 1         | 39                | 2.93               |  |

| 15          | 1         | 53                | 4.08               |  |

#### 4.2 Cells' precursor performances:

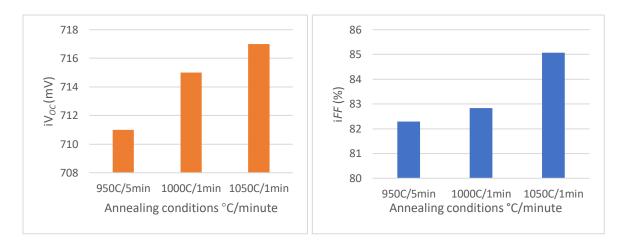

Three wafers are fabricated according to the details explained in section 3.2, where the only difference between them is the post-implantation annealing conditions to prove our result on the quality of the passivating contact obtained in chapter 3. The  $iV_{OC}$  and iFF for the cell's precursors measurement are carried out by Sinton WCT-120 after the hydrogenation step. The plotted results in figure 4.2 show that the  $iV_{OC}$  values are in the range between 711 and 719mV where the  $iV_{OC}$  increases when the temperature of the post-annealing increases, which is consistent with our passivation quality tests performed in chapter 3, see figure (4.2).

Figure (4.2) Passivation quality of the cell's precursor (iV $_{OC}$  and iFF).

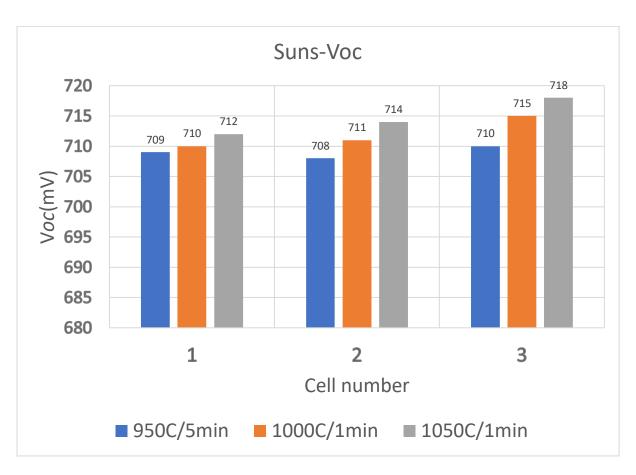

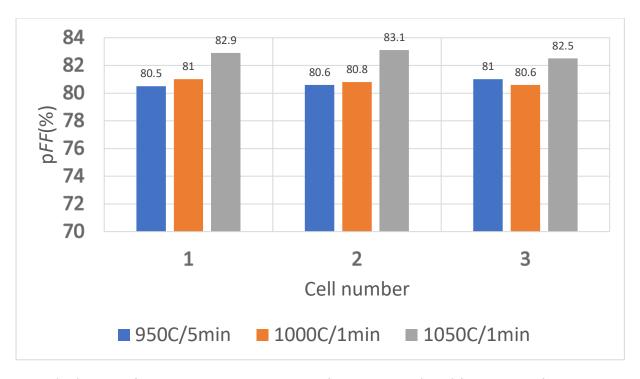

#### 4.3 Suns- $V_{OC}$ measurement:

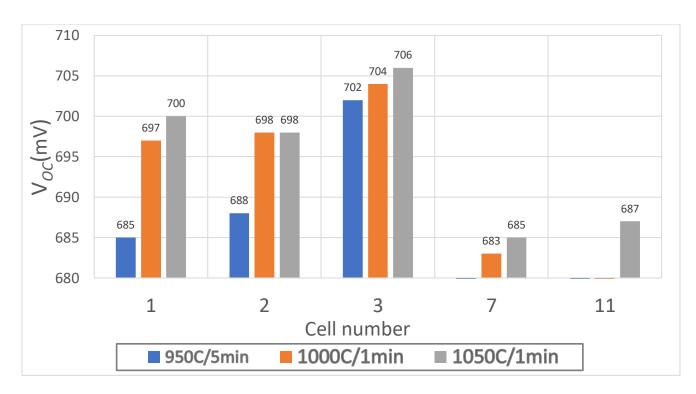

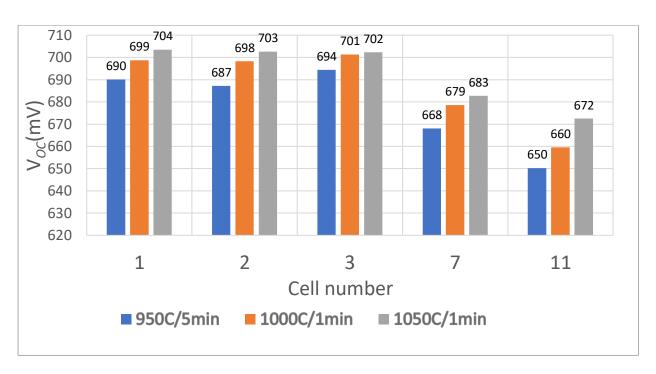

Suns- $V_{OC}$  measurement is also performed after the fabrication of the cells to compare it with  $V_{OC}$  results and evaluate the series resistance, see Figure (4.3) and (4.4). Firstly, Suns- $V_{OC}$  measurement is carried out to make advantage of estimating the maximum  $V_{OC}$  and FF since this measurement excludes the effect of the series resistance, thus the difference between pFF and -FF represents a good indicator of the carrier transportation quality in terms of the series resistance [37]. Figures (4.3) and (4.4) illustrate the results obtained for cells 1, 2, and 3, and compare them to the same cells of the other wafers with the same metal gird fraction but annealed at different conditions. The output of the measurement shows that the highest Suns- $V_{OC}$  obtained is 718 mV for cell number 3 annealed at

1050°C/1min condition whereas for the same cell at annealing condition of 950°C/5min it reaches 710 mV, the minimal value obtained was 708 mV for cell number 2 annealed at 950°C/5min. The outcomes show increasing in the Suns-V<sub>OC</sub> by raising the annealing temperature which is consistent with the passivation quality test result performed in chapter 3. The pseudo fill factor measured reaches 83.1% for the cell number 2 annealed at 1050°C/1min while the lowest value was 80.5% for the cell number 1 annealed at 950°C/1min condition. It is noticeable that cells annealed at 950°C/5min and 1000°C/1min conditions have very close results while the samples annealed at 1050°C/1min show the best outcome and the maximum  $\Delta FF$  does not exceed 3% between the top and lowest obtained pFF which is also consistent with the result of iFF of the cell's precursors shown in figure (4.2).

Figure (4.3) results of Suns-V<sub>OC</sub> measurement, the V<sub>OC</sub> for cells number(1,2,3) from three wafers annealed at different conditions(950°C/5min, 1000°C/1min, and 1050°C/1min).

Figure (4.4) results of Suns- $V_{OC}$  measurement, the pFF for cells number(1,2,3) from three wafers annealed at different conditions(950°C/5min, 1000°C/1min, and 1050°C/1min).

#### 4.4 I-V measurement:

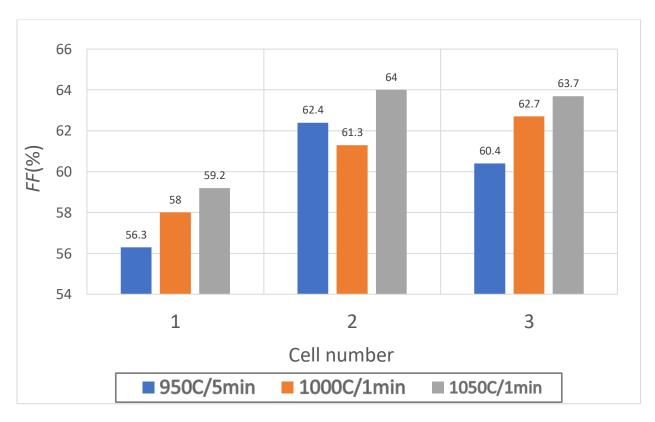

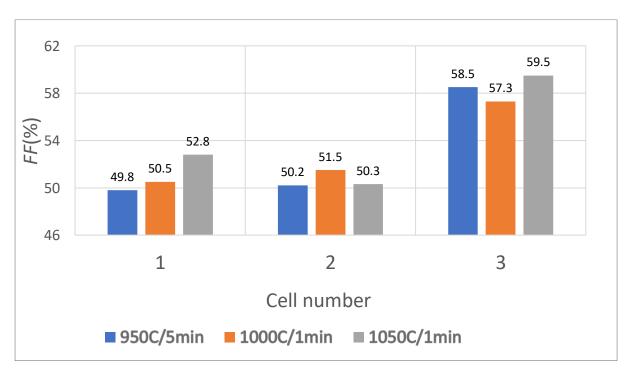

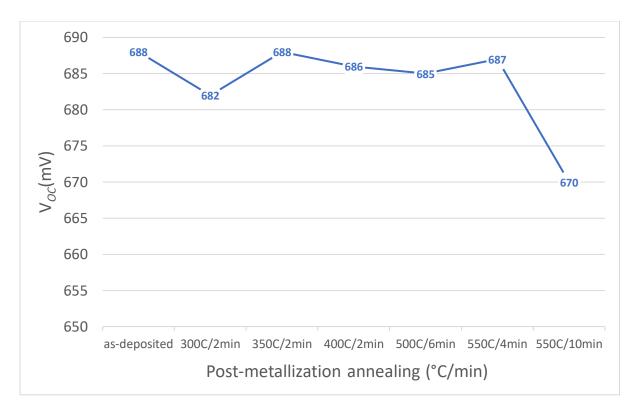

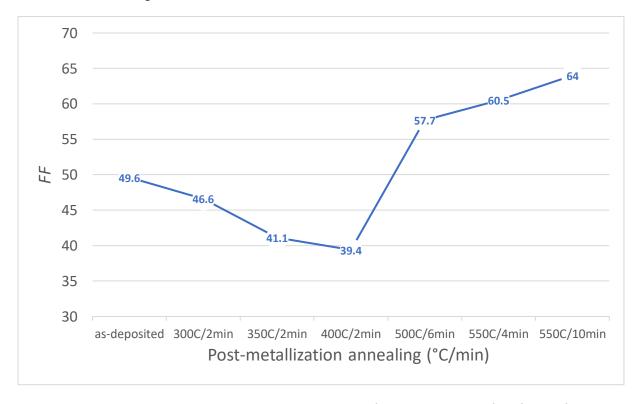

The next step was to measure the J-V curve to characterize the  $V_{OC}$  and the FF of the fabricated cells with Silver back contacts, the output is plotted in figures (4.5) and (4.6) consequently. The results obtained of  $V_{OC}$  values in a trend similar to the Suns- $V_{OC}$  measurement. 706 mV of cell number 3 annealed at  $1050^{\circ}$ C/1min condition is the highest  $V_{OC}$  achieved whereas cells annealed at  $950^{\circ}$ C/5min and  $1000^{\circ}$ C/1minconditions record 702,704 mV consequently. Cells number 3 have a higher metal cover percentage than cells number 2 and 1 thus they have higher FF due to lower series resistance. Surprisingly, Cells number 3 also show higher  $V_{OC}$  even though they have higher metal coverage which causes more shading, but the result shows that they have higher FF which can be attributed to more light absorption due to none-ideal coverage of the rest cells during the measurement since we cover the rest cells manually by black paper. However, designing the metal grid has an important influence on both FF and  $V_{OC}$  as many factors compete with each other,i.e increasing the metal width reduces the series resistance but on the other hand, it increases the shading, therefore, an optimal has to be found to achieve the highest conversion efficiency [6].

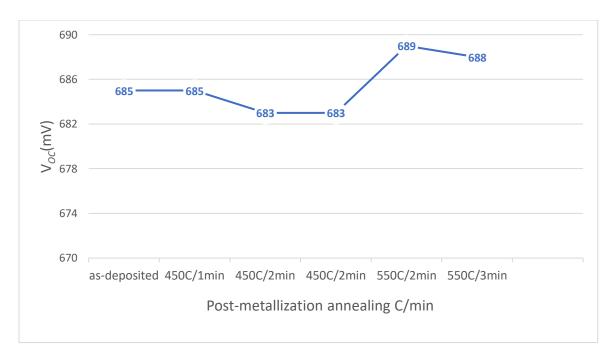

Comparing the values are obtained for the fill factor which is in the range between 56% and 64%, with the pseudo fill factor which is over 80%. A huge reduction in the fill factor is observed which indicates a large series resistance that hinders the current flow from the bulk to the metal contacts. The resistivity between the metals and the poly-Si is part of this resistance, remark was made by another