DELFT UNIVERSITY OF TECHNOLOGY Faculty of Electrical Engineering, Mathematics and Computer Science

MASTERS'S THESIS

## Evaluation of advantageous modulation methods for a dual active bridge converter with a wide output voltage range

July 21, 2022

Author: C.A Straathof

Jury: Prof.dr.ir. P. Bauer (Chair) Dr.ir. Z. Qin (Supervisor) Dr.ir. R. Santbergen Student number: 4557352

Daily supervisor: Dingsihao Lyu

## Abstract

In this thesis two new modulation methods are proposed for a wide output voltage range dual active bridge (DAB) converter for bidirectional EV charging application. The objective of the proposed modulation method is to maximize the number of ZVS events over the operating range, while maintaining low current stress. The first modulation method achieves this with fixed a switching frequency, while the second achieves full ZVS operation using a variable switching frequency combined with alternative charging profiles. The design of the modulation method is done through an analysis of the operating modes and the ZVS behaviour of the DAB converter. To verify the improvements to the ZVS behaviour of the proposed modulation method, the modulation method is implemented in a simulation and on an 11 kW prototype with an input voltage range of 640 to 840 V, and an output voltage range from 250 to 1000 V, to ensure compatibility with various types of EV's. A control system and a transient mitigation method are designed to facilitate the experimental verification. The proposed modulation method is compared to a peak current optimization for the DAB converter found in the literature. Measurements done on the 11 kW prototype confirm that the improvements in ZVS are achieved. These improvements in ZVS of the proposed modulation method also result in increased efficiency compared to the peak current optimization, especially in the low-power operating regions. The full power efficiency over the entire voltage range of the peak current optimization, the proposed fixed frequency, and the proposed variable frequency modulation are 97.895%, 97.879% and 97.964% respectively.

## Acknowledgments

First of all, i would like to thank Yang for helping me find an interesting thesis topic after after my previously selected topic suddenly became unavailable. This brought me into contact with Dingsihao, who proposed this interesting topic. I enjoyed working with him and appreciate his supervision, especially during the testing period. His feedback in the writing process is also greatly appreciated. I would also like to thank my official supervisor Dr.ir. Zian Qin for making this thesis possible. I am also grateful to Thiago for having designed the PCB used for testing, and to Joris and Mladen for their assistance in creating a functional prototype.

> Coen Straathof July 2022

# Contents

| 1        | $\mathbf{Intr}$ | Introduction 6                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|          | 1.1             | Objectives & requirements                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|          | 1.2             | Thesis Structure    7                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| <b>2</b> | Ana             | Analysis of DAB modulation methods 8                                                                                                                        |  |  |  |  |  |  |  |  |  |

|          | 2.1             | DAB converter operation                                                                                                                                     |  |  |  |  |  |  |  |  |  |

|          | 2.2             | modulation methods                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|          |                 | 2.2.1 EPS and DPS modulation                                                                                                                                |  |  |  |  |  |  |  |  |  |

|          |                 | 2.2.2 TPS modulation $\ldots \ldots \ldots$ |  |  |  |  |  |  |  |  |  |

|          |                 | 2.2.3 Hybrid modulation methods                                                                                                                             |  |  |  |  |  |  |  |  |  |

|          | 2.3             | General ZVS conditions                                                                                                                                      |  |  |  |  |  |  |  |  |  |

|          |                 | 2.3.1 Single half bridge                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|          |                 | 2.3.2 Both half-bridges $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $14$                                                                          |  |  |  |  |  |  |  |  |  |

|          |                 | 2.3.3 Cases involving both H-bridges                                                                                                                        |  |  |  |  |  |  |  |  |  |

|          | 2.4             | Proposed modulation method                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.4.1 EPS ZVS boundaries                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|          |                 | 2.4.2 mode 1 TPS ZVS boundaries                                                                                                                             |  |  |  |  |  |  |  |  |  |

|          |                 | 2.4.3 Resulting control law                                                                                                                                 |  |  |  |  |  |  |  |  |  |

|          |                 | 2.4.4 Overall ZVS performance                                                                                                                               |  |  |  |  |  |  |  |  |  |

|          | 2.5             | Transient Behaviour                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|          |                 | 2.5.1 Zero current regions                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.5.2 Magnetizing current                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|          | 2.6             | ZVS range extention                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|          |                 | 2.6.1 Variable frequency operating modes                                                                                                                    |  |  |  |  |  |  |  |  |  |

|          |                 | 2.6.2 Modified EPS modulation                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 3        | $\mathbf{Sim}$  | ulation 27                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|          | 3.1             | Hardware modelling                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|          |                 | 3.1.1 Transformer and inductor model                                                                                                                        |  |  |  |  |  |  |  |  |  |

|          |                 | 3.1.2 Mosfet model                                                                                                                                          |  |  |  |  |  |  |  |  |  |

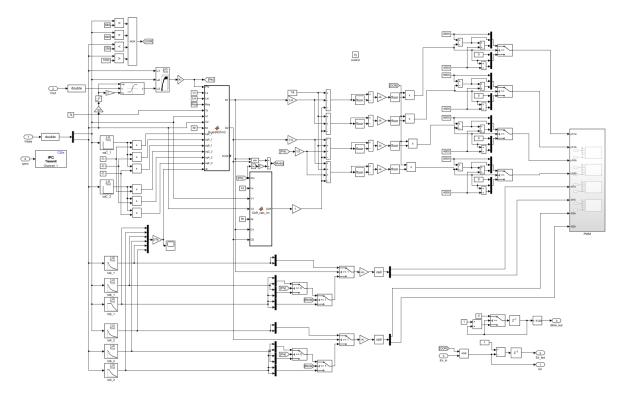

|          | 3.2             | Controller                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|          |                 | 3.2.1 Duty cycle & offset calculation                                                                                                                       |  |  |  |  |  |  |  |  |  |

|          |                 | 3.2.2 PWM generation                                                                                                                                        |  |  |  |  |  |  |  |  |  |

|          |                 | 3.2.3 Dead-time Calculation                                                                                                                                 |  |  |  |  |  |  |  |  |  |

|          |                 | 3.2.4 Outer Controller                                                                                                                                      |  |  |  |  |  |  |  |  |  |

|          | 3.3             | Non-ideal converter behaviour                                                                                                                               |  |  |  |  |  |  |  |  |  |

|          |                 | 3.3.1 Junction capacitor non-linearity                                                                                                                      |  |  |  |  |  |  |  |  |  |

|          |                 | 3.3.2 Magnetizing current                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|          |                 | 3.3.3 MOSFET and transformer resistance                                                                                                                     |  |  |  |  |  |  |  |  |  |

|          |                 | 3.3.4 Switch capacitance & dead-time                                                                                                                        |  |  |  |  |  |  |  |  |  |

|          | 34              | Modified control function 39                                                                                                                                |  |  |  |  |  |  |  |  |  |

|              |      | 3.4.1    | Variable frequency control modifications                                                                                                              |

|--------------|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 3.5  | Simula   | tion results $\ldots \ldots 41$       |

|              |      | 3.5.1    | Transient behaviour                                                                                                                                   |

|              |      | 3.5.2    | compensation effects                                                                                                                                  |

| 4            | Pra  | ctical i | mplementation 44                                                                                                                                      |

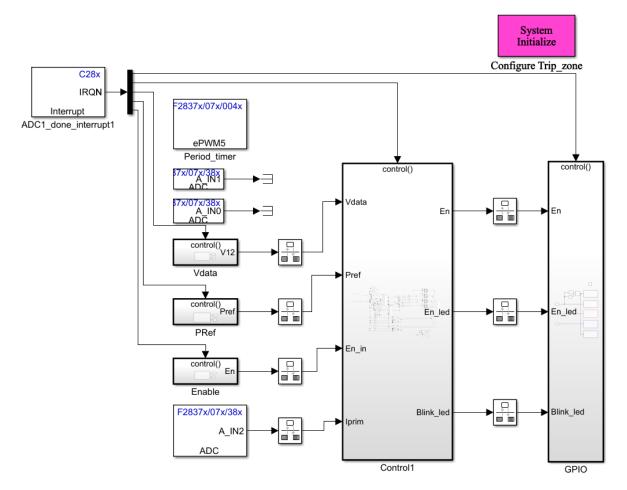

|              | 4.1  | Contro   | l system implementation $\ldots \ldots 45$                                      |

|              |      | 4.1.1    | System timer and interrupt routine                                                                                                                    |

|              |      | 4.1.2    | Enable implementation 45                                                                                                                              |

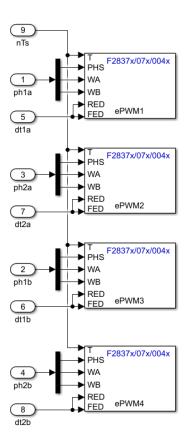

|              |      | 4.1.3    | PWM implementation                                                                                                                                    |

|              | 4.2  | Hardw    | are considerations $\ldots \ldots 46$                      |

|              |      | 4.2.1    | Approximate turns ratio Optimization                                                                                                                  |

|              |      | 4.2.2    | Transistor selection                                                                                                                                  |

|              |      | 4.2.3    | Loss based optimization                                                                                                                               |

|              |      | 4.2.4    | Magnetic design                                                                                                                                       |

|              |      | 4.2.5    | Efficiency estimation                                                                                                                                 |

| <b>5</b>     | Test | t result | s 53                                                                                                                                                  |

|              | 5.1  | Test se  | tup                                                                                                                                                   |

|              | 5.2  | ZVS B    | ehavior                                                                                                                                               |

|              |      | 5.2.1    | Comparison of the ideal and proposed triangular region 54                                                                                             |

|              |      | 5.2.2    | ZVS performance around the transition region                                                                                                          |

|              |      | 5.2.3    | Unity voltage gain behaviour                                                                                                                          |

|              |      | 5.2.4    | High voltage operation                                                                                                                                |

|              |      | 5.2.5    | Unexpected non-ZVS behaviour                                                                                                                          |

|              |      | 5.2.6    | Variable switching frequency modulation ZVS behaviour                                                                                                 |

|              | 5.3  | Transie  | ent Behaviour                                                                                                                                         |

|              | 5.4  | Conver   | ter efficiency $\ldots \ldots \ldots$ |

| 6            | Con  | clusion  | 66                                                                                                                                                    |

|              | 6.1  | future   | work                                                                                                                                                  |

| $\mathbf{A}$ | Con  | troller  | implementation 68                                                                                                                                     |

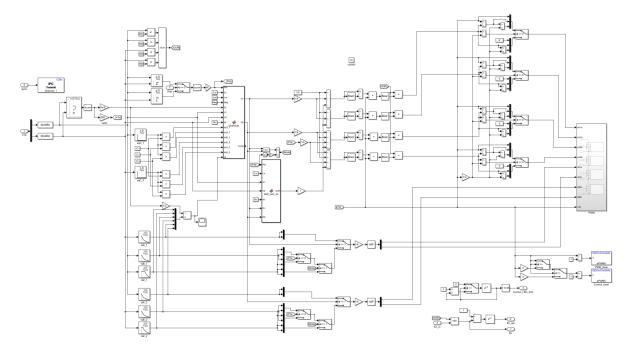

|              | A.1  | Simulii  | 1k model                                                                                                                                              |

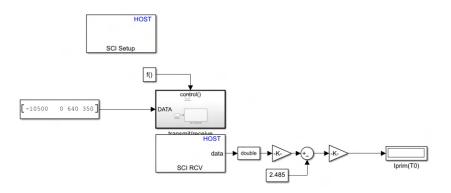

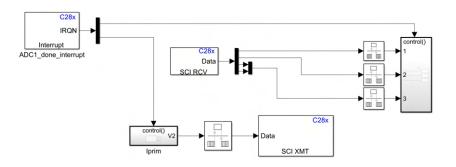

|              |      | A.1.1    | Communication                                                                                                                                         |

|              |      | A.1.2    | Controller model                                                                                                                                      |

|              | A.2  | Offset   | calculation code                                                                                                                                      |

|              | A.3  | Contro   | l function code                                                                                                                                       |

|              |      | A.3.1    | Control function for the peak current optimization                                                                                                    |

|              |      | A.3.2    | Control function for the proposed fixed frequency modulation 73                                                                                       |

|              |      | A.3.3    | Control function for the variable switching frequency modulation 75                                                                                   |

## List of Abbreviations

| Abbreviation | Explanation                |

|--------------|----------------------------|

| DAB          | Dual Active Bridge         |

| ZVS          | Zero Voltage Switching     |

| ZCS          | Zero Current Switching     |

| CV           | Constant Voltage           |

| CC           | Constant Current           |

| MSCC         | Multistep Constant Current |

| ESS          | Energy Storage Systems     |

| EV           | Electric Vehicle           |

| SPS          | Single Phase Shift         |

| EPS          | Extended Phase Shift       |

| DPS          | Dual Phase Shift           |

| TPS          | Triple Phase Shift         |

Table 1

## Chapter 1

# Introduction

To reduce the effects of climate change, the need to reduce greenhouse gas emissions arises. In applications like transportation and heating of homes, which have a significant contribution to global greenhouse gas emissions, efforts are being made to replace fossil fuels with electricity as an energy source. In the field of transportation this is mainly done through electric vehicles (EV) and public transportation, while for heating, solutions like heat pumps, or usage of industrial waste heat are common.

Due to the intermittent nature of renewable energy sources, Energy storage systems (ESS) are required to stabilize the electricity grid. Battery energy storage, which has a rapid response time and good efficiency is a promising solution for dealing with the short term energy imbalance. To reduce the total amount of resources required for the ESS, EV batteries can be used to support the grid. This would introduce a large amount of additional energy storage that will be available for the majority of the day, as most EV's will only be used for a few hours each day.

To achieve this, both the EV charger and the EV itself need to be capable of bidirectional power transfer. For people to interact with the charger system safely, galvanic isolation is a necessary feature for the system. This is typically achieved through a transformer, working at 50 Hz, or at a higher frequency as part of a power converter. The higher frequency operation of the transformer in such converters allows for much smaller transformers at the same power rating, and is thus preferred over a 50 Hz transformer. Among different brands of EV's, battery voltage ranging from 320 to 800 V can be found [18]. To ensure that the charger is compatible with all vehicle types it should have a wide output voltage range.

To achieve bidirectional isolated DC/DC conversion, multiple converter topologies can be used. The dual active bridge (DAB) and CLLLC resonant DAB topologies are suitable for EV charging application, as they have high power density, efficiency [7, 24]. Given that correct control strategies are used, both converter types are capable of zero voltage and/or zero current switching, providing a significant reduction in switching losses compared to hard switched converters. When considering the DAB and resonant converter for EV charging application, in a design with a single DC-DC converter, the phase shift based DAB performs better as it can handle a wider voltage range and has a faster dynamic response than the CLLLC resonant converter [24]. Alternatively a design with two DC-DC stages could be used with either the DAB or resonant converter, where a buck or boost stage is added to extend the voltage range. However, as this increases the part count and design complexity, a single stage DAB is chosen for this application.

When charging a battery, the charging process can affect the useful life of the battery. The most basic charging method charges the battery using a constant current, until the battery voltage reaches an upper limit, after which the battery will be charged at a constant voltage (CC-CV) [14]. Alternatively the charging current can be reduced in steps (MSCC) [14], which

has the potential to achieve higher efficiency, as individual DC/DC converters can be shut down allowing the others to operate closer to their optimal operating region. Alternative methods like pulsed charging [14, 1] can also be used, providing a similar advantage as MSCC, where the converter can operate in its optimal operating region. Pulsed charging also offers benefits to battery life [1], however this method can also have a negative impact on the electricity grid [14].

## 1.1 Objectives & requirements

The goal of this thesis is to design a control system for a wide output voltage range DAB converter for EV charging application. The focus will be on the modulation, however other parts of the control system should also be considered. The control system should improve the ZVS behaviour and efficiency of the converter, which is mainly affected by the modulation method. It should also take into account the transient behaviour of the converter, as large DC offsets or saturation are not desirable. The requirements for the for the DAB converter are shown below:

- An input voltage range from 640 V to 840 V

- An output voltage range from 250 V to 1000 V

- A maximum output power of 11 kW

- A maximum DC current of 30 A

- Bidirectional power transfer

To verify whether the control system actually provides an improvement, it should be compared to a control system using an already existing modulation method to observe whether the ZVS behaviour and efficiency have improved. In addition to this, tests should be performed to observe the transient performance of the converter.

## 1.2 Thesis Structure

To start the design of the control system, first a literature study regarding the DAB converter and its modulation methods will be performed. This is discussed in chapter 2, together with the analysis of the ZVS requirements and transient behaviour. This chapter will also introduce the new modulation and transient mitigation methods proposed in this thesis, which improves the DAB converters ZVS behaviour over the operating range, while retaining low current stress.

Based on the theoretical analysis done for the control system, a simulation will constructed to verify the functionality of the control system. Problems arising from the simulation will be addressed when necessary. Chapter 3 will discuss the simulation and it's results.

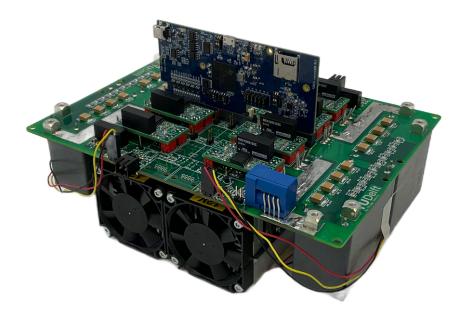

In chapter 4, the practical implementation of the converter and its control system will be discussed. This includes the implementation of key parts of the control system on a TMS320F28379D microcontroller, the selection of the switches, and the design of the transformer and inductor. Specific details about the implementation of the control system on the microcontroller can be found in the appendix. Based on the designed hardware, and the control system, an estimate of the converters efficiency over the operating range is made.

Finally, the constructed converter will be used to test the proposed modulation methods and transient mitigation method. The results of these test are discussed in chapter 5.

## Chapter 2

# Analysis of DAB modulation methods

## 2.1 DAB converter operation

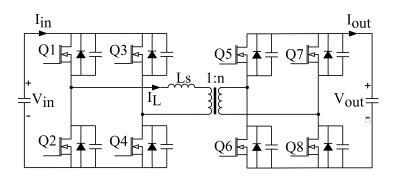

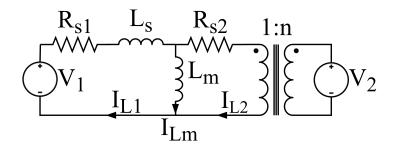

The DAB converter consists of two H-bridges, with a transformer that has a relatively large leakage inductance, as shown in figure 2.1. In this circuit the magnetizing inductance is neglected, as it is typically significantly larger than the leakage inductance thus limiting its influence on converter behaviour. Each half-bridge in the circuit operates at a 50% duty cycle. Below the parameters that can be manipulated to control the converter are listed.

- $-1 < \Phi < 1$ , the normalised phase shift between the two H-bridges.

- $0 < D_1 < 1$ , the effective duty cycle of the left H-bridge.

- $0 < D_2 < 1$ , the effective duty cycle of the right H-bridge.

- $T_s$ , the sample time, which equals  $\frac{1}{f_s}$

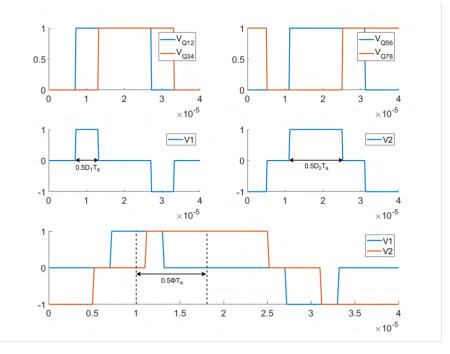

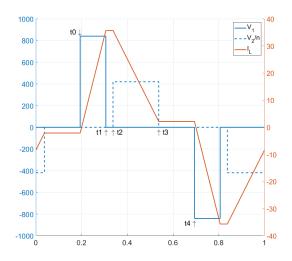

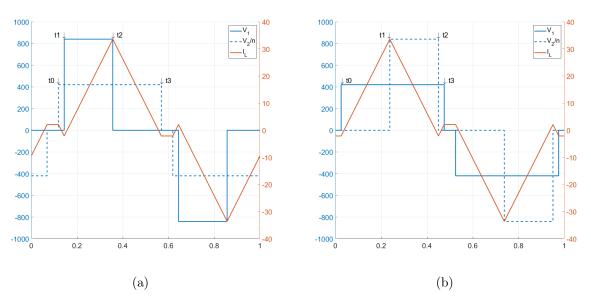

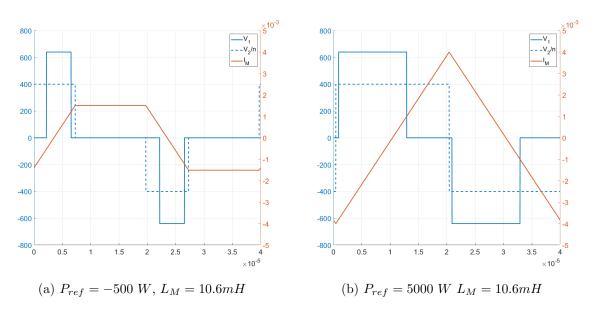

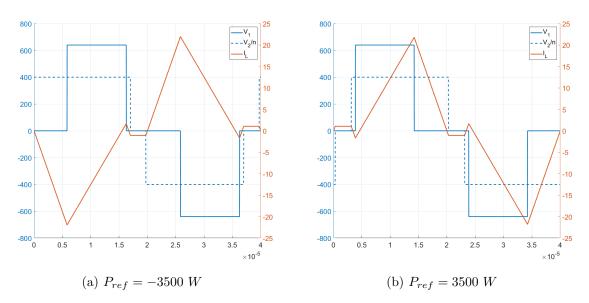

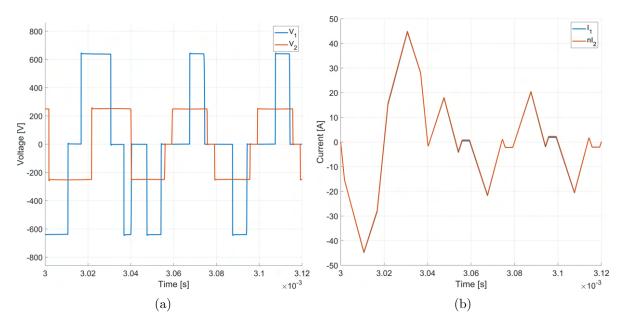

Figure 2.2 shows the voltage waveform of a single switching period at 25 kHz to clarify the parameters listed above. The effective duty cycle  $D_1$  and  $D_2$ , which can be observed in the output voltage waveforms of the primary and secondary H-bridge (V1 and V2), are implemented through the phase shift between the half bridges ( $V_{Qxx}$ ) in the H-bridge.  $\Phi$ , the phase shift between the primary and secondary H-bridge, and is defined from the centre of the voltage waveforms.

$\Phi$  is the main control parameter of the DAB converter, determining the direction of power flow and affecting its magnitude. By manipulating  $D_1$  and  $D_2$ , the magnitude of the power flow can be altered, and the ZVS range can be extended. This is done in various modulation methods like extended (EPS), dual (DPS) and triple phase shift (TPS) modulation [15]. Finally there is the switching frequency, which has an inversely proportional relationship with the transferred power. It can potentially be used to optimize the performance at different voltage levels, or different loads.

### 2.2 modulation methods

In literature various modulation methods can be found. The most simple modulation method is single phase shift modulation, where only  $\Phi$  is manipulated. At unity voltage gain, it provides ZVS over the most of the operating range. However at non-unity voltage ratio the ZVS

Figure 2.1: Circuit of the DAB converter

Figure 2.2: Voltage waveforms for  $\Phi = 0.4$ ,  $D_1 = 0.3$  and  $D_2 = 0.7$

range is limited at lower loads, and current stress is high compared to more advanced modulation methods [15]. This makes it unsuitable for wide voltage range applications like EV charging.

#### 2.2.1 EPS and DPS modulation

To improve the modulation, a second control parameter can be used, which is done in EPS modulation and DPS modulation. Here both  $\Phi$ ,  $D_1$  and  $D_2$  can be manipulated with some restrictions. In the case of EPS modulation, only  $D_1$  or  $D_2$  can be manipulated while the other is set equal to 1, depending on the voltage ratio. For DPS modulation  $D_1$  is set equal to  $D_2$ . This limits the number of control variables to 2.

For both modulation types, the power range where ZVS applies is extended due to the additional control parameters, however they do not provide full range ZVS when considering the switch junction capacitors. Between EPS and DPS modulation, EPS modulation generally performs better as it has reduced current stress compared to DPS modulation [16]. The exception to this is at very low power, where the small duty cycle in both H-bridges occurring in DPS modulation reduces the reactive power in the inductor compared to EPS modulation where one H-bridge will operate a duty cycle of 1. To resolve the issue regarding the limited ZVS range, in [22] and [20] for EPS modulation, and [13] for DPS modulation, the ZVS range is expanded to the full operating range by making use of the magnetizing current of the transformer. This is implemented by designing the transformer to have a smaller magnetizing inductance. When comparing the two modulation methods, EPS again has an advantage as it requires a much smaller magnetizing current compared to DPS modulation to obtain full ZVS range. The main cause of this difference is that the ZVS range of EPS modulation without magnetizing inductance only has a small non-ZVS gap in the power range when transitioning between operating modes [22], while DPS modulation loses ZVS in the entire low power operating range [13]. Modulation techniques that rely on magnetizing inductance are considered to be less desirable compared to other methods, as the additional magnetizing current results in more conduction losses.

Instead of using the magnetizing inductance, which results in additional conduction losses, it is also possible to manipulate the switching frequency to bridge the gap in power between the two ZVS regions [6]. Although the control complexity is higher compared to the magnetizing current method, it has the potential of achieving higher efficiency. The lowered switching frequency needed the low power switching region also has the advantage of decreasing the switching losses in this region.

In [25] a variation of EPS is discussed, where asymmetric pwm is used to reduce rms current and expand the ZVS range. Although such a method has the potential to extend the ZVS range, the DC offset is problematic, and requires a series capacitor to prevent saturation of the transformer. This is a disadvantage as a series capacitor results in additional conduction losses, and larger converter size.

#### 2.2.2 TPS modulation

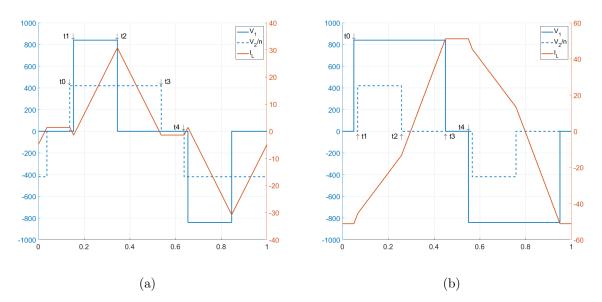

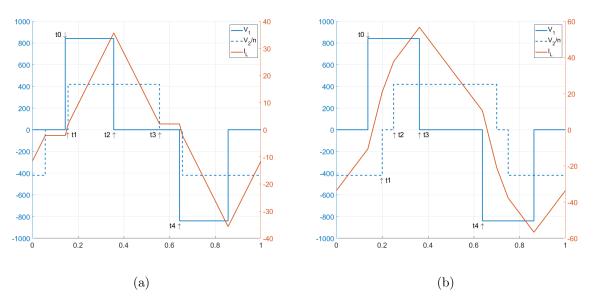

By allowing the duty cycle of both H-bridges to be controlled separately, it is possible to control the DAB converter in a more optimal way than when using EPS or DPS modulation, as EPS and DPS modulation in essence variants of TPS with certain restrictions applied to it for the purpose of reducing complexity. In [5] twelve operating regions are derived for TPS modulation. Removing mirrored operating modes, and the obsolete operating modes with  $\Phi = \pm 1$ , five operating modes remain [10, 19, 11]. Table 2.1 shows the boundaries of these operating modes. The waveforms corresponding to the operating modes are shown in figure 2.3, 2.4 and 2.5.

| Mode | Condition 1                              | Condition 2                                                           | ZVS turn-on (max) |

|------|------------------------------------------|-----------------------------------------------------------------------|-------------------|

| 1    | $\frac{ D_2 - D_1 }{4} > \frac{\Phi}{2}$ | $sign(D_2 - D_1) = sign(V_1 - V_2)$                                   | 8/8               |

| 2    | $\frac{ D_2 - D_1 }{4} > \frac{\Phi}{2}$ | $sign(D_2 - D_1) = sign(V_2 - V_1)$                                   | 6/8               |

| 3    | $\frac{ D_2 - D_1 }{4} < \frac{\Phi}{2}$ | $\frac{\Phi}{2} < \frac{D_2 + D_1}{4} < \frac{1}{2} - \frac{\Phi}{2}$ | 6/8               |

| 4    | $\frac{D_1 + D_2}{4} > \frac{\Phi}{2}$   | $\frac{D_1+D_2}{4} > \frac{1}{2} - \frac{\Phi}{2}$                    | 8/8               |

| 5    | $\frac{D_1 + D_2}{4} < \frac{\Phi}{2}$   | $\frac{D_1+D_2}{4} < \frac{1}{2} - \frac{\Phi}{2}$                    | 6/8               |

Table 2.1: Limits of each operating mode

#### **TPS** optimization

As the most flexible among the modulation methods, TPS modulation can be optimized for minimum peak or rms current or minimum reactive power. In [5] and [10] a minimum peak current optimization is done, this results in 2 operating regions, which naturally transition into each other.

At low power, the peak current has the lowest value when operating at the boundary between mode 1 and 3 of TPS, where the duty cycles are proportional to the voltage ratio. As the current

Figure 2.3: TPS mode 1 & 2

Figure 2.4: TPS mode 3 & 4

waveform resembles a triangular shape, it is also called ideal triangular modulation. At higher power, the peak current is minimized when operating with a duty cycle of 1 on the H-bridge with lower voltage, which is equivalent to EPS modulation. A similar modulation method is derived in [19], by first removing the non-ideal operating modes, and finding the minimum rms current through analytical means.

As discussed in [10] and [19], it is possible to achieve full soft-switching using these methods. While operating at higher power in the EPS region, full ZVS can be achieved. When the power is decreased, the converter will start to operate using ideal triangular modulation. As 6 out of 8 switching events will switch with zero current, ZVS will be lost for these switching events, in return ZCS is obtained, compensating the lack of ZVS to a certain degree.

A further improvement has been made to the soft switching in [11], where a slow control loop optimizes  $D_1$  and  $D_2$  for increased steady state efficiency with a peak current optimization

Figure 2.5: TPS mode 5

as a reference. As a result the triangular operation is shifted into the mode 1 TPS region at low power, as switching losses are reduced here due to increased number of ZVS events. Although this controller does maximize the efficiency, it has a slow dynamic response and its implementation is fairly complex. It also requires high speed voltage and current sensors on the input to measure the efficiency.

#### 2.2.3 Hybrid modulation methods

Instead of following a complex optimization process, it is also possible to combine multiple different modulation techniques. The modulation techniques used are typically fairly simple in implementation, but not fully optimized for minimum current or ZVS.

The most basic hybrid modulation methods simply combine two different modulation techniques. For example in [23] and [26] a combination of SPS and a modified triangular modulation modulation with higher maximum power than normal triangular modulation is proposed. This allows the system to maintain soft switching in a relatively large part of the operating range. This comes at the cost of increased rms current, as the proposed modified triangular modulation has high circular current.

A more optimal hybrid modulation is proposed in [8], utilizing SPS in its ZVS range. Once the limit of the ZVS range has been reached, the duty cycle of the higher voltage bridge will decrease until the ratio between voltage and duty cycles is equal, this operating region can be implemented as a specific case of EPS modulation. The low power boundary of this region coincides with the maximum power of triangular modulation, which is used at even lower power. Although it doesn't provide full range ZVS, it does provide ZCS where ZVS is absent. Compared to the previously discussed TPS modulation methods, it has increased conduction and switching losses, but its implementation is very simple.

The efficiency of the above methods could be enhanced by providing a small duty cycle offset similar to what is done for trapezoidal modulation in [21]. This would provide more ZVS events compared to the original methods, although it does increase the complexity of the modulation techniques by a certain degree.

## 2.3 General ZVS conditions

To achieve ZVS in a DAB converter, the energy stored in the leakage inductance should be greater or equal to the energy required to fill or empty the junction capacitance of the switches, and the energy to overcome the voltage applied on  $L_s$  by the non-switching H-bridge. A similar ZVS analysis has been done for EPS modulation in [22] and [20], and for DPS modulation in [13]. However, as these are restricted to EPS and DPS modulation respectively, they do not cover all types of switching events. Given the variety of modulation techniques that will be considered, in this subsection, the general ZVS conditions with the minimum or maximum inductor current as the output value will be derived.

To simplify the calculation the voltage applied on the inductor by the input side H-bridge is defined as  $V_1$ , The voltage applied to the inductor by the output side H-bridge is defined as  $V_2$ .  $V_1$  can be  $\pm V_{in}$  or 0,  $V_2$  can be  $\pm V_{out}$  or 0, depending on the control signals sent to the switches of both H-bridges.

Different switching events can be considered. First is the single H-bridge, which can either be switched to or from a state where the output of the H-bridge is 0. This affects the contribution of the output of the non-switching H-bridge to the ZVS requirement. There is also the case where  $D_1$  or  $D_2$  is equal to one, where both half bridges in the same H-bridge switch at the same time. It is also possible to have multiple half bridges in a different H-bridge switch at the same time.

#### 2.3.1 Single half bridge

The first two cases consider the switching of only a single half bridge, either entering or leaving the zero voltage state of the H-bridge. This can occur in all four half bridges, but the ZVS requirements use the same equations. Figure 2.6 shows the equivalent circuits for both cases of a single bridge switching. The calculations will assume the circuit is lossless, thus in practice some safety margin may be needed.

Figure 2.6: Equivalent circuits for transitions from  $V_{in}$  to 0 and from 0 to  $V_{in}$

To derive the necessary inductor current, the energy stored in the capacitors and inductor, and the energy consumed by the secondary side voltage will be considered. When switching from a zero state to a positive or negative state, the inductor needs to provide energy for the capacitors, which may be reduced if the voltage applied by the non switching H-bridge also supplies energy. The energy equation for the input bridge switching from the 0 to the positive  $V_{in}$  state is shown in 2.1, which results in equation 2.2 when solved for the inductor current. In these equations  $E_C$  represents the energy needed to change the capacitor voltage, while  $E_V = Q_c V$ represents the energy provided by the non-switching H-bridge.

$$E_L = E_C - E_V = C_j V_{in}^2 - 2C_j V_{in} \frac{V_2}{n}$$

(2.1)

$$I_L = -V_{in} \sqrt{\frac{2C_j}{L} (1 - 2\frac{V_2}{nV_{in}})} \qquad \frac{V_2}{nV_{in}} < 0.5$$

(2.2)

The same principle can be used for switching from a positive state to a 0 state of the H-bridge, however in this case the capacitor contains more energy initially compared to the final state, which leads to a different leads to a different ZVS requirement. The energy equation for this case is shown in equation 2.3, which results in equation 2.4 when solved.

$$E_L = E_V - E_C = 2C_j V_{in} \frac{V_2}{n} - C_j V_{in}^2$$

(2.3)

$$I_L = V_{in} \sqrt{\frac{2C_j}{L} (2\frac{V_2}{nV_{in}} - 1)} \qquad \qquad \frac{V_2}{nV_{in}} > 0.5$$

(2.4)

In the above calculations, only positive voltage switching has been considered in the input side H-bridge. In the output side H-bridge, the transformer turns ratio results causes some minor differences in the equation. The equations thus need to be modified to work for both polarities and for the secondary H-bridge, which is done using the same steps as for the above cases. The results of this process are shown in table 2.2.  $\Delta V_{1/2}$  in these equations is the change in voltage of the switching H-bridge, which equals the DC voltage on the switching side multiplied by the switching direction. The voltage of the non switching side,  $V_{1/2}$  is the output voltage of the secondary H-bridge, which can be either  $\pm V_{in/out}$  or 0.

| Bridge 1 switching (0 to $\pm V_{in}$ )                             |                                                                                |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------|

| $\frac{V_2}{n\Delta V_1} < 0.5$                                     | $I_{L-lim} = -\Delta V_1 \sqrt{\frac{2C_j}{L} (1 - 2\frac{V_2}{n\Delta V_1})}$ |

| $\frac{V_2}{n\Delta V_1} \ge 0.5$                                   | $I_{L-lim} = 0$                                                                |

| Bridge 1 switching $(\pm V_{in} \text{ to } 0)$                     |                                                                                |

| $\frac{V_2}{n\Delta V_1} > 0.5$                                     | $I_{L-lim} = -\Delta V_1 \sqrt{\frac{2C_j}{L} (2\frac{V_2}{n\Delta V_1} - 1)}$ |

| $\frac{\frac{n \Delta V_1}{V_2}}{\frac{V_2}{n \Delta V_1}} \le 0.5$ | $I_{L-lim} = 0$                                                                |

| Bridge 2 switching (0 to $\pm V_{out}$ )                            |                                                                                |

| $\frac{nV_1}{\Delta V_2} < 0.5$                                     | $I_{L-lim} = \Delta V_2 \sqrt{\frac{2C_j}{L} (1 - 2\frac{nV_1}{\Delta V_2})}$  |

| $\frac{nV_1}{\Delta V_2} \ge 0.5$                                   | $I_{L-lim} = 0$                                                                |

| Bridge 2 switching $(\pm V_{out} \text{ to } 0)$                    |                                                                                |

| $\frac{nV_1}{\Delta V_2} > 0.5$                                     | $I_{L-lim} = \Delta V_2 \sqrt{\frac{2C_j}{L} (2\frac{nV_1}{\Delta V_2} - 1)}$  |

| $\frac{nV_1}{\Delta V_2} \le 0.5$                                   | $I_{L-lim} = 0$                                                                |

Table 2.2: ZVS conditions for single switching events

#### 2.3.2 Both half-bridges

The other cases involve both half bridges in an H-bridge switching at the same time. This only occurs during EPS and SPS modulation when switching from the negative state of the H-bridge to a positive one, or reversed. the energy stored in the capacitors of the one H-bridge can flow

into the capacitors of the other H-bridge. Given that the capacitor energy is already present, the energy absorbed or delivered by the secondary side voltage is the only contributing factor to the ZVS conditions. The same energy equation as for the single half bridge switching events is used, as shown in equation 2.5, based on figure 2.7.

$$Q_c = 2V_1 C_j \qquad E_{V2} = Q_c * \frac{V_2}{n} = 2V_{in} C_j \frac{V_2}{n} \qquad E_L = \frac{1}{2} L_s I_L^2 \qquad (2.5)$$

Solving these equations for I leads to the minimum amplitude of the inductor current shown in table 2.3, the amplitude for the secondary side H-bridge is calculated using the same method from the secondary side of the transformer.

| Bridge 1 switching          |                                                                                        |

|-----------------------------|----------------------------------------------------------------------------------------|

| $\Delta V_{in} * V_2 < 0$   | $I_{L-lim} = \frac{V_2}{n} \sqrt{\frac{4C_j}{L_s}} \left  \frac{nV_{in}}{V_2} \right $ |

| $\Delta V_{in} * V_2 \ge 0$ | $I_{L-lim} = 0$                                                                        |

| Bridge 2 switching          |                                                                                        |

| $\Delta V_{out} * V_1 < 0$  | $I_{L-lim} = -nV_1\sqrt{\frac{4C_j}{L_s}\left \frac{V_{out}}{nV_1}\right }$            |

| $\Delta V_{out} * V_1 > 0$  | $I_{L-lim} = 0$                                                                        |

Table 2.3: ZVS condition when two half bridges in the same H-bridge switch at once

In case both half bridges in the same H-bridge turn on or off at the same time, ZVS is only possible in one of the two half-bridges, as both half bridges require a different current polarity to achieve ZVS. The conditions that apply to either of the half bridges are similar to those of the single switch case from the 0 to the positive or negative output state, as the non-ZVS switch will conduct through the diode as a result of the current polarity. This only occurs when the duty cycle of one of the H-bridges approaches zero, at which point it will be more optimal stop the H-bridge from switching to reduce losses.

Figure 2.7: Equalvalent circuit when both half bridges switch at once

#### 2.3.3 Cases involving both H-bridges

It is also possible for H-bridges on both sides to switch at the same time at the boundaries of the switching modes. If both H-bridges increase in voltage, similar to the previous non-ZVS case, only one H-bridge can have ZVS. This generally only occurs on the boundaries between switching modes, like on the boundary between TPS mode 1, mode 3 and mode 4. The switch that gets ZVS is determined by the current direction in this case, where the inductor current will fill or drain the capacitors of the ZVS bridge, while the non-ZVS bridge will conduct through the diode of the switch that was previously on. The inductor current requirement can thus be calculated as if the ZVS bridge has a single switching event.

Alternatively the two H-bridges can switch in opposing directions, which will lead to decreased ZVS requirements. The part of the operation regions this occurs in is located at the boundary between TPS mode 3 and 5, and at the outer boundary of TPS mode 4. These events are not considered in the calculations as they occur in sub-optimal operating regions that suffer from high circular currents.

### 2.4 Proposed modulation method

While a peak current optimization based modulation provides low currents stress and full soft range soft switching, at low power where the converter operates using ideal triangular modulation, it only has 2 out of 8 ZVS switching events. To improve efficiency at low power, a new modulation method is proposed which maximizes the number of ZVS events in the operating range. As the modulation method is similar to that of the peak current optimization, it should still retain low current stress.

The proposed modulation method will operate in mode 1 TPS at low power and in EPS at high power, similar to what resulted from the efficiency optimizing control loop in [11]. This will increase low power efficiency compared to the peak current optimizations. The boundaries of the DAB converter operating modes are analysed and a transition region is added to maximize the number of ZVS events over the operating range.

The control law will remain close to that of the optimizations for peak current done in [5], [10] and [19]. This is preferred over the rms current optimization in [22] for the high power EPS region, as the peak current optimization results in a linear, easy to implement modulation method, while the difference in rms current is rather small. The rms current optimization uses non-linear equations, including multiple square roots, which is not very suitable for implementation in a microcontroller.

In this section, firstly the ZVS constraints of EPS and mode 1 TPS modulation will be analysed. The ZVS conditions of a transition region which uses mode 1 EPS, a specific case of mode 1 TPS, will also be analysed. Based on this analysis a control law will be created, taking into account the ZVS analysis. In these equations k will be used to represent the voltage gain between the two sides of the converter, k is defined as  $k = \frac{V_{out}}{nV_{in}}$ .

#### 2.4.1 EPS ZVS boundaries

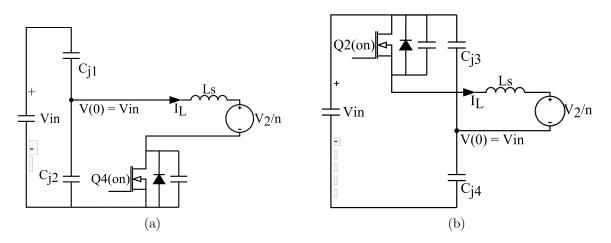

EPS has two operating modes, mode 1 EPS is a specific case of mode 1 TPS, and mode 2 EPS a case of mode 4 TPS. Depending on whether k > 1 or k < 1 either  $D_2$  or  $D_1$  will be equal to 1, which is not the case for the TPS modes. Only mode 2 EPS will be discussed here as mode 1 EPS is a variation of mode 1 TPS, which will be covered at a later point. The forward and reverse power transfer voltage and current waveforms for mode 2 EPS are shown in figure 2.8.

The required current amplitude for ZVS depends on the conditions under which the switching occurs. The switching events at  $t_0$  in figure 2.8a and the switching event at  $t_2$  in figure 2.8b are symmetrical and will have the same current amplitude during switching. However due to the different voltages applied by the non-switching H-bridge, their ZVS requirements will be different. Similar differences can be found for the other switching events depending on the polarity of  $\Phi$  and k.

Figure 2.8: EPS case 2 in forward and reverse power transfer operation

To simplify the control system, the polarity of  $\Phi$  with the worst case ZVS requirements will be used in the calculations. When considering a positive polarity of  $\Phi$  for k < 1, the switching event at  $t_0$  in figure 2.8 will have a larger ZVS requirement compared to its symmetrical point at  $t_2$  for a negative polarity of  $\Phi$ . For the switching event at  $t_1$  this is reversed, having a larger ZVS requirement for a negative polarity of  $\Phi$ .

For k > 1, the worst case polarities of  $\Phi$  are reversed compared to k < 1 at the same points in the voltage and current waveform.

## Solutions when $V_{in} > \frac{V_{out}}{n}$

The current values at the switching times are mirrored between the two conduction modes, where  $t_0$  in forward mode corresponds to the current at  $t_2$  in reverse mode. In these equations the absolute value of  $\Phi$  is used assuming symmetry between forward and reverse power transfer. This leads to the inequalities based on forward power transfer in equation  $2.6(t_0)$ ,  $2.7(t_1)$  and  $2.8(t_2)$ , where  $k_w$  is the worst case value of k for the specific the ZVS requirements.

$$-\frac{T_s}{4L_s}(D_1(V_{in} + \frac{V_{out}}{n}) + (2|\Phi| - 2)\frac{V_{out}}{n}) < -V_{in}\sqrt{\frac{2C_{j1}}{L}(1 + 2k)} \qquad k_w = 1 \qquad (2.6)$$

$$\frac{T_s}{4L_s}(V_{out}/n + (2|\Phi| - 1)V_{in}) > nV_{in}\sqrt{\frac{4C_{j2}k}{L}} \qquad k_w = 1$$

(2.7)

$$\frac{T_s}{4L_s}(D_1V_{in} + (2|\Phi| - D_1)V_{out}/n) > V_{in}\sqrt{\frac{2C_{j1}}{L}(2k-1)} \qquad k_w = 1 \qquad (2.8)$$

By filling in the the worst case values for k, and solving the inequalities, simplified boundary values for the ZVS region of mode 2 EPS can be derived. The solutions, which are valid in both directions of operation, and are shown in equation  $2.9(t_1)$ ,  $2.10(t_0)$  and  $2.11(t_2)$ . It can be seen that there are two ZVS requirements on  $D_1$ , these are both for a different half bridge. In practice the ZVS requirement in equation 2.11 is not relevant as it lies outside of the boundary of EPS mode 2, with the exception of k being very close to 1. Under these circumstances the ZVS requirement on  $D_1$  will only be effective for very small values of  $|\Phi|$ .

$$|\Phi| > 0.5 - 0.5k + \frac{2nL_s}{T_s} \sqrt{\frac{4C_{j2}}{L_s}}$$

(2.9)

$$D_1 > \frac{k(2-2|\Phi|) + \frac{4L}{T_s}\sqrt{\frac{6C_{j1}}{L}}}{1+k}$$

(2.10)

$$D_1 > \frac{-2k|\Phi| + \frac{4L}{T_s}\sqrt{\frac{2C_{j1}}{L}}}{1-k}$$

(2.11)

## Solutions when $V_{in} < \frac{V_{out}}{n}$

Using the exact same method, a set of solutions for when  $V_{in}$  is smaller than  $\frac{V_{out}}{n}$  can also be derived. Here equation 2.15 applies to the primary side H-bridge, while equation 2.16 and 2.17 apply to the half bridges of the secondary side H-bridge.

$$-\frac{T_s}{4L_s}(D_2(V_{in} + \frac{V_{out}}{n}) + (2|\Phi| - 2)V_{in}) < -V_{out}\sqrt{\frac{2C_{j2}}{L}(1 + 2k^{-1})} \qquad k_w = 1 \quad (2.12)$$

$$\frac{T_s}{4L_s}(V_{in} + (2|\Phi| - 1)\frac{V_{out}}{n}) > V_{out}\sqrt{\frac{4C_{j1}k^{-1}}{L}} \qquad k_w = 1 \qquad (2.13)$$

$$\frac{T_s}{4L_s}(D_2(\frac{V_{out}}{n} - V_{in}) + 2|\Phi|) > V_{out}\sqrt{\frac{2C_{j2}}{L}(2k^{-1} - 1)} \qquad k_w = 1 \qquad (2.14)$$

$$|\Phi| > 0.5 - 0.5k^{-1} + \frac{2L_s}{T_s}\sqrt{\frac{4C_{j1}}{L_s}}$$

(2.15)

$$D_2 > \frac{k^{-1}(2-2|\Phi|) + \frac{4nL}{T_s}\sqrt{\frac{6C_{j2}}{L}}}{1+k^{-1}}$$

(2.16)

$$D_2 > \frac{-2k^{-1}|\Phi| + \frac{4nL}{T_s}\sqrt{\frac{2C_{j2}}{L}}}{1 - k^{-1}}$$

(2.17)

#### 2.4.2 mode 1 TPS ZVS boundaries

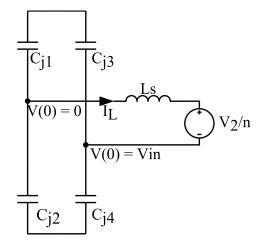

The approach for mode 1 TPS will differ from the one in the EPS case, as in mode 1 TPS there are more control variables to take into account. Figure 2.9 shows the waveforms for mode 1 TPS operation. The H-bridge with the larger duty cycle, always switches with zero voltage applied by the non-switching H-bridge, making the switching events at  $t_0$  and  $t_3$  independent of k. The switching events at  $t_1$  and  $t_2$  are dependent on k. To simplify the equations a similar as used for EPS mode 2 is used, where worst case values of k are assumed. For the switching event at  $t_1$ , depending on the polarity of  $k \ k_w = 0$  or  $\frac{1}{k_w} = 0$  gives the worst case ZVS requirement, while for the switching event at  $t_2$  this occurs at  $k_w = 1$ .

Figure 2.9: Mode 1 TPS waveforms for  $V_{in} > V_{out}$  and  $V_{in} < V_{out}$

## **ZVS** equations when $V_1 > \frac{V_2}{n}$

Below the ZVS inequalities for mode 1 TPS are shown.

$$\frac{T_s}{4L_s} (D_2 \frac{V_{out}}{n} - D_1 V_{in}) > V_{out} \sqrt{\frac{2C_{j2}}{L_s}} \qquad 0 < k < 1$$

(2.18)

$$\frac{T_s}{4L_s} \left(2\Phi \frac{V_{out}}{n} + D_1(\frac{V_{out}}{n} - V_{in})\right) < -V_{in} \sqrt{\frac{2C_{j1}}{L}(1 - 2k)} \qquad worstcasek = 0$$

(2.19)

$$\frac{T_s}{4L_s}(2\Phi \frac{V_{out}}{n} + D_1(V_{in} - \frac{V_{out}}{n})) > V_{in}\sqrt{\frac{2C_{j1}}{L}(2k-1)} \qquad worstcasek = 1$$

(2.20)

This results in the following restrictions to the duty cycle:

$$D_2 > \frac{D_1}{k} + \frac{4nL_s\sqrt{\frac{2C_{j2}}{L_s}}}{T_s}$$

(2.21)

$$D_1 > \frac{2k\Phi}{1-k} + \frac{4L_s\sqrt{\frac{2C_{j1}}{L_s}}}{(1-k)T_s}$$

(2.22)

$$D_1 > -\frac{2k\Phi}{1-k} + \frac{4L_s\sqrt{\frac{2C_{j1}}{L_s}}}{(1-k)T_s}$$

(2.23)

This can be rewritten as:

$$D_1 > \frac{2k|\Phi|}{1-k} + \frac{4L_s\sqrt{\frac{2C_{j1}}{L_s}}}{(1-k)T_s}$$

(2.24)

$$D_2 > \frac{2|\Phi|}{1-k} + \frac{4L_s}{T_s} \left(\frac{\sqrt{\frac{2C_{j1}}{L_s}}}{k(1-k)} + n\sqrt{\frac{2C_{j2}}{L_s}}\right)$$

(2.25)

where  $|\Phi_{TRG-lim}|$  in the equation below is the maximum phase shift for full ZVS mode 1 TPS operation, as at which point  $D_2 = 1$  and cannot be increased further.

$$|\Phi_{TRG-lim}| = 0.5 - 0.5k - \frac{2L_s}{T_s} \left(\frac{\sqrt{\frac{2C_{j1}}{L_s}}}{k} + n(1-k)\sqrt{\frac{2C_{j2}}{L_s}}\right)$$

(2.26)

### **ZVS** equations when $V_1 < \frac{V_2}{n}$

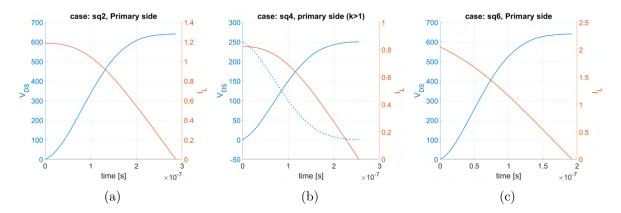

When the When the voltage ratio k is bigger than 1, operation is changed slightly. In 2.27, 2.28 and 2.29 the modified ZVS equations for operations under these conditions are shown for  $t_0$ ,  $t_1$  and  $t_2$  in 2.9b.

$$-\frac{T_s}{4L_s}(D_1V_{in} - D_2\frac{V_{out}}{n}) < -V_{in}\sqrt{\frac{2C_{j1}}{L_s}} \qquad 0 < k < 1$$

(2.27)

$$\frac{T_s}{4L_s}(2\Phi V_{in} + D_2(\frac{V_{out}}{n} - V_{in})) > V_{in}\sqrt{\frac{2C_{j2}}{L_s}(1 - 2k^{-1})} \qquad worstcasek^{-1} = 0 \qquad (2.28)$$

$$\frac{T_s}{4L_s}(2\Phi V_{in} + D_2(V_{in} - \frac{V_{out}}{n})) < -V_{in}\sqrt{\frac{2C_{j2}}{L_s}(2k^{-1} - 1)} \qquad worstcasek^{-1} = 1 \qquad (2.29)$$

Solving these equations, and merging the conditions for  $t_1$  and  $t_2$  in a similar way as was done for k < 1, results in the conditions in equation 2.30 and 2.31. The requirement for  $D_1$  assumes operation on the boundary of  $D_2$ , as  $D_2$  has been substituted in the equation for  $D_1$ . The phase shift boundary for ZVS is shown in equation 2.32.

$$D_2 > \frac{2k^{-1}|\Phi|}{1-k^{-1}} + \frac{4nL_s\sqrt{\frac{2C_{j2}}{L_s}}}{(1-k^{-1})T_s}$$

(2.30)

$$D_1 > \frac{2|\Phi|}{1-k^{-1}} + \frac{4nL_s}{T_s} \left(\frac{n\sqrt{\frac{2C_{j2}}{L_s}}}{k^{-1}(1-k^{-1})} + \sqrt{\frac{2C_{j1}}{L_s}}\right)$$

(2.31)

$$|\Phi_{TRG-lim}| = 0.5 - 0.5k^{-1} - \frac{2L_s}{T_s} \left(\frac{n\sqrt{\frac{2C_{j2}}{L_s}}}{k^{-1}} + (1 - k^{-1})\sqrt{\frac{2C_{j1}}{L_s}}\right)$$

(2.32)

#### 2.4.3 Resulting control law

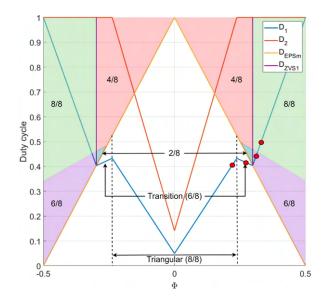

The ZVS boundaries presented in this section can be used to construct a control law. The control law will consist of three regions, the (mode 2) EPS region at high power, the mode 1 TPS region at low power, and a transition region to connect both regions.

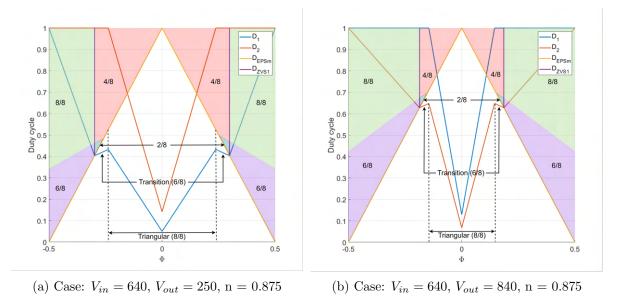

Values of  $D_1$  and  $D_2$  in the EPS region are determined by linear extrapolation between two points. The first point is located at  $|\Phi| = 0.5$  and  $D_1 = D_2 = 1$ , where the converter power is maximized. The second point is determined by the intersection between the ZVS boundary on  $|\Phi|$  for EPS mode 2 shown in equation 2.9 and 2.15, and the boundary between EPS mode 1 and 2, which occurs at  $D_{1/2} = 1 - 2|\Phi|$ . By choosing the boundary of the EPS region in this way, all ZVS requirements except for those in equation 2.10 and 2.16 are met. This ensures 6 out of 8 switching events can maintain ZVS in this operating mode.

The mode 1 TPS region, which will also be referred to as the triangular region, is defined by the duty cycle equations presented in the previous subsection. It starts at  $\Phi = 0$ , and ends at  $\Phi_{TRG-lim}$ , at which point either  $D_1$  or  $D_2$  will be equal to 1. At the boundary of this operation region, the converter will operate in mode 1 EPS.

By themselves, the EPS and triangular region are not connected, creating a discontinuity in the control law. To resolve this, a transition region is added in between. The values of  $D_1$ and  $D_2$  are calculated using linear extrapolation between the boundaries of the triangular and EPS region.

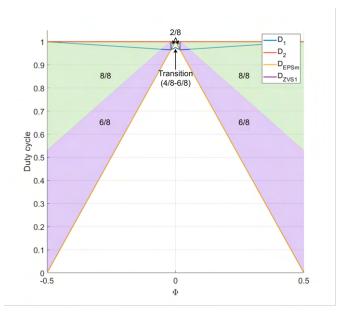

A special case of the control law occurs when k approaches 1. Here  $|\Phi_{TRG-lim}|$ , the boundary of the triangular region, becomes negative. This means that the system will not operate in the triangular region under these conditions. Instead the converter will operate in the transition region at  $\Phi = 0$ . The boundary values for  $D_1$  and  $D_2$  can still be calculated using the negative value of  $|\Phi_{TRG-lim}|$ , however the ZVS requirements at  $t_1$  and  $t_2$  in Figure 2.9 will not be met. The ZVS requirements at  $t_0$  and  $t_3$  will still be met under these conditions, maintaining 4 out of 8 ZVS switching events.

Operation in the transition region occurs in mode 1 EPS, a special case of mode 1 TPS where depending on the voltage gain k either  $D_1$  or  $D_2$  is equal to 1. In this situation, only the ZVS conditions at  $t_0$  and  $t_3$  in figure 2.9 change compared to normal mode 1 TPS operation, as the  $t_0$  and  $t_3$  switching events now occur at the same time. Given that the voltage of the non-switching side is always zero when this occurs, the ZVS current requirement will also be zero, based on the values from table 2.3. In the case of k < 1 the ZVS requirement for  $D_2$  changes to  $D_2 > \frac{D_1}{k}$ , while for k > 1 it changes to  $D_1 > \frac{D_2}{k^{-1}}$ .

In practice the current during the specified switching events will not be zero, as at the boundary of the mode 1 triangular and mode 2 EPS region, the currents will also be non-zero. The current during the  $t_0$  and  $t_3$  switching events will be in between that for the triangular and EPS operating regions. This means the ZVS conditions at  $t_0$  and  $t_3$  will always be met in the transition region. From the ZVS requirements that apply to  $t_1$  and  $t_2$ , only one of the two will be met in the transition region if  $|\Phi_{TRG-lim}| > 0$ , if  $|\Phi_{TRG-lim}| < 0$ , neither will be met.

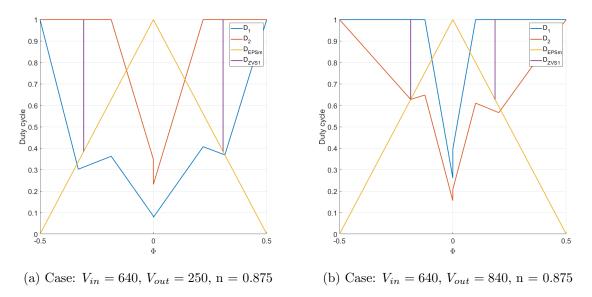

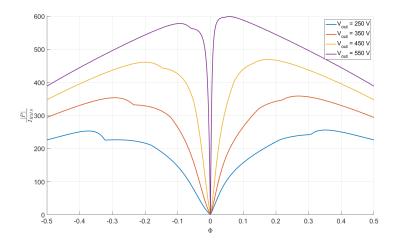

The resulting control law is shown in figure 2.10, here  $D_{EPS}$  marks the boundary between of EPS mode 1 and mode 2.  $D_{ZVS1}$  shows the ZVS boundary on  $|\Phi|$  in the EPS region, which is used together with  $D_{EPS}$  to define the EPS region boundary point of the control law. In EPS mode 2, the number of ZVS events per region is shown. It also includes the triangular and transition regions, which are marked using arrows.

Figure 2.11 shows the control law at unity voltage gain. It can be observed that  $D_2$  remains constant at a value of 1, never entering the triangular region where  $D_2$  would be smaller than 1.

Figure 2.10: Duty cycle waveforms for k < 1 and k > 1 with ZVS regions

#### 2.4.4 Overall ZVS performance

The proposed control law will provide full ZVS in most of the operating range except for the transition region, and a small part of the EPS operating region bordering the transition region,

Figure 2.11: Duty cycle waveforms for k = 1

where 6/8 switches will have ZVS. When the voltage gain is close to one, the ZVS events in the transition region are reduced to 4/8. It is expected that this will increase the operating efficiency compared to the non-ZVS peak current optimizations in [5], [10] and [19].

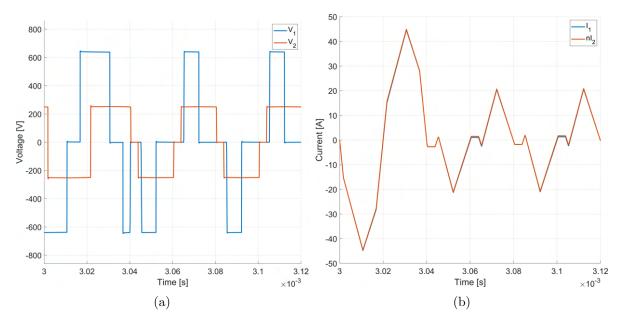

## 2.5 Transient Behaviour

Given the application of the converter, which is EV charging, it is expected that the converter operation will be fairly static. However during the startup sequence, or during a load change this does not apply. In these situations, attention must be paid to the initial current at the start of each switching period. If a large change in output power is made without taking this into account, it can lead to a DC offset in the leakage inductance current and magnetizing current. The offset of the leakage inductance, which can be very significant, can obstruct ZVS, and cause additional conduction losses. The DC-offset of the magnetizing current mainly involves the risk of transformer saturation, which an in turn cause the transformer to overheat.

In [3] various methods of removing these transient DC offsets are discussed, utilizing transient states to transition between operating points of the converter. Various solutions are provided which can transition in less than half a cycle, while other need slightly less than a whole switching cycle. In [9] a general method that can be applied to all modulation types is proposed, it prevents a offset from occurring in both the leakage and magnetizing current, with a transition of less than a half cycle.

Although methods using a transient state do solve the transient issue, these methods have the disadvantage of increasing the control complexity. This increase in complexity is caused by the introduction of a variable length switching period every transition. It also requires a boundary for the minimum amount of change in power or voltage before something is considered a transition, otherwise it will be triggered unintentionally by noise on the voltage measurement. In this thesis an alternative method is proposed, where every switching cycle will starts and ends at a current of 0 A. This prevents a DC offset in the leakage inductor current from occurring during a change in power output, but does not prevent an offset in the magnetizing current. In return the proposed method is much simpler to implement as a fixed duty cycle can be used. To be able to start each switching period at 0 A, the zero current regions in the operating waveforms need to be analysed.

#### 2.5.1 Zero current regions

The system has two operating modes, mode 2 EPS and mode 1 TPS. In mode 1 TPS, there will always be a zero crossing during the time that the lower voltage side is one, while the high voltage side is 0. Whether the left or right side of the high voltage waveform is selected depends on the direction of the phase shift, and whether the voltage ratio is bigger or smaller than one.

To minimize the transition switching losses, similar switching states should be chosen as the start or end point of the period. When  $V_{in} > \frac{V_{out}}{n}$  the switching state chosen is  $V_2 = \frac{V_{out}}{n}$ , with  $V_1 = 0$  or  $V_1 = -V_{in}$ , depending on the operating mode. In mode 1 TPS this occurs to the left of  $t_1$ , or the right of  $t_2$ , depending on the polarity of the phase shift, as seen in figure 2.9. In mode 2 EPS this occurs around  $t_3$  in forward conduction mode, and around  $t_2 + 0.5T_s$  in reverse conduction mode, in figure 2.8.

Similar states can be found for when  $V_{in} < \frac{V_{out}}{n}$ , based on the input side voltage  $V_1 = V_{in}$ . Here the output side voltage on the inductor can be either  $V_2 = 0$  or  $V_2 = -\frac{V_{out}}{n}$ .

The solution are calculated by taking one of the boundaries of the 0 current region, and adding a  $\Delta I$  term that is equal to  $\frac{V_{inductor}}{L}t$ . The resulting equation is then solved for t. This gives a time offset relative to one of the boundaries of the 0 current region. By dividing this time offset by the sample time, it can be normalized in a range from 0 to 1.

An additional offset is required as the point at which the boundary of the zero current region is located is not at the start of a switching cycle. For the calculation of this term, it is assumed that the primary side voltage has a fixed phase shift, while the secondary voltage is shifted by  $\Phi$ . The standard position can be observed in figure 2.8 and 2.9.

#### Mode 1 TPS solutions

In mode 1, there is a total of 4 possible cases.  $\Phi$  bigger or smaller than 0, and  $V_{in}$  being bigger or smaller than  $\frac{V_{out}}{n}$ . The solutions for the offset  $D_{off}$  for the mode 1 cases are shown in table 2.5.  $D_{off}$  is the offset of the zero current switching point from the start of the period, and can vary from 0 to 1.

| Voltage gain | Phase shift | $D_{off}$                                  |

|--------------|-------------|--------------------------------------------|

| k < 1        | $\Phi > 0$  | $0.5 \Phi  + \frac{D_1}{4}k^{-1} + 0.25$   |

| k < 1        | $\Phi < 0$  | $ -0.5 \Phi  + \frac{D_1}{4}k^{-1} + 0.25$ |

| k > 1        | $\Phi > 0$  | $-\frac{D_2}{4}k + 0.25$                   |

| k > 1        | $\Phi < 0$  | $\frac{D_2}{4}k + 0.25$                    |

Table 2.4: Transient conditions

#### Mode 2 EPS solutions

In mode 2 EPS there are 8 possible cases. Similar to the solutions for mode 1 TPS, they are separated by the polarity of  $\Phi$  and the voltage ratio. In addition to this, the polarity of the current at the switching event around which the zero current region is found determines on which side of the switching event the zero current point is found. For  $V_{in} > \frac{V_{out}}{n}$  the current is shown in equation 2.33, and for  $V_{in} < \frac{V_{out}}{n}$  it is shown in equation 2.34.

$$I_{0-EPS_1} = \frac{Ts}{4L} (D1 * (k^{-1} + 1) + 2|\Phi| - 2)$$

(2.33)

| k < 1 | $\Phi > 0$ | $I_{0-EPS-2} > 0$ | $\frac{2 \Phi -2}{4(k^{-1}+1)} + 0.75$          |

|-------|------------|-------------------|-------------------------------------------------|

| k < 1 | $\Phi > 0$ | $I_{0-EPS-2} < 0$ | $\frac{ \Phi }{2} + \frac{D_1}{4}k^{-1} + 0.25$ |

| k < 1 | $\Phi < 0$ | $I_{0-EPS-2} > 0$ | $-\frac{2 \Phi -2}{4(k^{-1}+1)}+0.75$           |

| k < 1 | $\Phi < 0$ | $I_{0-EPS-2} < 0$ | $1.25 -  \Phi /2 - \frac{D_1}{4}k^{-1}$         |

| k > 1 | $\Phi > 0$ | $I_{0-EPS-1} > 0$ | $k \frac{2 \Phi -2}{4(1+k)} + \frac{D_1}{4}$    |

| k > 1 | $\Phi > 0$ | $I_{0-EPS-1} < 0$ | $-\frac{D_2}{4}k + \frac{D_1}{4}$               |

| k > 1 | $\Phi < 0$ | $I_{0-EPS-1} > 0$ | $-k\frac{2 \Phi -2}{4(1+k)} + \frac{D_1}{4}$    |

| k > 1 | $\Phi < 0$ | $I_{0-EPS-1} < 0$ | $\frac{D_2}{4}k + \frac{D_1}{4}$                |

$I_{0-EPS_2} = \frac{Ts}{4L} (D2 * (1+k) + 2|\Phi| - 2)$ (2.34)

Table 2.5: Transient conditions

#### 2.5.2 Magnetizing current

Using these equation for transient behaviour results in the preservation of ZVS in transient cases, but it neglects the magnetizing current. While at positive  $\Phi$  during steady state the magnetizing current at the start of a period will be positive, at negative  $\Phi$  it will be negative. In the worst case scenario, if a transition from  $\Phi$  to  $-\Phi$  were to occur, a DC offset in the magnetizing current of 2x the  $I_{maq-peak}$  can occur.

A smaller magnetizing current offset can be obtained if the initial states of the switches at the start of each switching period are neglected. Instead the converter will try to maintain an average negative (or positive) voltage during the first half of each switching period. This will result in a positive magnetizing current at the start of each period during steady state, regardless of the polarity of  $\Phi$ , at the cost of ZVS during the transition. This limits the maximum DC offset to only 1x  $I_{mag-peak}$ . In the case of k < 1, for positive  $\Phi$  the equations remain unchanged. For negative  $\Phi$  a switching state where  $V_2$  is negative can be implemented, by applying a normalized phase shift of 0.5 to the offset equations.

The option to reduce the peak magnetizing flux is preferred over the reduction in switching loss when a transition from positive to negative  $\Phi$  occurs. This choice is made as the peak magnetizing flux has a larger impact on the circuit design than the occasional additional switching loss. It should be noted that a transition from positive to negative power is not something that is expected to occur often for EV charging application.

#### 2.6 ZVS range extention

The proposed modulation method introduces improvements to the number of ZVS events compared to other modulation methods, but it still does not operate with full ZVS over the entire operating range. An example of this would be operation at higher output voltage, where operation will occur in the transition region at full power. As it is likely that the converter will operate at full power a majority of the time, operating with a reduced number of ZVS events at this operating point is undesirable.

Through variable frequency operation, and by using alternative charging profiles, it is theoretically possible to extend the ZVS range to the full operating range.

The primary idea behind the ZVS range extention is that variable frequency operation can be used to ensure the converter always operates in a mode with full ZVS while operating at maximum power. By combining this with alternative charging profiles, that use the converter either at full power, or turn it off, full ZVS operation can be ensured.

Charging profiles suitable for this include pulsed charging, and the Multistep Constant Current (MSCC) charging profile when using multiple DAB converters connected in parallel [14]. For a pulsed charging profile, the converter operates at full power until a voltage limit is reached, at which point it shuts off for a certain time. For a parallel DAB converter configuration, one of the parallel converters is shut off every time the voltage limit is reached, reducing the power in steps.

#### 2.6.1 Variable frequency operating modes

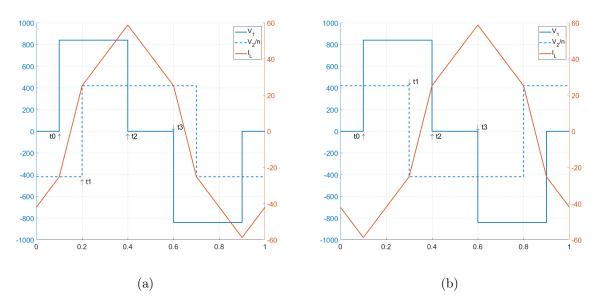

To obtain the desired full ZVS operation, the converter should always operate in the triangular region, or the full ZVS part of the EPS region. This can be achieved by increasing the switching frequency, which decreases the output power, requiring an increase in  $\Phi$  to achieve the same power. As a result operation will shift towards the EPS region, where full ZVS can be achieved.

Similarly if the switching frequency is reduced,  $\Phi$  needs to be reduced to maintain the same output power. The lower value of  $\Phi$  will shift operation towards the triangular region.

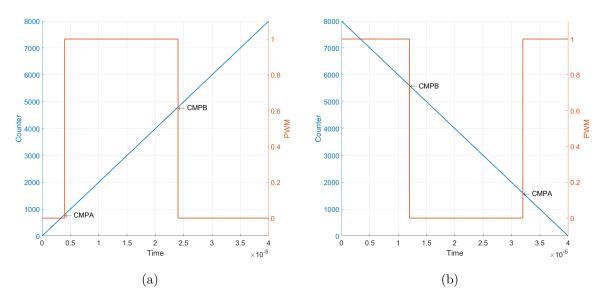

Although various combinations of increased and decreased frequency are possible, a continuous switching frequency over the operating region is desired, to simplify implementation in a lookup table. A discontinuity would result in the lookup table selecting an in between value at the discontinuity, where the system does not operate with full ZVS. The lookup table could also be operated in a stepwise manner, instead of the default point-slope method, however an increase in resolution and would be required, increasing memory usage.

In table 2.6 the maximum and minimum frequencies are shown for various combinations of frequency changes. These are calculated by looping through *Phi* until the positive and negative maximum power is reached. Once this power is reached, the operating mode will be checked. When the system operates in an undesirable operating mode like the transition region or the non-ZVS part of the EPS region, the switching period is increased or decreased. The Power calculation is then repeated until the full power operating mode is as desired. The frequency values in 2.6 use a version of of the control equations that includes compensation for non-ideal converter behaviour, which will be discussed in chapter 3.

| Continuous | Frequency         | $f_{min}$          | $f_{max}$            | $ratio(\frac{f_{max}}{f_{min}})$ |

|------------|-------------------|--------------------|----------------------|----------------------------------|

| no         | increase/decrease | 11.8 kHz           | 71.4 kHz             | 6.07                             |

| no         | increase          | $25 \mathrm{~kHz}$ | $83.3 \mathrm{~kHz}$ | 3.33                             |

| no         | decrease          | 7.14 kHz           | $25 \mathrm{~kHz}$   | 3.5                              |

| yes        | increase          | $25 \mathrm{~kHz}$ | $83.3 \mathrm{~kHz}$ | 3.33                             |

| yes        | decrease          | $0 \text{ kHz}^*$  | $25 \mathrm{~kHz}$   | -                                |

Table 2.6: Variable frequency results for L = 104.3 uH using the proposed control law

Among the options shown in table 2.6, the most viable option is based on a continuous frequency increase while operating only in the EPS region. An increase in frequency is less likely to affect the magnetic design in a negative way and will reduce peak flux density in the transformer core. It is also the only viable option that has a switching frequency continuous over the voltage range, as the alternative continuous approach of always operating in the triangular region fails when operating close to unity gain voltage gain.

#### 2.6.2 Modified EPS modulation

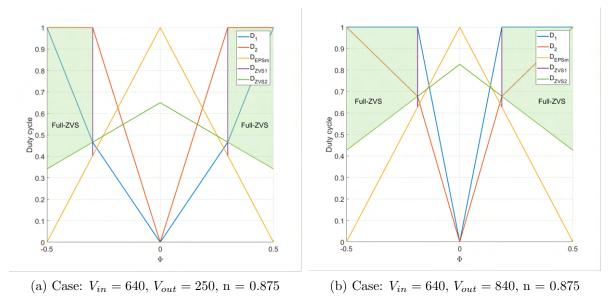

While the Proposed modulation method maximizes the number of ZVS events over the entire operating range, it does not do so specifically for the EPS region. By modifying the control law for variable frequency operation, it is possible to reduce the minimum power while operating at full ZVS in the EPS region. This has the advantage of reducing the maximum switching frequency.

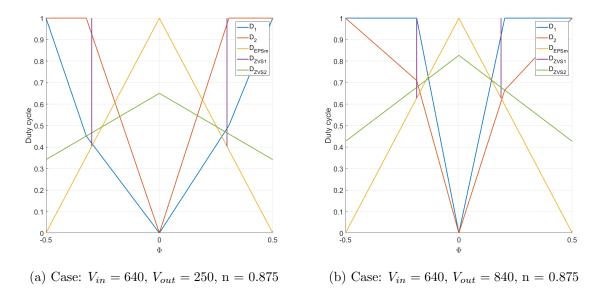

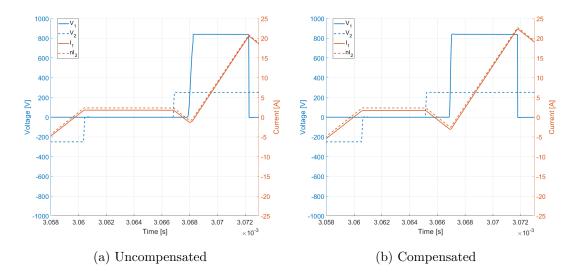

The ZVS range in the EPS mode 2 region can be used more optimally if instead of using the intersection of the EPS mode boundary and the ZVS boundary, the intersection between two EPS mode 2 ZVS boundaries is used to define the boundary of the high power operating region. The resulting control law is shown in 2.12. By using this modified control function, the maximum switching frequency can be reduced from 83.3 kHz to 66.7 kHz, which will reduce switching and inductor core losses.

Figure 2.12: Duty cycle waveform including the EPS mode 2 ZVS boundaries and mode boundary for variable switching frequency operation

The modified EPS modulation has a parts that operate without ZVS or in the mode 1 TPS region at lower values of Phi. This is only implemented to keep the modulation continuous for lower values of  $|\Phi|$ . A variable switching frequency will be used to maintain operation in the full ZVS part of the EPS region.

## Chapter 3

# Simulation

To test the control method that has been created in the previous chapter, a simulation is made using simulink. In this chapter, the simulink model of the DAB converter, the control system and the non-ideal behaviour of the DAB converter will be discussed.

## 3.1 Hardware modelling

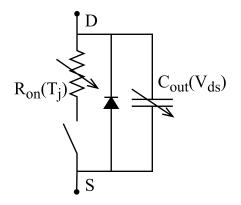

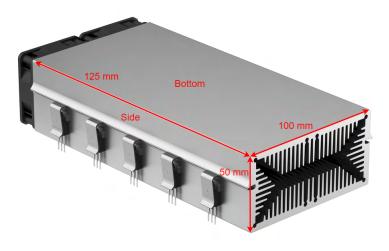

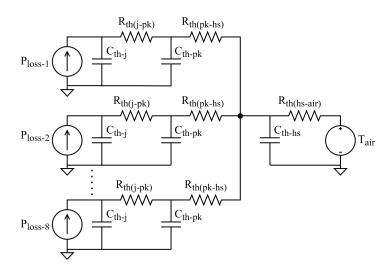

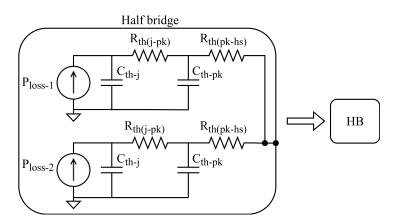

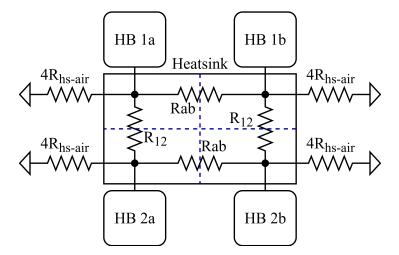

The goal of the hardware model is to provide sufficient accuracy for the performance aspects that matter, like the ZVS behaviour of the converter, while minimizing its complexity. Among the system components the transformer and the MOSFETs are the only parts that affect ZVS behaviour. As semiconductor MOSFETs are temperature dependent, a thermal model should be included too. Parts like protection systems and gate drivers are not considered in the model.

#### 3.1.1 Transformer and inductor model

The transformer of a DAB converter can be constructed in different ways, but generally a high leakage inductance is required. This high leakage inductance can be implemented in two ways, by adding an external leakage inductor, or by using a more complex transformer design.

Integrating the leakage inductance into the transformer offers a more compact solution, and can be achieved by placing the primary and secondary windings on separate transformer legs, while providing a flux path that does not go through the other winding. The air gap of this alternative flux path can then be tuned to provide the desired leakage inductance. Although this solution is compact, the design process for such a transformer will be more complicated.

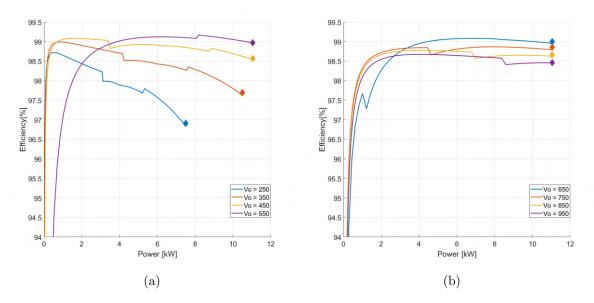

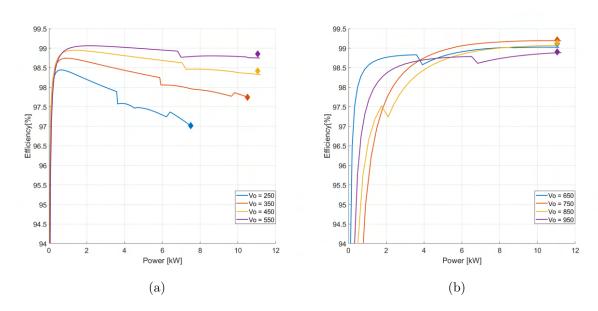

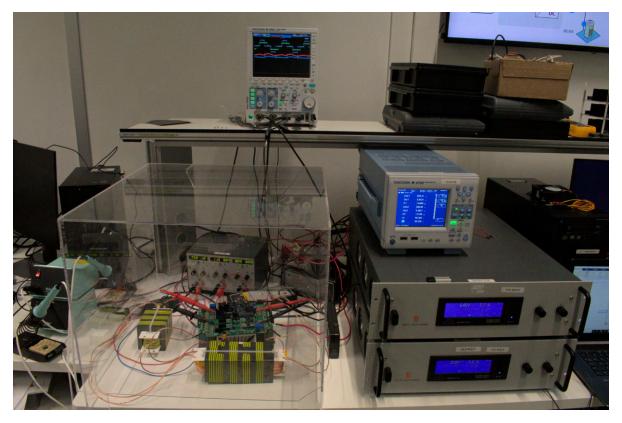

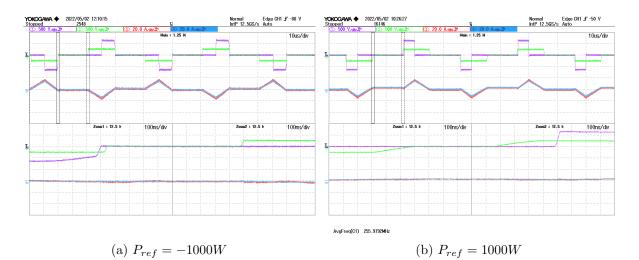

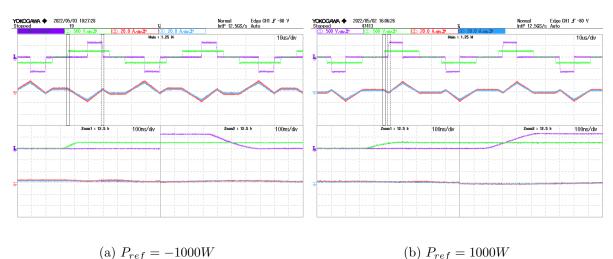

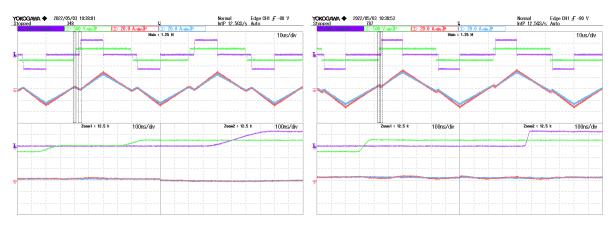

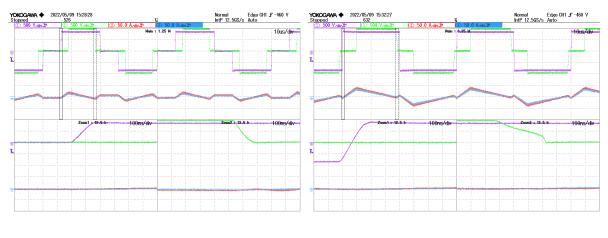

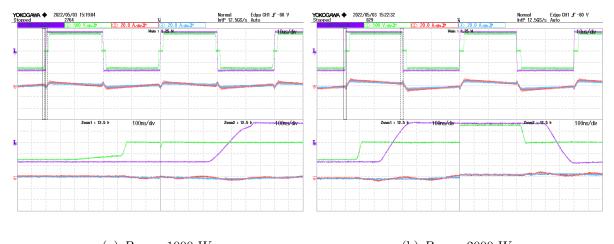

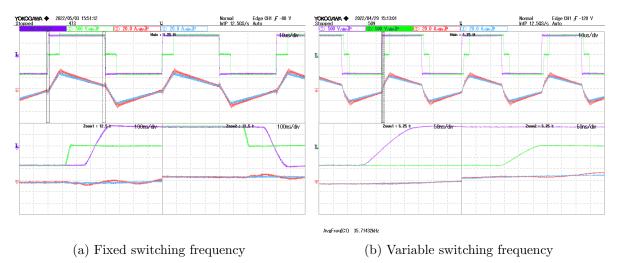

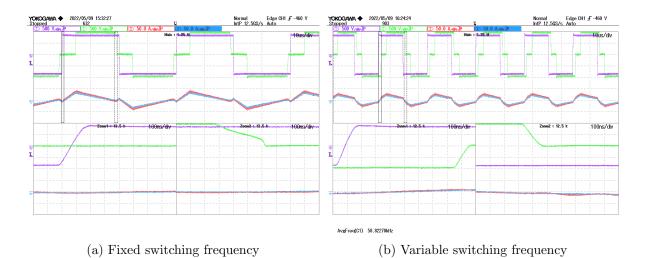

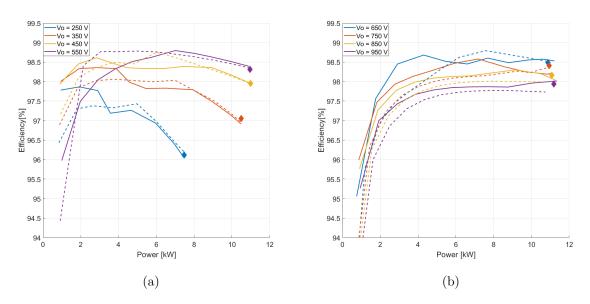

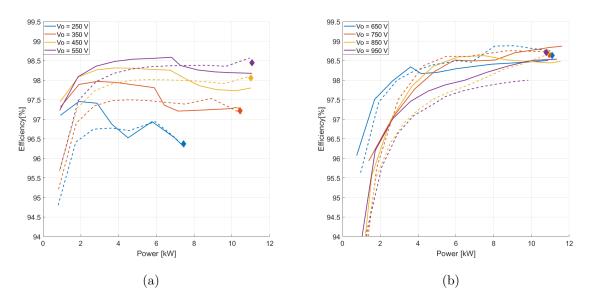

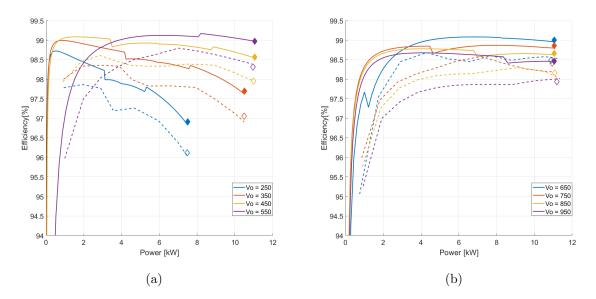

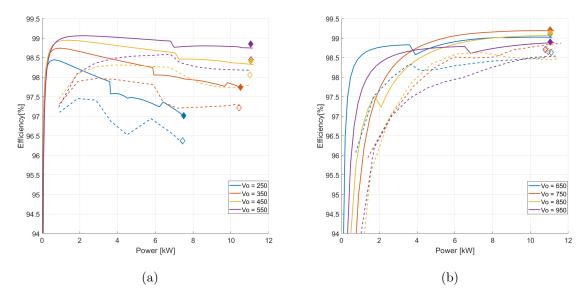

As the focus of the thesis is on the modulation and control system design, and not on hardware optimization, instead an external leakage inductor and transformer will be used, as this allows for much simpler design.