#### A Thin and Low-Inductance 1200 V SiC MOSFET Fan-Out Panel-Level Packaging With Thermal Cycling Reliability Evaluation

Chen, Wei; Jiang, Jing; Meda, Abdulmelik H.; Ibrahim, Mesfin S.; Zhang, Guogi; Fan, Jiajie

DOI

10.1109/TED.2023.3263150

**Publication date**

**Document Version** Final published version

Published in

IEEE Transactions on Electron Devices

Citation (APA)

Chen, W., Jiang, J., Meda, A. H., Ibrahim, M. S., Zhang, G., & Fan, J. (2023). A Thin and Low-Inductance 1200 V SiC MOSFET Fan-Out Panel-Level Packaging With Thermal Cycling Reliability Evaluation. *IEEE Transactions on Electron Devices*, 70(5), 2268-2275. https://doi.org/10.1109/TED.2023.3263150

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A Thin and Low-Inductance 1200 V SiC MOSFET Fan-Out Panel-Level Packaging With Thermal Cycling Reliability Evaluation

Wei Chen, Jing Jiang, Abdulmelik H. Meda<sup>®</sup>, Mesfin S. Ibrahim<sup>®</sup>, *Member, IEEE*, Guoqi Zhang<sup>®</sup>, *Fellow, IEEE*, and Jiajie Fan<sup>®</sup>, *Senior Member, IEEE*

Abstract—SiC MOSFET is mainly characterized by the higher electric breakdown field, higher thermal conductivity, and lower switching loss enabling high breakdown voltage, high-temperature operation, and high switching frequency. However, their performances are considerably limited by the high parasitic inductance and poor heat dissipation capabilities associated with existing wirebonding packaging methods. To address this challenge, a 1200 V/136 A fan-out panel-level packaging (FOPLP) SiC MOSFET with a size of 8  $\times$  8  $\times$  0.75 mm was proposed. The electrical parameters of the devices were characterized experimentally. Both the static and dynamic parameters of the package matched the bare die values, which confirmed the functioning of the proposed packaging method for SiC MOSFET. The package parasitic inductance, thermal resistance, and soldering stress were analyzed through simulations. The reliability of the packages was evaluated by performing the thermal cycling test. The

Manuscript received 9 February 2023; revised 8 March 2023; accepted 23 March 2023. Date of publication 10 April 2023; date of current version 24 April 2023. This work was supported in part by the National Natural Science Foundation of China under Grant 52275559, in part by Shanghai Pujiang Program under Grant 2021PJD002, in part by Taiyuan Science and Technology Development Funds under Grant Jie Bang Gua Shuai Program, in part by Shanghai Science and Technology Development Funds under Grant 19DZ2253400 and Grant 20501110700, and in part by the Centre for Advances in Reliability and Safety (CAiRS) admitted under AIR@InnoHK Research Cluster. The review of this article was arranged by Editor M. Hua. (Wei Chen and Jing Jiang contributed equally to this work.) (Corresponding author: Jiajie Fan.)

Wei Chen and Jing Jiang are with the Institute of Future Lighting, Academy for Engineering and Technology, Fudan University, Shanghai 200433, China (e-mail: chenw21@m.fudan.edu.cn; king@scc.com.cn).

Abdulmelik H. Meda is with the Department of Industrial and System Engineering, The Hong Kong Polytechnic University, Hong Kong (e-mail: abdulmelik.meda@connect.polyu.hk).

Mesfin S. Ibrahim is with the Centre for Advances in Reliability and Safety, Hong Kong, and also with the Kombolcha Institute of Technology, Wollo University, Kombolcha 208, Ethiopia (e-mail: mesfin. ibrahim@connect.polyu.hk).

Guoqi Zhang is with the Department of Microelectronics Engineering, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: G.Q.Zhang@TUDelft.nl).

Jiajie Fan is with the Institute of Future Lighting, Academy for Engineering and Technology, Shanghai Engineering Technology Research Center of SiC Power Device, Fudan University, Shanghai 200433, China, and also with the Research Institute, Fudan University, Ningbo 315336, China (e-mail: jiajie\_fan@fudan.edu.cn).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2023.3263150.

Digital Object Identifier 10.1109/TED.2023.3263150

experimental results revealed that: 1) SiC MOSFET FOPLP had 0.36 nH drain–source parasitic inductance at 100 kHz, a 96% reduction compared with a conventional wire-bonded package; 2) double-sided cooling enabled the packages to exhibit a thermal resistance as low as 0.55  $^{\circ}$ C/W; and 3) after 2000 thermal cycling cycles, drain–source on-state resistance [ $R_{\rm DS(on)}$ ] increased by less than 2%, which revealed the higher reliability of the package under thermal cycling.

Index Terms— Fan-out panel-level packaging (FOPLP), parasitic inductance, SiC MOSFET, thermal cycling, thermal resistance.

#### I. INTRODUCTION

C ILICON carbide (SiC), as one of the wide bandgap semiconductors, exhibits a high intrinsic breakdown field and thermal conductivity. Furthermore, SiC MOSFET bare dies exhibit higher switching frequency, lower energy loss, and higher temperature resistance than those of Si-based MOSFETs [1], [2], [3], [4]. Generally, the bare die can be used in circuits to achieve the switching function only after packaging [5], [6]. High-quality packaging is essential for the accurate functioning and increased performance of SiC MOSFET bare dies. It ensures reliable electrical connections between the die and terminals, dissipates heat generated in the die, and provides mechanical robustness and protection for operation in harsh conditions. However, existing packaging for commercial SiC MOSFETs is based on wirebonding packaging methods [6] that are typically developed for Si-semiconductor power devices, including both discrete transistor outline (TO) packages for the single die and a power module represented by parts stacking for multi-dies. The parasitic inductance of up to 10 nH was induced by the bonding wire [7], [8]. Because of the high di/dt in the high-frequency switching process, the voltage overshoot and voltage oscillation resulting from high parasitic inductance can cause an increasing electric energy loss, electromagnetic interference, and thermal breakdown of the die [9], [10]. Furthermore, the changes in the source voltage attributed to high source parasitic inductance considerably affect the driving voltage (gate-source voltage) of the device, which will cause errors in the switching state of the device [11]. The junction temperature for most commercial SiC- or

0018-9383 © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Si-based devices is both rated from 150 °C to 175 °C, and SiC die devices can function steadily at temperatures over 320 °C in theory [12]. Thus, a solder paste with low melting temperature used in the Si device was not suitable for the device [13]. To sum up, the SiC MOSFET package should satisfy the following requirements: 1) small packaging parasitic parameters to guarantee switching speed; 2) low package thermal resistance to facilitate rapid heat dissipation; 3) high-temperature package materials to enable the device to operate at high temperatures; and 4) high fatigue stress resistance to resist periodic temperature changes. Some of the advanced packages that have emerged so far for SiC MOSFET include wire-bondless interconnection packaging, press-pack packaging, 3-D packaging, and so on [14], [15]. A key objective of advanced packages is to reduce package parasitic parameters.

In conventional packaging, the die is soldered to copper lead frames or direct bond copper (DBC) substrates, and the gate and source are electrically connected to the terminals using bonding wires. Liang [16] proposed a wire-bondless SiC MOSFET with planar packaging, featuring a bare die sandwiched between two DBCs. Two heatsink pads were attached to these DBCs to allow double-side heat dissipation. To reduce mechanical stress caused by the rigid connection between the die and the DBC, a porous sintered silver interposer was introduced to the device. The interposer was positioned between the die and the DBC [17]. To overcome the mutual inductance between different current paths, Yang et al. [18] proposed a SiC MOSFET power module with an interleaved planar structure in which the currents of two adjacent die were in opposite directions. Another type of wire-bondless interconnection packaging is using a copper clip to replace the bonding wire [19], [20].

Fan-out panel-level packaging (FOPLP) facilitates device miniaturization. The redistribution layer (RDL) of this packaging method is critical to the electrical connection [21], [22], [23]. In a printed circuit board (PCB) embedded FOPLP, the bare die is first embedded into bismaleimide triazine (BT) laminate with almost the same thickness as the die. The gaps between BT and die were filled with photo imageable dielectric (PID) through exposure, development, and cure process. The RDL is subsequently fabricated through trepanning, copper deposition, and copper plating. Hou et al. [23] proposed a PCB-embedded FOPLP SiC MOSFET power module with laterally distributed dies. Regnat et al. [24] reported a similar packaging method but with dies distributed vertically. Fan et al. [25] proposed another, but facile FOPLP process where an epoxy molding compound (EMC) was used. In this process, first, the die was attached to the lead frame, then RDL was performed after molding. Shao et al. [26], [27] proposed single-die and dual-die MOSFETs with EMC-based FOPLP successively, realizing lower thermal resistance and ON-state resistance than wire-bonding structures. Due to the fewer and more convenient steps to finish die fixation, FOPLP using EMC exhibits lower costs and higher efficacy than PCB-embedded FOPLP.

Numerous studies have reported on novel MOSFET packages and their initial electrical properties [14], [16], [17], [18], [19], [20], [21], [22], [23], [24], [25]. However, the long-term reliability and robustness of packaging are key factors in applications [28], [29]. Because faults may generate after several years of application before causing device failure, accelerated lifetime tests (ALT) are performed to proactively verify the reliability of SiC MOSFET under various working conditions. Thermal cycling is a critical ALT reliability test in which periodic temperature stress is applied to the device under test to induce failures due to the mismatch coefficients of thermal expansion (CTE) between adjacent layers of the package [30], [31], [32]. Package failure modes during thermal cycling tests include die attachment layer voids and creaks and RDL peeling, which increased the  $R_{\rm DS(on)}$  value.

In this study, first, a SiC MOSFET with FOPLP was fabricated. Next, the performance and long-term reliability of the device were analyzed and performed in detail using both experimental and simulation methods. The remainder of this article is organized as follows. Section II introduces the SiC MOSFET FOPLP and details its packaging process. The analyses of parasitic inductance, thermal resistance, and mechanical performance are described in Section III. The initial electrical parameters and thermal cycling reliability of the package are discussed in Section IV. Finally, Section V provides concluding remarks.

## II. FOPLP SIC MOSFET AND ITS PACKAGING PROCESS

This section provides an overview of the structure and components of SiC MOSFET FOPLP followed by a detailed presentation of its packaging process.

#### A. Packaging Structure

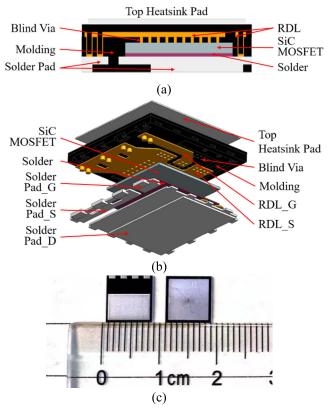

The SiC MOSFET FOPLP is composed of mainly SiC MOSFET die, RDL, solder, solder pad, and molding as depicted in Fig. 1. In this study, we used SiC MOSFET die (S4601M) from ROHM semiconductor rated at 1200 V, 136 A, and 12 m $\Omega$ . The size of the SiC MOSFET die was  $5 \times 5 \times 0.15$  mm, the surface metallization of the gate and source pad contained Ni/Pd/Au, and the surface metallization of the drain contained Ti/Ni/Au. Sn5Sb solder paste was used as a die attachment material. The source and gate pads of the die were connected to corresponding solder pads through RDL. The top heatsink pad was embedded in an EMC. Thus, the heat generated in the die can be dissipated through the solder pads and top heatsink pad which results in a doubleside cooling effect. The thermal and mechanical parameters of package components, including thermal conductivity (K), coefficient of thermal expansion (CTE), Young modulus (E), and Poisson's ratio (v), are listed in Table I.

#### B. Packaging Process

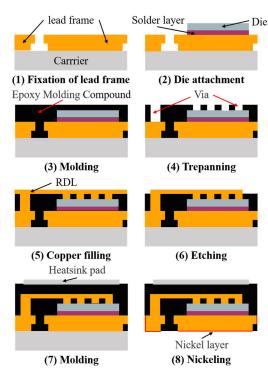

The SiC MOSFET FOPLP packaging process (see Fig. 2) is described as follows: 1) the lead frame was mounted on the

Fig. 1. SiC MOSFET FOPLP structure: (a) cross section view, (b) exploded view, and (c) photograph.

TABLE I

THERMAL AND MECHANICAL PARAMETERS OF PACKAGING MATERIALS

| Component                       | Material | K<br>(W/m⋅°C) | CTE<br>(ppm/°C) | E<br>(GPa) | v    |

|---------------------------------|----------|---------------|-----------------|------------|------|

| RDL Solder Pad,<br>Heatsink Pad | copper   | 401           | 18              | 110        | 0.34 |

| SiC MOSFET die                  | SiC      | 58.6          | 5.1             | 400        | 0.14 |

| Solder                          | Sn5Sb    | 70            | 31              | 49         | 0.38 |

| Molding                         | EMC      | 1.5           | 9               | 15         | 0.38 |

carrier; 2) solder paste was used to solder the die to the lead frame; 3) the die was covered with EMC; 4) specific vias were prepared in EMC using laser drilling for RDL construction; 5) a copper plate of 8  $\mu$ m thickness was deposited on the gate and source pads of the die, followed by filling the vias with copper using electroplating technique and forming a layer of copper on the EMC; 6) laser processing was performed to remove the extra copper layer; 7) the RDLs were encased in the EMC in the second molding process and then a top heatsink pad was mounted on the EMC; and 8) finally, the carrier was removed, and the solder pads were plated with nickel by chemical plating, which resulted in successful fabrication of an SiC MOSFET FOPLP with a dimension of  $8 \times 8 \times 0.75$  mm.

## III. ELECTRICAL, THERMAL AND MECHANICAL SIMULATIONS AND ANALYSIS

Electro-thermo-mechanical analyses were performed using the simulation method to evaluate the electrical, thermal, and mechanical performances of SiC MOSFET FOPLP. First, the

Fig. 2. Flowchart of SiC MOSFET FOPLP packaging process.

parasitic inductances of the package were extracted using the finite/boundary element (FBE) method in ANSYS Q3D. Next, the thermal resistances and soldering stresses were assessed using the finite element (FE) method in ANSYS Workbench.

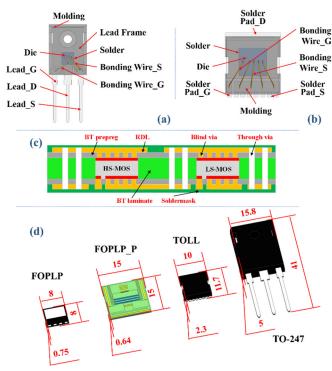

To compare with the developed SiC MOSFET FOPLP, three SiC MOSFETs were established with TO-247, TO leadless (TOLL) wire-bonding packaging, and PCB-embedded FOPLP wireless-bonding packaging. TO-247 is the most commonly used package mode in the past years, and TOLL with small size and small parasitic parameters is one of the state-of-the-art commercial SiC MOSFET packages. The TO-247 and TOLL have the same specification parameters as the FOPLP for the die, the solder layer, and the molding. In accordance with MIL-PRF-38535J, for both TO-247 and TOLL, four copper bonding wires of diameter 15 mil were selected to connect the source and source terminal, and one copper bonding wire of diameter 15 mil was used to connect the gate and gate terminal. The phase-leg SiC MOSFET module with PCB-embedded FOPLP (denoted as FOPLP\_P) is from our previous work, and the materials parameters can be referred from Hou et al. [23]. The FOPLP\_P contains a high-side SiC MOSFET (HS-MOS) and a low-side SiC MOSFET (LS-MOS). In this study, only HS-MOS was used to analyze.

The physical models of FOPLP, TOLL, TO-247, and FOLPL\_P are displayed in Figs. 1 and 3(a)–(c), respectively, and their dimensions are shown in Fig. 3(d).

#### A. Parasitic Inductance Simulation

Parasitic inductance is an inherent property of a conductor and depends on both the material and structure of the conductor. SiC MOSFET switching speeds are severely limited by packaging parasitic inductance. The package parasitic

Fig. 3. SiC MOSFET (a) TO-247, (b) TOLL wire-bonding packaging structures, and (c) PCB-embedded FOPLP wireless-bonding packaging [23]. (d) Size comparison of FOPLP, FOPLP\_P, TOLL, and TO-247 packages.

TABLE II

PARASITIC INDUCTANCE DEFINITIONS OF FOPLP, TOLL, TO-247, AND FOPLP\_P

| Package<br>type | Symbol           | Definition                                      |  |  |

|-----------------|------------------|-------------------------------------------------|--|--|

|                 | $L_{ m D}$       | From solder pad_D to solder                     |  |  |

| FOPLP           | $L_{ m S}$       | From RDL_S to solder pad_S                      |  |  |

|                 | $L_{ m G}$       | From solder pad_G to RDL_G                      |  |  |

|                 | $L_{ m D}$       | From solder pad _D to solder                    |  |  |

| TOLL            | $L_{\mathrm{S}}$ | From bonding wire_S to solder pad_S             |  |  |

|                 | $L_{ m G}$       | From solder pad_G to bonding wire_G             |  |  |

|                 | $L_{ m D}$       | From lead_D to solder                           |  |  |

| TO-247          | $L_{\rm S}$      | From bonding wire_S to lead_S                   |  |  |

|                 | $L_{ m G}$       | From lead_G to bonding wire_G                   |  |  |

|                 | $L_{ m D}$       | Interfaces between blind vias and HS-MOS drain  |  |  |

| FOPLP_P         | $L_{\mathrm{S}}$ | Interfaces between blind vias and HS-MOS gate   |  |  |

|                 | $L_{\rm G}$      | Interfaces between blind vias and HS-MOS source |  |  |

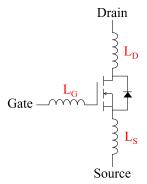

inductance of SiC MOSFET is composed of drain inductance  $(L_{\rm D})$ , source inductance  $(L_{\rm S})$ , and gate inductance  $(L_{\rm G})$  (see Fig. 4). Drain–source inductance  $(L_{\rm DS})$  is defined as the sum of  $L_{\rm D}$  and  $L_{\rm S}$ . Table II lists the parasitic inductance definitions of FOPLP, TOLL, and TO-247.

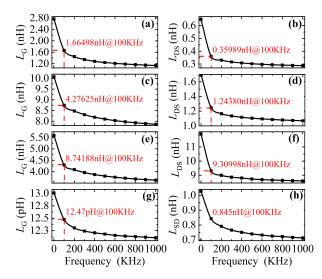

In inductance extraction, the bulk conductivity of copper and Sn5Sb solder were set as 5.8e7 and 7e6 S/m, respectively, and the relative permittivity of SiC was set as 10. The sweep frequency ranged from 0 to 1000 kHz. The simulated package parasitic inductances of FOPLP, TOLL, TO-247, and FOPLP\_P are shown in Fig. 5. The packaging parasitic inductance is dependent on the switching frequency. For the skin effect and proximity effect, the packaging parasitic inductance decreased with the switching frequency. However,

Fig. 4. Equivalent circuit diagram of the SiC MOSFET.

Fig. 5. Simulated package parasitic inductance versus switching frequency: (a)  $L_G$  of FOPLP, (b)  $L_{\rm DS}$  of FOPLP, (c)  $L_G$  of TOLL, (d)  $L_{\rm DS}$  of TOLL, (e)  $L_G$  of TO-247, (f)  $L_{\rm DS}$  of TO-247, (g)  $L_G$  of FOPLP\_P, and (h)  $L_{\rm DS}$  of FOPLP\_P.

the decrease rate continued progressively with the increase in the switching frequency.

Because of the longer conductive path and the bent in the bonding wire, the packaging parasitic inductances of TOLL and TO-247 are higher than those of FOPLP and FOPLP\_P. The  $L_{\rm G}$  and  $L_{\rm DS}$  of the FOPLP at 100 kHz were 1.66 and 0.36 nH, respectively, and the  $L_{\rm G}$  and  $L_{\rm DS}$  of the FOPLP\_P at 100 kHz were 12.47 pH and 0.845 nH, respectively. While the  $L_{\rm G}$  and  $L_{\rm DS}$  of TOLL at 100 kHz were 4.28 and 1.24 nH respectively, and the  $L_{\rm G}$  and  $L_{\rm DS}$  of TO-247 at 100 kHz were 8.74 and 9.31 nH respectively. Compared with TOLL, the  $L_{\rm G}$  and  $L_{\rm DS}$  of FOPLP decreased by 61.21% and 70.97%, respectively. And compared with TO-247, the  $L_{\rm G}$  and  $L_{\rm DS}$  of FOPLP decreased by 81% and 96%, respectively. Therefore, RDL, as an electrical interconnection component, provides a superior parasitic inductance reduction than the copper bonding wire.

#### B. Thermal Resistance Simulation

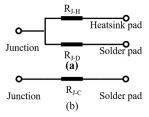

The high heating power, small size, and low thermal conductivity of EMC presented numerous thermal management challenges. Therefore, an efficient heat dissipation solution is necessary for SiC MOSFET. Double-sided cooling provided

Fig. 6. Equivalent thermal network resistance: (a) double-side cooling and (b) single-side cooling.

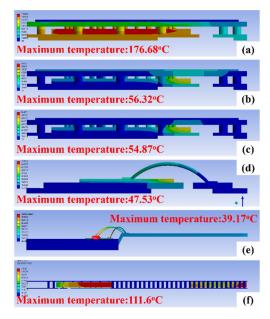

Fig. 7. Simulated temperature distribution results: (a) FOPLP using the heatsink pad for cooling, (b) FOPLP using the solder pad for cooling, (c) FOPLP with double-side cooling, (d) TOLL with single-side cooling, (e) TO-247 with single-side cooling, and (f) FOPLP\_P with single-side cooling.

by the FOPLP allows higher heat dissipation than single-sided cooling does as depicted in Fig. 6.

A thermal simulation was conducted to evaluate the heat dissipation effect of the FOPLP with double-side cooling. The heating power was set at 58.8 W, for the on-state current and on-state resistance of 70 A and 12 m $\Omega$ , respectively. The ambient temperature of 25 °C was applied on the heat dissipation surface, and two heat dissipation surfaces were realized at double-side cooling. The thermal parameters of packaging materials used in the simulation were listed in Table I. The thermal resistance is calculated by the equation given as

$$R = (T_{\text{junction}} - T_{\text{ambient}})/P_{\text{th}}$$

(1)

where  $T_{\text{junction}}$  is defined as the maximum simulated temperature for the die,  $T_{\text{ambient}}$  is the ambient temperature, and  $P_{\text{th}}$  is the internal heat power.

The simulated temperature distribution results of FOPLP under various cooling conditions are displayed in Fig. 7(a)–(c). Because the die and heatsink pad were separated by EMC with low thermal conductivity, the maximum temperature reached 176.68 °C when using only the heatsink pad for cooling [see Fig. 7(a)]. Another scenario involves attaching a solder pad to a die through RDLs. In this

TABLE III

DEFINITIONS AND VALUES OF THERMAL RESISTANCE

| Package<br>types | Symbols         | Definitions                                        | Values<br>(°C/W) |

|------------------|-----------------|----------------------------------------------------|------------------|

| FOPLP            | $R_{	ext{J-H}}$ | From junction to heatsink                          | 2.58             |

|                  | $R_{	ext{J-S}}$ | From junction to solder pad                        | 0.53             |

|                  | $R_{	ext{J-C}}$ | From junction to case with double side dissipation | 0.51             |

| TOLL             | $R_{	ext{J-C}}$ | From junction to case                              | 0.38             |

| TO-247           | $R_{	ext{J-C}}$ | From junction to case                              | 0.24             |

| FOPLP_P          | $R_{	ext{J-C}}$ | From junction to case                              | 1.47             |

case, the maximum temperature reached only 56.32 °C [see Fig. 7(b)]. The best heat dissipation capability was achieved when double-sided cooling FOPLP was used, and a maximum temperature of only 54.87 °C was recorded [see Fig. 7(c)].

Among TOLL, TO-247, and FOPLP\_P, only one side was used for cooling. As displayed in Fig. 7(d)–(f), the maximum temperature of TOLL, TO-247, and FOPLP\_P SiC MOSFETs under the same simulation condition as FOPLP were 47.53 °C, 39.17 °C, and 111.6 °C. The TOLL and TO-247 packages exhibit a maximum temperature lower than the FOPLP and FOPLP\_P package. The thermal resistance can be calculated from the simulation results. Table III compares the thermal resistance values of the FOPLP, TOLL, TO-247, and FOPLP\_P packages. It can be noted that the volumes of TOLL and TO-247 are most of the time greater than the FOPLP package. Numerically, the volumes of FOPLP, FOPLP\_P TOLL, and TO-247 are 47.49, 130.54, 226.55, and 1156 mm³, respectively, in the ratio of 1:2.74:4.77:24.34.

#### C. Thermo-Mechanical Simulation

In the die attachment process, the die, solder, and lead frame undergo reflow soldering at 250 °C. When the temperature decreased to room temperature (25 °C), residual stress was readily brought to the assembly, for the CTE mismatch in adjacent materials. Residual stress generated in the reflow soldering process was simulated using the FE method to investigate the thermo–mechanical properties of the assembly and the thermo-mechanical parameters of packaging materials used in the simulation are listed in Table I.

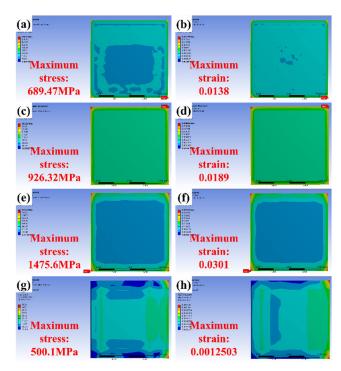

In the simulation, the temperature decreased from 250 °C to 25 °C. Remote displacement was imposed on the bottom surface of the lead frame or solder pad\_D. Furthermore, the contact between the adjacent layers was assumed to be ideal, and dimension tolerances, which were dependent on the packaging process were also not considered. The simulated static thermo–mechanical performance results in FOPLP, TOLL, TO-247, and FOPLP\_P packaging dies are displayed in Fig. 8. The maximum strains and stresses in both FOPLP, TOLL, TO-247, and FOPLP\_P occurred in the corner of die. However, the dies in TOLL and TO-247 should withstand a larger mechanical load.

The maximum stress and strain of FOPLP were 689.47 MPa and 0.0138, respectively. The maximum stress and strain of TOLL were 926.32 MPa and 0.0189, respectively. The maximum stress and strain of TO-247 were 1475.60 MPa and 0.0301, respectively. The maximum stress and strain

Fig. 8. Static thermo-mechanical simulation results in the dies of different packages: (a) maximum stress of FOPLP, (b) maximum strain of FOPLP, (c) maximum stress of TOLL, (d) maximum strain of TOLL, (e) maximum stress of TO-247, (f) maximum strain of TO-247, (g) maximum stress of FOPLP\_P, and (h) maximum strain of FOPLP\_P.

of FOPLP\_P were 500.1 MPa and 0.0012503, respectively. Compared with TOLL and TO-247, the FOPLP relieved the residual stress of packaging materials and reduced their deformation. Compared to TOLL, the maximum stress and strain of FOPLP decreased by approximately 25.57% and 26.98%, respectively. Compared to TO-247, the maximum stress and strain of FOPLP decreased by approximately 53.27% and 54.15%, respectively.

Generally, as a wire-bondless interconnection packaging, RDL is used in FOPLP to replace bonding wire. So FOPLP exhibits lower parasitic inductance compared to wire-bonding TO-247 and TOLL. The miniaturization of FOPLP also reduces the thermal stress in the packaging when an unreasonable temperature change occurs. Because the source, gate, and drain are all connected by thin RDL, FOPLP\_P has superior thermo—mechanical performance over FOPLP. However, thermal management challenges the application of FOPLP, for its higher power density.

#### IV. INITIAL PERFORMANCE AND LONG-TERM RELIABILITY CHARACTERIZATIONS OF SIC MOSFET FOPLP

The initial performance of SiC MOSFET FOPLP was measured to verify its proper functionality. Next, the thermal cycling test of SiC MOSFET FOPLP was performed for long-term reliability investigation.

As shown in Fig. 9, the devices were electrically connected to the tester using a custom high-power socket for static parameters measurement; for capacitance measurement, the devices were soldered on the PCB with an edge connector.

Fig. 9. (a) Custom socket for static parameter measurement and (b) PCB for capacitance measurement.

TABLE IV

MEASURED STATIC PARAMETERS RESULTS OF SIC MOSFET FOPLP

| Symbols              | Conditions                                            | Units | Mean<br>values | Variances | Maximum values of die |

|----------------------|-------------------------------------------------------|-------|----------------|-----------|-----------------------|

| $I_{ m DSS}$         | $V_{\rm DS}$ =950V                                    | μΑ    | 2.90           | 1.46      | 80                    |

| $I_{\mathrm{GSS^+}}$ | $V_{\rm GS}=23{ m V}$                                 | nA    | 69.48          | 9.81      | 100                   |

| $I_{\mathrm{GSS-}}$  | $V_{\rm GS}$ =-2V                                     | nA    | -<br>14.47     | 1.02      | -100                  |

| $V_{ m GS(th)}$      | $V_{\rm DS}=V_{\rm GS},$<br>$I_{\rm D}=35.1 {\rm mA}$ | V     | 3.13           | 0.21      | 4.5                   |

| $R_{ m ds(on)}$      | $I_{\rm D}$ =70A,<br>$V_{\rm GS}$ =18V                | mΩ    | 10.88          | 0.11      | 15                    |

Fig. 10. Measured capacitances versus the drain–source voltage (0-1300 V).

#### A. Initial Performance Characterization

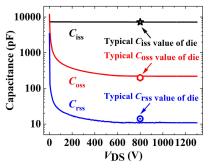

The static parameters of SiC MOSFET FOPLP including zero gate voltage drain current  $(I_{DSS})$ , gate-source leakage current  $(I_{GSS})$ , gate threshold voltage  $[V_{GS(th)}]$ , and ONstate resistance  $[R_{DS(on)}]$  were measured by using a static parameter tester (1600A-MT, HUSTEC). The results are listed in Table IV. All static parameter values were lower than the corresponding maximum values of the die provided in the datasheet. The input capacitance  $(C_{iss})$ , output capacitance  $(C_{oss})$ , and reverse transfer capacitance  $(C_{rss})$  were tested in a curve tracer (B1505A, Agilent) under the following test conditions:  $V_{GS} = 0$  V, f = 1 MHz, and the test results are shown in Fig. 10. The measured  $C_{iss}$ ,  $C_{oss}$ , and  $C_{rss}$  at 800 V were close to the typical values of die. The capacitances decreased with the frequency. From  $V_{DS}$  values of 0 to 100 V, the capacitances decreased notably. Capacitances gradually decreased and leveled off as the drain-source voltage increased from 100 to 1300 V.

#### B. Thermal Cycling Reliability Analysis

The thermal cycling test is widely used to investigate the effect of periodical temperature changes on the packaging

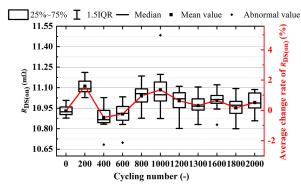

Fig. 11. Variation of  $R_{DS(on)}$  during aging cycles.

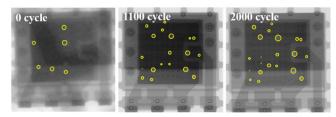

Fig. 12. X-RAY images at 0, 1100, and 2000 cycles.

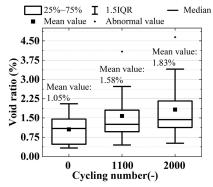

Fig. 13. Void ratios at 0, 1100, and 2000 cycles.

material interfaces. In a thermal cycling test, the device temperature is changed by varying the testing chamber temperature between the upper and lower limits. The thermal cycling test was conducted on 12 samples of SiC MOSFET FOPLPs by using an environmental chamber (EC-106MHHP, HITACHI). Test temperatures ranged from  $-55\,^{\circ}\text{C}$  to  $125\,^{\circ}\text{C}$ , and the holding time and conversion time were 15 and 10 min, respectively.

ON-state resistance  $[R_{\rm DS(on)}]$  will increase when degradation occurred in the solder or the interconnection between the die and RDL. Thus,  $R_{\rm DS(on)}$ , as a degradation precursor, is typically used to determine the packaging fatigue failure occurring in thermal cycling. Here,  $R_{\rm DS(on)}$  was experimentally monitored during the test process through a static parameter tester (1600A-MT, HUSTEC). Fig. 11 displays the variation of  $R_{\rm DS(on)}$ during aging cycles. The  $R_{\rm DS(on)}$ value basically remained constant over the test process, and the maximum average change rate of  $R_{\rm DS(on)}$  was less than 2%. The stability of  $R_{\rm DS(on)}$  proved the high reliability of the package.

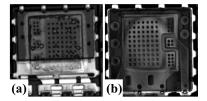

To detect the states of the solder and the interconnection between the die and RDL, X-RAY, and C-SAM tests were

Fig. 14. C-SAM images of the sample at 2000 cycles: (a) bottom view and (b) top view.

carried out for aged samples. Nordson DAGE XD7500 was used to perform X-RAY characterization. All samples were imaged prior to cycling to provide a basis for comparison and subsequently imaged at 1100 and 2000 cycles. The X-ray images are displayed in Fig. 12. The number of voids increased with the increase in aging cycles. FiJi distribution of ImageJ was used to count the void ratio of all samples, and the voids were marked with a vellow circle. The results are depicted in Fig. 13. The mean void ratios at 0, 1100, and 2000 were recorded as 1.05%, 1.58%, and 1.83%, respectively. The increase in void ratios was related to the crack propagation that occurred during thermal cycling [33]. The C-SAM images of the sample subjected to 2000 aging cycles were captured using SHSIWI YTS-500. Fig. 14(a) illustrates the presence of voids in solder; however, no delamination was observed. Fig. 14(b) reveals that the RDL was firmly connected to the die. The increase in void or lateral crack increases  $R_{\rm DS(on)}$  slightly. The delamination of the interface between various materials can result in device failure.

#### V. CONCLUSION

In this article, SiC MOSFET FOPLP was fabricated, analyzed, and characterized. The simulation method was used to investigate the high electric, thermal, and mechanical performances of SiC MOSFET FOPLP. The initial performance and long-term reliability of the device were experimentally verified. Compared with conventional wirebonded packaging, the proposed method reduced drain–source parasitic inductance by 96% at 100 kHz. Because of double-sided cooling, the package exhibited a low thermal resistance of 0.55 °C/W. Compared with TOLL and TO-247, the soldering stress and strain were alleviated in FOPLP. The static and dynamic parameters of the package were consistent with those provided on the bare die datasheet. The drain–source ON-state resistance increased by less than 2% after 2000 thermal cycles, which revealed the durability of the packages.

#### REFERENCES

- L. F. S. Alves, P. Lefranc, P. O. Jeannin, and B. Sarrazin, "Review on SiC-MOSFET devices and associated gate drivers," in *Proc. IEEE Int. Conf. Ind. Technol. (ICIT)*, Feb. 2018, pp. 824–829, doi: 10.1109/ICIT.2018.8352284.

- [2] T. Kimoto et al., "Progress and future challenges of SiC power devices and process technology," in *IEDM Tech. Dig.*, Dec. 2017, pp. 9.5.1–9.5.4, doi: 10.1109/IEDM.2017.8268360.

- [3] X. Wang, H. Wen, and Y. Zhu, "Review of SiC power devices for electrical power systems: Characteristics, protection, and application," in *Proc. 6th Asia Conf. Power Electr. Eng. (ACPEE)*, Apr. 2021, pp. 1–5, doi: 10.1109/ACPEE51499.2021.9437108.

- [4] X. She, A. Q. Huang, Ó. Lucía, and B. Ozpineci, "Review of silicon carbide power devices and their applications," *IEEE Trans. Ind. Electron.*, vol. 64, no. 10, pp. 8193–8205, Oct. 2017, doi: 10.1109/ TIE.2017.2652401.

- [5] C. Chen, F. Luo, and Y. Kang, "A review of SiC power module packaging: Layout, material system and integration," *CPSS Trans. Power Electron. Appl.*, vol. 2, no. 3, pp. 170–186, Sep. 2017, doi: 10.24295/CPSSTPEA.2017.00017.

- [6] H. Lee, V. Smet, and R. Tummala, "A review of SiC power module packaging technologies: Challenges, advances, and emerging issues," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 1, pp. 239–255, Nov. 2020, doi: 10.1109/JESTPE.2019.2951801.

- [7] B. Zhang and S. Wang, "Parasitic inductance modeling and reduction for wire-bonded half-bridge SiC multichip power modules," *IEEE Trans. Power Electron.*, vol. 36, no. 5, pp. 5892–5903, May 2021, doi: 10.1109/TPEL.2020.3032521.

- [8] K. Ashu, J. Johansson, and R. Pugo, "Estimation of wirebonded package inductance and resistance using statistical DOE/RSM," in *Proc. Electr. Design Adv. Packag. Syst. (EDAPS)*, Dec. 2019, pp. 1–3, doi: 10.1109/EDAPS47854.2019.9011650.

- [9] J. Wang, H. S. H. Chung, and R. T. H. Li, "Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 573–590, Jan. 2013, doi: 10.1109/TPEL.2012.2195332.

- [10] Z. Chen, D. Boroyevich, and R. Burgos, "Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics," in *Proc. Int. Power Electron. Conf. (ECCE ASIA)*, Jun. 2010, pp. 164–169, doi: 10.1109/IPEC.2010.5543851.

- [11] M. Wang, F. Luo, and L. Xu, "A double-end sourced multi-chip improved wire-bonded SiC MOSFET power module design," in *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Mar. 2016, pp. 709–714, doi: 10.1109/APEC.2016.7467949.

- [12] X. Zhong, X. Wu, W. Zhou, and K. Sheng, "An all-SiC high-frequency boost DC–DC converter operating at 320 °C junction temperature," *IEEE Trans. Power Electron.*, vol. 29, no. 10, pp. 5091–5096, Oct. 2014, doi: 10.1109/TPEL.2014.2311800.

- [13] G. Tang, T. C. Chai, and X. Zhang, "Thermal optimization and characterization of SiC-based high power electronics packages with advanced thermal design," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 9, no. 5, pp. 854–863, May 2019, doi: 10.1109/TCPMT.2018.2860998.

- [14] H. Fengze, W. Wenbo, C. Liqiang, L. Jun, and S. Meiying, "Review of packaging schemes for power module," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 1, pp. 223–238, Mar. 2019, doi: 10.1109/JESTPE.2019.2947645.

- [15] J. Schuderer, U. Vemulapati, and F. Traub, "Packaging SiC power semiconductors—Challenges, technologies and strategies," in *Proc. IEEE Workshop Wide Bandgap Power Devices Appl.*, Oct. 2014, pp. 18–23, doi: 10.1109/WiPDA.2014.6964616.

- [16] Z. Liang, "Planar-bond-all: A technology for three-dimensional integration of multiple packaging functions into advanced power modules," in *Proc. IEEE Int. Workshop Integr. Power Packag. (IWIPP)*, May 2015, pp. 115–118, doi: 10.1109/IWIPP.2015.7295992.

- [17] C. Ding, H. Liu, K. D. T. Ngo, R. Burgos, and G. Q. Lu, "A double-side cooled SiC MOSFET power module with sintered-silver interposers: Idesign, simulation, fabrication, and performance characterization," *IEEE Trans. Power Electron.*, vol. 36, no. 10, pp. 11672–11680, Oct. 2021, doi: 10.1109/TPEL.2021.3070326.

- [18] F. Yang et al., "Interleaved planar packaging method of multichip SiC power module for thermal and electrical performance improvement," *IEEE Trans. Power Electron.*, vol. 37, no. 2, pp. 1615–1629, Feb. 2022, doi: 10.1109/TPEL.2021.3106316.

- [19] J. A. Herbsommer, J. Noquil, O. Lopez, and D. Jauregui, "Innovative 3D integration of power MOSFETs for synchronous buck converters," in *Proc. 26th Annu. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Mar. 2011, pp. 1273–1274, doi: 10.1109/APEC.2011.5744756.

- [20] L. Wang et al., "Cu clip-bonding method with optimized source inductance for current balancing in multichip SiC MOSFET power module," *IEEE Trans. Power Electron.*, vol. 37, no. 7, pp. 7952–7964, Jul. 2022, doi: 10.1109/TPEL.2022.3141373.

- [21] J. Fan et al., "Genetic algorithm-assisted design of redistribution layer vias for a fan-out panel-level SiC MOSFET power module packaging," in *Proc. IEEE 72nd Electron. Compon. Technol. Conf. (ECTC)*, May 2022, pp. 260–265, doi: 10.1109/ECTC51906.2022.00049.

- [22] J. Jiang et al., "Research on FOPLP package of multi-chip power module," in *Proc. IEEE 8th Electron. Syst.-Integr. Technol. Conf. (ESTC)*, Sep. 2020, pp. 1–6, doi: 10.1109/ESTC48849.2020. 9229816.

- [23] F. Hou et al., "Fan-out panel-level PCB-embedded SiC power MOSFETs packaging," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 1, pp. 367–380, Nov. 2020, doi: 10.1109/JESTPE.2019.2952238.

- [24] G. Regnat et al., "Silicon carbide power chip on chip module based on embedded die technology with paralleled dies," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, Sep. 2015, pp. 4913–4919, doi: 10.1109/ECCE.2015.7310353.

- [25] Y. Qian, F. Hou, J. Fan, Q. Lv, X. Fan, and G. Zhang, "Design of a fan-out panel-level SiC MOSFET power module using ant colony optimization-back propagation neural network," *IEEE Trans. Electron Devices*, vol. 68, no. 7, pp. 3460–3467, May 2021, doi: 10.1109/ TED.2021.3077209.

- [26] Z. Liang, D. Shao, K. Ding, and C. Tian, "Design and analysis of MOSFET based on fan-out panel-level package technology," in *Proc.* 22nd Int. Conf. Electron. Packag. Technol. (ICEPT), Sep. 2021, pp. 1–4, doi: 10.1109/ICEPT52650.2021.9568028.

- [27] J. Li, D. Shao, and K. Ding, "Optimizing R<sub>DS(on)</sub> of dual-chip power MOSFET by fan-out panel level packaging (FOPLP)," in *Proc. 23rd Int. Conf. Electron. Packag. Technol. (ICEPT)*, Aug. 2022, pp. 1–3, doi: 10.1109/ICEPT56209.2022.9872647.

- [28] H. Wang et al., "Transitioning to physics-of-failure as a reliability driver in power electronics," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 2, no. 1, pp. 97–114, Mar. 2014, doi: 10.1109/JESTPE.2013.2290282.

- [29] H. Wang, M. Liserre, and F. Blaabjerg, "Toward reliable power electronics: Challenges, design tools, and opportunities," *IEEE Ind. Electron. Mag.*, vol. 7, no. 2, pp. 17–26, Jun. 2013, doi: 10.1109/ MIE.2013.2252958.

- [30] L. Yang et al., "Electrical performance and reliability characterization of a SiC MOSFET power module with embedded decoupling capacitors," *IEEE Trans. Power Electron.*, vol. 33, no. 12, pp. 10594–10601, Dec. 2018, doi: 10.1109/TPEL.2018.2809923.

- [31] B. Mouawad, L. Yang, P. Agyakwa, M. Corfield, and C. M. Johnson, "Packaging degradation studies of high temperature SiC MOSFET discrete packages," in *Proc. 32nd Int. Symp. Power Semiconductor Devices ICs (ISPSD)*, Sep. 2020, pp. 90–93, doi: 10.1109/ISPSD46842. 2020.9170030.

- [32] D. H. Kim, A. S. Oh, E. Y. Park, K. H. Kim, S. J. Jeon, and H. C. Bae, "Thermal and electrical reliability analysis of TO-247 for bonding method, substrate structure and heat dissipation bonding material," in *Proc. IEEE 71st Electron. Compon. Technol. Conf. (ECTC)*, Jun. 2021, pp. 1950–1956, doi: 10.1109/ECTC32696.2021.00308.

- [33] J. Fan, J. Wu, C. Jiang, H. Zhang, M. Ibrahim, and L. Deng, "Random voids generation and effect of thermal shock load on mechanical reliability of light-emitting diode flip chip solder joints," *Materials*, vol. 13, no. 1, p. 94, 2020, doi: 10.3390/ma13010094.