## A Hybrid Magnetic Current Sensor With a Dual Differential DC Servo Loop

Jouyaeian, Amirhossein; Fan, Qinwen; Ausserlechner, Udo; Motz, Mario; Makinwa, Kofi A.A.

DOI 10.1109/JSSC.2023.3307471

Publication date 2023 **Document Version** Final published version

Published in IEEE Journal of Solid-State Circuits

Citation (APA) Jouyaeian, A., Fan, Q., Ausserlechner, U., Motz, M., & Makinwa, K. A. A. (2023). A Hybrid Magnetic Current Sensor With a Dual Differential DC Servo Loop. *IEEE Journal of Solid-State Circuits*, *58*(12), 3442-3449. Article 3307471. https://doi.org/10.1109/JSSC.2023.3307471

### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

# 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A Hybrid Magnetic Current Sensor With a Dual Differential DC Servo Loop

Amirhossein Jouyaeian<sup>(D)</sup>, *Member, IEEE*, Qinwen Fan, *Senior Member, IEEE*, Udo Ausserlechner<sup>(D)</sup>, Mario Motz, *Member, IEEE*, and Kofi A. A. Makinwa<sup>(D)</sup>, *Fellow, IEEE*

Abstract—This article presents a hybrid magnetic current sensor for contactless current measurement. Pick-up coils and Hall plates are employed to sense the high and low-frequency fields, respectively, generated by a current-carrying conductor. Due to the differentiating characteristic of the pick-up coils, a flat frequency response can then be obtained by summing the outputs of the coil and the Hall paths and passing the result through a 1st-order low-pass filter (LPF). For maximum resolution, the LPF corner frequency (2 kHz) is set such that the noise contribution of each path is equal. To suppress the coil-path offset without the use of large ac coupling capacitors, an area-efficient dual dc servo loop (D3SL) is used. This effectively suppresses the coilpath offset, resulting in a total offset of 73  $\mu$ T, which is mainly dominated by the Hall path. Fabricated in a standard 0.18-µm CMOS process, the current sensor occupies 3.9 mm<sup>2</sup> and draws 7.1 mA from a 1.8 V supply. It achieves 43 mA resolution in a 5 MHz bandwidth, which is 1.5× better than the state-of-theart hybrid sensors. It also achieves the lowest energy efficiency FoM (3.5x) among CMOS magnetic current sensors.

*Index Terms*—Contactless sensing, dc servo loop (DSL), high resolution, hybrid current sensors, magnetic current sensing, temperature compensation.

#### I. INTRODUCTION

AGNETIC current sensors are widely employed in high-voltage industrial applications such as electric drivers, photovoltaic inverters, chargers, and power supplies. In such applications, their inherent galvanic isolation outweighs their lower accuracy and resolution compared to shunt-based sensors [1], [2], [3], [4].

Magnetic current sensors can be made using fluxgates [5], [6], [7], magnetoimpedance [8] and tunneling magnetoresistance (TMR) [9] sensors. Their limited linearity means that closed-loop current sensing schemes are required to achieve high dynamic range (DR) [5]. However, the need to drive a field-canceling coil makes it difficult to achieve wide bandwidth. Furthermore, magnetoimpedance and TMR

Manuscript received 15 May 2023; revised 25 July 2023; accepted 15 August 2023. Date of publication 6 September 2023; date of current version 28 November 2023. This article was approved by Associate Editor Drew Hall. (*Corresponding author: Amirhossein Jouyaeian.*)

Amirhossein Jouyaeian, Qinwen Fan, and Kofi A. A. Makinwa are with the Electronic Instrumentation Laboratory, Microelectronics Department, Faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS), Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: a.jouyaeian@tudelft.nl).

Udo Ausserlechner and Mario Motz are with Infineon Technologies AG, 9500 Villach, Austria.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2023.3307471.

Digital Object Identifier 10.1109/JSSC.2023.3307471

sensors are not CMOS-compatible, leading to two-die solutions and increased production cost.

Alternatively, magnetic current sensors can be made using CMOS-compatible Hall plates and pick-up coils, which have a much wider linear input range [10], [11], [12], [13], [14], [15]. However, although they can achieve wide bandwidths, pick-up coils cannot sense dc signals, while the resolution of Hall plates decreases with the square-root of bandwidth due to its thermal noise. By combining Hall plates and pick-up coils, hybrid current sensors with wide bandwidth and high resolution can be realized [16], [17], [18], [19], [20].

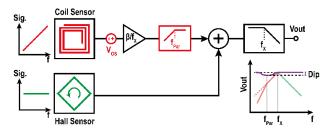

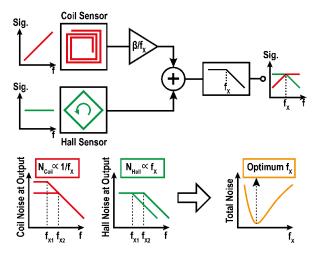

One of the main challenges in the design of hybrid current sensors is achieving a flat response over the frequency range. A current sensor with a flat frequency response ensures compatibility with frequency-dependent systems, enabling accurate current monitoring and control over a wide frequency range. As shown in Fig. 1, a 1st-order low-pass filter (LPF) can be used to smoothly combine the differentiating characteristic of coils and the all-pass characteristic of Hall plates. The corner frequency of the LPF defines the crossover frequency  $f_X$ , which also defines the sensor's noise bandwidth. For maximum resolution,  $f_X$  should be chosen such that the Hall and coil paths contribute the same amount of noise. In practice, a highpass filter (HPF) is required to block the offset of the coil path, which may often be significantly larger than the mV-level output of the Hall plates. However, the HPF creates a parasitic pole at  $f_{Par}$  in the coil path, which, in turn, causes a dip around  $f_X$  in the combined response of the two signal paths. To minimize this dip,  $f_{Par}$  must be set much lower than  $f_X$ , which is quite challenging since  $f_X$  is typically in the order of a few kHz.

In [17], the crossover frequency  $f_X$  (=2 kHz) was optimized for maximum resolution, while coil-path offset was blocked by the combination of ac-coupling and a dc-servo loop. However, a large off-chip capacitor (10  $\mu$ F) was used to stabilize the dc servo loop (DSL). Furthermore, this design sensed the coil voltage, which, due to its differentiating characteristic, limited its high-frequency DR. The sensor achieved a resolution of 480 mA<sub>rms</sub> in a 3 MHz BW and consumed 38.5 mW.

In [20], a hybrid current sensor achieves greater DR by reading out the coil current instead of the coil voltage. To eliminate the need for external components, its coil path employed a two-stage LPF. Coil-path offset was then blocked by a large on-chip capacitor (1.2 nF) placed between the two stages. However, the resulting parasitic pole caused a 3% dip in the sensor's frequency response around  $f_x$  (=10 kHz). Compared

0018-9200 © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 1. Effect of parasitic pole on the gain flatness.

Fig. 2. System block diagram and optimum crossover frequency.

to [17], this sensor achieves  $7 \times$  better resolution (69 mA<sub>rms</sub>) and  $3 \times$  less power dissipation (14 mW).

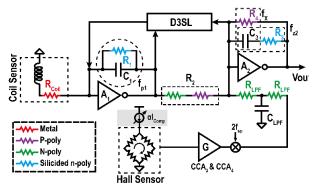

In this article, an extended version of [21], the design of a hybrid magnetic current sensor with an optimized crossover frequency is presented. As in [16] and [20], a two-stage coil path is used. However, to simultaneously suppress coil-path offset and achieve good gain flatness, the large blocking capacitor in [16] and [20] is replaced by an area-efficient dual-differential dc servo loop (D3SL). The gain drift with temperature of the Hall plates is partially compensated by a near-PTAT bias current. Their remaining gain drift is compensated for by designing the amplifiers in the Hall path to have a temperature-dependent gain. A similar approach is used to compensate for the gain drift of the coil path.

The rest of this article is organized as follows. The proposed system, including the crossover frequency optimization for noise, the design of the D3SL, and the temperature compensation in both the coil path and Hall path, are presented in Section II. Section III shows and discusses the measurement results. Finally, conclusions are drawn in Section IV.

#### II. PROPOSED HYBRID MAGNETIC CURRENT SENSOR

#### A. System Architecture

A system block diagram of the proposed hybrid current sensor is shown in Fig. 2. A LPF with a corner frequency  $f_X$  is used to flatten the coil's differentiating characteristic and to limit the noise bandwidth of the Hall path. To achieve a flat response, the output of the coil path at  $f_X$  must be equal to that of the Hall path. As a result, the gain of the coil path can be expressed as  $\beta/f_X$ , where  $\beta$  is a constant. Taking into

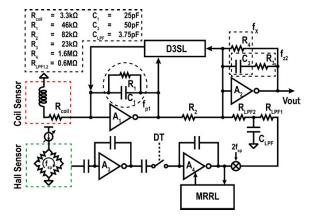

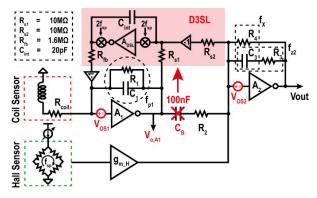

Fig. 3. Simplified single-ended schematic of the hybrid sensor.

account the equivalent noise bandwidth of a 1st-order filter, the total output noise power of the Hall path is proportional to  $f_X$  and can be expressed as

$$N_{\text{Hall}} = 2kTR_{\text{H}} \times \pi f_{\text{X}} \tag{1}$$

where  $R_{\rm H}$  is the output resistance of the Hall plate. In contrast, the output noise power of the coil path is inversely proportional to  $f_{\rm X}$  and can be expressed as

$$N_{\rm Coil} = 2kTR_{\rm C} \times \beta^2 \times \frac{\pi}{f_{\rm X}}$$

(2)

where  $R_{\rm C}$  is the resistance of the coil.

The sensor's total noise power is the sum of the contributions of the coil path and the Hall path. As shown in Fig. 2, if the crossover frequency is set too low, the noise of the coil path will be dominant, while if it is set too high, the noise of the Hall path will become dominant. At the optimum crossover frequency, the noise contribution of both paths is equal, resulting in the minimum total output noise. This optimized crossover frequency can be calculated as

$$f_{\rm X,Opt} = \sqrt{\frac{R_{\rm C}}{R_{\rm H}}} \times \beta.$$

(3)

In this design,  $f_{X,Opt}$  is 2 kHz. Simulations show that even large (20%) variations in  $f_X$  only increase the total noise slightly (<4%). Therefore, no trimming is required.

A simplified single-ended schematic of the proposed hybrid current sensor is shown in Fig. 3, while the actual implementation is fully differential. As in [16] and [20], the coil path employs a two-stage LPF based on a pole-zero cancellation scheme for reading out the coil current. The first stage sets a pole  $f_{p1} = 140$  kHz  $(1/2\pi R_1C_1)$  to limit the first-stage output swing at high frequencies, while the second stage cancels the pole  $f_{p1}$  with a zero  $f_{z2}$   $(1/2\pi R_3C_3)$  and introduces a new pole  $f_X = 2$  kHz  $(1/2\pi R_4C_3)$ . The pole  $f_X$  sets the crossover frequency and is chosen for maximum resolution. To ensure the robustness of the pole-zero cancellation scheme, the same type of components are used to realize  $f_{p1}$  and  $f_{z2}$ .

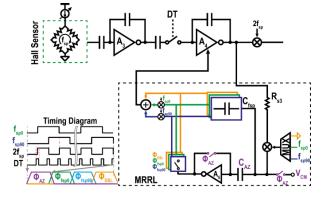

In the Hall path, the up-modulated outputs of the spinning Hall plates are first amplified by two capacitively coupled amplifiers (CCAs). The amplified Hall signal is then demodulated back to dc and injected into the 2nd stage of the coil path via an LPF with a pole at  $f_{z2}$ . The combination of this LPF

Fig. 4. Multiplexed RRL

and the transfer function of the coil-path's 2nd stage results in a 1st-order LPF with a pole at  $f_X$ .

As in [20], a multiplexed ripple-reduction-loop (MRRL) is used to suppress spinning-induced ripple (Fig. 4), which is caused by the offset of the Hall plates [22]. The ripple can be decomposed into four orthogonal components: two square waves in quadrature at  $f_{sp}$ , a square wave at  $2f_{sp}$  that results in a residual offset in the final output, and a dc component that is blocked by the first CCA. The MRRL operates in four phases to consecutively suppress the quadrature component at  $f_{sp}$ , the offset of  $A_4$ , and the offset of  $A_5$ . In the first two phases, the MRRL is configured as a ripple-reduction loop (RRL), which senses the ripple via a sensing resistor  $R_{s3}$  (=10 M $\Omega$ ) and a chopper demodulator. The resulting dc signal  $C_{\rm fsp}$  (=5 pF) to generate a correction signal, which is then up-modulated and fed back to the amplifier A<sub>4</sub> via an auxiliary input stage. In the second phase, the choppers are disabled, and the MRRL functions as a DSL to attenuate the offset of  $A_4$ . In the last phase, the offset of A<sub>5</sub> is autozeroed to reduce the residual ripple it causes.

#### B. Dual Differential DC Servo Loop

To achieve accurate sensing of dc signals using the Hall path, it is essential to eliminate the offset contribution of the coil path. Without an offset cancellation technique, the offsets of  $A_1$  and  $A_2$  would be amplified, resulting in an output-referred offset in the coil path (Fig. 5)

$$V_{\rm OS,Out} = -\left(1 + \frac{R_1}{R_{\rm Coil}}\right) \left(\frac{R_4}{R_2}\right) V_{\rm OS1} + \left(1 + \frac{R_4}{R_2}\right) V_{\rm OS2} \qquad (4)$$

where  $V_{OS1}$  and  $V_{OS2}$  are input-referred offsets of A<sub>1</sub> and A<sub>2</sub>, respectively. In [16] and [20], a blocking capacitor is used between the coil-path stages to attenuate the coil-path offset. Due to its high impedance at dc, the blocking capacitor rejects  $V_{OS1}$  and ensures that  $V_{OS2}$  appears at the output with a gain of 1. However, the blocking capacitor  $C_B$  and the series resistor  $R_2$  create a parasitic pole  $f_{Par}$  (=230 Hz), which causes a dip in the sensor's transfer function. In [20],  $C_B$  (1.2 nF) occupies more than 10% of the chip area, and  $R_2$  (500 k $\Omega$ ) contributes 25% of the noise in the coil path. Therefore, it is not possible to further increase the size of these components to decrease  $f_{Par}$ . Instead, a higher than optimal crossover frequency (10 kHz rather than 2 kHz) was chosen in [20] to achieve less than 3% dip around  $f_X$ . To achieve the optimum

Fig. 5. Dual differential dc servo loop.

crossover frequency (2 kHz), reduce the noise contribution of  $R_2$  to less than 5%, and achieve a gain flatness of  $\pm 1\%$ , a  $100 \times$  larger blocking capacitor would be required, which is not practical.

Therefore, the blocking capacitor is replaced by a D3SL in this work (see Fig. 5). It senses the dc voltage across  $R_2$  and drives it to zero by regulating the output of A<sub>1</sub>. Like a blocking capacitor, this ensures that the dc current flowing through  $R_2$  is zero, by driving the output-referred offset of A<sub>1</sub> to  $V_{OS2}$ .

In the proposed scheme, the voltage across  $R_2$  is sensed via two sensing resistors  $R_{s1,2}$  (=10 M $\Omega$ ), and then integrated on a capacitor  $C_{int}$  (=20 pF) built around the amplifier A<sub>DSL</sub>. The resulting voltage is fed back to the input of A<sub>1</sub> via a feedback resistor  $R_{fb}$  (=1.6 M $\Omega$ ) to close the feedback loop and regulate the output of A<sub>1</sub>. By applying feedback theory,  $f_{Par}$  caused by the D3SL can be calculated as

$$f_{\text{Par}} = \frac{1}{2\pi \times R_{\text{s}1,2} \times C_{\text{int}} \times \frac{R_{\text{fb}}}{R_1}}$$

(5)

in this design  $R_{s1,2} = 10 \text{ M}\Omega$ ,  $R_{fb} = 1.6 \text{ M}\Omega$ ,  $R_1 = 46 \text{ k}\Omega$ , and  $C_{int} = 20 \text{ pF}$ , which leads to a D3SL corner frequency  $f_{Par} = 15 \text{ Hz}$ .

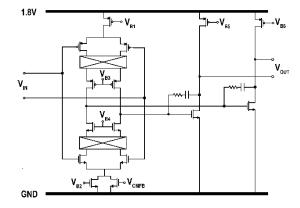

As shown in Fig. 6, to reduce the offset of  $A_1$  to less than 1  $\mu$ V, a two-stage amplifier A<sub>DSL</sub> with a high dc gain of 120 dB is employed. The first stage of A<sub>DSL</sub> is a current reuse telescopic stage designed to maximize noise efficiency, while the second stage is a conventional common source stage with a rail-to-rail output driver. To achieve a 60° phase margin, a Miller compensation capacitor with a nulling resistor is used. To mitigate the offset of ADSL, the first-stage PMOS and NMOS input pairs are chopped. Otherwise, the offset of  $A_{DSL}$  would appear at the output of  $A_1$  and then be amplified to the final output. The choppers modulate ADSL offset and the resulting ripple is then attenuated by the D3SL low-pass characteristic. Since  $R_{s1,2}$  are much larger than  $R_2$ , and  $R_{fb}$ is much larger than  $R_{coil}$ , the noise contribution of the D3SL is negligible. From simulations, it only increases the output integrated noise by 5%.

#### C. Temperature Compensation

As Hall-plate sensitivity is strongly temperature-dependent, a temperature compensation scheme is required. Otherwise, the Hall plates would exhibit a significant gain drift over

Fig. 6. Schematic of A<sub>DSL</sub>.

Fig. 7. Temperature compensation scheme.

temperature (>20% from -70 °C to 170 °C [23]). The sensitivity of the Hall path can be expressed as [see Fig. 7]

$$S_{\text{Hall-Path}} \propto I_{\text{Bias}} \times S_{\text{Hall}} \times \left(\frac{R_4}{2R_{\text{LPF}}}\right)$$

(6)

where  $I_{\text{Bias}}$  is the Hall-plate bias current and  $S_{\text{Hall}}$  is the current-related sensitivity of the Hall plate. It is worth noting that the gain of the CCAs (A<sub>3</sub> and A<sub>4</sub>) used in the Hall path is temperature-independent. This is because the gain is determined by the ratio of capacitors.

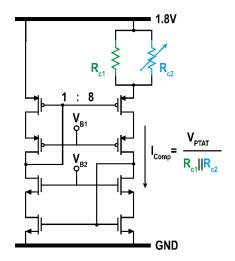

In [16] and [20], a PTAT bias current with a large positive  $TC_{PTAT}$  is employed to partially compensate for the large negative TC (about -0.4%/K) of Hall plates. As the Hall plates are realized in an n-well layer with a large positive TC ( $TC_{Nwell} = 0.37\%/K$ ), the supply voltage of the Hall plate has a very large TC of  $TC_{PTAT} + TC_{Nwell}$  (~0.77%/K). This limits the maximum bias current at room temperature for a given supply voltage.

In this work, to simultaneously compensate for the Hall-plates gain drift and increase the maximum bias current, two different types of resistors are used as  $R_4$  and  $R_{LPF}$  (Fig. 7).  $R_{LPF}$  and  $R_4$  are non-silicided n-poly (-0.15%/K) and non-silicided p-poly (-0.02%/K) resistors, respectively. Thus, the dc gain of the output stage has a positive TC of 0.13%/K.

The remaining Hall-plate sensitivity drift is compensated by using a tunable sub-PTAT bias current. As shown in Fig. 8, the sub-PTAT bias current is generated by forcing a PTAT voltage  $\Delta V_{GS}$  across two parallel resistors: a fixed non-silicided n-poly  $R_{C1}$  (5.7 k $\Omega$ ) and a tunable silicided n-poly  $R_{C2}$  (7.5–17.2 k $\Omega$ ).

Fig. 8. Tunable sub-PTAT bias generator.

This tunability provides  $\pm 9\%$  tuning range with a resolution of 0.3%.

As the coil path reads out the coil current and the coil is made of metal with a large TC of 0.34%/K, a temperature compensation scheme is required to minimize the gain drift over the temperature in the coil path. The coil-path output is proportional to the ratio of resistors

$$V \operatorname{out}_{\operatorname{Coil}} \propto \begin{cases} \frac{R_1}{R_{\operatorname{Coil}} \times R_2}, & f_X < f < f_{p1,z2} \\ \frac{R_3}{R_{\operatorname{coil}} \times R_2}, & f > f_{p1,z2}. \end{cases}$$

(7)

In [16] and [20], the TC of the coil resistance  $R_{\text{Coil}}$  is compensated by using silicided n-poly (TC = 0.29%/K) and non-silicided p-poly resistors (TC = -0.02%/K) as  $R_{1,3}$  and  $R_2$ , respectively. However, the residual TC causes a 2.7% gain drift over the temperature range. In this work, this residual TC is canceled by combining two types of resistors as  $R_2$ : 75% non-silicided p-poly (TC = -0.02%/K) and 25% n-poly (TC = -0.15%/K) resistors. This combination achieves the desired TC to cancel the residual TC.

#### **III. MEASUREMENT RESULTS**

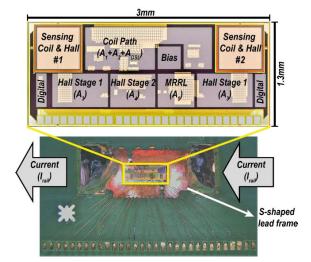

The integrated hybrid current sensor [see Fig. 9] was implemented in a standard 0.18-µm CMOS process and occupied 3.9 mm<sup>2</sup>. Similar to [16] and [20], it is mounted on a lowresistance (250  $\mu\Omega$ ) S-shaped current rail (Fig. 9, bottom). The current flows through the current rail, generating a perpendicular magnetic field over the rail slots. The resulting magnetic field is then sensed via two coils and Hall plates positioned above the slots. The S-shaped geometry provides differential sensing and higher sensitivity ( $\sim 2 \times$ ) compared to a straight current rail. A non-conductive glue is used to isolate the chip from the current rail. The die thickness is 200  $\mu$ m. This results in a current-to-magnetic coupling of about 283  $\mu$ T/A. The sensor draws about 7.1 mA from a 1.8-V supply at room temperature. About 60% of this current (4.4 mA) is used to bias the Hall plates. Each Hall plate consists of four Hall devices connected in parallel to reduce the initial offset. The current-related sensitivity of each Hall

Fig. 9. Sensor die on a copper lead-frame (bottom) Die micrograph (top).

Fig. 10. Sensitivity versus frequency.

device is 45 V/A  $\cdot$  T. Based on the geometry of the current rail, the coils consist of 43 minimum-width turns of top metal with an outer width of 500  $\mu$ m. The coil can be modeled as a series inductance (1043 nH) with a resistance (3.3 k $\Omega$ ), in parallel with a parasitic capacitor (3.95 pF). Simulations show that the coil current flowing into the virtual ground of A<sub>1</sub> has a differentiating characteristic up to ~100 MHz.

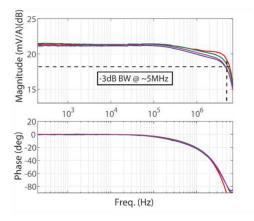

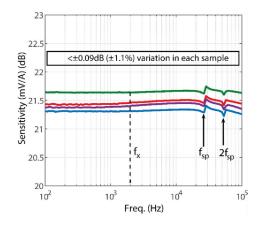

In this design, a spinning frequency  $(f_{sp})$  of 25 kHz is selected to achieve a good tradeoff between the offset and the filtered residual ripple. Fig. 10 shows the magnitude and phase of the sensor's overall frequency response with a 1-A input dc through the current rail. Four samples have been measured. To achieve a flat frequency response, the Hall-plates biasing current is trimmed via an 8-bit current DAC. The -3 dB BW of the sensor is approximately 5 MHz. At frequencies above 200 kHz, the gain decreases slightly due to eddy current induced in the current rail [24]. This was confirmed by FEM simulations in ANSYS. These show that eddy-current effects cause the flux through the coils to roll off at frequencies above 150 kHz, which agrees well with the measured data. Since each of the prototypes was assembled by hand, we attribute the observed spread in the roll-off to variations in the vertical distance between the coils and the lead-frame and in the alignment of the coil centers with the slits. The sensor's frequency response around  $f_X$  is shown in

Fig. 11. Zoomed in sensitivity versus frequency around  $f_X$ .

Fig. 12. Output spectrum w/ MRRL ON/OFF.

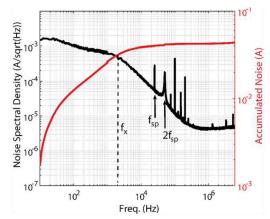

Fig. 13. Noise spectral density and accumulated noise referred to current rail.

Fig. 11. The parasitic pole caused by the D3SL causes less than 1% dip in the transfer function. The MRRL notches at  $f_{sp}$  and  $2f_{sp}$  limit the gain variation to around  $\pm 1.1\%$ .

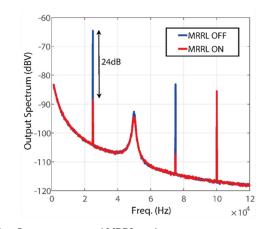

The output spectrum at zero input current is shown in Fig. 12. Enabling the MRRL reduces the spinning tones at  $f_{sp}$  and  $3f_{sp}$  by more than 24 dB. Measurements on five samples show that the achieved reduction spreads from 22 to 26 dB.

The noise spectral density and the accumulated noise are shown in Fig. 13. The noise spectral density has a 1st-order low-pass characteristic with a corner frequency of  $f_X$ (~2 kHz). At this frequency, the noise contribution of the coil path and the Hall path are equal. The integrated input-referred

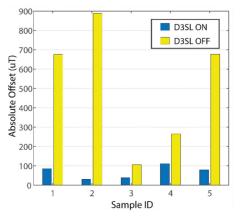

Fig. 14. Sensor absolute offset (Hall) referred to current rail w/ D3SL ON/OFF.

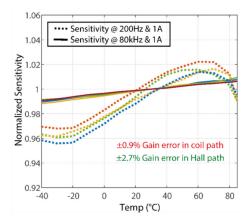

Fig. 15. Sensitivity versus temperature.

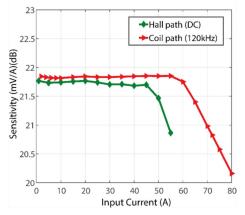

Fig. 16. Sensitivity versus input range for dc and extrapolated ac (rms) currents.

noise is 43 mA<sub>rms</sub> in a 5 MHz BW. The total input-referred ripple is 5 mA<sub>rms</sub>, which is more than  $8 \times$  smaller than the integrated noise. In addition, the residual ripple at  $f_{sp}$  only causes a 0.3 mA step in the accumulated noise plot, which proves that the MRRL suppression is sufficient.

To verify the effectiveness of the proposed D3SL, the sensor offset (Hall + coil) of five samples has been measured (Fig. 14). By enabling the D3SL, the offset is reduced from 600  $\mu$ T (1 $\sigma$ ) to 73  $\mu$ T (1 $\sigma$ ). Of this, about 60  $\mu$ T (1 $\sigma$ ) is due to the output-referred offset of A<sub>2</sub>, and could be reduced by e.g., trimming.

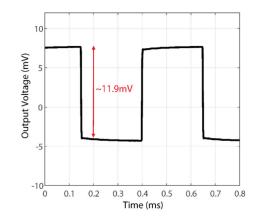

Fig. 17. Transient response for a 1 A<sub>p-p</sub> square wave @  $f_X = 2$  kHz (1024× averaging).

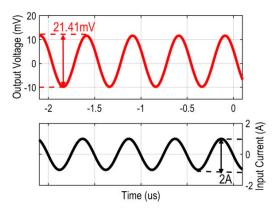

Fig. 18. Transient response for a  $2A_{p-p}$  sine wave @1 MHz (1024  $\!\times$  averaging).

The gain drift of the sensor is characterized in an oven from -40 °C to 85 °C. A 1-A input current is generated outside the oven and applied at 200 Hz and 80 kHz to measure the gain drift of the Hall and coil paths, respectively. The normalized sensitivities are shown in Fig. 15. After fixing the TC trim setting, four samples have been characterized. With a fixed TC trim setting, the coil path and Hall path gain drifts are below  $\pm 0.9\%$  and  $\pm 2.7\%$ , respectively.

To evaluate the linearity of the Hall path, a dc current is applied to the current rail. As shown in Fig. 16, the -1 dB compression point of the input current is 55 A, limited by the self-heating of the current rail. Due to the complexity of supplying large (tens of amps) current at high frequencies, the input range of the coil-path is determined by injecting a test current into the coil path (bypassing the coil sensors). This results in an equivalent input range of 72 A<sub>p</sub> (51 A<sub>rms</sub>). The sensor's response to a 1 A<sub>p-p</sub> square wave and a 2 A<sub>p-p</sub> sine wave are illustrated in Figs. 17 and 18, respectively. The slight lack of amplitude flatness in the square-wave response is due to the residual gain mismatch between the Hall and coil paths.

Table I summarizes the performance of the proposed hybrid sensor in comparison to other state-of-the-art magnetic current sensors. Compared to prior hybrid sensors, the resolution  $(1.5\times)$ , DR (+9.5 dB), and gain error  $(1.6\times)$  have significantly improved. Furthermore, it achieves the highest

| Source                    | This<br>work                                 | JSSC'23<br>[20] | JSSC'17<br>[17] | JSSC'19<br>[14] | JSSC'22<br>[5]       | APEC'19<br>[19] |

|---------------------------|----------------------------------------------|-----------------|-----------------|-----------------|----------------------|-----------------|

| Sensor Type               | Coil + Hall                                  | Coil + Hall     | Coil + Hall     | Hall            | IFG                  | Coil + Hall     |

| Technology (µm)           | 0.18                                         | 0.18            | 0.18            | 0.35            | 0.25                 | 0.18            |

| Supply (V)                | 1.8                                          | 1.8             | 5               | 3.3             | 1.8/5                | 1.8             |

| Area (mm <sup>2</sup> )   | 3.9                                          | 4.6             | 8.75            | N/A             | 4+3.6                | 2.74            |

| Resolution (mArms)        | 43                                           | 69              | 480             | 480             | 11°                  | 710             |

| Input Range (A)           | DC: ±55 <sup>a</sup><br>AC: ±51 <sup>a</sup> | $\pm 46^{a}$    | $\pm 18^{a}$    | ±300            | ±53°                 | ±60             |

| Dynamic Range (dB)        | 61.5                                         | 54              | 17              | 56              | 74                   | 39              |

| BW (MHz)                  | 5                                            | 5               | 3               | 1.7             | 0.125                | 15.3            |

| Power Consumption (mW)    | 12.8                                         | 14              | 38.5            | 13.2            | 100 <sup>d</sup> +13 | 63.5            |

| Gain Flatness             | ±1.1%                                        | ±1.5%           | <u>N/A</u>      | <u>N/A</u>      | <u>N/A</u>           | ±3.7%           |

| Residual Ripple @fsp (µT) | 1.5                                          | 6               | 8               | <u>N/A</u>      | <u>N/A</u>           | <u>N/A</u>      |

| Residual Offset (µT)      | 73                                           | 57              | 40              | 262             | <u>N/A</u>           | <u>N/A</u>      |

| FoM <sup>b</sup> [fW/Hz]  | 0.45                                         | 1.6             | 2281            | 5               | 8.5                  | 145             |

TABLE I PERFORMANCE SUMMARY AND COMPARISON

energy-efficiency FoM  $(3\times)$  among other magnetic current sensors.

#### **IV. CONCLUSION**

This article presents a hybrid magnetic current sensor consisting of coil sensors and Hall plates for high and low frequencies, respectively. A two-stage LPF reads out the coil current, while two CCAs are used to amplify the upmodulated Hall voltage. By optimizing the crossover frequency  $f_X$ (2 kHz) for noise, coil and Hall paths are combined. A D3SL reduces the coil-path offset from 600 to 73  $\mu$ T. The D3SL acts similar to a blocking capacitor between the coil-path stages in an area-efficient manner. With this approach, the D3SL causes a parasitic pole at 15 Hz which is more than  $100 \times$  smaller than  $f_X$  and so has a negligible effect ( $\pm 1\%$  dip) on the gain flatness. To achieve the same flatness and parasitic pole, a 100 nF blocking capacitor would have been required, occupying  $\sim 100 \times$  more chip area. The gain drift over the temperature in both paths is reduced by using different types of resistors. In addition, in the Hall path, a sub-PTAT bias generator is employed to cancel the residual TC of the Hall path. This results in a gain error of  $\pm 0.9\%$  and  $\pm 2.7\%$  (from -40 °C to 85 °C) in the coil and Hall paths, respectively. Overall, the presented sensor is the most energy-efficient magnetic sensor reported so far, achieving a FoM of 0.45 fW/Hz.

#### ACKNOWLEDGMENT

The authors would like to thank Zu-yao Chang and Lukasz Pakula for their help with sensor assembly and chip bonding.

#### References

[1] S. H. Shalmany, D. Draxelmayr, and K. A. A. Makinwa, "A ±36-a integrated current-sensing system with a 0.3% gain error and a 400- $\mu$ A offset from -55 °C to +85 °C," IEEE J. Solid-State Circuits, vol. 52, no. 4, pp. 1034-1043, Apr. 2017.

- [2] R. Zamparette and K. Makinwa, "A ±2A/15A current sensor with 1.4  $\mu$ A supply current and  $\pm 0.35\%/0.6\%$  gain error from -40 to  $85^{\circ}$ C using an analog temperature-compensation scheme," in Proc. Symp. VLSI Circuits, Jun. 2021, pp. 1-2.

- [3] Z. Tang, R. Zamparette, Y. Furuta, T. Nezuka, and K. A. A. Makinwa, "A versatile  $\pm 25$ -a shunt-based current sensor with  $\pm 0.25\%$  gain error from -40 °C to 85 °C," IEEE J. Solid-State Circuits, vol. 57, no. 12, pp. 3716-3725, Dec. 2022.

- [4] L. Xu, J. H. Huijsing, and K. A. A. Makinwa, "A ±4-a high-side current sensor with 0.9% gain error from -40 °C to 85 °C using an analog temperature compensation technique," IEEE J. Solid-State Circuits, vol. 53, no. 12, pp. 3368-3376, Dec. 2018.

- [5] P. Garcha et al., "A duty-cycled integrated-fluxgate magnetometer for current sensing," IEEE J. Solid-State Circuits, vol. 57, no. 9, pp. 2741-2751, Sep. 2022.

- [6] M. Kashmiri, W. Kindt, F. Witte, R. Kearey, and D. Carbonell, "27.9 A 200kS/s 13.5b integrated-fluxgate differential-magnetic-to-digital converter with an oversampling compensation loop for contactless current sensing," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2015, pp. 490-492.

- [7] M. F. Snoeij, V. Schaffer, S. Udayashankar, and M. V. Ivanov, "Integrated fluxgate magnetometer for use in isolated current sensing," IEEE J. Solid-State Circuits, vol. 51, no. 7, pp. 1684-1694, Jul. 2016.

- [8] I. Akita, T. Kawano, H. Aoyama, S. Tatematsu, and M. Hioki, "A 2.6 mW 10pTI / Hz 33 kHz magnetoimpedance-based magnetometer with automatic loop-gain and bandwidth enhancement," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2022, pp. 1–3.

- [9] H. Zhang, F. Li, H. Guo, Z. Yang, and N. Yu, "Current measurement with 3-D coreless TMR sensor array for inclined conductor," IEEE Sensors J., vol. 19, no. 16, pp. 6684-6690, Aug. 2019.

- [10] P. D. Dimitropoulos, P. M. Drljaca, and R. S. Popovic, "A 0.35µm-CMOS, wide-band, low-noise Hall magnetometer for current sensing applications," in Proc. IEEE Sensors, Oct. 2007, pp. 884-887.

- [11] T. Funk and B. Wicht, Integrated Wide-Bandwidth Current Sensing. New York, NY, USA: Springer, 2020.

- [12] J. C. Van Der Meer, F. R. Riedijk, E. Van Kampen, K. A. A. Makinwa, and J. H. Huijsing, "A fully integrated CMOS Hall sensor with a  $3.65\mu$ T 3σ offset for compass applications," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, vol. 1, Feb. 2005, pp. 246-247.

- [13] M. Crescentini et al., "The X-Hall sensor: Toward integrated broadband current sensing," IEEE Trans. Instrum. Meas., vol. 70, pp. 1-12, 2021.

- [14] Y. Li, M. Motz, and L. Raghavan, "A fast T&H overcurrent detector for a spinning Hall current sensor with ping-pong and chopping techniques," IEEE J. Solid-State Circuits, vol. 54, no. 7, pp. 1852-1861, Jul. 2019.

- [15] M. Crescentini, S. F. Syeda, and G. P. Gibiino, "Hall-effect current sensors: Principles of operation and implementation techniques," *IEEE Sensors J.*, vol. 22, no. 11, pp. 10137–10151, Jun. 2022.

- [16] A. Jouyaeian, Q. Fan, M. Motz, U. Ausserlechner, and K. A. A. Makinwa, "5.6 A 25A hybrid magnetic current sensor with 64 mA resolution, 1.8 MHz bandwidth, and a gain drift compensation scheme," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2021, pp. 82–84.

- [17] J. Jiang and K. A. A. Makinwa, "Multipath wide-bandwidth CMOS magnetic sensors," *IEEE J. Solid-State Circuits*, vol. 52, no. 1, pp. 198–209, Jan. 2017.

- [18] T. Funk and B. Wicht, "A fully integrated DC to 75 MHz current sensing circuit with on-chip Rogowski coil," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2018, pp. 1–4.

- [19] T. Funk, J. Groeger, and B. Wicht, "An integrated and galvanically isolated DC-to-15.3 MHz hybrid current sensor," in *Proc. IEEE Appl. Power Electron. Conf. Exposit. (APEC)*, Mar. 2019, pp. 1010–1013.

- [20] A. Jouyaeian, Q. Fan, R. Zamparette, U. Ausserlechner, M. Motz, and K. A. A. Makinwa, "A hybrid magnetic current sensor with a multiplexed ripple-reduction loop," *IEEE J. Solid-State Circuits*, early access, May 18, 2023, doi: 10.1109/JSSC.2023.3273389.

- [21] A. Jouyaeian, Q. Fan, M. Motz, U. Ausserlechner, and K. A. A. Makinwa, "23.3 A 51A hybrid magnetic current sensor with a dual differential DC servo loop and 43 mArms resolution in a 5 MHz bandwidth," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2023, pp. 22–24.

- [22] A. Udo, "Limits of offset cancellation by the principle of spinning current Hall probe," in *Proc. IEEE Sensors*, vol. 3, Aug. 2004, pp. 1117–1120.

- [23] S. Huber, W. Leten, M. Ackermann, C. Schott, and O. Paul, "A fully integrated analog compensation for the piezo-Hall effect in a CMOS single-chip Hall sensor microsystem," *IEEE Sensors J.*, vol. 15, no. 5, pp. 2924–2933, May 2015.

- [24] J. Jiang and K. A. A. Makinwa, "A multi-path CMOS Hall sensor with integrated ripple reduction loops," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Nov. 2015, pp. 1–4.

Amirhossein Jouyaeian (Member, IEEE) received the B.Sc. and M.Sc. degrees from the Sharif University of Technology, Tehran, Iran, in 2015 and 2017, respectively. He is currently pursuing the Ph.D. degree with the Delft University of Technology, Delft, The Netherlands.

He joined the Kavoshcom Research and Development Group in Tehran, in 2018, where he was involved in designing LiFi systems. His current research interests include magnetic current sensors and other precision analog and irrenits

mixed-signal integrated circuits.

**Qinwen Fan** (Senior Member, IEEE) received the B.Sc. degree in electronic science and technology from Nankai University, Tianjin, China, in 2006, and the M.Sc. degree (cum laude) in microelectronics and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2008 and 2013, respectively.

From October 2012 to May 2015, she worked at Maxim Integrated Products, Delft. From June 2015 to January 2017, she worked at Mellanox, Delft. Since 2017, she has been with the Delft

University of Technology, where she is currently an Assistant Professor at the ECTM. She has published more than 20 top scientific papers including International Solid-State Circuits Conference (ISSCC), Very Large Scale Integration (VLSI), Journal of Solid-State Circuits (JSSC), and APEC. She also holds multiple patents with industrial partners including ADI, ASML, and Infineon. Her current research interests include precision analog, high-performance class D audio amplifiers, smart power inverters in wide bandgap semiconductors, low-power dc-dc converters for energy harvesters, and low-power circuits for Internet of Things (IoT) nodes.

Dr. Fan serves as an Associate Editor for *Open Journal of the Solid-State Circuits Society* (OJ-SSCS), a TPC member of the International Solid-State Circuits Conference (ISSCC), VLSI Symposium on Technology and Circuits, and European Solid-State Circuits Conference (ESSCIRC). She is also a Distinguished Lecturer of the SSCS Society.

**Udo Ausserlechner** was born in Badgastein, Austria, in 1968. He received the M.Sc. degree in electrical engineering from the Faculty of Electrical Engineering, Technical University of Vienna, Vienna, Austria, in 1991, and the Ph.D. degree in physics from the Faculty of Natural Sciences, Technical University of Vienna, in 1996.

Since 1997, he has been a Microelectronic Circuit Design Engineer of integrated magnetic sensor ICs for automotive applications. He is currently with Infineon Technologies Austria AG, Villach, Austria.

He developed a theory of the signals induced in pick-up coils of vibrating sample magnetometers and constructed a cryogenic 15 Tesla magnetometer for studies in solid-state physics at the Technical University of Vienna. He has authored more than 150 granted patents in analog circuits and magnetic sensors. His main fields of work comprise integrated magnetic sensors (in particular Hall sensors), mechanical stress in plastic packages, equipment for testing magnetic sensors, and magnetic sensor arrangements for automotive applications.

**Mario Motz** (Member, IEEE) was born in Germany. He received the diploma degree in technical cybernetics from TH Magdeburg, Magdeburg, Germany, in 1983.

Until 1990, he worked as a Design Engineer for A/D- and D/A-converters in the semiconductor plant, Frankfurt/Oder, Germany. In 1990, he joined Gaertner Elektronik, and in 1991 ITT Intermetal, Freiburg, Germany (now Micronas AG), where he designed Hall sensor ICs in CMOS technology. Since 1999, he has been with Siemens AG, Villach, Austria (now

Infineon Technologies AG), where his current position is a Distinguished Engineer for analog/mixed-signal circuit design. His work is focused on precision sensor Ics, bandgaps and oscillators, ADCs, EMC-robust circuits and ultralow-power circuits, and compensation techniques for mechanical stress effects, offset, and sensitivity of sensors. He filed more than 150 patents and 12 IEEE publications as an author or coauthor in these areas.

Kofi A. A. Makinwa (Fellow, IEEE) received the B.Sc. and M.Sc. degrees from Obafemi Awolowo University, Ife, Nigeria, in 1985 and 1988, respectively, the M.E.E. degree from the Philips International Institute, Eindhoven, The Netherlands, in 1989, and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2004.

From 1989 to 1999, he was a Research Scientist with Philips Research Laboratories, Eindhoven. Since 1999, he has been at the Delft University of

Technology, where he is an Antoni van Leeuwenhoek Professor and the Head of the Microelectronics Department. His research interests include the design of mixed-signal circuits, sensor interfaces, and smart sensors. This has led to more than 20 books, more than 350 technical articles, and more than 30 patents.

Dr. Makinwa was a Distinguished Lecturer of the Solid-State Circuits Society and an Elected Member of its Adcom. He is a member of the Royal Netherlands Academy of Arts and Sciences. He is currently on the Executive Committee of the Very Large Scale Integration (VLSI) Symposium and a Co-Organizer of the Advances in Analog Circuit Design (AACD) workshop and the IEEE Sensor Interfaces Meeting (SIM). He was the co-recipient of 18 best paper awards, from the JSSC, ISSCC and VLSI symposium, among others. At the 70th anniversary of ISSCC, he was recognized as its top contributor. He was the Analog Subcom Chair of ISSCC and has served on the program committees of several other IEEE conferences.