# A Low-Jitter and Low-Spur Charge-Sampling PLL

Gong, Jiang; Charbon, Edoardo; Sebastiano, Fabio; Babaie, Masoud

וסמ

10.1109/JSSC.2021.3105335

Publication date

**Document Version**Final published version

Published in IEEE Journal of Solid-State Circuits

Citation (APA)

Gong, J., Charbon, E., Sebastiano, F., & Babaie, M. (2022). A Low-Jitter and Low-Spur Charge-Sampling PLL. *IEEE Journal of Solid-State Circuits*, *57*(2), 492-504. https://doi.org/10.1109/JSSC.2021.3105335

# Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# A Low-Jitter and Low-Spur Charge-Sampling PLL

Jiang Gong<sup>®</sup>, Student Member, IEEE, Edoardo Charbon<sup>®</sup>, Fellow, IEEE, Fabio Sebastiano<sup>®</sup>, Senior Member, IEEE, and Masoud Babaie<sup>®</sup>, Member, IEEE

Abstract—This article presents a low-jitter and low-spur charge-sampling phase-locked loop (CSPLL). A charge-domain sub-sampling phase detector is introduced to achieve a high phase-detection gain and to reduce the PLL in-band phase noise. Even without employing any power-hungry isolation buffers, the proposed phase detector dramatically suppresses the reference spurs by both minimizing the modulated capacitance seen by the voltage-controlled oscillator (VCO) tank and by reducing the duty cycle of the sampling clock. A 50- $\mu$ W RF-dividerless frequency-tracking loop is also introduced to lock the CSPLL robustly when the VCO faces a sudden frequency disturbance. Fabricated in a 40-nm CMOS process, the prototype CSPLL occupies a core area of 0.13 mm<sup>2</sup> and synthesizes 9.6-to-12-GHz tones using a 100-MHz reference. At 11.2 GHz, it achieves a reference spur of -77.3 dBc and an RMS jitter of 48.6 fs while consuming 5 mW.

Index Terms—Charge-sampling phase detector (CSPD), charge-sampling phase-locked loop (CSPLL), divider-less frequency-tracking loop (FTL), in-band phase noise (PN), low jitter, reference spur, sub-sampling.

# I. INTRODUCTION

**P**HASE-LOCKED loops (PLLs) with high spectral purity are in great demand for high-performance data converters, optical communication links, wireline, and wireless transceivers. For example, directly digitizing signals via an RF sampling analog-to-digital converter can significantly reduce the system's complexity, power consumption, and cost in macro-cellular base stations and satellite communication systems [1]. However, it imposes stringent requirements on the PLL's power consumption ( $P_{DC}$ ), phase noise (PN), RMS jitter, and reference spur ( $S_{REF}$ ). Consequently, significant effort has been made in the last decade to improve PLLs' spectral purity and power efficiency [2]–[31].

A divider-less sub-sampling PLL (SSPLL) based on voltage sampling can achieve low jitter while dissipating low power,

Manuscript received February 22, 2021; revised June 22, 2021; accepted August 4, 2021. Date of publication August 27, 2021; date of current version January 28, 2022. This article was approved by Associate Editor Jaeha Kim. This work was supported in part by Intel Corporation and in part by the Netherlands Organization for Scientific Research under Project 17303. (Corresponding author: Jiang Gong.)

Jiang Gong and Fabio Sebastiano are with the Department of Quantum and Computer Engineering, Delft University of Technology, 2628 CJ Delft, The Netherlands, and also with Qutech, 2628 CJ Delft, The Netherlands (e-mail: gongjiangjlu@gmail.com).

Edoardo Charbon is with the Kavli Institute of Nanoscience, 2628 CJ Delft, The Netherlands, and also with École polytechnique fédérale de Lausanne (EPFL), 1015 Lausanne, Switzerland.

Masoud Babaie is with the Department of Microelectronics, Delft University of Technology, 2628 CJ Delft, The Netherlands, and also with Qutech, 2628 CJ Delft, The Netherlands.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2021.3105335.

Digital Object Identifier 10.1109/JSSC.2021.3105335

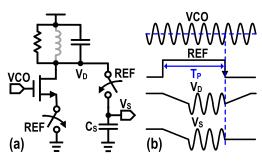

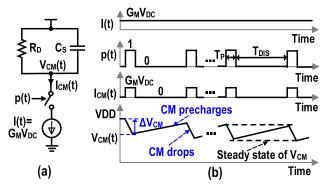

Fig. 1. (a) Schematic and (b) conceptual waveforms of a voltage-sampling PD using a power-gated isolation buffer.

as it eliminates the noise of the feedback divider and suppresses the noise of the charge pump and phase detector (PD) due to its high phase-detection gain ( $K_{PD}$ ) [9]–[18]. Unfortunately, the direct sampling of the voltage-controlled oscillator (VCO) voltage by a low-frequency reference clock (REF) can introduce a high  $S_{REF}$  due to the periodic tank-capacitance perturbation, reference clock feedthrough, and charge injection from the sampling switch to the VCO. The periodic switching of the sampling capacitor modulates the VCO's frequency,  $F_{VCO}$ , in a similar fashion to the case of binary frequency-shift keying (BFSK), which creates a spur at the reference frequency ( $F_{REF}$ ) given by

$$S_{\text{REF-BFSK}} = 20 \cdot \log_{10} \left[ \sin(\pi \cdot D_{\text{REF}}) \cdot \frac{N}{2\pi} \cdot \frac{C_{\text{MOD}}}{C_{\text{TANK}}} \right]$$

(1)

where  $D_{\rm REF}$  is the reference clock duty cycle,  $C_{\rm MOD}$  is the modulated capacitance seen by the VCO tank, and  $C_{\rm TANK}$  is the total tank capacitance [10].  $S_{\rm REF}$  can be improved by directly decreasing the sampling capacitor ( $C_S$ ) [10] to reduce  $C_{\rm MOD}$ . However, a small  $C_S$  degrades the in-band PN due to the sampling noise, diminishing the benefit of a sub-sampling PD. Hence, a dummy sampler was added in [14] such that the VCO could see a small  $C_{\rm MOD}$ . Yet, this approach suffers from the mismatch between these two sampling capacitors, thus limiting  $S_{\rm REF}$  to -56 dBc for a 2.2-GHz carrier

Consequently, to target a low  $S_{\rm REF}$  (e.g., <-70 dBc) through lowering  $C_{\rm MOD}$ , an isolation buffer with either inductive or resistive load is typically employed between VCO and sampler [10], [20]. However, the buffer operates at  $F_{\rm VCO}$ , resulting in a substantial penalty in the PLL's area,  $P_{\rm DC}$ , and jitter. Moreover, the rise and fall times of the signal at the sampler input may be reduced, shrinking the linear phase-detection range of the PD. Hence, a power-hungry slope generator is added in [10] and [20] to realize a triangular-like waveform for the sampler.

0018-9200 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

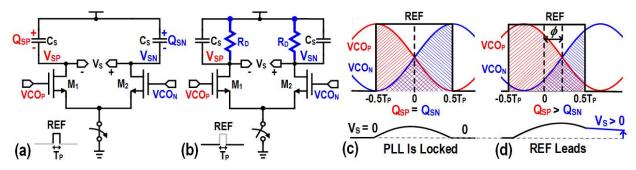

Fig. 2. Simplified schematic of the proposed CSPD when REF is (a) high and (b) low; its conceptual waveforms (c) without and (d) with a phase error.

Power-gated operation of the isolation buffer, as shown in Fig. 1(a), reduces  $D_{REF}$ , thus alleviating  $S_{REF}$  and  $P_{DC}$ overhead [12], [13]. However, the REF pulsewidth  $(T_P)$  cannot be shorter than a few cycles (e.g., 5-10) of the VCO period  $(T_{\rm VCO})$  to ensure that the resonant buffer reaches its steadystate amplitude before the sampling instants. In the case of the resistive buffer, the common-mode (CM) settling time sets the shortest possible  $T_P$ , thus limiting  $S_{REF}$  and  $P_{DC}$  improvement. Moreover, to provide a low-noise signal amplification at  $F_{VCO}$ , the buffer's transistors must be wide enough to draw a relatively large current during the ON-state. Due to the use of wide transistors, the buffer's input capacitance significantly changes when the devices enter saturation from the cutoff region and vice versa. Therefore, the VCO experiences a large  $C_{\text{MOD}}$ , thus limiting the PLL spur performance. Besides, the clock feedthrough and charge injection issues still exist through the large gate parasitic capacitance of the isolation buffer. Consequently, due to the constraints on the minimum achievable  $C_{\text{MOD}}$  and  $D_{\text{REF}}$ , even by using a gated isolation buffer in [13],  $S_{REF}$  and figure of merit (FOM) are still limited to -67 dBc and -256 dB at 2.4-GHz carrier frequency, respectively.

To improve on those limitations, we propose a charge-sampling PLL (CSPLL), first introduced in [19], whose phase-detection mechanism is based on a windowed current integration. Without exploiting any isolation buffers, the proposed CSPLL achieves -77-dBc  $S_{\rm REF}$  by simultaneously minimizing  $C_{\rm MOD}$  and  $D_{\rm REF}$ . It also offers a high  $K_{\rm PD}$  even without requiring an RF bandwidth (BW) at the sampler output, resulting in -259-dB jitter-power FOM. Furthermore, a highly digital frequency-tracking loop (FTL) without the use of any RF dividers is proposed to guarantee the PLL's robust operation.

This article is organized as follows. Section II focuses on the detailed theoretical analysis and design considerations of the charge-sampling PD (CSPD). Section III describes the complete CSPLL architecture and FTL operation. The circuit implementation of critical building blocks of the CSPLL is shown in Section IV. Section V presents the measurement results, while Section VI wraps up this article with conclusions.

### II. CHARGE-SAMPLING PD

# A. Voltage Sampling Versus Charge Sampling

Voltage-sampling phase detectors (VSPDs) capture the instantaneous input voltage when the sampling switch is turned off [see Fig. 1(b)]. Their ideal locking point is when

the VCO zero crossings occur at the REF falling edge [9]. The VSPD phase-detection gain is directly proportional to the voltage swing at the sampler's output, thus demanding a high power consumption for both the isolation buffer and the sampling circuit for realizing an RF BW close to  $F_{VCO}$ . On the other hand, charge sampling is based on integrating an input current on a capacitor over a fixed time window and taking the resulting voltage as the sampler output. It is a well-known technique to reduce the sampling error caused by the clock jitter in high-speed sample-and-hold amplifiers [32], [33]. It is also widely used in software-defined radio receivers due to its built-in anti-aliasing and reconfigurability [34]–[37]. However, the interesting properties of the chargesampling concept have not yet been exploited in the PLL design. This article shows that the fundamental differences in the voltage sampling and charge-sampling operation profoundly impact the PLL performance in terms of locking point,  $K_{\rm PD}$ ,  $S_{\rm REF}$ , PN, and  $P_{\rm DC}$ .

#### B. Locking Point

Fig. 2 shows the schematic and conceptual waveforms of a CSPD. The transconductors  $(M_{1,2})$  convert the VCO's output voltage  $VCO_P - VCO_N = 2A_{VCO} \cdot \sin(\omega_{VCO}t + \phi)$ into a differential RF current, realizing a charge difference on  $C_S$  when REF is high. If the VCO zero crossings occur at the center of the REF pulse,  $M_{1,2}$  charge  $C_S$  during the first half of the REF pulse (i.e., from  $-0.5 T_P$  to 0) and discharge  $C_S$  during the second half of the REF pulse (i.e., from 0 to 0.5  $T_P$ ). Consequently, the sampled net charge difference  $Q_S = (Q_{SP} - Q_{SN})$  is zero, which is represented by the equaled shaded blue and red areas in Fig. 2(c). Hence, the sampled differential voltage  $V_S$  (= $V_{SN} - V_{SP}$ ) remains zero after the phase comparison, corresponding to the ideal locking condition of the PLL. If there is any phase error  $(\phi)$ , the CSPD converts it into a non-zero  $Q_S$  and  $V_S$ , as shown in Fig. 2(d), thus indicating that the PLL is not locked. Consequently, similarly as in sub-sampling PDs, the CSPD works without using RF dividers if  $N = F_{VCO}/F_{REF}$  is an integer number.

When REF is low,  $V_S$  is partially discharged via load resistors  $(R_D)$  and  $C_S$  since  $M_{1,2}$  are turned off. This peculiar discharging process is crucial for the CSPD's operation, which will be discussed in Section II-C.

#### C. Phase-Detection Gain

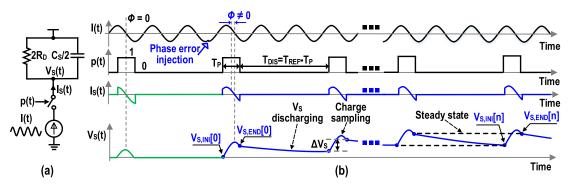

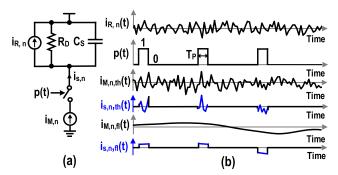

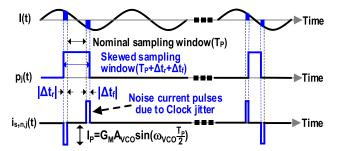

Fig. 3 shows the time-domain differential-mode model of the CSPD, where a periodic sampling function [p(t)] samples

Fig. 3. (a) Time-domain differential-mode model of the CSPD. (b) Waveforms of the CSPD before and after applying a phase error to the VCO.

a continuous-time RF current  $I(t) = G_M A_{VCO} \sin(\omega_{VCO} t + \phi)$ . This results in a train of discrete-time narrow current pulses

$$I_S(t) = G_M A_{VCO} \sin(\omega_{VCO} t + \phi) \cdot p(t)$$

(2)

where  $G_M$  is the large-signal transconductance of  $M_{1,2}$  and

$$p(t) = \begin{cases} 1, & \frac{-T_P}{2} + n \cdot T_{\text{REF}} \le t \le \frac{T_P}{2} + n \cdot T_{\text{REF}} \\ 0, & \text{otherwise.} \end{cases}$$

(3)

Due to the phase error ( $\phi$ ) between the VCO zero crossings and middle of the REF pulse [see Fig. 3(b)],  $V_S$  increases by

$$\Delta V_S = V_{S,\text{END}}[n] - V_{S,\text{INI}}[n] = \frac{2}{C_S} \int_{-0.5T_P}^{0.5T_P} I_S(t) dt$$

$$= \frac{4G_M A_{\text{VCO}}}{\omega_{\text{VCO}} C_S} \cdot \sin(0.5\omega_{\text{VCO}} T_P) \cdot \sin(\phi) \tag{4}$$

during each phase comparison, where  $V_{S,\mathrm{INI}}[n]$  and  $V_{S,\mathrm{END}}[n]$  represent the voltages of  $V_S$  at the beginning and end of the charge sampling, respectively, at the nth reference clock cycle. Following the phase comparison, p(t) becomes 0 for a duration of  $T_{\mathrm{DIS}} = T_{\mathrm{REF}} - T_P$ .  $V_{S,\mathrm{END}}[n]$  is exponentially discharged through  $R_D$  and  $C_S$  and brings  $V_{S,\mathrm{INI}}$  to

$$V_{S,\text{INI}}[n+1] = V_{S,\text{END}}[n] \cdot \exp^{-k}$$

(5)

at the next cycle, where k is defined as  $T_{\rm DIS}/(R_DC_S)$ . By combining (4) and (5),  $V_{S,\rm END}[n]$  can be calculated as

$$V_{S,\text{END}}[n] = \Delta V_S \sum_{k=0}^{n-1} \exp^{-n \cdot k}$$

(6)

and it reaches a steady-state value given by  $V_{S,END}[n]|_{st} = \Delta V_S/(1 - \exp^{-k})$ .

The unique discharging process of  $V_S$  is critical for the proper operation of a CSPD. Let us consider two extreme cases here. In the first one, k approaches 0 by removing  $R_D$ . Therefore, the sampled charge is accumulated, and CSPD resembles an ideal integrator, exhibiting a pole at dc and causing instability issues in the PLL. In the second case, if k is chosen to be  $\sim N$  by picking a small  $R_D$  and  $C_S$ , which is a typical case in a VSPD using a power-gated isolation buffer [12], [13], the detected  $V_S$  will rapidly return to zero, thus destroying the PD's memory and requiring a hold switch at the sampler output. In this design, k is designed to be

$\sim$ 0.4, so as to satisfy the PLL's required phase margin and simultaneously guarantee the PD's charge-sampling operation. As a result, CSPD resembles a leaky phase integrator with a pole location determined by k. We will discuss this further in Section III.

In the steady state,  $V_S$  becomes a periodic function of  $T_{REF}$ , and its average value can be estimated by<sup>2</sup>

$$\overline{V_S} \approx \frac{1}{T_{\text{REF}}} \int_{0.5T_P}^{T_{\text{REF}} - 0.5T_P} V_{S, \text{END}}[n]|_{\text{st}} \cdot \exp^{\frac{-t}{R_D C_S}} dt$$

$$\approx \frac{2G_M A_{\text{VCO}} R_D}{N\pi} \cdot \sin(0.5\omega_{\text{VCO}} T_P) \cdot \sin(\phi). \tag{7}$$

$K_{\rm PD}$  is then defined as  $\overline{V_S}/\phi$  and can be calculated by

$$K_{\rm PD} = \frac{2G_M A_{\rm VCO} R_D}{N\pi} \cdot \sin(0.5\omega_{\rm VCO} T_P) \cdot \frac{\sin(\phi)}{\phi}.$$

(8)

We can inspect the validity of the above equation by using an alternative method. The phase error modifies the shape of the sampled current pulses [see Fig. 3(b)] and creates a non-zero dc current ( $\overline{I_S}$ ). Notice that  $\overline{I_S}$  must flow into the resistive load  $R_D$ , thus creating a dc voltage given by

$$\overline{V_S} = \frac{2R_D}{T_{\text{REF}}} \cdot \int_{-0.5T_P}^{T_{\text{REF}} - 0.5T_P} G_M A_{\text{VCO}} \sin(\omega t + \phi) dt$$

$$= \frac{2G_M A_{\text{VCO}} R_D}{N\pi} \cdot \sin(0.5\omega_{\text{VCO}} T_P) \cdot \sin(\phi). \tag{9}$$

Interestingly,  $K_{PD}$  is not a function of  $C_S$ . This indicates that an arbitrarily large  $C_S$  can be used without sacrificing  $K_{PD}$ . The complete phase-detection gain by considering the PD delay can be estimated by  $K_{PD}(s) \approx K_{PD}/(1 + s \cdot R_D C_S)$ .

Notice that, unlike a VSPD,  $K_{PD}$  of a CSPD is a function of both  $T_P$  and N. At first glance, it seems that  $K_{PD}$  of a CSPD with  $N\pi$  factor in the denominator is much smaller than that of a VSPD (i.e.,  $K_{PDVS} \approx 2G_M A_{VCO} R_D$ ). However, the reduction of  $K_{PD}$  by  $N\pi$  can be easily compensated by choosing a large  $R_D$ . Note that the finite output impedance of  $M_{1,2}$  ( $r_{ds}$ ) has a marginal impact on  $K_{PD}$ , as long as  $1/(\omega_{VCO} C_S) \ll r_{ds}$ . This condition can be easily satisfied in a CSPD by choosing a large  $C_S$ . Hence, without compromising  $K_{PD}$ , a minimum channel length device can be used for  $M_{1,2}$  to minimize  $C_{MOD}$  and to improve  $S_{REF}$ . In contrast to the CSPD,  $r_{ds}$  significantly reduces  $K_{PDVS}$  in deep-submicrometer technologies due to short-channel effects, enforcing the use of long channel length devices and thus degrading  $S_{REF}$ .

<sup>&</sup>lt;sup>1</sup>Here, we assume that  $1/(C_S \omega_{VCO}) \ll R_D$ . Also, it will be shown later that this assumption is valid for a CSPD.

<sup>&</sup>lt;sup>2</sup>This approximation is valid since  $T_P \ll T_{\rm DIS}$  in a CSPD.

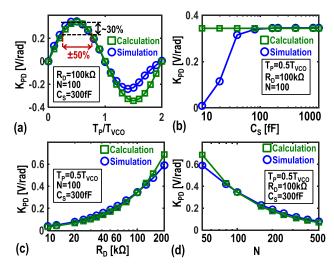

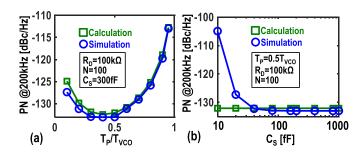

Fig. 4. Simulated and calculated  $K_{\rm PD}$  as a function of (a)  $T_p$ , (b)  $C_S$ , (c)  $R_D$ , and (d) N.

Due to the integration operation,  $K_{PD}$  is a periodic function of  $T_P$  and reaches its maximum at  $T_P = 0.5 T_{VCO}$ . Using  $T_P$  $\gg 0.5 T_{\rm VCO}$  does not improve  $K_{\rm PD}$  but degrades the reference spur. Notice that, due to the sinusoidal dependence of  $K_{PD}$ to  $T_P$ , a  $\pm 50\%$  variation of  $T_P$  around its optimum point only reduces  $K_{\rm PD}$  by 30%, suggesting that CSPD is robust against process, voltage, and temperature (PVT) variations. In this design,  $K_{PD}$  of  $\sim 0.35$  V/rad is achieved by choosing  $R_D = 100 \text{ k}\Omega, (W/L)_{1,2} = 2 \mu\text{m}/40 \text{ nm}, G_M = 1.2 \text{ mS},$ and N = 100. Note that the achieved gain is sufficiently high to suppress the noise of PLL loop components. Further increasing  $K_{PD}$  would require a pulser circuit to reduce the loop gain (LG) [9], complicating the design. Fig. 4 shows the simulated and calculated  $K_{PD}$  versus various parameters of the CSPD. Although there are some deviations especially if a large  $T_P$  and a small  $C_S$  are used, simulations match the presented theory very well. The discrepancies will be justified in Section II-D by investigating the CM behavior of the CSPD.

#### D. CM Settling

Fig. 5 shows the time-domain CM model and waveforms of the CSPD, where the sampling function p(t) is used to sample a constant current. Consequently, a train of current pulses with a fixed amplitude of  $G_M V_{DC}$  and a duration of  $T_P$  is pumped into  $R_D$  and  $C_S$  irrespective of the phase error, where  $V_{DC}$  is  $M_{1,2}$  gate-source bias voltage. This results in a CM voltage drop of  $\Delta V_{CM} = G_M V_{DC} T_P / C_S$  when p(t) is 1 (i.e., during the phase comparison). When p(t) is 0, the output CM voltage  $(V_{CM})$  is exponentially precharged to a high level such that  $M_{1,2}$  can be turned on very fast (i.e., <15 ps), only limited by the ON-resistance and parasitic capacitance of the tail switch. Note that CSPD CM settles to its steady-state right after the power-up and follows the same pattern regardless of the phase error variations.

$K_{\rm PD}$  could be potentially compromised if  $M_{1,2}$  enter the triode region, as shown in Fig. 4(a) and (b), where the simulated  $K_{\rm PD}$  deviates from its theoretical value if a larger  $T_P$  or a smaller  $C_S$  is used. Therefore, a large  $C_S$  and very

Fig. 5. (a) Time-domain CM model of the CSPD. (b) CM waveforms of the CSPD.

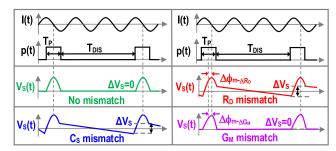

Fig. 6. Conceptual waveforms of the CSPD due to  $C_S$ ,  $R_D$ , and transistor mismatch.

narrow pulsewidth for the REF must be utilized to maintain a high output CM voltage and keep  $M_{1,2}$  in saturation during each phase comparison.<sup>3</sup>

The current consumption of the CSPD is obtained by averaging the CM current over one reference period

$$\overline{I_{\text{CM}}} = \frac{2}{T_{\text{REF}}} \int_{-\frac{T_P}{2}}^{T_{\text{REF}} - \frac{T_P}{2}} G_M V_{\text{DC}} dt = \frac{2G_M V_{\text{DC}} T_P}{T_{\text{REF}}}.$$

(10)

By considering  $V_{DC}=0.6$  V,  $(W/L)_{1,2}=2$   $\mu$ m/40 nm, and  $T_P=0.3T_{VCO}$ , the CSPD consumes less than 5  $\mu$ A. Consequently, a low power consumption and a high  $K_{PD}$  can be simultaneously achieved by having a small  $T_P$  (e.g., 0.3  $T_{VCO}$ ) in the proposed CSPD. On the contrary, to deliver a maximum voltage gain, a VSPD needs a large  $T_P$  for proper CM settling of its gated isolation buffer, thus degrading both power consumption and  $S_{REF}$ .

# E. Mismatch Analysis

1)  $C_S$  Mismatch: As discussed earlier, since the averaged differential output of CSPD  $(\overline{V_S})$  is not a function of  $C_S$ , the locking point and  $K_{PD}$  are also not sensitive to the mismatch between the sampling capacitors  $(\Delta C_S)$ . However, due to  $\Delta C_S$ , even when the phase error is zero, the CSPD's differential output in steady state experiences a voltage jump  $(\Delta V_S)$  during each phase comparison followed by an exponential voltage change over the discharging phase [see the blue curve in Fig. 6]. This results in a sawtooth ripple in  $V_S$ , whose fundamental amplitude is given by

$$A_{\text{rip}-\Delta C_S} \approx \frac{\Delta C_S}{C_S} \cdot \frac{\Delta V_{\text{CM}}}{\pi}.$$

(11)

<sup>3</sup>Interestingly, in contrast to a VSPD, a proper CSPD design always favors a small  $T_P$  and a large  $C_S$ .

Fig. 7. (a) Half-circuit noise model and (b) time-domain noise waveforms of the CSPD.

The effect of this sawtooth-like ripple on the reference spur will be discussed further in Section III.

2)  $R_D$  Mismatch: If the VCO zero crossings occur at the center of the REF pulse, then a non-zero  $\overline{V_S}$  (= $G_M V_{DC} \Delta R_D T_P / T_{REF}$ ) will be created due to the mismatch between the CSPD load resistors ( $\Delta R_D$ ), indicating that the PLL is not locked. The loop must therefore develop a phase offset of

$$\Delta \phi_{m-\Delta R_D} \approx \frac{\Delta R_D}{R_D} \cdot \frac{N\pi T_P}{2\sin(0.5\omega_{\text{VCO}}T_P)T_{\text{RFF}}}$$

(12)

to compensate for  $\Delta R_D$  and realize  $\overline{V_S}=0$  in the locked state. Even considering a pessimistic  $\Delta R_D/R_D=10\%$ ,  $\Delta \phi_{m-\Delta R_D}$  would be <4° with almost no penalty on  $K_{PD}$ . Nevertheless, due to this offset, a sawtooth ripple will show up in  $V_S$  again [see the red curve in Fig. 6], whose fundamental amplitude can be found by

$$A_{\text{rip}-\Delta R_D} \approx 4G_M A_{\text{VCO}} \cdot \sin(\Delta \phi_{m-\Delta R_D}) \cdot \frac{\sin(0.5\omega_{\text{VCO}} T_P)}{\pi \omega_{\text{VCO}} C_S}.$$

(13)

The impact of this ripple on  $S_{REF}$  will be quantified in Section III.

3)  $M_{1,2}$  Mismatch: Similar to the  $R_D$  mismatch, the loop must create a phase offset to compensate for the mismatch between the transconductance of the transistors  $(\Delta G_M)$ , as shown in Fig. 6. The phase offset can be estimated by

$$\Delta \phi_{m-\Delta G_M} \approx \frac{\Delta G_M}{G_M} \cdot \frac{N\pi T_P}{2\sin(0.5\omega_{\text{VCO}}T_P)T_{\text{REF}}}.$$

(14)

By considering  $\Delta G_M/G_M = 50\%$ ,  $\Delta \phi_{m-\Delta G_M}$  is  $\sim 16.9^\circ$ , degrading  $K_{PD}$  by only  $\sim 0.4$  dB. Fortunately, since  $C_S$  and  $R_D$  are matched, there is no sawtooth ripple in  $V_S$  at the steady state [see the pink curve in Fig. 6]; hence,  $S_{REF}$  is not affected by  $\Delta G_M$ .

#### F. Phase-Noise Analysis

1) Noise of  $R_D$ : Since  $R_D$  is always connected to the CSPD output, the effective power spectral density (PSD) of its noise current can be simply expressed as  $i_{s,R,n}^2/\Delta f = 4KT/R_D$ . Note that this expression slightly overestimates  $R_D$  noise when transferred to the CSPD output, as its noise current partially flows to the ground due to the finite  $r_{ds}$  of  $M_{1,2}$ .

2) Thermal Noise of  $M_{1,2}$ : As shown in Fig. 7,  $M_{1,2}$  contribute noise only when the REF is high by injecting a train of narrow noise current pulses  $[i_{s,n}(t) = i_{M,n}(t) \cdot p(t)]$  into  $R_D$  and  $C_S$ . Suppose that  $i_{M,n}(t)$  contains only thermal noise  $[i_{M,n,\text{th}}(t)]$  with a variance of  $i_{M,n,\text{th}}^2$ . The resulting  $i_{s,n}(t)$  is a white and cyclostationary process, and its auto-correlation function can be expressed as

$$R_{i_{s,n}}(t,t+\tau) = i_{M,n,\text{th}}^2 \cdot \delta(\tau) \cdot p(t+\tau) \cdot p(t)$$

(15)

which is a function of both t and the lag  $\tau$ . The  $i_{s,n}(t)$  PSD is obtained by averaging  $R_{i_{s,n}}(t, t+\tau)$  over one reference period and taking the Fourier transformation, and it is given by

$$\frac{\overline{i_{s,n,\text{th}}^2}}{\Delta f} = \int_{-\infty}^{+\infty} \exp^{-j2\pi f \tau} \int_{-\frac{T_P}{2}}^{T_{\text{REF}} - \frac{T_P}{2}} \frac{R_{i_{s,n}}(t, t+\tau)}{T_{\text{REF}}} dt d\tau$$

$$= i_{M,n,\text{th}}^2 \cdot \frac{T_P}{T_{\text{REF}}}.$$

(16)

As expected, a smaller  $T_P$  also reduces the  $M_{1,2}$  contribution to the PLL total PN.

3) Flicker Noise of  $M_{1,2}$ : Since the flicker noise of  $M_{1,2}$ :  $[i_{M,n,fl}(t)]$  is a slow process and varies little during the charge-sampling window, it can be assumed that its time average determines the root mean square of the flicker fluctuations [38]. Consequently, the output flicker noise current can be modeled as an impulse train with a height of  $T_P/T_{REF}$  ·  $i_{M,n,fl}(t)$  sampled at the reference frequency

$$i_{s,n,\text{fl}}(t) = \frac{T_P}{T_{\text{REF}}} \cdot \sum_{k=0}^{n} \left( i_{M,n,\text{fl}}(t) \cdot \delta(t - k \cdot T_{\text{REF}}) \right). \tag{17}$$

Its PSD at low frequencies can be estimated by

$$\frac{\overline{i_{s,n,\text{fl}}^2}}{\Delta f} = \frac{T_P^2}{T_{\text{REF}}^2} \cdot \frac{\overline{i_{M,n,\text{fl}}^2}}{\Delta f}$$

(18)

where  $\overline{i_{M,n,\mathrm{fl}}^2}/\Delta f$  is the PSD of  $M_{1,2}$  flicker noise. Note that the spectrum of the flicker noise current at the CSPD output consists of sampled replicas appearing at integer multiples of  $F_{\mathrm{REF}}$ , which are sufficiently suppressed by the large time constant of  $R_D C_S$ .

4) In-Band PN Due to CSPD: The in-band PN is obtained by considering the noise contributions of  $R_D$  and  $M_{1,2}$  at the CSPD output and referring the resulting voltage noise to the input of CSPD

$$\mathcal{L}_{\text{CSPD}} = 2 \cdot \left( \frac{\overline{i_{s,R,n}^2}}{\Delta f} + \frac{\overline{i_{s,n,\text{th}}^2}}{\Delta f} + \frac{\overline{i_{s,n,\text{fl}}^2}}{\Delta f} \right) \cdot \frac{R_D^2}{K_{\text{PD}}^2}.$$

(19)

Notice that, in contrast to a VSPD, the theoretical PN of a CSPD is not a function of  $C_S$ . Fig. 8 shows the simulated and calculated in-band PN at 200-kHz offset from a 10-GHz carrier due to both the flicker and thermal noise of CSPD (but excluding any other noise sources) when  $R_D=100~\mathrm{k}\Omega$  and  $(W/L)_{1,2}=2~\mu\mathrm{m}/40~\mathrm{nm}$ . The simulation results are in good agreement with the presented calculations if  $C_S$  is not chosen too small, which is anyway outside the optimum range. If a very small  $C_S$  is used, the simulated PN is much higher than the theoretical value due to the reduced  $K_{\mathrm{PD}}$  caused by  $V_{\mathrm{CM}}$  drop. However, if a larger  $C_S$  is used, the simulated in-band PN is very weakly related to  $C_S$ , as expected. This is very

Fig. 8. Simulated and calculated PN at 200-kHz offset from a 10-GHz carrier as a function of (a)  $T_p$  and (b)  $C_S$  due to CSPD only.

different from a VSPD, where a large  $C_S$  is essential to reduce the KT/C noise.

As shown in Fig. 8(a), the CSPD displays a minimum inband PN (<-133 dBc/Hz) when  $T_P$  reaches  $\sim$ 0.5  $T_{\rm VCO}$ . While  $M_{1,2}$  flicker noise corner is very high (i.e.,  $\sim$ 60 MHz) due to their small dimensions, the charge sampling suppresses the flicker noise much more than the thermal counterpart [compare (16) with (18)]. As a result, the  $R_D$  thermal noise, the  $M_{1,2}$  thermal noise, and the  $M_{1,2}$  flicker noise contribute almost equally to the total PN at 200-kHz offset. A larger  $T_P$  degrades both  $K_{\rm PD}$  and voltage noise contributed by  $M_{1,2}$ , worsening the in-band PN. Although a smaller  $T_P$  reduces the PN originated from the flicker noise of  $M_{1,2}$ , it degrades in-band PN due to the reduced  $K_{\rm PD}$ . Nevertheless, choosing  $T_P$  between 0.2  $T_{\rm VCO}$  and 0.6  $T_{\rm VCO}$  maintains the PN within 3 dB of the optimum performance.

5) PN Due to Clock Jitter: The jitter of the reference clock alters the moment when  $M_{1,2}$  are both turned on and off, thus randomly changing the sampling function  $[p_j(t)]$ , as shown in Fig. 9. The resultant sampling error  $[i_{s,n,j}(t)]$  contains two noise current pulses with a fixed amplitude of  $I_P = G_M A_{\text{VCO}} \sin(\omega_{\text{VCO}}(T_P/2))$  and variable widths of  $|\Delta t_r|$  and  $|\Delta t_f|$  over one reference period, where  $\Delta t_r$  and  $\Delta t_f$  are the clock jitter of the REF rising edge and falling edge, respectively. Since  $\Delta t_r$  and  $\Delta t_f$  are very small,  $i_{s,n,j}(t)$  can be represented as the sum of two impulse trains sampling at the reference frequency

$$i_{s,n,j}(t) = \sum_{k=0}^{n} \frac{I_P \cdot \Delta t_r[k]}{T_{\text{REF}}} \cdot \delta \left( t - \left( \frac{-T_P}{2} + k \cdot T_{\text{REF}} \right) \right) + \sum_{k=0}^{n} \frac{I_P \cdot \Delta t_f[k]}{T_{\text{REF}}} \cdot \delta \left( t - \left( \frac{T_P}{2} + k \cdot T_{\text{REF}} \right) \right).$$

(20)

If  $\Delta t_r$  and  $\Delta t_f$  are uncorrelated but with the same variance,  $i_{s,n,j}(t)$  PSD can be estimated by

$$\frac{\overline{i_{s,n,j}^2}}{\Delta f} = \frac{I_P^2}{T_{\text{PEF}}^2} \left( \text{psd}(\Delta t_r) + \text{psd}(\Delta t_f) \right) = \frac{I_P^2}{2\pi^2} \cdot \mathcal{L}_j(f) \quad (21)$$

where  $\mathcal{L}_j(f)$  is the PN at the rising edge and falling edge of the reference clock. The in-band PN of the PLL due to the uncorrelated jitter can be derived as

$$\mathcal{L}_{\text{pll},j}(f) = \frac{\overline{i_{s,n,j}^2}}{\Delta f} \cdot \frac{(2R_D)^2}{K_{\text{pp}}^2} = \frac{N^2}{2} \mathcal{L}_j(f). \tag{22}$$

Fig. 9. Sampling error due to the REF jitter.

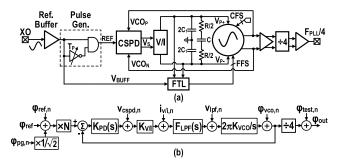

Fig. 10. (a) Block diagram of the proposed CSPLL with an RF-dividerless FTL. (b) Linear phase-domain model of the CSPLL.

Consequently, in a CSPD, the uncorrelated noise of the rising and falling edges of REF is only multiplied by  $N^2/2$  when transferred to the PLL output, alleviating the noise requirement of the pulse generator (PG). On the contrary, this noise is still multiplied by  $N^2$  for a VSPD in [12] and [13]. However, similar to a VSPD, the correlated noise generated by the off-chip crystal and on-chip reference buffer is still multiplied by  $N^2$  when transferred to the PLL output.

#### III. CHARGE-SAMPLING PHASE-LOCKED LOOP

Fig. 10(a) shows the block diagram of the proposed type-II CSPLL with an FTL operating in the background. A reference buffer and a PG are used to generate a narrow pulse signal (REF) from an off-chip sine reference. The CSPD converts the phase error between the VCO and REF into a differential voltage,  $V_S$ . A fully differential V/I stage then rejects the CM ripples on the CSPD output and converts its desired differential-mode signal into a current, which is further filtered by the loop filter (composed of R, C, and  $C_1$ ) to generate a fine-tuning voltage  $V_P (=V_{P+} - V_{P-})$  for the VCO. Note that there is no isolation buffer between the VCO and CSPD so as to verify the inherent low-spur performance of the CSPD. There is still a need for a VCO buffer in a practical system to drive the corresponding load (e.g., an IF mixer or a divider). If the CSPD is driven by the VCO buffer, even a lower reference spur could be obtained. However, this results in poor isolation between the CSPD and IF mixer or divider, leading to unpredictable noise coupling.

### A. Phase-Domain Model

Fig. 10(b) shows the linear phase-domain model for the proposed CSPLL, where  $K_{V/I}$  is the transconductance of the V/I stage and  $F_{LPF}(s)$  represents the transfer function of the loop filter. This model is accurate as long as the PLL

BW is much smaller than  $F_{\rm REF}$ . Like an SSPLL, there is no divide-by-N in the feedback path, and a virtual frequency multiplier " $\times N$ " is added to the reference path due to the subsampling process. However, a factor of  $1/\sqrt{2}$  is used for the PG noise to capture the charge-sampling process, as discussed in Section II. The closed-loop transfer function of the CSPLL can be found as

$$H_{\rm cl}(s) = \frac{H_{\rm ol}(s)}{1 + H_{\rm ol}(s)}$$

(23)

where  $H_{ol}(s)$  is the open-loop transfer function and can be expressed as

$$H_{\text{ol}}(s) = K_{\text{PD}}(s) \cdot K_{V/I} \cdot F_{\text{LPF}}(s) \cdot \frac{2\pi K_{\text{VCO}}}{s}$$

$$= \frac{2\pi \cdot K_{\text{PD}}}{1 + s \cdot R_D C_S} \cdot K_{V/I} \cdot \left(R + \frac{1}{s \cdot C}\right) \left\| \frac{1}{s \cdot C_1} \cdot \frac{K_{\text{VCO}}}{s} \right\|. \tag{24}$$

Here, we ignored the sinc-type low-pass filtering response of  $K_{\rm PD}(s)$  introduced by the windowed current integration since  $T_P$  is very small compared to  $T_{\rm REF}$ .

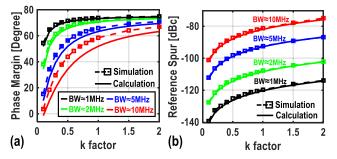

1) Phase Margin Analysis: By considering the presented phase-domain model, the phase margin of CSPLL can be estimated as

$$PM \approx \tan^{-1} (\omega_u RC) - \tan^{-1} (\omega_u RC_1) - \tan^{-1} (\omega_u R_D C_S)$$

(25)

where  $\omega_u$  is the frequency in which  $|H_{\rm ol}(s)| = 1$ . Since  $k \approx T_{\rm REF}/(R_D C_S)$ , we can rearrange this equation as

$$PM \approx \tan^{-1} \left(\omega_u RC\right) - \tan^{-1} \left(\omega_u RC_1\right) - \tan^{-1} \left(\frac{\omega_u T_{REF}}{k}\right).$$

(26)

Note that there is also a delay between the CSPD differential output and VCO waveforms due to the current integration. Nevertheless, the resulting phase delay is ignored in the phase margin calculations as it is  $<\tan^{-1}(2\pi\,F_{\rm REF}T_P/2)\approx 0.1^\circ$  in a realistic design. Due to the extra pole introduced by CSPD,  $C_1$  should be much smaller than that in a conventional loop filter ( $\sim 0.015 \times C$  in this design) to minimize PM degradation. By ignoring the pole introduced by CSPD ( $-1/R_DC_S$ ), we can approximate  $\omega_u$  as

$$\omega_u \approx \omega_n \cdot \sqrt{2\zeta^2 + \sqrt{4\zeta^4 + 1}} \tag{27}$$

where  $\omega_n$  (=( $K_{PD}K_{V/I}K_{VCO}/C$ )<sup>1/2</sup>) and  $\zeta$  (=0.5 $RC\omega_n$ ) are the natural frequency and the damping factor, respectively. Given a certain damping factor and PLL BW,<sup>4</sup> one can calculate C and R to find the phase margin. Fig. 11(a) shows the simulated and calculated phase margins versus k factor for various BW settings with  $\zeta$  = 1.5, where the discrepancy at high BW is due to the neglected pole of CSPD in estimating  $\omega_u$ . A large k factor improves the system phase margin, especially for large PLL BWs. However, to ensure a proper charge-sampling operation without sacrificing  $K_{PD}$ , the k factor must be smaller than 2. By choosing k factor between 0.4 and 2, PM varies between 51.9° and 70.9° for a BW of 5 MHz.

<sup>4</sup>BW can be estimated by  $(2\zeta^2 + 1 + ((2\zeta^2 + 1)^2 + 1)^{1/2})^{1/2} \cdot \omega_n/(2\pi)$ .

Fig. 11. Simulated and calculated (a) phase margin and (b) reference spur due to differential-mode ripple versus the k factor.

# B. Spur Due to Charge Sampling

In this section, the reference spur due to CSPD's non-idealities will be discussed and quantified.

1) Spur Due to BFSK Effect: Due to the windowed current integration, the CSPD can operate with a small  $T_P$ . In addition, the transconductors  $(M_{1,2})$  of CSPD can be sized very small without sacrificing in-band PN due to the CSPD's high  $K_{\rm PD}$  and short  $T_P$ . Those lead to a substantial spur reduction due to the BFSK effect as predicted by (1). Based on design parameters (i.e.,  $C_{\rm MODE} \approx 0.3$  fF,  $D_{\rm REF} = 0.003$ , and  $C_{\rm TANK} = 650$  fF),  $S_{\rm REF-BFSK}$  is -83 dBc, where  $C_{\rm MODE}$  is mainly originated from the gate-source capacitance  $(C_{\rm gs})$  variation of  $M_{1,2}$  due to the REF switching.

Apart from the spur due to the BFSK effect, unlike a conventional SSPLL in [10], a CSPLL contains other spur mechanisms that disturb the VCO through its tuning voltage. In other words, there is a tradeoff between the maximum BW and minimal reference spur level. Nevertheless, it will be shown in Section III-B2 that the spur level due to those mechanisms is much lower than  $S_{\text{REF-BESK}}$ .

2) Spur Due to Differential-Mode Ripple: Unfortunately, as can be gathered from Fig. 3(b), the differential output of CSPD ( $V_S$ ) experiences a ripple with a worst case peak value of  $2G_M A_{\rm VCO}/(\omega_{\rm VCO} C_S)$  during each phase comparison even if the PLL is locked. This ripple is first attenuated by the loop filter and then upconverted to spurious tones around the carrier. However, since  $C_S$  does not affect  $K_{\rm PD}$ , the  $V_S$  ripple can be easily suppressed by increasing  $C_S$  as long as the PLL phase margin is satisfied. Therefore, the output voltage swing of the CSPD can be very small (i.e., <100 mV) in the lock state, which is also beneficial to reduce the spur due to the charge kickback.

The fundamental component of this differential ripple at  $F_{\text{REF}}$  can be estimated as  $A_{\text{drip}} \approx 4G_M A_{\text{VCO}}/(N\pi \omega_{\text{VCO}} C_S)$ . The resulting spur level can be estimated by

$$S_{\text{REF-drip}} \approx 20 \cdot \log_{10} \left( \frac{A_{\text{drip}} \cdot K_{V/I} R K_{\text{VCO}}}{2F_{\text{REF}} \sqrt{1 + (2\pi F_{\text{REF}} R C_1)^2}} \right). \quad (28)$$

Based on the expression of  $A_{\text{drip}}$ ,  $K_{\text{PD}}$ , and k,  $S_{\text{REF-drip}}$  can be rearranged as

$$S_{\text{REF-drip}} \approx 20 \cdot \log_{10} \left( \frac{k \cdot K_{\text{PD}} K_{V/I} R K_{\text{VCO}}}{\omega_{\text{VCO}} \sqrt{1 + (2\pi F_{\text{REF}} R C_1)^2}} \right). \quad (29)$$

Fig. 11(b) shows the simulated and calculated spur level due to the differential-mode ripple versus the k factor for various

BW settings. By choosing k = 0.4, the resulting spur level is below -100.4 dBc for a 5-MHz BW, which is marginal compared with the spur due to the BFSK effect.

3) Spur Due to CM Ripple: In addition, the output of CSPD also contains a CM ripple [see Fig. 5], with a very large amplitude of  $\sim \Delta V_{\rm CM}/\pi$  at  $F_{\rm REF}$ . First, this ripple can be converted to a differential one by the V/I and results in a spur level estimated by

$$S_{\text{REF-crip1}} \approx 20 \cdot \log_{10} \left( \frac{G_M V_{\text{DC}} T_P}{C_S \pi} \cdot A_{\text{CM-DM}} \cdot \frac{K_{\text{VCO}}}{2 F_{\text{REF}}} \right)$$

(30)

where  $A_{\rm CM-DM}$  is the CM-to-differential-mode gain of the V/I at  $F_{\rm REF}$ . Second, the CM ripple is attenuated by the V/I and then appears at the input of the VCO. It will also introduce a spur due to the finite CM rejection of VCO. The resulting spur level can be estimated as

$$S_{\text{REF-crip2}} \approx 20 \cdot \log_{10} \left( \frac{G_M V_{\text{DC}} T_P}{C_S \pi} \cdot \frac{A_{\text{CM}}}{\text{CMR}} \cdot \frac{K_{\text{VCO}}}{2F_{\text{REF}}} \right)$$

(31)

where  $A_{\rm CM}$  is the CM gain of the V/I and CMR is the CM rejection ratio of the VCO. By considering  $K_{\rm VCO} = 50$  MHz/V and  $C_S = 250$  fF (or k = 0.4),  $A_{\rm CM-DM}$  and  $A_{\rm CM}/{\rm CMR}$  must be below -47 dB so as to suppress  $S_{\rm REF-crip1,2}$  below -90 dBc, which can be satisfied by a proper design.

4) Spur Due to  $C_S$  and  $R_D$  Mismatch: As discussed in Section II, the mismatch of  $C_S$  and  $R_D$  also creates a differential ripple at the CSPD output [see Fig. 6]. The resulting spur level can be estimated by

$$S_{\text{REF-ms}} \approx 20 \cdot \log_{10} \left( \frac{A_{\text{rip-ms}} \cdot K_{V/I} R K_{\text{VCO}}}{2 F_{\text{REF}} \sqrt{1 + (2\pi F_{\text{REF}} R C_1)^2}} \right)$$

(32)

where  $A_{\text{rip-ms}}$  is the ripple amplitude due to mismatch (i.e., equal to  $A_{\text{rip-}\Delta C_S}$  or  $A_{\text{rip-}\Delta R_D}$ ). By considering a moderate  $C_S$  or  $R_D$  matching (e.g.,  $\Delta C_S/C_S = \Delta R_D/R_D = 1\%$ ), the resulting spur level is below -105 dBc for a 5-MHz BW.

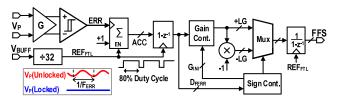

#### C. Frequency Locking

Like a VSPD, the CSPD also has a limited lock-in range and one cannot distinguish between the desired Nth harmonic and other harmonics of  $F_{REF}$ . To avoid locking to a wrong harmonic, the works [9]–[15] employed an RF divider-based FTL to bring the VCO frequency within the SSPLL's lock-in range. In the locked condition, the same FTL is also used to correct the frequency error  $(F_{ERR})$  introduced by the sudden frequency disturbance on the VCO. However, when the PLL is locked, the maximum  $F_{\text{ERR}}$  due to voltage and temperature variations or power leakage from other chip components is in the order of tens of MHz.<sup>5</sup> Consequently, it is not wise to use a full range FTL as its high-frequency divider consumes substantial power consumption. We address this issue by introducing a power-efficient FTL that does not rely on any power-hungry RF dividers and can be implemented chiefly by digital blocks, as can be gathered from Fig. 12.

Due to the removal of the RF divider, the lock-in range of the proposed FTL is limited to  $\pm 0.5 F_{REF}$  (e.g.,  $\pm 50$  MHz).

$^5$ The measured VCO frequency of this work is within  $\pm 27$  MHz over a VCO supply variation of 100 mV and a temperature variation of 160 °C.

Fig. 12. Block diagram of the FTL.

Hence, the VCO's frequency must be initially calibrated within  $\pm 0.5 F_{\rm REF}$  of the desired frequency. This is done offline by adjusting the coarse switchable capacitor at power ON. In a future design, a conventional FTL as in [9]–[15] can be used to automatically tune the VCO frequency. Once  $F_{\rm ERR}$  is within  $\pm 0.5 F_{\rm REF}$ , our proposed FTL takes over and the RF divider-based FTL is shut down to save power consumption.

Now, suppose that the VCO experiences a frequency disturbance during the CSPLL's nominal operation. If  $F_{ERR}$  is within the lock-in range (e.g., ~5 MHz), it can be corrected by the CSPLL. However, if  $F_{\text{ERR}}$  exceeds the lock-in range, it causes a lock failure of the CSPLL. An aliasing signal with an amplitude of  $\sim$ 20-to-40 mV and  $F_{\rm ERR}$  of  $|N| \times$  $F_{\text{REF}} - F_{\text{VCO}}$  will appear at the CSPD output [39], [40]. Instead of using the divided RF clock, the proposed FTL relies on this aliasing signal to initiate the feedback and calculate the frequency error. An amplifier and a Schmitt trigger are employed to convert this aliasing signal to a digital bitstream (ERR). A  $\div 32$  frequency divider generates the FTL master clock (REF<sub>FTL</sub>) from the reference. To ensure that the following digital logics are synchronized with REF<sub>FTL</sub>, the number of ERR rising edges is first accumulated only when REF<sub>FTL</sub> is high. Then, a differentiator clocked by REF<sub>FTL</sub> is used to obtain the digital representation of the frequency error  $(D_{\text{FERR}})$ . As a result, the ratio of REF<sub>FTL</sub> frequency to its duty cycle determines the minimum detectable  $F_{ERR}$ , which must be smaller than CSPLL lock-in range to ensure a seamless frequency locking operation.

FTL should first determine the  $F_{\rm ERR}$  sign since the aliasing signal does not provide that information. Consequently, FTL is initially set to decrease  $F_{\rm VCO}$  once the detected  $D_{\rm FERR}$  is larger than a programmable threshold. Depending on whether  $D_{\rm FERR}$  is decreasing or increasing, the initial loop sign is kept or flipped. To speed up the frequency locking process, FTL LG can be adaptively controlled based on the  $D_{\rm FERR}$  value. Once FTL brings  $F_{\rm VCO}$  into the PLL's lock-in range, the CSPLL rapidly locks the VCO phase to REF, forcing a nearly constant  $V_P$ . Hence, ERR stops toggling due to the insufficient input swing and low gain of the amplifier at frequencies below the PLL's lock-in range, eliminating the power of the digital logic. To avoid a false unlock detection, the noise of the amplifier is optimized such that it does not trigger the FTL when the CSPLL is locked.

# IV. CIRCUITS IMPLEMENTATION

### A. Reference Buffer and PG

Fig. 13(a) shows the reference buffer schematic adapted from [14]. The main transistor ( $M_1$ ) is a thick-oxide device to allow a higher input swing and is sized large and wide (3.2 mm/550 nm) to achieve a low PN floor (<-168 dBc/Hz).

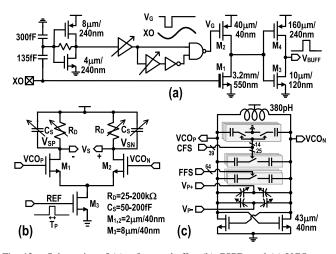

Fig. 13. Schematics of (a) reference buffer, (b) CSPD, and (c) VCO.

The gate terminal of the PMOS transistor ( $M_2$ ) is driven by a pulse signal,  $V_G$ , derived from the delayed reference clock edge. In this way, the short-circuit current of  $M_1$  and  $M_2$  is minimized since  $M_2$  is OFF when  $M_1$  conducts current. The rising edge of the reference buffer then drives the PG to realize the required CSPLL reference, whose pulsewidth ( $\sim$ 35–55 ps) can be adjusted by a 4-bit switched-capacitor bank. While the simulated pulsewidth of PG varies  $\sim \pm 50\%$  over PVT variations, the maximum PD gain degradation is limited to 30%.

### B. PD, V/I, and Loop Filter

Fig. 13(b) shows the CSPD schematic, whose phasedetection gain can be changed (~0.1–0.6 V/rad) by a 7-bit poly resistor. Moreover, a 4-bit switched metal-oxide-metal (MOM) capacitor is added to adjust the CSPD output CM voltage (e.g., >500 mV) over PVT variations. The VCO output directly drives the CSPD without any isolation buffers to eliminate their power consumption and noise. V/I is based on a fully differential folded-cascode operational transconductance amplifier whose transconductance can be tuned by a 4-bit source-degenerated poly resistor. Due to the achieved high  $K_{\rm PD}$ , even by consuming a negligible power (i.e., <20  $\mu$ W), the simulated in-band PN due to the V/I thermal noise is extremely low (i.e., <-148 dBc/Hz). The simulated  $A_{\rm CM-DM}$ and  $A_{\rm CM}$  are below -63 and -32 dB, respectively. The total capacitance of the loop filter is only 20.7 pF due to the fully differential structure, optimized  $K_{PD}$ , and wide PLL BW. The compensation resistance of the loop filter can be adjusted by a 4-bit poly resistor to regulate the BW and damping factor of the PLL.

# C. VCO

As shown in Fig. 13(c), the VCO employs an NMOS-only cross-coupled pair with a single-turn inductor to achieve a low PN. The implicit CM resonance technique is used to reduce PN further [41]–[43]. To cover a wide tuning range with a small  $K_{\rm VCO}$ , a combination of discrete tuning by switched-capacitor banks and continuous tuning by accumulation-mode MOS varactors is adopted. The control of the varactors is fully differential [15] to reject any CM ripples originated from the

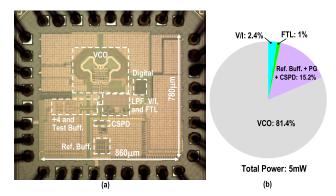

Fig. 14. (a) Chip micrograph. (b) Measured power breakdown.

heavily switched reference path with CMR > 15 dB according to post-layout simulations. In order to further minimize reference spurs due to the reference switching noise, the ground of the VCO, VCO test buffer, and loop filter is shared but is isolated from the ground of the reference buffer, PG, CSPD, V/I, and FTL.

# V. MEASUREMENT RESULTS

The CSPLL was fabricated in a standard 40-nm bulk CMOS and the core circuit occupies 0.13 mm<sup>2</sup>, as shown in Fig. 14(a). The PLL is powered by 0.6- and 1.1-V supplies. The 0.6-V supply is used for the VCO to satisfy time-dependent dielectric breakdown (TDDB) requirements for thin-oxide transistors, thus securing PLL's long-term reliability [44]. In a future design, thick-oxide devices can be used in the VCO such that the entire PLL can operate under a single power supply. This would not compromise the PLL PN and jitter performance but would slightly degrade VCO's tuning range. Alternatively, a complementary VCO can be used without sacrificing the tuning range and jitter performance. The entire PLL (excluding the test divider and buffer but including the reference buffer) dissipates 5 mW, and its power breakdown is shown in Fig. 14(b). The test buffer between the VCO and divider consumes 2.1 mW. The FTL consumes 50  $\mu$ W in total, of which the amplifier, the digital logic, and the reference clock divider consume 39, 8, and 3  $\mu$ W, respectively. The power and area overhead of the CSPD and FTL are negligible compared to the VCO.

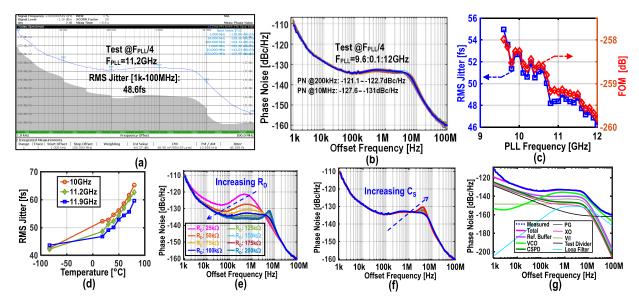

The reference clock is derived from an off-chip highquality VLCU-Type series crystal oscillator offered by Taitien. Fig. 15(a) shows the measured PN plot at a PLL frequency  $(F_{PLL})$  of 11.2 GHz after an on-chip divide-by-four. The RMS jitter is 48.6 fs (integrated from 1 kHz to 100 MHz but excluding reference spurs). To optimize the jitter performance at this frequency,  $T_P$  tuning code was adjusted to achieve the highest  $K_{\rm PD}$ , and the PLL BW was digitally regulated at  $\sim$ 6 MHz by adjusting the resistance of the loop filter, the transconductance of the V/I converter, and  $R_D$  of the CSPD. The measured PN, RMS jitter, and FOM plots covering the PLL's tuning range (i.e., 9.6–12 GHz) are shown in Fig. 15(b) and (c). The in-band PN, RMS jitter, and FOM are better than -121 dBc/Hz, 55 fs, and -258 dB, respectively. As shown in Fig. 15(d), the CSPLL appropriately works over a wide temperature range (i.e., from -80 °C to +80 °C), but its integrated jitter increases to 65 fs at 80 °C. Notice that all of the above measurements were carried

Fig. 15. (a) Measured PN at 11.2 GHz after an on-chip divide-by-four. (b) Measured PN for all integer channels. (c) RMS jitter and FOM versus PLL tuning range. (d) Measured RMS jitter versus temperature; measured PN for different values of (e)  $R_D$  and (f)  $C_S$ . (g) Simulated PN contribution of different PLL blocks with the measured PN performance.

out under the same loop parameters setting,<sup>6</sup> indicating the robustness of the design.

Fig. 15(e) shows the measured PN plots for different  $R_D$ values. As predicted by (8), by enlarging  $R_D$ ,  $K_{PD}$  increases, and the in-band PN at 200 kHz is monotonically reduced. Furthermore, for small  $R_D$  values, the CSPLL BW is not wide enough to sufficiently attenuate the VCO PN. As the PLL loop BW is widened by increasing  $R_D$ , the VCO PN is suppressed and the reference buffer eventually dominates the in-band PN. However, increasing  $R_D$  or  $C_S$  beyond their practical useful range introduces peaking on the measured PN plots [see Fig. 15(e) and (f)] due to the reduced phase margin. Changing  $T_P$  control code only marginally affects the measured PN performance due to the sine characteristics of  $K_{PD}$  [see Fig. 4(a)] and the limited  $T_P$  tuning range of the PG. To verify the phase-domain model presented in Section III, the measured reference and free-running VCO PN, in addition to simulated loop parameters of the CSPLL, were used to calculate the closed-loop PN and compare it to the measured result, as shown in Fig. 15(g). The measured PN in blue matches very well with the predicted PN in pink. The discrepancy between two curves at 1-kHz-to-4-kHz frequency offsets mainly originates from the neglected supply noise in the phase-domain analysis.

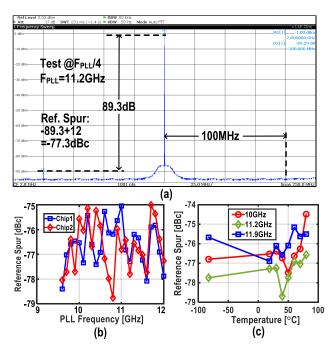

Fig. 16(a) shows the measured spectrum at the divide-by-four output. The measured reference spur is -89.3 dBc at the divider output, translating to -77.3 dBc when referred to  $F_{\rm PLL}$ . Since the measured spur level is  $\sim 25$  dB lower than the integrated PN ( $\sim -52$  dBc), the impact of reference spur on RMS jitter is marginal. The measured reference spur for two wire-bonded samples is <-74 dBc over the tuning range and varies <3 dB over temperatures, as shown in Fig. 16(b) and (c). The measured spur level varies <0.7 dB by sweeping  $C_S$  control code, indicating that the voltage ripple on  $V_S$  and the

Fig. 16. (a) Measured CSPLL spectrum after an on-chip divide-by-four. Measured reference spur versus (b) PLL tuning range and (c) temperature.

mismatch between CSPD components have a minor impact on reference spur. In addition, the measured spur level is also weakly related to  $T_P$  control word and is  $\sim$ 5 dB higher than the theoretical prediction given by (1). The dominated spur mechanism of the CSPLL is charge injection and clock feedthrough according to simulations. Compared with the CSPLL originally presented in [19], the spur performance is improved by modifying the PCB layout and reducing the PCB ground bounces originated from the high current spike of the reference pin. In the modified PCB, the reference ground and VCO ground are merely connected near their corresponding power supplies to minimize unwanted couplings.

<sup>&</sup>lt;sup>6</sup>Unless otherwise specified, we fixed the loop parameters setting for all of the remaining measurements in this article.

| TABLE I                                                                                                          |

|------------------------------------------------------------------------------------------------------------------|

| ${\tt Comparison  Table  With  State-of-the-Art  Inductance-Capacitance  (\it{LC})-Based  Integer-\it{N}  PLLs}$ |

|                                                  | This Work                 | [11]<br>JSSC'20              | [12]<br>ISSCC'19             | [23]<br>ISSCC'20            | [13]<br>JSSC'20   | [15]<br>JSSC'18         | [3]<br>JSSC'19               | [16]<br>ISSCC'19          | [2]<br>ISSCC'18           | [4]<br>VLSI'19              |

|--------------------------------------------------|---------------------------|------------------------------|------------------------------|-----------------------------|-------------------|-------------------------|------------------------------|---------------------------|---------------------------|-----------------------------|

| PLL Architecture                                 | Type-II<br>CSPLL          | Type-II<br>SSPLL             | Type-II<br>iSSPLL            | Type-II<br>SSPLL            | Type-II<br>SSPLL  | Type-I<br>SSPLL         | Type-II<br>RSPLL             | Type-II<br>SSPLL          | Type-II<br>CPPLL          | Type-II<br>ILCM             |

| Power Supply [V]                                 | 1.1/0.6                   | 0.65                         | 1/0.55                       | NA                          | 1                 | 0.8                     | 1.2/0.5                      | NA                        | NA                        | NA/0.14                     |

| F <sub>REF</sub> [MHz]                           | 100                       | 200                          | 103                          | 50                          | 100               | 100                     | 50                           | 100                       | 500                       | 100                         |

| F <sub>PLL</sub> [GHz]<br>FTR [GHz]              | 11.2<br>9.6-12<br>(22.2%) | 14<br>12-16<br>(28.6%)       | 26.4<br>25.4-29.5<br>(14.9%) | 13.05<br>12-14.5<br>(18.9%) | 2.4<br>NA<br>(NA) | 5<br>4.6-5.6<br>(19.6%) | 2.55<br>2.05-2.55<br>(21.7%) | 3.8<br>3.3-4.3<br>(26.3%) | 12.5<br>7.4-14<br>(61.7%) | 2.4<br>2.2-2.6<br>(16.7%)   |

| PLL Bandwidth [MHz]                              | ~6                        | ~7                           | ~4                           | ~3                          | ~0.6              | ~6                      | ~1                           | ~3                        | ~3                        | ~10                         |

| S <sub>REF</sub> [dBc]                           | -77.3                     | -64.6                        | -63                          | <b>-</b> 75                 | -67               | -64.1                   | -63                          | -75                       | -75                       | -66.5 \$                    |

| *S <sub>REF_Nor</sub> [dBc]                      | -77.3                     | -66.5                        | -70.4                        | -76.3                       | -53.6             | -57.1                   | -50.1                        | -65.6                     | -76                       | -53.1                       |

| RMS Jitter, $\sigma_{rms}$ [fs] [Int. Bandwidth] | 48.6<br>[1k-100MHz]       | 56.4<br>[1k <b>-</b> 100MHz] | 71<br>[1k-100M]              | 83<br>[1k-100M]             | 161<br>[10k-100M] | 162.2<br>[10k-100MHz]   | 110<br>[10k-100M]            | 72<br>[1k-30MHz]          | 53.6<br>[10k-10M]         | 298<br>[0.1k <b>-</b> 100M] |

| P <sub>DC</sub> [mW]                             | 5                         | 7.2                          | 15.3 ^                       | 6.7                         | 0.9#              | 1.1                     | 3.7                          | 19.1                      | 45                        | 0.17 #                      |

| P <sub>DC</sub> of Iso. Buffer [mW]              | 0                         | 1.4                          | 0.56                         | ~1.5                        | 0                 | 0.15                    | ~0.4                         | ~7                        | NA                        | 0                           |

| Inductor Used in Iso. Buffer ?                   | NO                        | YES                          | YES                          | YES                         | NO                | NO                      | NO                           | NO                        | NO                        | NO                          |

| **FOM [dB]                                       | -259.2                    | -256.4                       | -251.1                       | -253                        | -256.3            | -255.4                  | -253.5                       | -250.1                    | -248.9                    | -258.2                      |

| ***FOM <sub>N</sub> [dB]                         | -279.7                    | -274.9                       | -275.4                       | -277.2                      | -269.8            | -272.4                  | -270.6                       | -265.8                    | -262.8                    | -272                        |

| Core Area [mm²]                                  | 0.13                      | 0.234                        | 0.24                         | 0.23                        | 0.42              | 0.01                    | 0.36                         | 0.21                      | 0.35                      | 0.25                        |

| Process [nm]                                     | 40                        | 40                           | 65                           | 65                          | 65                | 65                      | 65                           | 65                        | 16                        | 65                          |

\*S<sub>REF\_Nor</sub> = S<sub>REF</sub>+20\*log<sub>10</sub>(11.2GHz/ F<sub>PLL</sub>) \*\*FOM = 20\*log<sub>10</sub>( $\sigma_{rms}/1s$ )+10\*log<sub>10</sub>(P<sub>Dc</sub>/1mW) \*\*\*FOM<sub>N</sub> = FOM+10\*log<sub>10</sub>(1/N) defined in [8] \*Reference buffer power of 5.08mW excluded #FTL power excluded or not reported \$Reported value using an 800MHz reference

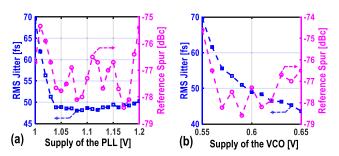

Fig. 17. Measured RMS jitter and reference spur versus the power supply of (a) PLL and (b) VCO at 11.2 GHz.

Fig. 17 shows the measured RMS jitter and reference spur versus the power supply of the PLL and VCO at 11.2 GHz. The RMS jitter varies <4 fs when the PLL supply was swept from 1.04 to 1.2 V. However, it degrades to 70 fs under a 1-V supply mainly due to the higher PN contribution of the reference buffer. As the oscillation swing increases by raising VCO's supply voltage, both VCO PN and  $K_{\rm PD}$  are improved, leading to a lower RMS jitter. The measured reference spur is still <-74 dBc over a wide supply variation.

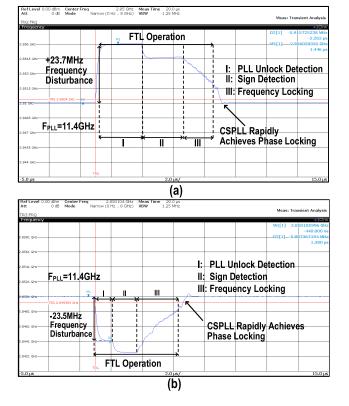

Fig. 18 shows the measured transient response of the FTL to a positive or negative frequency disturbance injected to the VCO by intentionally changing the VCO control code. In both cases, the FTL successfully detects the frequency error and relocks the VCO within 10  $\mu$ s due to the implemented adaptive gain adjustment technique.

Table I summarizes the CSPLL performance and compares it with the state of the art. Due to the proposed CSPD and low-power FTL, the proposed CSPLL shows the lowest reference spur, lowest jitter, best FOM, and a 2.5-dB improvement in  $FOM_N$ . While the SSPLL in [23] achieved a comparable

Fig. 18. Measured FTL transient response to (a) positive frequency disturbance and (b) negative frequency disturbance.

reference spur level, an area-hungry VCO isolation buffer with an inductive load was used. The CSPLL also occupies the smallest area compared to other type-II PLLs.

#### VI. CONCLUSION

We presented a CSPLL and analyzed in-depth its transient response, phase-detection gain, reference spur, and PN performance. Due to its high phase-detection gain and excellent isolation between the VCO and the sampling capacitor, the PLL can simultaneously achieve an ultra-low-RMS jitter and an outstanding reference spur with a large frequency multiplication factor. Moreover, a power-efficient highly digital FTL is introduced to lock the CSPLL robustly when the VCO faces a sudden frequency disturbance. Measurement results show that the CSPLL achieves 48.6-fs RMS jitter and -77.3-dBc reference spur at an 11.2-GHz carrier frequency while consuming 5 mW. This corresponds to the best-reported jitter-power FOM and reference spur performance.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. Stefano Pellerano, Yue Chen, Zhong Gao, Yiyu Shen, Atef Akhnoukh, Zu-Yao Chang, Pascal 't Hart, and Job van Staveren for technical discussions and measurement assistance.

#### REFERENCES

- [1] M. Brandolini *et al.*, "A 5 GS/s 150 mW 10 b SHA-less pipelined/SAR hybrid ADC for direct-sampling systems in 28 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 2922–2934, Dec. 2015.

- [2] D. Turker et al., "A 7.4-to-14 GHz PLL with 54fs<sub>rms</sub> jitter in 16 nm FinFET for integrated RF-data-converter SoCs," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 378–380.

- [3] J. Sharma and H. Krishnaswamy, "A 2.4-GHz reference-sampling phase-locked loop that simultaneously achieves low-noise and low-spur performance," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1407–1424, May 2019.

- [4] H. Zhang et al., "0.2 mW 70Fs<sub>rms</sub>-jitter injection-locked PLL using desensitized SSPD-based injecting-time self-alignment achieving -270 dB FoM and -66 dBc reference spur," in *Proc. Symp. VLSI Circuits*, Jun. 2019, pp. C38-C39.

- [5] S. Yoo, S. Choi, Y. Lee, T. Seong, Y. Lim, and J. Choi, "30.9 A 140fs<sub>rms</sub>-jitter and -72 dBc-reference-spur ring-VCO-based injection-locked clock multiplier using a background triple-point frequency/phase/slope calibrator," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 490–492.

- [6] A. Musa, W. Deng, T. Siriburanon, M. Miyahara, K. Okada, and A. Matsuzawa, "A compact, low-power and low-jitter dual-loop injection locked PLL using all-digital PVT calibration," *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 50–60, Jan. 2014.

- [7] B. M. Helal, C. M. Hsu, K. Johnson, and M. H. Perrott, "A low jitter programmable clock multiplier based on a pulse injection-locked oscillator with a highly-digital tuning loop," *IEEE J. Solid-State Circuits*, vol. 44, no. 5, pp. 1391–1400, May 2009.

- [8] K. M. Megawer, A. Elkholy, D. Coombs, M. G. Ahmed, A. Elmallah, and P. K. Hanumolu, "A 5 GHz 370fs<sub>rms</sub> 6.5 mW clock multiplier using a crystal-oscillator frequency quadrupler in 65 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 392–394.

- [9] X. Gao, E. A. M. Klumperink, M. Bohsali, and B. Nauta, "A low noise sub-sampling PLL in which divider noise is eliminated and PD/CP noise is not multiplied by N<sup>2</sup>," *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3253–3263, Dec. 2009.

- [10] X. Gao, E. A. M. Klumperink, G. Socci, M. Bohsali, and B. Nauta, "Spur reduction techniques for phase-locked loops exploiting a sub-sampling phase detector," *IEEE J. Solid-State Circuits*, vol. 45, no. 9, pp. 1809–1821, Sep. 2010.

- [11] Z. Zhang, G. Zhu, and C. P. Yue, "A 0.65-V 12–16-GHz sub-sampling PLL with 56.4-fs<sub>rms</sub> integrated jitter and -256.4-dB FoM," *IEEE J. Solid-State Circuits*, vol. 55, no. 6, pp. 1665–1683, Jun. 2020.

- [12] Z. Yang, Y. Chen, S. Yang, P.-I. Mak, and R. P. Martins, "16.8 A 25.4-to-29.5 GHz 10.2 mW isolated sub-sampling PLL achieving -252.9 dB jitter-power FoM and -63 dBc reference spur," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 270-272.

- [13] D.-G. Lee and P. P. Mercier, "A sub-mW 2.4-GHz active-mixer-adopted sub-sampling PLL achieving an FoM of -256 dB," *IEEE J. Solid-State Circuits*, vol. 55, no. 6, pp. 1542–1552, Jun. 2020.

- [14] X. Gao, E. Klumperink, G. Socci, M. Bohsali, and B. Nauta, "A 2.2 GHz sub-sampling PLL with 0.16ps<sub>rms</sub> jitter and -125 dBc/Hz in-band phase noise at 700μW loop-components power," in *Proc. Symp. VLSI Circuits*, 2010, pp. 139–140.

- [15] A. Sharkia, S. Mirabbasi, and S. Shekhar, "A type-I sub-sampling PLL with a 100×100 μm<sup>2</sup> footprint and -255-dB FOM," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3553-3564, Nov. 2018.

- [16] J. Kim et al., "16.2 A 76fs<sub>rms</sub> jitter and -40 dBc integrated-phase-noise 28-to-31 GHz frequency synthesizer based on digital sub-sampling PLL using optimally spaced voltage comparators and background loop-gain optimization," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 258–260.

- [17] L. Bertulessi et al., "A 30-GHz digital sub-sampling fractional-N PLL with -238.6-dB jitter-power figure of merit in 65-nm LP CMOS," IEEE J. Solid-State Circuits, vol. 54, no. 12, pp. 3493–3502, Dec. 2019.

- [18] K. Raczkowski, N. Markulic, B. Hershberg, and J. Craninckx, "A 9.2–12.7 GHz wideband fractional-N subsampling PLL in 28 nm CMOS with 280 fs RMS jitter," *IEEE J. Solid-State Circuits*, vol. 50, no. 5, pp. 1203–1213, May 2015.

- [19] J. Gong, F. Sebastiano, E. Charbon, and M. Babaie, "A 10-to-12 GHz 5 mW charge-sampling PLL achieving 50 fsec RMS jitter, -258.9 dB FOM and -65 dBc reference spur," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Aug. 2020, pp. 15-18.

- [20] W. Wu et al., "A 28-nm 75-fs<sub>rms</sub> analog fractional-N sampling PLL with a highly linear DTC incorporating background DTC gain calibration and reference clock duty cycle correction," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1254–1265, May 2019.

- [21] D. Liao, Y. Zhang, F. F. Dai, Z. Chen, and Y. Wang, "An mm-wave synthesizer with robust locking reference-sampling PLL and wide-range injection-locked VCO," *IEEE J. Solid-State Circuits*, vol. 55, no. 3, pp. 536–546, Mar. 2020.

- [22] M. Mercandelli et al., "17.5 A 12.5 GHz fractional-N type-I sampling PLL achieving 58fs integrated jitter," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 274–276.

- [23] Y. Lim et al., "17.8 A 170 MHz-lock-in-range and -253dB-FoM jitter 12-to-14.5 GHz subsampling PLL with a 150 μW frequency-disturbance-correcting loop using a low-power unevenly spaced edge generator," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 280–282.

- [24] Y. Hu *et al.*, "17.6 A 21.7-to-26.5 GHz charge-sharing locking quadrature PLL with implicit digital frequency-tracking loop achieving 75fs jitter and -250 dB FoM," in *IEEE Int. Solid-State Circuits Conf.* (*ISSCC*) Dig. Tech. Papers, Feb. 2020, pp. 276-278.

- [25] A. Santiccioli et al., "A 66-fs-rms jitter 12.8-to-15.2-GHz Fractional-N bang-bang PLL with digital frequency-error recovery for fast locking," IEEE J. Solid-State Circuits, vol. 55, no. 12, pp. 3349–3361, Dec. 2020.

- [26] W. Wu et al., "32.2 A 14 nm analog sampling fractional-N PLL with a digital-to-time converter range-reduction technique achieving 80fs integrated jitter and 93fs at near-integer channels," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2021, pp. 444–446.

- [27] M. Mercandelli et al., "32.3 A 12.9-to-15.1 GHz digital PLL based on a bang-bang phase detector with adaptively optimized noise shaping achieving 107.6fs integrated jitter," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2021, pp. 445–447.

- [28] J. Kim et al., "32.4 A 104fs<sub>rms</sub>-jitter and -61 dBc-fractional spur 15 GHz fractional-N subsampling PLL using a voltage-domain quantization-error cancelation technique," in *IEEE Int. Solid-State Cir*cuits Conf. (ISSCC) Dig. Tech. Papers, vol. 64, Feb. 2021, pp. 448–450.

- [29] E. Thaller et al., "32.6 A K-band 12.1-to-16.6 GHz subsampling ADPLL with 47.3fs<sub>rms</sub> jitter based on a stochastic flash TDC and coupled dual-core DCO in 16 nm FinFET CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, vol. 64, Feb. 2021, pp. 451–453.

- [30] L. Wu, T. Burger, P. Schönle, and Q. Huang, "A power-efficient fractional-N DPLL with phase error quantized in fully differentialvoltage domain," *IEEE J. Solid-State Circuits*, vol. 56, no. 4, pp. 1254–1264, Apr. 2021.

- [31] J. Gong, E. Charbon, F. Sebastiano, and M. Babaie, "A 2.7 mW 45fs<sub>rms</sub>-jitter cryogenic dynamic-amplifier-based PLL for quantum computing applications," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2021, pp. 1–2.

- [32] L. R. Carley and T. Mukherjee, "High-speed low-power integrating CMOS sample-and-hold amplifier architecture," in *Proc. IEEE Custom Integr. Circuits Conf.*, May 1995, pp. 543–546.

- [33] G. Xu and J. Yuan, "Comparison of charge sampling and voltage sampling," in *Proc. 43rd IEEE Midwest Symp. Circuits Syst.*, vol. 1, Aug. 2000, pp. 440–443.

- [34] R. Bagheri et al., "An 800-MHz-6-GHz software-defined wireless receiver in 90-nm CMOS," IEEE J. Solid-State Circuits, vol. 41, no. 12, pp. 2860–2876, Dec. 2006.

- [35] A. Abidi, "The path to the software-defined radio receiver," *IEEE J. Solid-State Circuits*, vol. 42, no. 5, pp. 954–966, May 2007.

- [36] M.-F. Huang, M.-C. Kuo, T.-Y. Yang, and X.-L. Huang, "A 58.9-dB ACR, 85.5-dB SBA, 5-26-MHz configurable-bandwidth, charge-domain filter in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 48, no. 11, pp. 2827–2838, Nov. 2013.

- [37] M. Tohidian, I. Madadi, and R. B. Staszewski, "Analysis and design of a high-order discrete-time passive IIR low-pass filter," *IEEE J. Solid-State Circuits*, vol. 49, no. 11, pp. 2575–2587, Nov. 2014.

- [38] H. Darabi and A. A. Abidi, "Noise in RF-CMOS mixers: A simple physical model," *IEEE J. Solid-State Circuits*, vol. 35, no. 1, pp. 15–25, Jan. 2000.

- [39] S. Pellerano *et al.*, "9.7 A scalable 71-to-76 GHz 64-element phased-array transceiver module with 2×2 direct-conversion IC in 22 nm FinFET CMOS technology," in *IEEE Int. Solid-State Circuits Conf.* (*ISSCC*) *Dig. Tech. Papers*, Feb. 2019, pp. 174–176.

- [40] H. Wang and O. Momeni, "A 9.6 mW low-noise millimeter-wave sub-sampling PLL with a divider-less sub-sampling lock detector in 65 nm CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2019, pp. 171–174.

- [41] J. Gong, Y. Chen, F. Sebastiano, E. Charbon, and M. Babaie, "19.3 A 200 dB FoM 4-to-5 GHz cryogenic oscillator with an automatic common-mode resonance calibration for quantum computing applications," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 308–310.

- [42] D. Murphy, H. Darabi, and H. Wu, "Implicit common-mode resonance in LC oscillators," *IEEE J. Solid-State Circuits*, vol. 52, no. 3, pp. 812–821, Mar. 2017.

- [43] M. Shahmohammadi, M. Babaie, and R. B. Staszewski, "A 1/f noise upconversion reduction technique for voltage-biased RF CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 51, no. 11, pp. 2610–2624, Nov. 2016

- [44] M. Babaie and R. B. Staszewski, "A study of RF oscillator reliability in nanoscale CMOS," in *Proc. Eur. Conf. Circuit Theory Design (ECCTD)*, Sep. 2013, pp. 1–4.

**Jiang Gong** (Student Member, IEEE) received the B.Sc. degree in electrical and electronic engineering from Jilin University, Changchun, China, in 2015, and the M.Sc. degree (*cum laude*) in microelectronics from Delft University of Technology, Delft, The Netherlands, in November 2017, where he is currently pursuing the Ph.D. degree.

His research focuses on high-spectral-purity and wide-tuning-range cryogenic frequency synthesizers for quantum computing applications.

Edoardo Charbon (Fellow, IEEE) received the Diploma degree from ETH Zürich, Zürich, Switzerland, in 1988, the M.S. degree from the University of California at San Diego, La Jolla, CA, USA, 1991, and the Ph.D. degree from the University of California at Berkeley, Berkeley, CA, USA, in 1995, all in electrical engineering and electrical engineering and computer science.

He was with Cadence Design Systems from 1995 to 2000, where he was the Architect of the company's initiative on information hiding for intellectual property protection. In 2000, he joined Canesta Inc., as the Chief Architect, where he led the development of wireless 3-D CMOS image sensors. Since 2002, he has been a member of the faculty of École polytechnique fédérale de Lausanne (EPFL), Lausanne, Switzerland, where has been a Full Professor since 2015. From 2008 to 2016, he was with Delft University of Technology, Delft, The Netherlands, as the Chair of VLSI design. He has been the driving force behind the creation of deep-submicrometer CMOS SPAD technology, which is mass-produced since 2015 and is present in telemeters, proximity sensors, and medical diagnostics tools. He has authored or coauthored over 400 articles and two books. He holds 23 patents. His research interests span from 3-D vision, FLIM, FCS, and NIROT to super-resolution microscopy, time-resolved Raman spectroscopy, and cryo-CMOS circuits and systems for quantum computing.

Dr. Charbon is a fellow of the Kavli Institute of Nanoscience Delft and a Distinguished Visiting Scholar of the W. M. Keck Institute for Space at Caltech

Fabio Sebastiano (Senior Member, IEEE) received the B.Sc. and M.Sc. degrees (cum laude) in electrical engineering from the University of Pisa, Pisa, Italy, in 2003 and 2005, respectively, the M.Sc. degree (cum laude) from the Sant'Anna School of Advanced Studies, Pisa, in 2006, and the Ph.D. degree from Delft University of Technology, Delft, The Netherlands, in 2011.

From 2006 to 2013, he was with NXP Semiconductors Research, Eindhoven, The Netherlands, where he conducted research on fully integrated

CMOS frequency references, nanometer temperature sensors, and areaefficient interfaces for magnetic sensors. In 2013, he joined Delft University of Technology, where he is currently an Associate Professor and the Research Lead of the Quantum Computing Division, QuTech, Delft, The Netherlands. He has authored or coauthored one book, 11 patents, and over 80 technical publications. His main research interests are cryogenic electronics, quantum computing, sensor readouts, and fully integrated frequency references.

Dr. Sebastiano is on the Technical Program Committee of the IEEE International Solid-State Circuits Conference (ISSCC), the IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, and the International Microwave Symposium (IMS). He was a co-recipient of the 2008 ISCAS Best Student Paper Award, the 2017 DATE Best IP Award, and the ISSCC 2020 Jan van Vessem Award for Outstanding European Paper. He is also serving as an Associate Editor for the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION. He has served as a Distinguished Lecturer for the IEEE Solid-State Circuit Society.

Masoud Babaie (Member, IEEE) received the B.Sc. degree (Hons.) from the Amirkabir University of Technology, Tehran, Iran, in 2004, the M.Sc. degree from Sharif University of Technology, Tehran, in 2006, and the Ph.D. degree (cum laude) from Delft University of Technology, Delft, The Netherlands, in 2016, all in electrical engineering.

From 2006 to 2011, he was with the Kavoshcom Research and Development Group, Tehran, where he was involved in designing wireless communication

systems. From 2014 to 2015, he was a Visiting Scholar Researcher at Berkeley Wireless Research Center, Berkeley, CA, USA. In 2016, he joined Delft University of Technology, where he is currently a tenured Assistant Professor. He has authored or coauthored one book, three book chapters, 11 patents, and over 60 technical articles. His research interests include RF/millimeter-wave integrated circuits and systems for wireless communications and cryogenic electronics for quantum computation.