# 23.2 A 40 A Shunt-Based Current Sensor with ±0.2% Gain Error from -40°C to 125°C and Self-Calibration

Tang, Zhong; Toth, Nandor G.; Zamparette, Roger; Nezuka, Tomohiro; Furuta, Yoshikazu; Makinwa, Kofi A.A.

DOI

10.1109/ISSCC42615.2023.10067304

Publication date 2023

Document Version

Final published version

Published in

2023 IEEE International Solid-State Circuits Conference, ISSCC 2023

Citation (APA)

Tang, Z., Toth, N. G., Zamparette, R., Nezuka, T., Furuta, Y., & Makinwa, K. A. A. (2023). 23.2 A 40 A Shunt-Based Current Sensor with ±0.2% Gain Error from -40°C to 125°C and Self-Calibration. In *2023 IEEE International Solid-State Circuits Conference, ISSCC 2023* (pp. 348-350). (Digest of Technical Papers - IEEE International Solid-State Circuits Conference; Vol. 2023-February). IEEE. https://doi.org/10.1109/ISSCC42615.2023.10067304

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

## 23.2 A 40A Shunt-Based Current Sensor with ±0.2% Gain Error from -40°C to 125°C and Self-Calibration

Zhong Tang<sup>1</sup>, Nandor G. Toth<sup>1</sup>, Roger Zamparette<sup>1</sup>, Tomohiro Nezuka<sup>2</sup>, Yoshikazu Furuta<sup>2</sup>, Kofi A. A. Makinwa<sup>1</sup>

<sup>1</sup>Delft University of Technology, Delft, The Netherlands <sup>2</sup>MIRISE Technologies, Aichi, Japan

Low-cost metal (e.g., PCB trace) shunts can be used to make accurate current sensors (<1% gain error) [1-3]. However, their reported maximum operating temperature (85°C) is not high enough for automotive applications, and at higher temperatures, shunt resistance may exhibit increased drift, especially at high current levels. This paper presents a metal-shunt-based current sensor with a wide temperature range and a stable on-chip reference current ( $I_{REF}$ ) source for shunt self-calibration. By employing a continuous-time (CT) front-end, it achieves an input noise density of  $14nV/\sqrt{Hz}$  while consuming only  $280\mu A$ , making it >10× more energy efficient than prior art [1,2], with comparable gain error ( $\pm 0.2\%$ ) over a wider current ( $\pm 40A$ ) and temperature (- $40^{\circ}C$  to  $125^{\circ}C$ ) range.

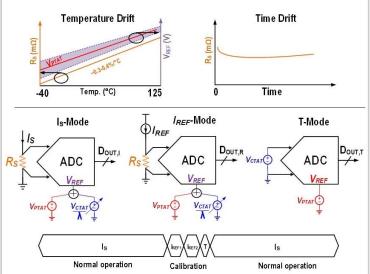

The proposed sensor employs an ADC to digitize the IR drop  $V_s$  across a copper shunt tresistor  $R_s$  (Fig. 23.2.1), whose large temperature coefficient (TC, ~0.4%/°C) is compensated by using a near-PTAT ADC reference ( $V_{REF}=V_{PTAT}+V_{CTAT}/\lambda$ ). By tuning  $\lambda$ , the TC of  $V_{REF}$  can be matched to that of the shunt [1,2], generating a temperature-independent digital output ( $I_s$ -mode). However,  $R_s$  may still drift over time [4]. In this work, by briefly disconnecting the shunt from the input current  $I_s$ ,  $R_s$  can be calibrated with a known  $I_{REF}$  ( $I_{REF}$ -mode). Since  $R_s$  is quite small (<1m $\Omega$ ), and  $I_{REF}$  is practically elimited to a few tens of mA, a low-noise ADC is needed to achieve the required sub- $\mu\Omega$  resolution in a reasonable measurement time (seconds). ADC offset and  $I_{REF}$  drift will also Scause residual errors. The former is mitigated by digital correlated-double-sampling (CDS). The latter requires a time and temperature stable  $I_{REF}$ , whose residual TC can be compensated by digitizing the ratio  $V_{CTAT}/V_{PTAT}$  to determine die temperature  $I_s$  to determine die temperature

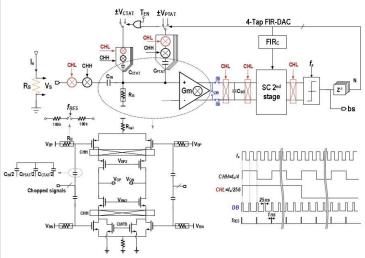

$\Xi$  Figure 23.2.2 shows the block diagram of the proposed current sensor. It consists of a  $\Xi$ 1-bit  $2^{nd}$ -order  $\Delta\Sigma$  modulator with a sampling frequency ( $f_s$ ) of 5.12MHz. The  $1^{st}$  stage is wbased on a CT capacitively-coupled Gm-C integrator, which blocks the input common-쁘mode voltage and avoids the kT/C noise limitations of the switched-capacitor (SC) gintegrators used in [1,2]. However, Gm-C integrators typically suffer from poor linearity, Rwhich either requires the use of source degeneration or complex multi-bit DACs to reduce their input swing. In this work, since the maximum shunt voltage  $V_{\text{S}}$  and the required V<sub>REF</sub> are quite small (~±50mV at room temperature, RT), the use of a simple 4-tap FIR- $\Xi$ DAC is enough to reduce the input swing to less than 30mV over temperature, which is well within the linear range of a tail-resistor-linearized (TRL) current-reuse OTA [5] (Fig. 23.2.2 bottom-left). To allow its NMOS and PMOS input pairs to be independently biased, the input and feedback capacitors are split into two banks, which couple V<sub>s</sub> and the FIR- $\stackrel{ extstyle e$ 턳directly to the input pairs, overloading the OTA and causing quantization-noise (Q-noise) 육folding. To mitigate this, dead-band (DB) switches briefly (~25ns) isolate the OTA from  $\frac{1}{2}$ the integration capacitor  $C_{INT}$  (40pF) during DAC transitions. Since its kT/C noise is Suppressed by the gain (~70dB) of the CT 1st integrator, the  $2^{nd}$  stage is built around an SC integrator with a sampling capacitor of 50fF. As in [5], it also serves as the summing Snode of the feedforward and FIR-DAC compensation paths.

To sense DC inputs, the capacitively-coupled TRL OTA must be chopped. However, this galso creates a gain notch at the chopping frequency  $f_{ch}$ . Since the 4-tap FIR-DAC creates a multiples of  $f_s/4$ , the TRL OTA can be chopped at  $f_s/4$  without degrading the modulator's noise-transfer function. Switched resistors are used to realize the large DC bias resistances (~40M $\Omega$ ) needed to ensure the highpass cut-off frequency (~1kHz) of the input network to well below  $f_{ch}$  (CHH=1.28MHz). To further mitigate offset and 1/f  $\Omega$  consequency chopping (CHL=20kHz) is applied to both integrators.

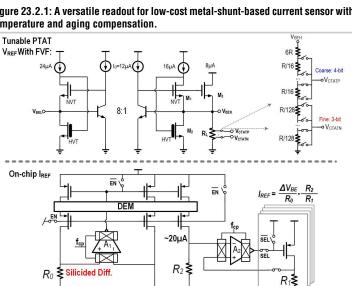

$\Xi$ As in [1-3], a tunable PTAT  $V_{REF}$  can be generated by diode-connected NPNs that provide  $\Xi$   $\Delta V_{BE}$  ( $V_{PTAT}$ ) and  $V_{BE}$  ( $V_{CTAT}$ ). However, due to their finite current gain  $\beta$  (~20), the base current of the NPNs will degrade the linearity of  $\Delta V_{BE}$  over temperature. In [6], this error  $\Xi$  is mitigated by using a source follower (SF) to supply the base current. Its output eimpedance must then be low enough to ensure rapid settling after the DAC transients,  $\Xi$  which would otherwise cause DAC non-linearity and Q-noise folding. This work employs  $\Xi$  a flipped voltage follower (FVF), whose output impedance is reduced by a factor ( $\Xi$   $\Xi$   $\Xi$  compared to that of an SF [6] (Fig. 23.2.3 top-left). To improve the pull-up capability of  $\Xi$  the higher  $V_{BE}$  ( $V_{BEH}$ ), an extra SF  $\Xi$  is added in parallel to achieve a Class-AB output.  $\Xi$  These measures reduce the settling time of  $\Sigma$   $\Xi$  transients to less than 25ns (13% of a  $\Xi$  sampling period) over PVT, allowing them to be blocked by the DB switches.

Since the TC of a copper shunt is nearly PTAT, the tuning factor  $\lambda$  needs to be quite large ( $|\lambda| > 90$ ) to cover the target TC tuning range (0.33±0.1%/°C). Thanks to the low output impedance of the FVF, part of this attenuation (<1/7) can be realized by a resistive divider

(Fig. 23.2.3 top-right). The rest (1/14) is then realized by the CDAC ( $C_{\text{PTAT}} = 14C_{\text{CTAT}} = C_{\text{IN}} = 4p\text{F}$ , in Fig. 23.2.2). To achieve a step of <10ppm/°C,  $V_{\text{CTAT}} / \lambda$  should be tuned with 7-bit resolution. By taking advantage of the differential nature of the CDAC, this is achieved by combining a 4-bit coarse trim of  $V_{\text{CTATP}}$  and a 3-bit fine trim of  $V_{\text{CTATN}}$  with the resistive dividers.

To monitor  $R_S$  drift,  $I_{REF}$  is generated by forcing  $\Delta V_{BE}$  (~54mV at RT) across a silicided diffusion resistor  $R_0$  (~16k $\Omega$ ) (Fig. 23.2.3 bottom).  $\Delta V_{BE}$  and  $R_0$  are both stable and have similar TCs (~0.3%/°C) [5], which are cancelled in the generated current. The residual TC (~60ppm/°C) can then be digitally compensated by sensing  $T_{DIE}$  in T-mode. Compared to the bandgap and SC-resistor-based  $I_{REF}$  generator used in [4], this approach avoids the need for an external zero-TC clock. As in [4], the resulting current is amplified by a current mirror (6×, ~20 $\mu$ A), and then boosted by an on-chip current driver with a programmable gain (from 500 to 2000). To mitigate errors due to transistor mismatch, chopping (at 625Hz) and DEM (at 1.25kHz) are applied to the amplifiers (A1 and A2) and current mirrors.

In T-mode, a fixed CTAT input ( $V_{BE}/28$ ) is applied to the modulator by using half of  $C_{CTAT}$ , while the input capacitor  $C_{IN}$  is shorted by the shunt. Then the bitstream average will be proportional to  $X=V_{BE}/\Delta V_{BE}$ , which is a well-defined function of temperature. Due to the small residual TC of  $I_{REF}$ , an inaccuracy of 1°C is acceptable, which can be achieved even with the expected mismatch (~1%) of  $C_{PTAT}$  and  $C_{CTAT}$ , and the required conversion time (tens of  $\mu$ s) is negligible compared to that required in  $I_{REF}$ -mode (seconds).

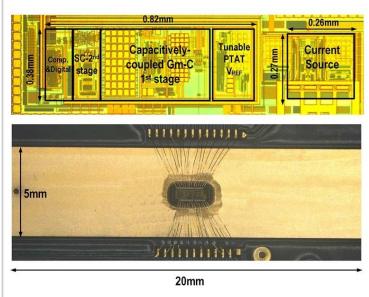

The sensor is implemented in a 0.18µm CMOS process and occupies 0.38mm² (Fig. 23.2.7, top). The modulator and the  $V_{\text{REF}}$  generator draw 280µA from a 1.8V supply, while the  $I_{\text{REF}}$  generator can output currents ranging from 11mA to 45mA. Its performance was verified with a  $0.83 m\Omega$  PCB trace shunt (Fig. 23.2.7, bottom). Good thermal coupling and galvanic isolation were achieved by bonding the chip to the shunt with nonconductive glue.

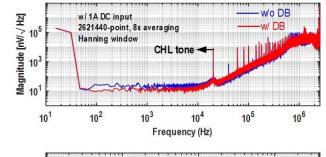

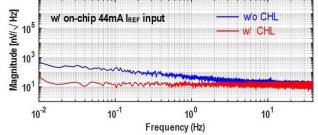

Figure 23.2.4 (top) shows the measured output spectra of the modulator. With DB disabled, its noise floor is limited to  $23\text{nV}/\sqrt{\text{Hz}}$  by Q-noise folding, which improves to  $14\text{nV}/\sqrt{\text{Hz}}$  after the DB is enabled. This results in a current-sensing resolution of  $1.7\text{mA}_{\text{rms}}$  in a 10kHz bandwidth. In  $I_{\text{REF}}$ -mode, with CHL enabled, the noise floor is flat down to 10mHz (Fig. 23.2.4 bottom), which is limited by ambient temperature drift and residual 1/f noise. This can be further suppressed by applying digital CDS to pairs of short (e.g., 128ms)  $I_{\text{REF}}$  measurements (45mA and 11mA). Then it achieves a resolution of ~9nVrms in 5s, which corresponds to a gain error of less than 0.1% ( $3\sigma$ ). Measurements on 10 samples show that the ADC's offset is less than  $35\mu\text{V}$  without CHL and is below  $4\mu\text{V}$  with CHI

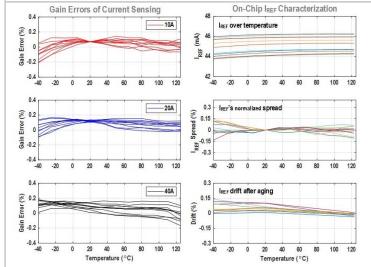

The sensor was characterized in a current range of  $\pm 40\text{A}$  from  $-40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$ . Figure 23.2.5 (left) shows the measured gain accuracy over temperature. With an optimal, but fixed,  $\lambda$  ( $\sim$ 200) obtained by batch calibration, it achieves a maximum gain error of  $\pm 0.2\%$  after a single-current gain trim (at RT and 10A). Figure 23.2.5 (right) shows the measured  $I_{\text{REF}}$  from  $-40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$ . Its absolute value varies by  $\pm 3\%$  due to resistor spread. After a 1-point correlated trim [5], both the nominal value and TC spread can be mitigated, resulting in a normalized spread of  $\pm 0.15\%$  from  $-40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$  after digital TC compensation. To verify the stability of  $I_{\text{REF}}$ , 10 samples were subjected to accelerate aging at  $150^{\circ}\text{C}$  for one week. The resulting drift is less than 0.1% around RT, and less than 0.15% over temperature, allowing a gain error of <0.3% for current sensing with shunt-drift calibration.

The performance of the sensor is summarized and compared with the state-of-the-art in Fig. 23.2.6. Compared to prior metal-shunt-based sensors [1-3], it achieves the highest energy efficiency (+11dB) and a competitive gain error ( $\pm 0.2\%$ ) over a wider current ( $\pm 40A$ ) and temperature (-40°C to 125°C) range. The proposed self-calibration scheme allows a gain error of 0.3% to be maintained even in the presence of shunt resistance drift.

#### Acknowledgement:

We would like to thank Zu-yao Chang and Lukasz Pakula for chip bonding, and thank Shotaro Wada, Shogo Kawahara for valuable comments.

#### References:

[1] Z. Tang et al., "A ±25A Versatile Shunt-Based Current Sensor with 10kHz Bandwidth and ±0.25% Gain Error from -40°C to 85°C Using 2-Current Calibration," *ISSCC*, pp. 66-67, Feb. 2022.

[2] R. Zamparette et al., " $\pm$ 2A/15A Current Sensor with 1.4 $\mu$ A Supply Current and  $\pm$ 0.35%/0.6% Gain Error From –40 to 85°C using an Analog Temperature-Compensation Scheme", *IEEE VLSIC*, June 2021.

[3] L. Xu et al., "A  $\pm$  12-A High-Side Current Sensor With 25 V Input CM Range and 0.35% Gain Error From  $-40^{\circ}$ C to  $85^{\circ}$ C," *IEEE SSCL*, vol. 1, no. 4, pp. 94-97, April 2018. [4] S. Danesh et al., "An Energy Measurement Frontend with Integrated Adaptive Background Accuracy Monitoring of the Full System Including the Current and Voltage Sensors," *IEEE JSSC*, vol. 54, no. 12, pp. 3269-3280, Dec. 2019.

temperature and aging compensation.

Figure 23.2.3: Simplified circuit diagram of the proposed tunable PTAT V<sub>RFF</sub> with FVF Figure 23.2.4: FFTs of the bitstream w/ and w/o dead-band (top) and FFTs of the (top) and the on-chip current source (bottom).

Figure 23.2.5: Gain errors of current sensing over temperature (left);  $I_{REF}$  over temperature (top-right); its spread after a 1-point correlated trim and TC compensation (middle-right) and the drift after accelerated aging at 150°C for one week (bottom-right).

Figure 23.2.2: Simplified circuit diagram of the Gm-C-based  $\Delta\Sigma$  modulator (top); The Figure 23.2.1: A versatile readout for low-cost metal-shunt-based current sensor with capacitively-coupled tail-resistor-linearized OTA (bottom-left); its timing diagram (bottom-right).

decimated results in  $I_{REF}$ -mode w/ and w/o CHL (bottom).

|                                                      | This work                        | Tang<br>ISSCC'22 [1]             | Zamparette<br>VLSI' 21 [2]       | Xu<br>SSCL' 18 [3]                | Danesh<br>JSSC'19 [4] | INA236 [7]           |

|------------------------------------------------------|----------------------------------|----------------------------------|----------------------------------|-----------------------------------|-----------------------|----------------------|

| Tech. (µm)                                           | 0.18                             | 0.18                             | 0.18                             | 0.18 BCD                          | 0.18                  | 2                    |

| Area (mm²)                                           | 0.38                             | 0.36                             |                                  | 1.4                               | -                     | 2                    |

| Shunt                                                | 0.83mΩ<br>(PCB)                  | 1.6mΩ<br>(PCB)                   | 3mΩ<br>(PCB)                     | 1mΩ<br>(PCB)                      | 0.14mΩ<br>(low-TC)    | -<br>(low-TC)        |

| l Range                                              | ±40A                             | ±25A                             | ±15A                             | ±12A                              | ±100 A                | 1-1                  |

| Gain Error                                           | ±0.2%                            | ±0.25%                           | ±0.6%                            | ±0.35%                            | ±0.1%                 | ~±0.1%<br>(ADC only) |

| Temp. Range                                          | -40 to 125°C                     | -40 to 85°C                      | -40 to 85°C                      | -40 to 85°C                       | -40 to 85°C           | -40 to 125°C         |

| ADC Offset                                           | <4µV                             | 6µV                              | 0.5µV                            | 1µV                               | 25                    | <5µV                 |

| Noise Density                                        | 14nV/√Hz                         | 85nV/√Hz                         | 955nV/√Hz                        | 174nV/√Hz                         | 7.8nV/√Hz             | ~300nV√Hz            |

| Resolution and BW                                    | 1.7mA@10kHz                      | 5.3mA@10kHz                      | 1.8mA@32Hz                       | 1.1mA@40Hz                        | -                     | -                    |

| Supply Voltage                                       | 1.8V                             | 1.8V                             | 1.8V                             | 1.8V                              | 3.3/1.8V              | 2.7-5.5V             |

| Supply Current                                       | 280µA<br>(ADC+V <sub>REF</sub> ) | 265µA<br>(ADC+V <sub>REF</sub> ) | 1.4µA<br>(ADC+V <sub>REF</sub> ) | 13.8µA<br>(ADC+V <sub>REF</sub> ) | 1700µA<br>(LNA+ADC)   | 300µA                |

| Dynamic Range                                        | 87dB                             | 73.5dB                           | 78.4 dB                          | 80.7dB                            | 72                    | -                    |

| FoM <sub>1</sub> *                                   | 160dB                            | 147dB                            | 149dB                            | 143dB                             | -                     | -                    |

| FoM <sub>2</sub> ** (nV <sup>2</sup> /Hz·mA)         | 54.9                             | 1915                             | 1277                             | 417.8                             | 103.4***              | 27000                |

| Shunt measurement<br>(I <sub>REF</sub> spread/drift) | Yes<br>(0.15%/0.15%)             | No                               | No                               | No                                | Yes<br>(0.15%/-)      | No                   |

FoM<sub>1</sub>=Dynamic Range +10log (Bandwidth/Power), from [1]

Figure 23.2.6: Performance summary and comparison with the state-of-the-art.

<sup>\*\*</sup>FoM<sub>2</sub>=Noise Density<sup>2</sup> × Supply current, from [4]

Excluding V<sub>REF</sub> generator

## **ISSCC 2023 PAPER CONTINUATIONS**

## Figure 23.2.7: Die micrograph (top); chip on a PCB shunt (bottom).

#### **Additional References:**

[5] S. Pan et al., "A 10fJ·K<sup>2</sup> Wheatstone Bridge Temperature Sensor with a Tail-Resistor-Linearized OTA," *IEEE JSSC*, vol. 56, no. 2, pp. 501-510, Feb. 2021.

[6] R. K. Kumar et al., "An Energy-Efficient BJT-Based Temperature-to-Digital Converter with  $\pm 0.13^{\circ}$ C (3 $\sigma$ ) Inaccuracy from -40 to 125 $^{\circ}$ C," *IEEE A-SSCC*, pp. 107-108, Nov. 2019.

[7] Texas Instruments, "INA236 data sheet", 2021,

<a href="https://www.ti.com/lit/ds/symlink/ina236.pdf">https://www.ti.com/lit/ds/symlink/ina236.pdf</a>