## Modelling and Analysis of the Single-Phase Operation of the Belgian PFC Rectifier

S.G. (Sjors) Verkamman

MSc Thesis

## Modelling and Analysis of the Single-Phase Operation of the Belgian PFC Rectifier

by

## Sjors Verkamman

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Wednesday October 7, 2020 at 11:00 AM.

| Student number:     | 4294815                             |                       |       |                     |

|---------------------|-------------------------------------|-----------------------|-------|---------------------|

| Project duration:   | December 16, 2019 – October 7, 2020 |                       |       |                     |

| Thesis committee:   | Prof. dr. ir. P. Bauer,             | TU Delft              | DCE&S | Professor           |

|                     | Dr. ir. T. Soeiro,                  | TU Delft              | DCE&S | Assistant Professor |

|                     | Dr. ir. M. Cvetkovic,               | TU Delft              | IEPG  | Assistant Professor |

| Company supervisor: | Dr. ir. J. Everts,                  | Prodrive Technologies |       |                     |

This thesis is confidential and cannot be made public until October 7, 2022.

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## Abstract

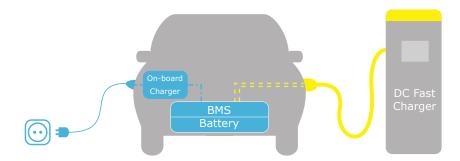

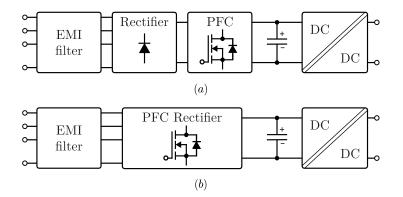

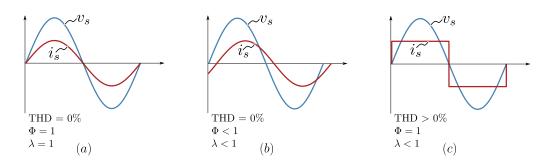

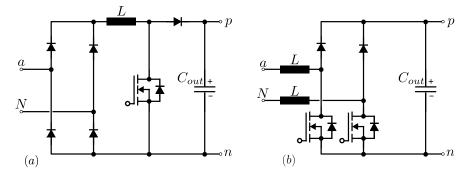

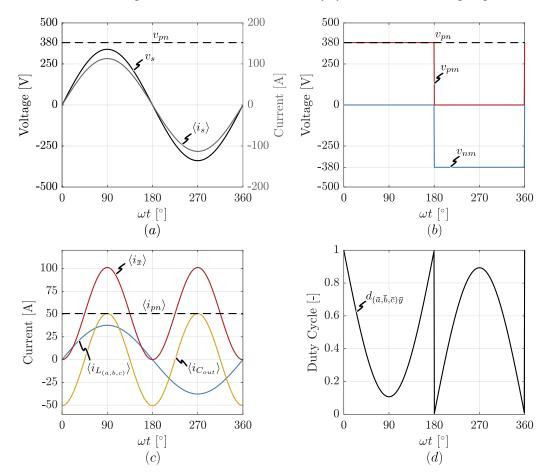

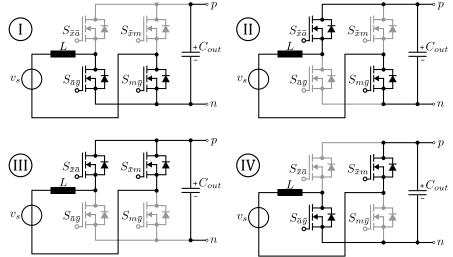

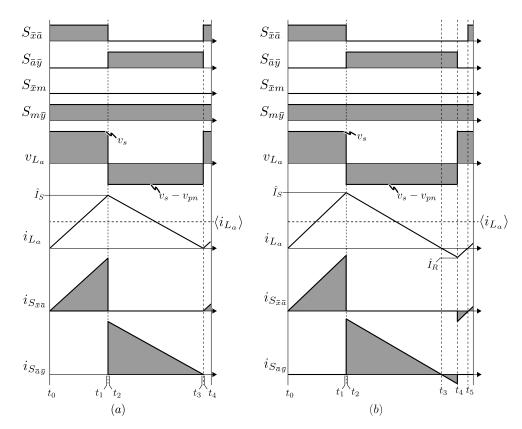

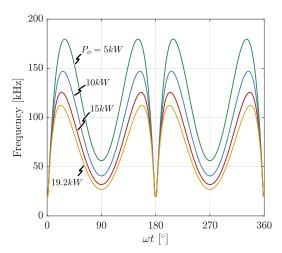

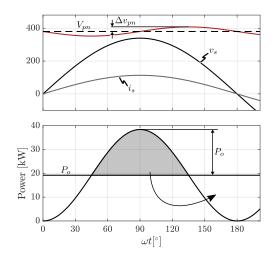

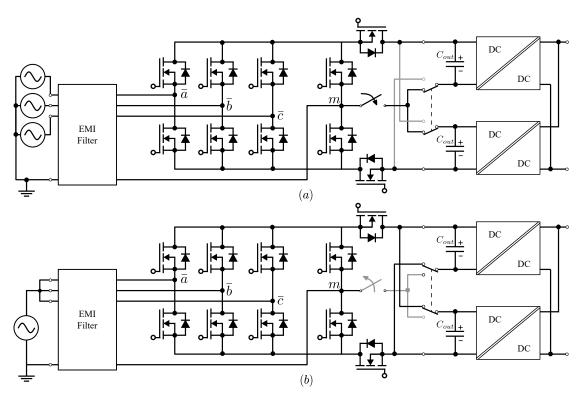

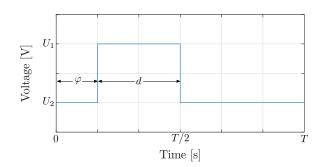

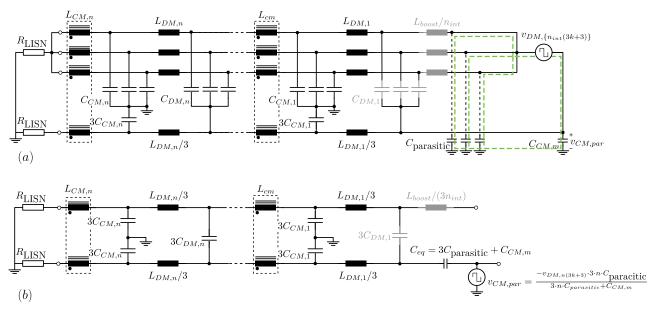

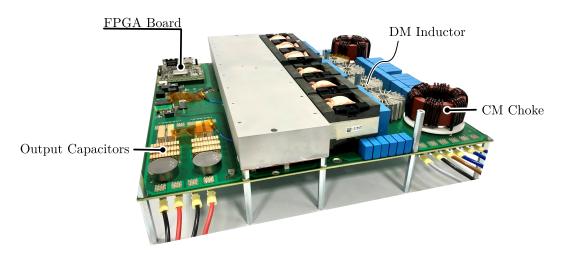

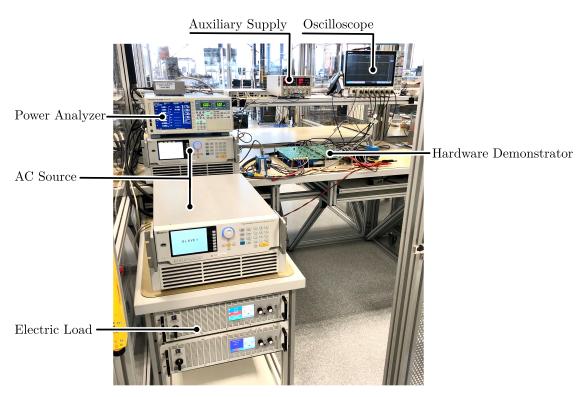

Boost-type power factor correction (PFC) rectifiers can be used in, for example, battery charging systems for Electric Vehicles (EVs). Conventionally available three-phase PFC rectifiers are limited to output 1/3 of the rated power when connected to a single-phase mains. This work presents the research into the single-phase operation of the Belgian rectifier, a novel boost-type PFC rectifier which allows for full power operation in both single- and three-phase operation (relevant for the three-wire split-phase systems in the USA with a maximum power of 19.2 kW). The single-phase AC-to-DC power converter is operated by paralleling and interleaving the three-phase rectifier bridge legs. By using the analysed triangular current mode (TCM) modulation scheme complete zero-voltage switching is achieved over the entire mains period. The power converter is further analysed with respect to the steady-state operation and component-level modelling. The modelling techniques are used to generate the Pareto-front of efficiency versus power density. The optimal design is selected based on the multi-objective requirements, and is a design with 6× interleaving with a boost inductance of 30µH that results in complete soft-switching transitions and achieves an efficiency of 98.42 % with a power density of 5.34 kW/dm<sup>3</sup>. After that, the single-phase Belgian rectifier is compared to the conventional six-switch boost PFC rectifier to identify and quantify the benefits. Finally, a closed-loop control model is proposed and implemented on the 19.2 kW, 1.5 kW/dm<sup>3</sup> hardware demonstrator for the conversion of a 240 V AC input with a maximum rms current of 80 A into a 380 V DC output to verify the single-phase operation of the Belgian PFC rectifier. Experimental results show efficiencies higher than 98% for power levels larger than 3 kW.

## Acknowledgement

In December 2019 I started my master thesis project at Prodrive Technologies with the expectations to be working the entire project in Eindhoven. However, from March 2020 Covid-19 forced us all to work from home generating a totally different work environment to which I had to adapt. Tackling problems was not as easy as before, and personal meetings changed to online meetings. I would like to thank Prodrive Technologies for allowing me to do my laboratory tests in the last months of the project while considering social distancing. The continuing support from the people around me has helped me to get to the conclusion of this research. Therefore, I could like to thank a few people.

First of all, I would like to thank my supervisor of Delft University of Technology, Prof. Bauer, for supporting me throughout the project and allowing doing this project at a company. Secondly, I would like to express my sincerest gratitude to my supervisor at Prodrive Technologies, Jordi Everts, for all his valuable guidance, knowledge, support, and enthusiasm throughout my project.

Additionally, I would like to thank Thomas Gerrits, Nikolay Mihaylov, Noud Slaats, Bas van de Ven for helping me whenever I was stuck with my models, simulations, software, or hardware demonstrator testing.

Finally, I would like to thank my family and friends for all the support during my studies and for allowing me to follow my dreams.

Sjors Verkamman Rotterdam, September 2020

## Table of Contents

| 1 | Intr | roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1  | Research Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 1.2  | Research Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 1.3  | Thesis Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| _ |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2 |      | erature Review 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 2.1  | The Basics of a Boost PFC Rectifier    5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

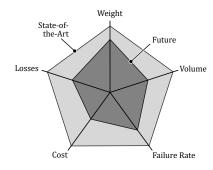

|   |      | 2.1.1    PFC Rectifier Efficiency and Power Density    8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 2.2  | Zero-Voltage Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 2.3  | Modelling of Power Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

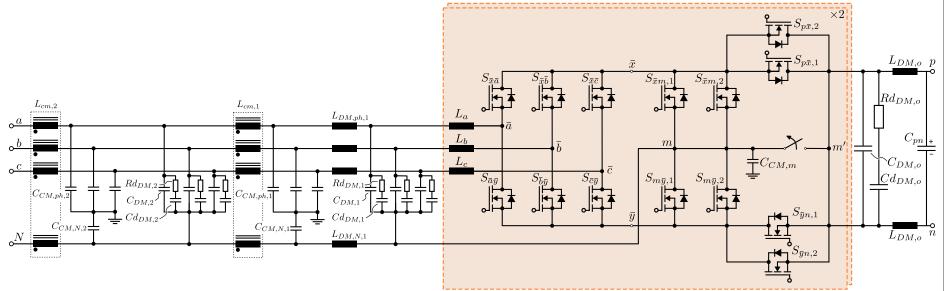

| 3 | Belg | gian Boost PFC Rectifier 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Ŭ | 3.1  | Introduction Internet Introduction Internet |

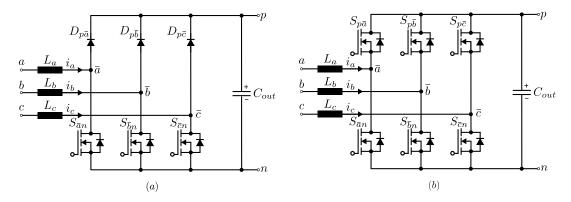

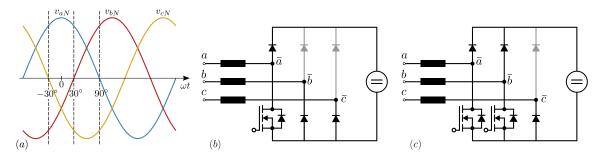

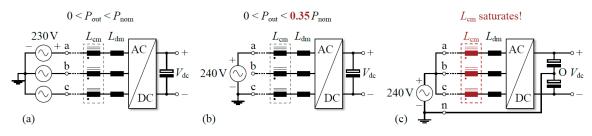

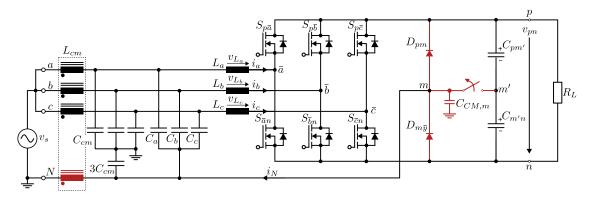

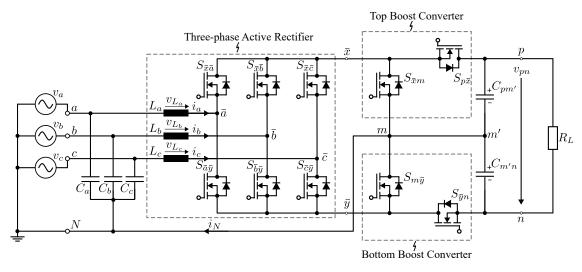

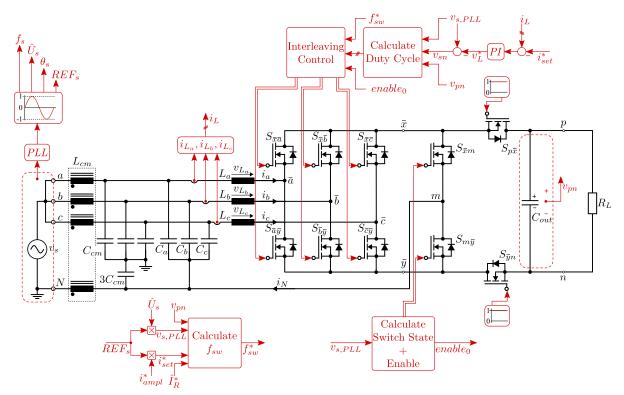

|   | 3.2  | Belgian PFC Rectifier Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

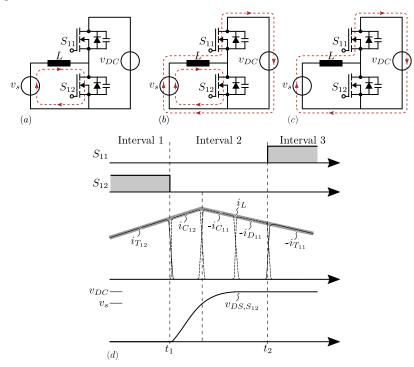

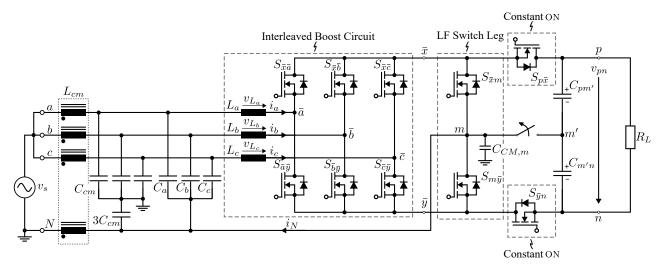

|   | 5.2  | 3.2.1 Single-Phase Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

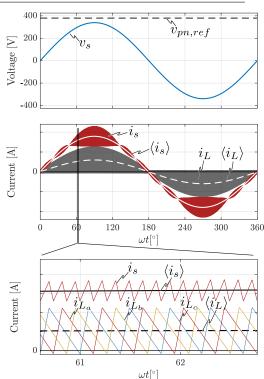

|   | 3.3  | Steady-State Average Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |      | Basic Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 3.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 3.5  | Component Stresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

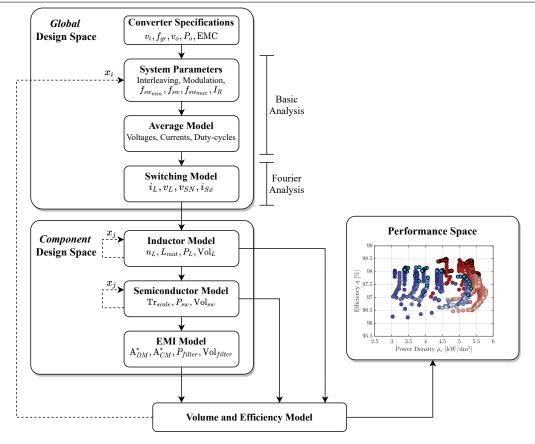

| 4 | Мос  | delling of the Main Converter Components 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 4.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

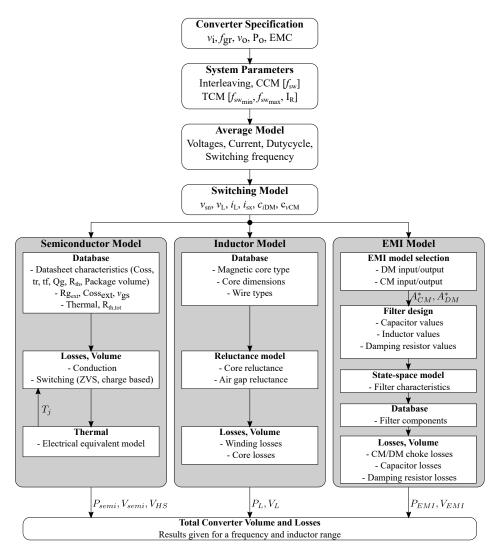

|   | 4.2  | Modelling Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 4.3  | Basic Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

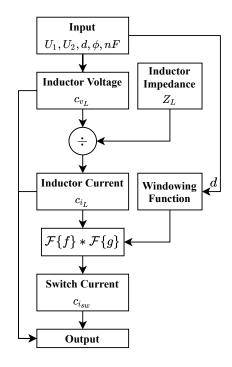

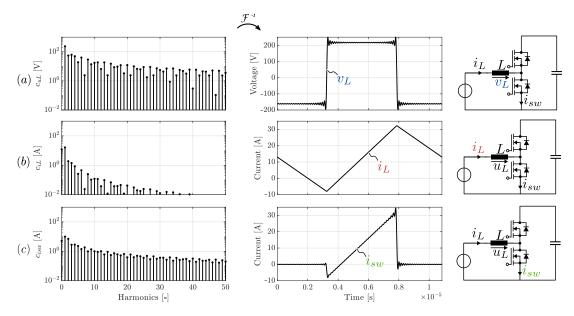

|   | 4.4  | Fourier Analysis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 4.5  | Component Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

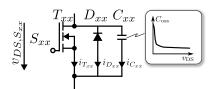

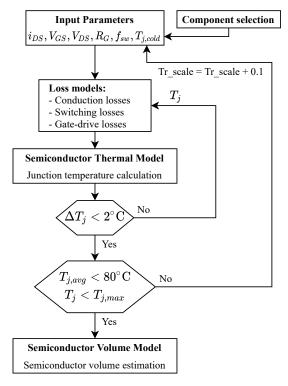

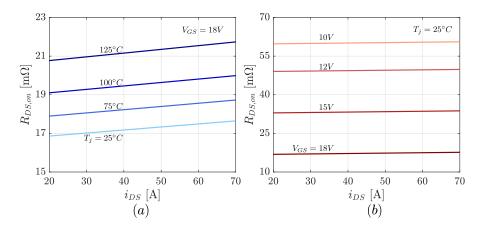

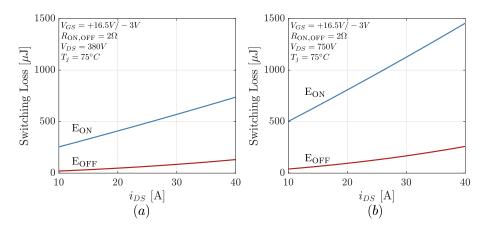

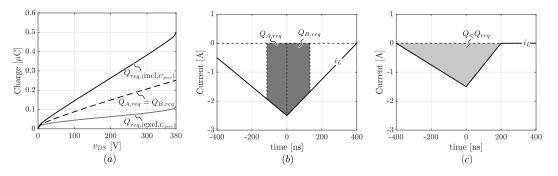

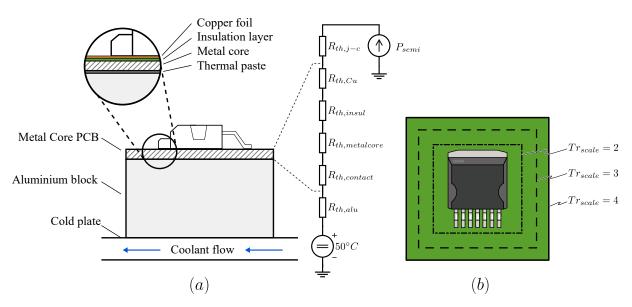

|   |      | 4.5.1 Semiconductor Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

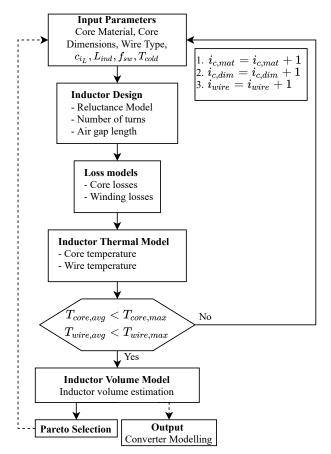

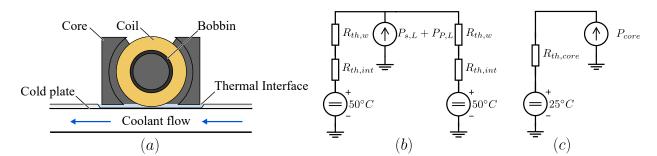

|   |      | 4.5.2 Inductor Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

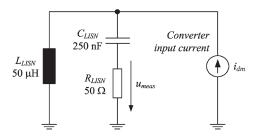

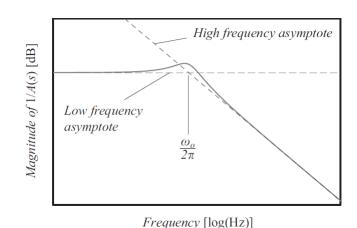

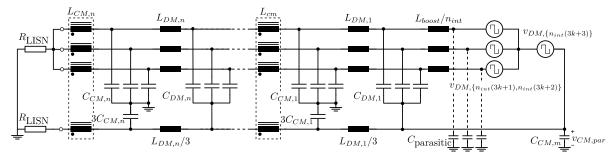

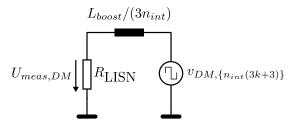

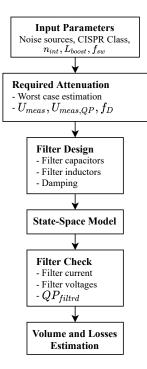

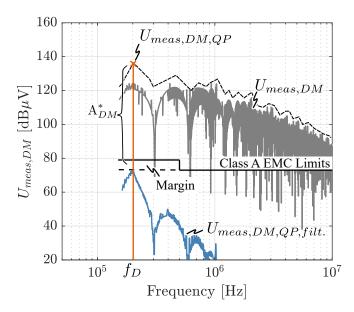

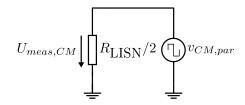

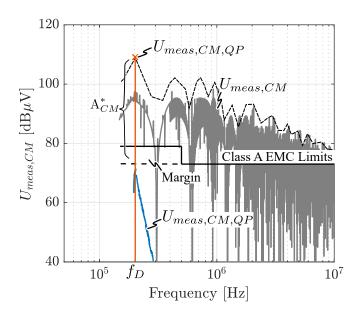

|   |      | 4.5.3 EMI Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 4.6  | Total Losses and Volume   40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 4.7  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 4.7  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

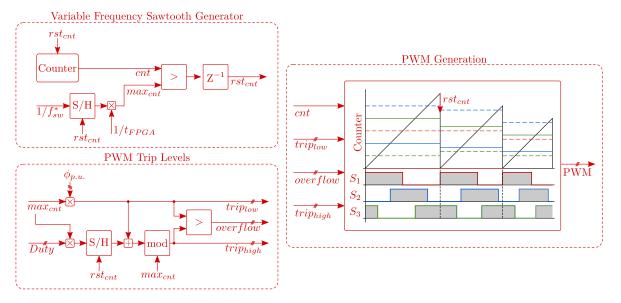

| 5 | Clos | sed-loop Control 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 5.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 5.2  | Control Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

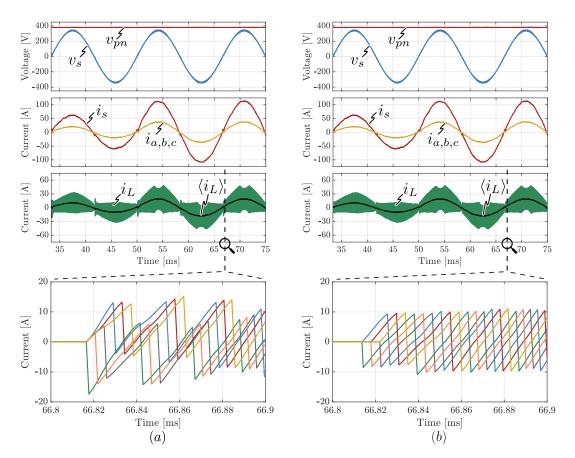

|   | 5.3  | Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 5.4  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| c | D    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

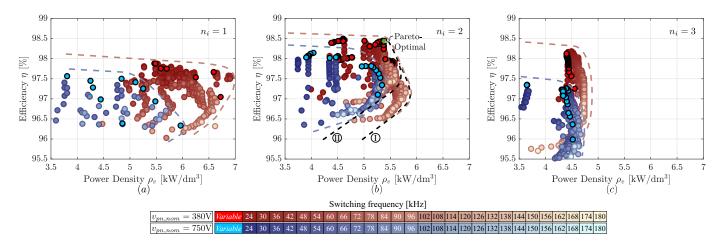

| 6 |      | sign Optimization 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

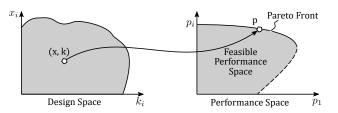

|   |      | Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

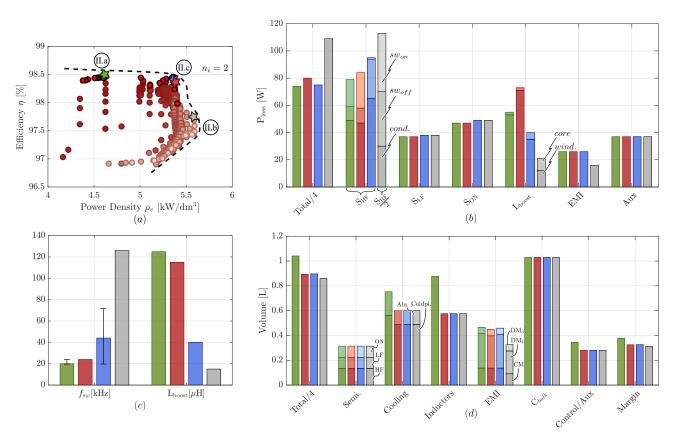

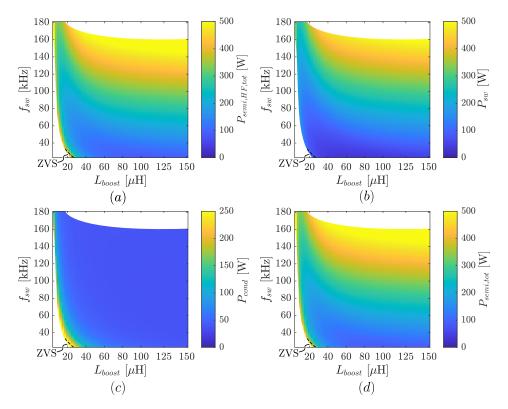

|   | 6.3  | Optimization Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 6.4  | Pareto-Optimum Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 6.5  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7 | Con  | nparative Evaluation 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| - | 7.1  | Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

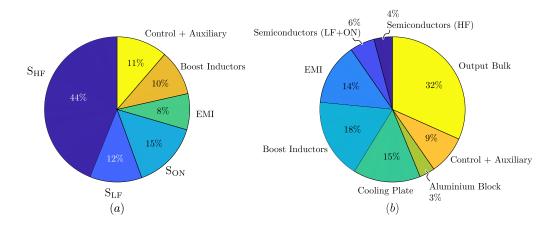

|   | 7.2  | Component Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | •••  | 7.2.1 Semiconductor Stresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |      | 7.2.1         Semiconductor Stresses         57           7.2.2         Semiconductor Losses         57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |      | 7.2.2         Semiconductor Losses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 7.3  | Comparison Conclusion         61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |