The lifeline of the Rover Deployment System

Bachelor Graduation Thesis

B. Goethals & S.J.H. Ramhit

# Power System: Lunar Zebro Rover Deployment System

The lifeline of the Rover Deployment System

by

## Brecht Goethals & Sanjeev J.H. Ramhit

| Student Name  | Student Number |

|---------------|----------------|

| B. Goethals   | 5540372        |

| S.J.H. Ramhit | 5229014        |

Supervisor: Dr. ir. C. Verhoeven Expert: Dr. A. Shekhar

Project Duration: April, 2024 - June, 2024

Faculty: Faculty of Electrical Engineering, Delft

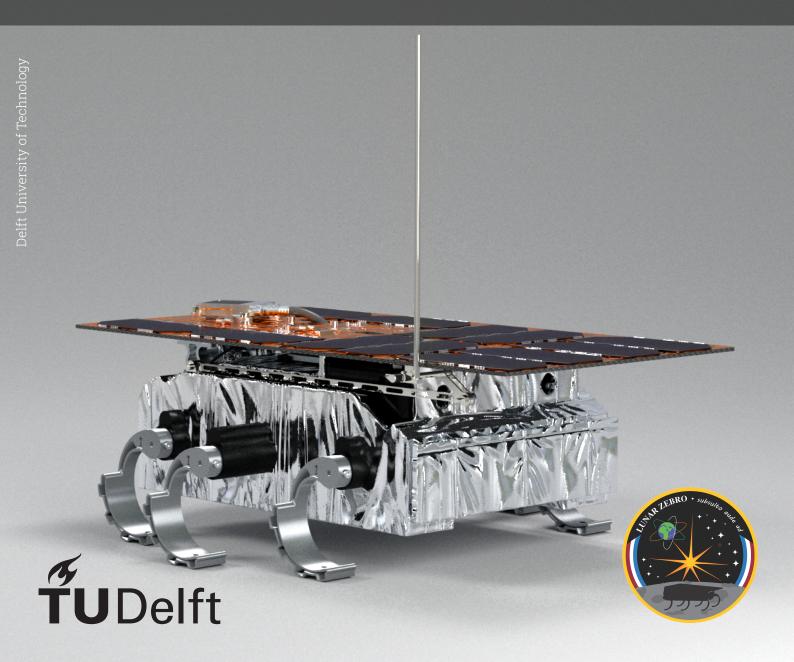

Cover: Lunar Zebro Render (Modified)

Style: TU Delft Report Style, with modifications by Daan Zwaneveld

## **Abstract**

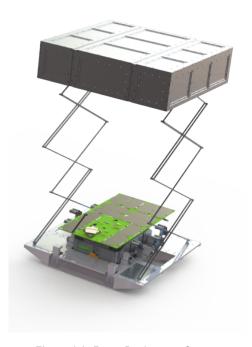

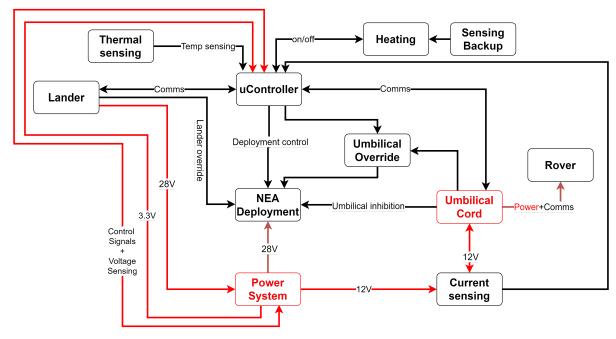

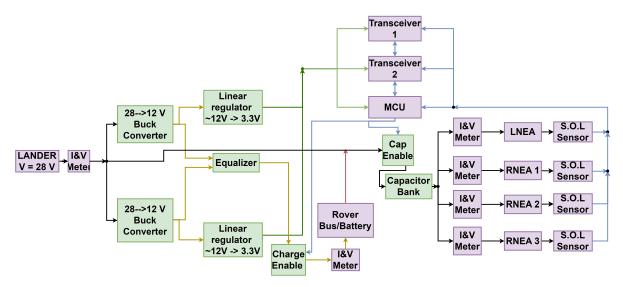

This thesis details the design and development of the Power System for the Rover Deployment System. This power system delivers and manages the necessary power required by the entire Rover Deployment System. The RDS is responsible for ensuring the rover's survival inside the transportation pod during transit. It also handles releasing the rover, which a mechanical mechanism will lower onto the lunar surface. The goal of Lunar Zebro is to send a nanosatellite to the moon for lunar surface exploration and radiation measurements.

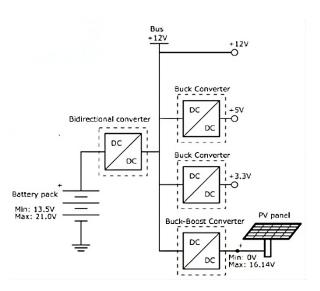

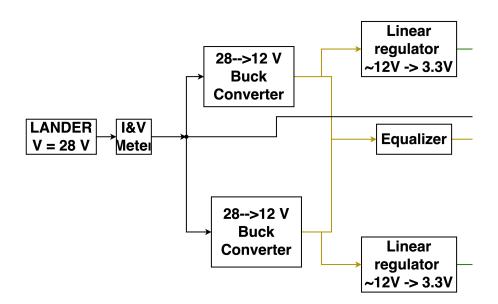

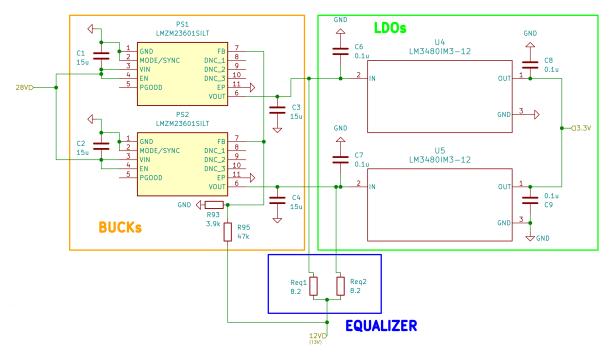

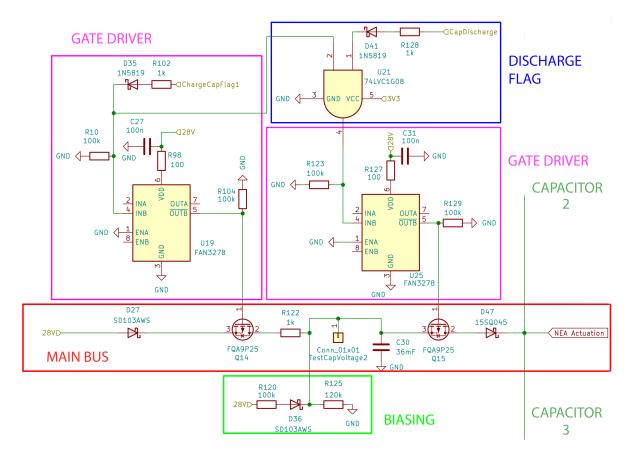

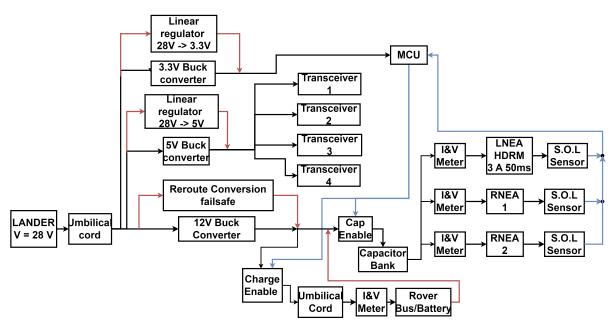

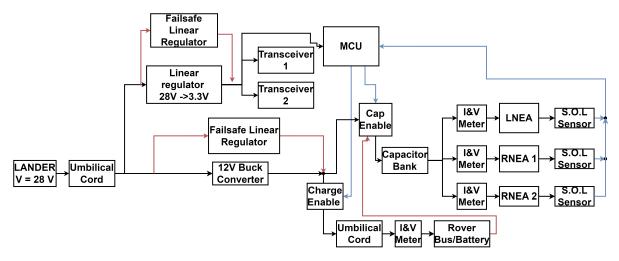

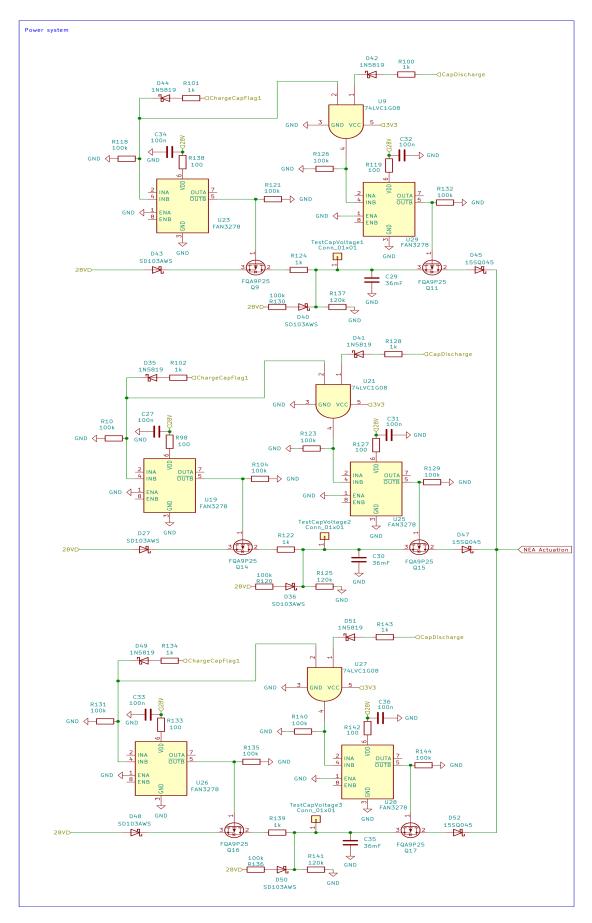

The power system was designed to power the MCU and transceivers at 3.3V, to provide power for rover charging at 12V, and to charge a capacitor bank used to provide the necessary actuation power to the NEAs. An electrically triggered umbilical release mechanism, unfortunately, could not be implemented due to a lack of available data. The circuit for this system was created, simulated, and added to the PCB design of the RDS. The simulations of the circuit behaved desirably. Due to the lead time on orders, the PCB has unfortunately not been received yet. Because of this, the entire power system has unfortunately not been tested yet.

## Preface

As the culmination of our undergraduate studies in Electrical Engineering, this thesis was prepared for the Bachelor's Graduation Project. This project was proposed by the Lunar Zebro research team. Its goal is to be the "world's smallest and lightest rover yet, built by TU Delft students" [75]. One of the necessary systems for this is the Rover Deployment System. Currently, the RDS team consists of mechanical students working on the mechanical aspects of the RDS. The RDS also requires a control system for communication, to direct power to the rover, and to deploy it. The design of this control system was the goal of this project.

This project could not have been possible without people willing to lend us their time and expertise to guide us during this project. The first person we would like to express our deep gratitude to is our supervisor and the project director for Lunar Zebro, Dr. Chris Verhoeven. While working on the 19th floor, we were always welcome to step into his office if we had a question. Through Dr. Verhoeven, we came into contact with the second person we would like to thank, namely Dr. Aditya Shekhar. His expertise in power electronics helped us design a large part of the voltage conversion portion of the system. We are grateful for the opportunity to finish our Bachelor's by adding something valuable to a research team like Lunar Zebro. They provided us with access to their facilities on the 19th floor, allowing us to work freely and comfortably. For this, we are extremely grateful. Some notable individuals on the team that we would like to thank are Project Leader Giannis Vardanikas, Chief Engineer and Head of System Engineers Ataberk Ayata, and RDS Engineer Sebastiaan Dirven. Last but not least, we would like to thank our colleagues, Diederik Aris, Henri Vanhuynegem, Noa Kant, and Tadjiro Velzel for an enjoyable and productive collaboration.

Brecht Goethals & Sanjeev J.H. Ramhit Delft, July 2024

## Contents

| Ak | stra             | ct                                        |                                                                                                                        |                  |                                                         |                                                         |   |      |          |          |      |          | ı                                                   |

|----|------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------|---------------------------------------------------------|---|------|----------|----------|------|----------|-----------------------------------------------------|

| Pr | eface            | )                                         |                                                                                                                        |                  |                                                         |                                                         |   |      |          |          |      |          | ii                                                  |

| Pr | eface            | )                                         |                                                                                                                        |                  |                                                         |                                                         |   |      |          |          |      |          | ii                                                  |

| No | men              | clature                                   |                                                                                                                        |                  |                                                         |                                                         |   |      |          |          |      |          | vi                                                  |

| No |                  | <b>clature</b><br>Abbrev                  |                                                                                                                        |                  |                                                         |                                                         |   | <br> | <br>     | <br>     | <br> | <br>     | <b>vi</b><br>vi                                     |

| 1  | 1.1<br>1.2       | Purpos<br>1.2.1                           | of-the-Art<br>se and So<br>Stakeho                                                                                     | Analysis cope    | ers                                                     |                                                         |   | <br> | <br><br> | <br><br> | <br> | <br><br> | 1<br>2                                              |

| 2  | Sys              | tem Ov                                    | erview                                                                                                                 |                  |                                                         |                                                         |   |      |          |          |      |          | 3                                                   |

| 3  | <b>Pro</b> § 3.1 | Requir                                    | RDS red<br>Require<br>3.1.2.1<br>3.1.2.2<br>Power S<br>Function<br>3.1.4.1<br>3.1.4.2<br>3.1.4.3<br>3.1.4.4<br>3.1.4.5 | ements Diverview | e entire sy<br>requirements<br>and requirements<br>ents | rstem ents . rements em uireme ers requ uireme m uireme | s |      |          |          |      |          | 5<br>5<br>5<br>6<br>6<br>6<br>6<br>6<br>7<br>7<br>7 |

| 4  |                  | tem De                                    |                                                                                                                        |                  |                                                         |                                                         |   |      |          |          |      |          | 8                                                   |

|    | 4.1              | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5 | Voltage<br>NEA act<br>Rover B<br>MCU an<br>Umbilica<br>evel Des<br>Final De<br>4.2.1.1<br>4.2.1.2                      | ision            | ers                                                     |                                                         |   | <br> |          |          |      | <br>     | 8<br>9<br>9<br>9<br>9<br>10<br>11                   |

| 5  | Circ             | uit Des                                   |                                                                                                                        | Capacitor B      | sank                                                    |                                                         |   | <br> | <br>     |          | <br> | <br>     | 11<br><b>12</b>                                     |

| -  |                  |                                           | e conver                                                                                                               | sion             |                                                         |                                                         |   |      |          |          |      |          | 12                                                  |

Contents

|    |                                        | 5.1.1                                           | Circuit a 5.1.1.1 5.1.1.2 5.1.1.3 5.1.1.4                                      | nalysis  Buck conv LDOs  Equalizer Supplement                          | <u>erters</u><br>   | <br>                 |               |             | <br><br>     | <br><br><br><br><br> | <br><br>     | <br><br>     | <br>         | <br>         | 13<br>14<br>15<br>16<br>17                   |

|----|----------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------|----------------------|---------------|-------------|--------------|----------------------|--------------|--------------|--------------|--------------|----------------------------------------------|

|    | 5.2                                    | Capac<br>5.2.1<br>5.2.2                         | itor Bank<br>Prelimin<br>Circuit a<br>5.2.2.1<br>5.2.2.2<br>5.2.2.3<br>5.2.2.4 | ary design nalysis  Main Bus Discharge Gate Drive Biasing . ve storage | flag .              |                      |               |             | <br>         | <br>                 |              |              | <br>         | <br>         | 18<br>18<br>19<br>19<br>21<br>21<br>22<br>22 |

|    |                                        | 5.2.4                                           |                                                                                | al Cord<br>Final desig                                                 |                     |                      |               |             | <br>         | <br>                 | <br>         | <br>         | <br>         |              | 23<br>24                                     |

| 6  | <b>Sim</b> (6.1 6.2 6.3 6.4            | Manufa<br>Simula                                | ation Set-<br>acturer mation goal                                              | up<br>nodels<br>s                                                      |                     | <br>                 |               |             | <br>         | <br>                 | <br>         | <br>         | <br>         |              | 25<br>25<br>26<br>27<br>27                   |

| 7  | 7.1<br>7.2<br>7.3                      | 12V Bt<br>7.1.1<br>7.1.2<br>7.1.3<br>Prototy    | us<br>Test resi<br>Test resi<br>Transier<br>ype testin                         | d Testingults: absolutults: differer ats ag                            | te meas<br>ntial me | suremo<br>asurei<br> | ents<br>ments | <br>S .<br> | <br><br><br> | <br><br><br><br><br> | <br><br><br> | <br><br><br> | <br><br><br> | <br>         | 29<br>30<br>32<br>33<br>33<br>34             |

| 8  | 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6 | Test re<br>Simula<br>Buck o<br>Capac            | omponent<br>sults<br>ation mod<br>converters<br>itor Bank                      | t selection  els s se mechanis                                         |                     | <br><br>             |               |             | <br><br><br> | <br><br><br><br><br> | <br>         | <br><br><br> | <br>         | <br><br><br> | 35<br>35<br>35<br>35<br>35<br>35<br>36       |

| 9  | Con                                    | clusior                                         | 1                                                                              |                                                                        |                     |                      |               |             |              |                      |              |              |              |              | 37                                           |

| 10 | 10.1<br>10.2<br>10.3<br>10.4<br>10.5   | Simula<br>Testing<br>Space<br>Energy<br>Buck of | ]<br>-qualifica<br>y storage<br>converter                                      | tion interleaving                                                      | <br><br>            | <br><br>             |               |             | <br>         | <br><br><br><br><br> | <br>         | <br><br><br> | <br>         | <br><br><br> | 38<br>38<br>38<br>38<br>39<br>39             |

| 11 | Futu                                   | ıre Wor                                         | <b>·</b> k                                                                     |                                                                        |                     |                      |               |             |              |                      |              |              |              |              | 40                                           |

| Re | feren                                  | ices                                            |                                                                                |                                                                        |                     |                      |               |             |              |                      |              |              |              |              | 41                                           |

| Α  | A.1<br>A.2                             | Input v<br>Simula                               | tions res                                                                      | on<br>power grap<br>ult graphs 6<br>hs                                 | 5.4                 |                      |               |             | <br>         | <br>                 | <br>         | <br>         | <br>         |              | <b>46</b><br>46<br>47<br>49                  |

| В  | High                                   | n <b>-Level</b><br>B.0.1                        | B.0.1.1                                                                        | esign<br>Voltage co                                                    | nversio             |                      |               |             |              |                      |              |              |              |              | <b>50</b> 50 51                              |

<u>Contents</u> v

|   |        |                                             | B.0.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Rover Battery                                                                                                                                                        |              | <br> | <br>         | <br>     |      |      |              |      | <br>51                                                         |

|---|--------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|--------------|----------|------|------|--------------|------|----------------------------------------------------------------|

|   | Е      | 3.0.2                                       | Second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Design                                                                                                                                                               |              | <br> | <br>         | <br>     |      |      |              |      | <br>51                                                         |

|   |        |                                             | B.0.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Voltage conve                                                                                                                                                        | rsion        | <br> | <br>         | <br>     |      |      |              |      | <br>52                                                         |

|   |        |                                             | B.0.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Capacitor bar                                                                                                                                                        | k            | <br> | <br>         | <br>     |      |      |              |      | <br>53                                                         |

|   |        |                                             | B.0.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Rover Battery                                                                                                                                                        |              |      |              |          |      |      |              |      | 53                                                             |

| _ | Circui | it Doo                                      | ian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |              |      |              |          |      |      |              |      | 54                                                             |

| C |        |                                             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | choice                                                                                                                                                               |              |      |              |          |      |      |              |      | 54<br>54                                                       |

|   |        |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |              |      |              |          |      |      |              |      | 54<br>54                                                       |

|   |        |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | y                                                                                                                                                                    |              |      |              |          |      |      |              |      | 54<br>54                                                       |

|   |        |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | y                                                                                                                                                                    |              |      |              |          |      |      |              |      | _                                                              |

|   |        |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | cost overview                                                                                                                                                        |              |      |              |          |      |      |              |      | 56                                                             |

|   |        | •                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ice                                                                                                                                                                  |              |      |              |          |      |      |              |      | 57                                                             |

|   |        | C.3.1                                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | diode                                                                                                                                                                |              |      |              |          |      |      |              |      | 57                                                             |

|   |        | C.3.2                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |              | <br> | <br>         | <br>     |      |      |              |      | <br>57                                                         |

|   |        | C.3.3                                       | Resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |              | <br> | <br>         | <br>     |      |      |              |      | <br>58                                                         |

|   |        |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Feedback res                                                                                                                                                         |              |      |              |          |      |      |              |      | 58                                                             |

|   |        |                                             | C.3.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Voltage droop                                                                                                                                                        |              |      |              |          |      |      |              |      | 59                                                             |

|   |        |                                             | C.3.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1k Capacitor                                                                                                                                                         |              |      |              |          |      |      |              |      | 61                                                             |

|   |        | C.3.4                                       | Superca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | pacitor                                                                                                                                                              |              | <br> | <br>         | <br>     | <br> |      |              |      | <br>61                                                         |

|   |        |                                             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                                                                                                                                                    |              |      |              |          |      |      |              |      |                                                                |

| D | Litera | iture F                                     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                      |              |      |              |          |      |      |              |      | 63                                                             |

| D |        |                                             | Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ·<br>I                                                                                                                                                               |              |      |              |          |      |      |              |      | <b>63</b>                                                      |

| D | D.1 F  | Prelim                                      | Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | rature Study .                                                                                                                                                       |              |      |              |          |      |      |              |      | 63                                                             |

| D | D.1 F  | Prelim<br>D.1.1                             | Research<br>inary Lite<br>Separati                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rature Study .<br>on devices                                                                                                                                         |              | <br> | <br>         | <br>     |      |      |              |      | <br>63<br>63                                                   |

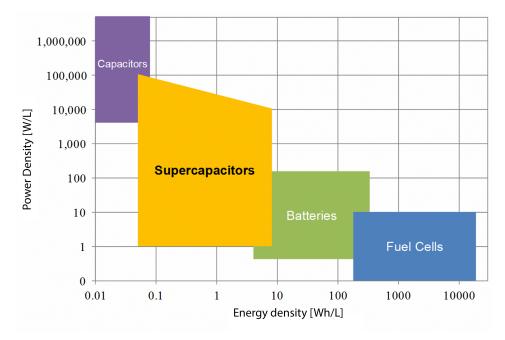

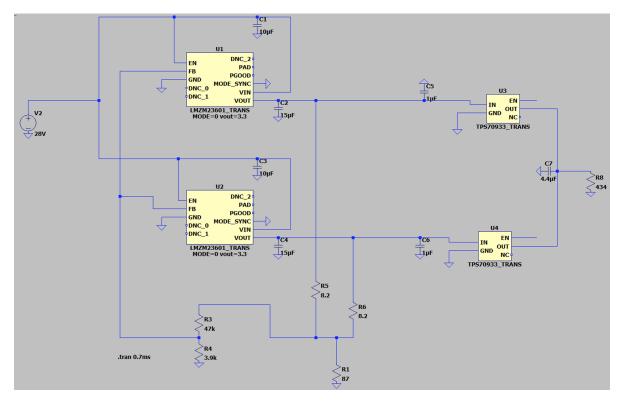

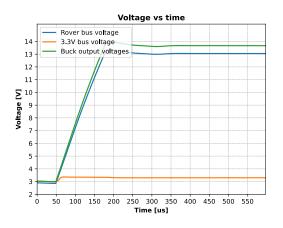

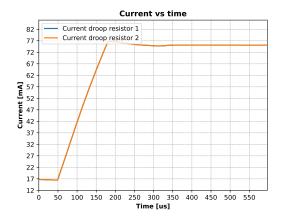

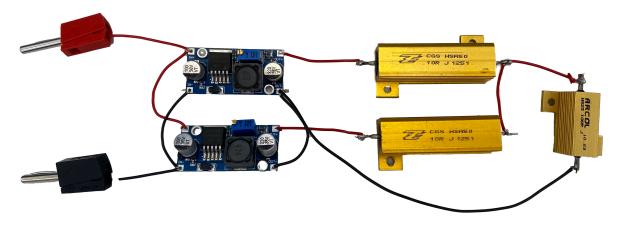

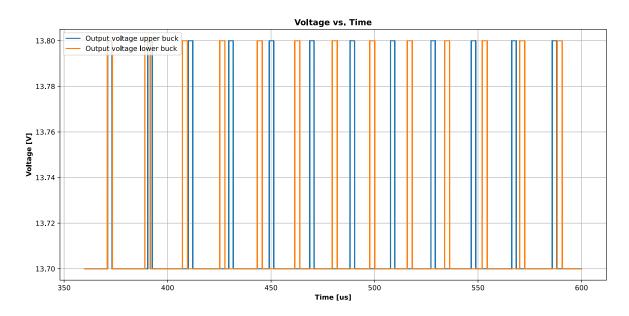

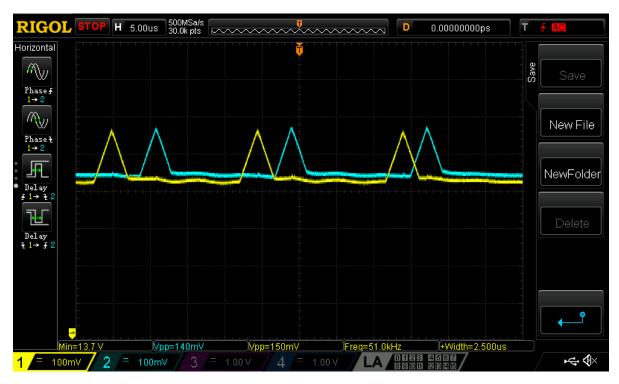

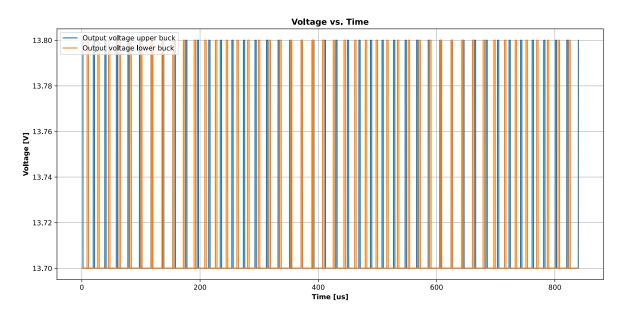

| D | D.1 F  | Prelim<br>D.1.1<br>D.1.2                    | Research<br>inary Lite<br>Separati<br>Soldering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rature Study .<br>on devices<br>g                                                                                                                                    |              | <br> | <br><br>     | <br>     |      |      | <br>         |      | <br>63<br>63<br>63                                             |