**Delft University of Technology**

#### Nanofabricated tips for device-based and double-tip scanning tunneling microscopy

Leeuwenhoek, Maarten

DOI 10.4233/uuid:ad392a9e-5490-49df-a8db-1e64715c8130

Publication date 2020

**Document Version** Final published version

#### Citation (APA)

Leeuwenhoek, M. (2020). Nanofabricated tips for device-based and double-tip scanning tunneling microscopy. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:ad392a9e-5490-49df-a8db-1e64715c8130

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

#### Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# NANOFABRICATED TIPS FOR DEVICE-BASED AND DOUBLE-TIP SCANNING TUNNELING MICROSCOPY

\_ I

\_ I

## NANOFABRICATED TIPS FOR DEVICE-BASED AND DOUBLE-TIP SCANNING TUNNELING MICROSCOPY

#### Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof.dr.ir. T.H.J.J. van der Hagen, voorzitter van het College voor Promoties, in het openbaar te verdedigen op donderdag 20 februari 2020 om 12:30 uur

door

#### **Maarten LEEUWENHOEK**

Master of Science in Physics, Universiteit Leiden, Leiden, Nederland, geboren te Nijmegen, Nederland. Dit proefschrift is goedgekeurd door de promotoren.

Samenstelling promotiecommissie:

| Rector Magnificus, | voorzitter                              |

|--------------------|-----------------------------------------|

| Dr. S. Gröblacher, | Technische Universiteit Delft, promotor |

| Dr. M.P. Allan,    | Universiteit Leiden, copromotor         |

*Onafhankelijke leden:* Prof. dr. A. F. Otte, Prof. dr. ir. T. H. Oosterkamp, Prof. dr. G. A. Steele, Dr. O. Kurnosikov, Dr. T. van der Sar,

Technische Universiteit Delft Universiteit Leiden Technische Universiteit Delft Technische Universiteit Eindhoven Technische Universiteit Delft

The work described in this thesis was performed at the Faculty of Applied Sciences at Delft University of Technology and the Faculty of Science at Leiden University.

*Keywords:* scanning tunneling microscopy, nanofabrication, double-tip, local gate *Printed by:* Ipskamp Printing

*Front & Back:* Maarten Leeuwenhoek

Copyright © 2020 by M. Leeuwenhoek Casimir PhD Series, Delft-Leiden 2020-05

ISBN 978-90-8593-432-5

\_ I

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

## **CONTENTS**

۱\_\_

| 1 | Introduction |                                         |   |  |  |  |  |  |

|---|--------------|-----------------------------------------|---|--|--|--|--|--|

|   | Refe         | erences                                 | 6 |  |  |  |  |  |

| 2 | Fab          | Fabrication of smart tips 9             |   |  |  |  |  |  |

|   |              | Introduction                            | 0 |  |  |  |  |  |

|   |              | Towards on-chip STM tips 10             | 0 |  |  |  |  |  |

|   |              | 2.2.1 Cleaved tips                      | 0 |  |  |  |  |  |

|   |              | 2.2.2 Deep etched smart tips            | 1 |  |  |  |  |  |

|   | 2.3          | Fabrication of SiN based smart tips     | 6 |  |  |  |  |  |

|   |              | 2.3.1 Overview                          | 6 |  |  |  |  |  |

|   |              | 2.3.2 Patterning SiN tip                | 7 |  |  |  |  |  |

|   |              | 2.3.3 Dicing                            | 8 |  |  |  |  |  |

|   |              | 2.3.4 Suspending SiN tip                | 9 |  |  |  |  |  |

|   |              | 2.3.5 Metallization                     | 0 |  |  |  |  |  |

|   |              | 2.3.6 Smart tip devices                 | 1 |  |  |  |  |  |

|   | 2.4          | Conclusion                              | 1 |  |  |  |  |  |

|   | Refe         | erences                                 | 3 |  |  |  |  |  |

| 3 | Real         | lization of the smart tip STM 23        | 5 |  |  |  |  |  |

| Ŭ |              | Introduction                            |   |  |  |  |  |  |

|   | 0.1          | 3.1.1 Overview                          | - |  |  |  |  |  |

|   | 3.2          | STM head                                | - |  |  |  |  |  |

|   | 3.3          | Cryostat                                |   |  |  |  |  |  |

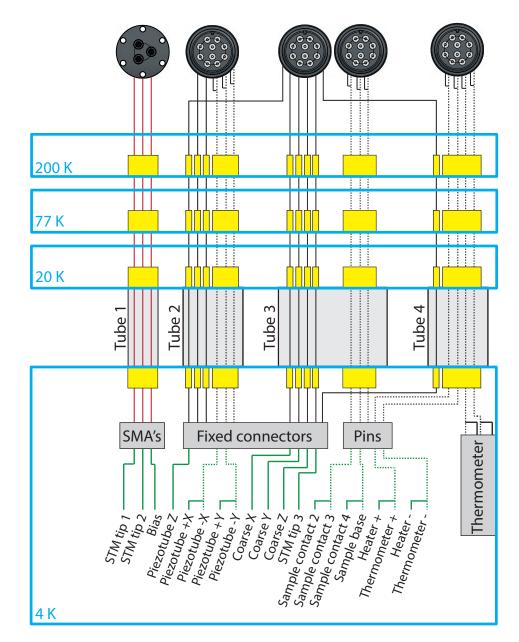

|   | 3.4          | Wiring                                  |   |  |  |  |  |  |

|   |              | 3.4.1 Thermalization                    | 4 |  |  |  |  |  |

|   | 3.5          | Ultra high vacuum system                | 6 |  |  |  |  |  |

|   | 3.6          | Vibration isolation                     | 7 |  |  |  |  |  |

|   |              | 3.6.1 Concrete island                   | 7 |  |  |  |  |  |

|   |              | 3.6.2 Vibration isolation table         | 8 |  |  |  |  |  |

|   |              | 3.6.3 Eddy current damper               | 8 |  |  |  |  |  |

|   | Refe         | erences                                 | 9 |  |  |  |  |  |

| 4 | Pro          | of of principle experiments 4           | 1 |  |  |  |  |  |

| т |              | Introduction                            | - |  |  |  |  |  |

|   | 4.2          | Single smart tip in a commercial STM.   | _ |  |  |  |  |  |

|   | 1.2          | 4.2.1         Implementation         44 | _ |  |  |  |  |  |

|   |              | 4.2.2 Smart tip performance             | _ |  |  |  |  |  |

|   | 4.3          | Smart tip STM performance               | - |  |  |  |  |  |

|   | 1.0          | 4.3.1 Scans                             | - |  |  |  |  |  |

|   |              | 432 Current and vibrational noise       | - |  |  |  |  |  |

|            | 4.4                  |         |                                        | 47              |

|------------|----------------------|---------|----------------------------------------|-----------------|

|            |                      | 4.4.1   | Implementation                         | 47              |

|            |                      | 4.4.2   | Approaching with a double-tip device   | 49              |

|            |                      | 4.4.3   | Challenges                             | 49              |

|            | Refe                 | erences |                                        | 51              |

| 5          | Tow                  | ards d  | ouble-tip STM                          | 53              |

| Ŭ          |                      |         | · · · · · · · · · · · · · · · · · · ·  | 54              |

|            |                      |         |                                        | 54              |

|            |                      |         |                                        | 54              |

|            |                      |         |                                        | 56              |

|            | 5.3                  |         |                                        | 60              |

|            |                      | 5.3.1   |                                        | 60              |

|            |                      | 5.3.2   |                                        | 62              |

|            |                      |         | 0                                      | 64              |

|            |                      |         |                                        | 67              |

|            |                      |         |                                        | 69              |

|            |                      |         | 1                                      | 69              |

|            | Refe                 | erences |                                        | 70              |

| 6          | Sca                  | nningt  | unneling microscopy with a local gate  | 73              |

|            | 6.1                  | · ·     |                                        | 74              |

|            | 6.2                  |         |                                        | 74              |

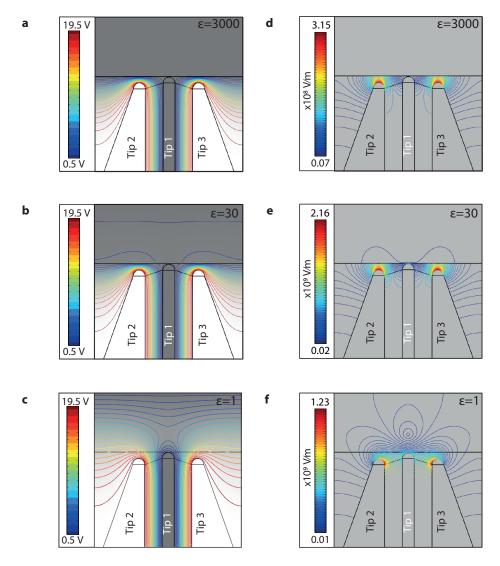

|            | 6.3                  | Prelin  | inary electric field simulations       | 77              |

|            |                      | 6.3.1   | Electric field inside a Mott insulator | 80              |

|            | 6.4                  | Devic   | es                                     | 81              |

|            | 6.5                  | Concl   |                                        | 81              |

|            | Refe                 | erences |                                        | 82              |

| 7          | Con                  | clusio  | 1                                      | 85              |

|            | 7.1                  |         |                                        | 87              |

|            | 7.2                  |         |                                        | 89              |

|            |                      |         |                                        | 91              |

|            | Dor                  | ination | of the transconductance                | റാ              |

| A          |                      |         |                                        | <b>93</b><br>96 |

|            | Refe                 | erences |                                        | 90              |

| B          |                      |         |                                        | 97              |

|            | Refe                 | erences |                                        | 99              |

| Su         | umma                 | arv     | 1                                      | 01              |

|            |                      |         |                                        |                 |

| Sa         | imen                 | vatting | 1                                      | 05              |

| С          | urric                | ulum V  | itæ 1                                  | 09              |

| <b>T</b> 2 | List of Publications |         |                                        |                 |

| LI         | stof                 | PUDIIC  | luons                                  | 11              |

| Ac         | Acknowledgements     |         |                                        | 13              |

\_ |

-I

# 1

**INTRODUCTION**

۱\_\_

1

#### Parts of this chapter have been published in Nanotechnology **30(33)**, 335702 (2019) [1].

Scanning tunneling microscopy (STM) is a leading tool for probing electronic and topographic information at the atomic scale [2]. Since its inception a few decades ago, data quality has dramatically improved by focusing on mechanical stability, tip preparation and lower temperatures [3–5]. New possibilities have emerged and greatly extended the range of STM, including quasi-particle interference studies with density of states mapping [6–10], spin-polarized STM [11, 12], scanning Josephson spectroscopy [13–15] and ultra-low temperature operation [3, 16, 17].

The majority of these new techniques have been achieved by relatively subtle -yet challenging- changes in the measurement apparatus. Many rely on three main improvements made over the years e.g. increased stability, lower operating (and electron) temperatures [3–5] and improved electronics. However, the scope of physical properties that can be probed by STM has mainly improved by changes to the tip itself. For example people have introduced spin-polarized tips to conventional STM to make it sensitive to spin orientation at the atomic scale [11]. Although additions like these seems subtle from a hardware point of view, development of these techniques has taken years and it has resulted in a new branch of STM based research. The emergence of scanning Josephson spectroscopy follows along that same path; it utilizes a superconducting tip, often made by dipping it into a superconductor or picking up a flake of high- $T_c$  superconductor, to create a superconductor-insulator-superconductor junction and spatially map the superfluid density [13–15]. These two techniques exemplify to large extent the inventiveness of the STM community to probe new branches of physics at the atomic scale without large changes to the instrument itself by innovations at the tip.

New techniques such as pump probe STM [18], electron spin resonance STM [19] and scanning noise spectroscopy [20–24] change the instrument beyond just the tip. Here the microscope is typically equipped with special cables for low attenuation throughput of high frequency signals. In the case of scanning noise spectroscopy the authors implemented a cold MHz amplifier based on a LC resonant circuit only few tens of centimeters from the STM junction to probe shot noise at the atomic scale [20, 21]. It turns out the capacitance of the coax cable from the tip to the amplifier fundamentally limits the bandwidth that can be achieved and forces the circuitry close to the tip (the low temperatures also make a critical impact).

We not only observe a shift towards adding functionality to conventional STM, we also see the additions are often moved close to the tip. Furthermore, we notice a shift that moves our view from a simple tunnel junction towards either a highly tunable Josephson junction (in case of superconducting tip and sample) or an interesting impedance as a part of a larger circuit. More challenging and perhaps longer term visions for STM have emerged very recently and they draw on a closer link to the ever growing field of quantum computing/sensing. The first example is to exploit a Majorana bound state living on the end of a one-dimensional semiconducting nanowire for the (local) detection of odd-frequency superconductivity [25]. The second is a newly proposed technique to use a superconducting charge qubit coupled to a tip to resolve tiny temperature and resistivity changes with the high spatial resolution provided by STM [26].

Here we want to add experimental provess to visions like these and invite further ingenuity to the field. Therefore, we introduce a platform for bringing device-based functionality to STM, with the aim to utilize decades of progress in device engineering for the field of scanning probes. We replace the conventional electrochemically etched, pointy metal wire with an integrated metal tip on a silicon chip. This new platform, which we call smart tip, allows in principle to directly add additional capabilities to a STM tip, including novel spin-sensitivity, local heating, local magnetic fields, local gating, high-frequency compatible coplanar waveguides, qubits, and double-tips. However, it is *a priori* unclear whether a nanofabricated tip will function for STM measurements, as several challenges arise: the stability needs to be below the picometer scale, stringent requirements exist on the shape and sharpness of the freestanding tip, and contamination from fabrication residues need to be absent. In the first half of this thesis, we demonstrate the feasibility of nanofabricated tips and the novel smart tip platform. We first discuss our newly developed fabrication procedure and then experimentally show the functionality of these tips in standard STM measurements.

The challenge in realizing smart tips is to make devices that are fully compatible with conventional STM, yet allow for compatibility with standard nano- and microfabrication processes. Specifically we need: (i) a clear protrusion of the tip relative to the underlying chip, (ii) precise control of the tip shape, and (iii) reliable, reproducible fabrication recipes. To meet these requirements, we developed a new fabrication method using suspended silicon nitride (SiN) tips covered with gold to create on-chip STM smart tips.

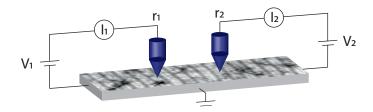

#### **DOUBLE-TIP STM**

A large part of this thesis describes our attempt to use the platform we introduced above to develop a double-tip STM that can be integrated in regular commercial STM systems. Double-tip STM, where two tips are brought into tunneling simultaneously to probe electron correlations within a few (tens of) nanometers, has been a long standing dream of scanning probe microscopy. However mostly due to the many technical challenges it has not gained much traction since its inception in the nineties of the last century. Much of the effort to the experimental realization of the double-tip STM has come from the multi-probe community that mostly focuses on studying resistance properties in mesoscopic systems on (sub)micrometer length scales by contacting the surface with two, three or, ideally, four probes. To large extent a double-tip STM with few nanometer probe separation operating in the tunneling regime is a natural goal to which their tools will evolve [27, 28].

Similar to conventional STM, multi-probe STM's are commercially available and mostly rely on four individually (piezo) driven STM and an additional scanning electron microscope (SEM) for navigation. Both do not benefit the mechanical stability that is so important to (spectroscopic imaging) STM and increase the complexity of the microscope significantly. However steady progress in stability [29] and control of the tips [30] has resulted in tip-to-tip distances down to 30 nm and the first double-tip transconductance (see Ch. 5) measurement to date [31].

In this thesis we start with a different approach that is aimed at overcoming some of the challenges double-tip STM faces. Our goal is to expand the use of our smart tip platform to create on-chip double-tip devices and directly implement them into a commercially available STM head. The most immediate challenge is the fabrication of the device and minimize the tip-to-tip distance. Given the joined nature of the tips we avoid part of the navigation problems and we thereby eliminate the use of an SEM column and

make them compatible with ultra-stable compact Pan type STM heads widely used for single tip experiments. Lastly we conclude with a discussion of the two main trade off that comes with our approach: reduced degrees of freedom and getting two fixed tips into tunneling requires tilt.

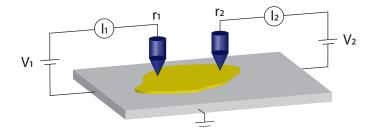

#### **STM** WITH A LOCAL GATE

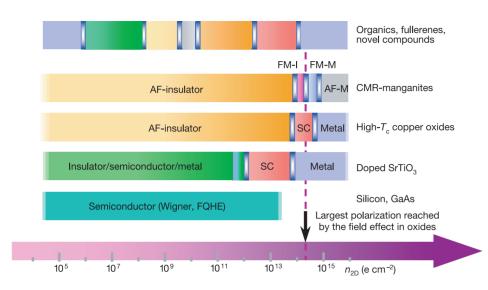

Interestingly, a new opportunity appears to use the double-tip devices for STM with a local gate also known as scanning gate spectroscopy [32]. The idea is conceptually straightforward, one probe acts as a normal STM tip while the other provides locally a strong electric field to induce or deplete carriers at the surface (under the adjoined tip). We are primarily interested in the application of such a technique on quantum materials such as (doped) Mott insulators or twisted bilayer graphene (TBLG). The concept of using scanning gate spectroscopy on quantum materials is appealing for two main reasons. First it will likely yield a more straightforward experiment compared to double-tip STM since we only need one tip in tunneling range. Second, simultaneous gating of quantum materials while studying the surface using STM proves challenging in some cases.

We will explore in detail the requirements and sample choices we need to make in Ch. 6. From the outset the obvious candidates will be materials with relatively low carrier density (at the surface) as a fully metallic surface will perfectly shield the electric field impose by the gating tip. Many low carrier materials such as Mott insulators at low doping, (twisted bilayer) graphene and (2D) semiconductors will be interesting to study. The latter two can in principle incorporate a bottom gate electrode as the are fabricated on a chip that contains contacts to the flake/thin film. Yet often obtaining a clean surface for STM after fabrication is challenging and may require annealing under ultra-high vacuum (UHV) conditions. Mott insulators (at low doping levels) can also be grown on insulating crystal substrates and contacted with lithographically defined top contacts but several problems arise. In-situ cleaving generally does not work for these samples and sample transfer from the growth chamber to the STM has not (yet) lead to overwhelming amount of new high quality data on these systems, despite efforts using UHV suitcases and the development of combined molecular beam epitaxy (MBE)/STM systems. Furthermore, the fabrication of a back gate on these crystalline materials proves difficult. The (thin) films generally grown using pulsed layer deposition (PLD) or MBE require meticulous matching of film and substrate lattices, especially for extremely thin films most suited for a back gate [33]. Ionic liquid based top gates have been successful in tuning the doping level to similar degree as chemically doped samples [34], but it is not always clear whether the gating is purely electrostatic or caused by oxygen displacement [34]. Also, ionic liquid gating is not suited for STM.

In short, we see that electrostatic (back) gating of Mott insulators proves difficult in combination with STM. Perhaps the most difficult would be the doped Mott insulator  $(Sr_{1-x}La_x)_2IrO_4$  that requires cleaving at low temperatures to obtain an unreconstructed, atomically flat and clean SrO terminated surface [35]. In this thesis we aim to briefly explore the possibility of local gating using our second tip with this material in mind. Beyond the difficulty of traditional gating on this material there are several other reasons that make it interesting. As a result of the insulating behavior at low chemical doping bending of the electron bands has already been observed and modeled using the dielectric character of the material [36]. From a physics point of view the iridates are proving very insightful in the understanding of the emergence of high- $T_c$  superconductivity in doped Mott insulators. They show remarkable resemblance to the well-studied cuprates while chemically very different, meaning that if superconductivity is found in the iridates it would be a consequence of the doped Mott state and not exclusive to copper oxide planes. To observe the potential superconductivity in  $(Sr_{1-x}La_x)_2IrO_4$  it requires a higher doping level that so far has been beyond the reach of crystal growers and therefore we are interested in exploring if our tip based gate can play a role here.

#### **THESIS OUTLINE**

In this thesis we present a new kind of tip for scanning tunneling microscopy by fully incorporating a metallic tip on a silicon chip using newly developed fabrication techniques and demonstrate its performance. We then explore the potential of additional functionality to the tip with the main focus on double-tips and its applications for studying quantum materials.

In Chapter 2 we describe in detail the challenges overcome to create the novel smart tips and the final fabrication process. The tips we create in this chapter are single tip devices without any additional features and where the full chip acts as a contact pad. These are the tips that we test in Chapter 4.

Chapter 3 is dedicated to the development of a new, homebuilt low temperature scanning tunneling microscope. Although the smart tips can by implemented in (existing) commercial systems, we built a dedicated microscope that is ideally suited for the implementation and testing of the new tips.

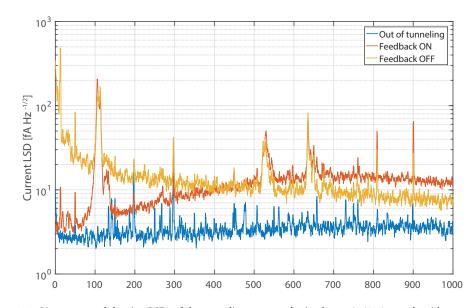

Chapter 4 consist of a series of proof of principle experiments to confirm that many of the building blocks are in place to create a fully functioning double-tip STM. First we demonstrate the performance of the smart tip in a commercial STM and test in-situ tip preparation methods. Second we test the homebuilt STM's performance by scanning on atomically flat Au(111) and analyzing the noise at the tunnel junction. Last we approach again a Au(111) surface with the double-tip devices we develop in Chapter 5, in an attempt to get good quality data using one of the two tips. This would be a big step towards a working STM with a local gate that we explore in Chapter 6.

In Chapter 5 we take an important step towards a fully functioning double-tip STM by extending the fabrication procedures of Chapter 2 to incorporate two probes separated by only few tens of nanometers. In addition we outline the challenges to get two fixed tips into tunneling simultaneously that still stand.

In Chapter 6 we propose and explore the possibility of using the double-tip devices for STM with a local gate. Here only one tip needs to be in tunneling and the other is used to locally induce or deplete charge carriers at the surface. This yields a more straightforward experiment and seems most suited for crystals that require in-situ cleaving and have low carrier densities.

Chapter 7 provides the main conclusions of this thesis together with an outlook on the potential future application of the smart tip platform for high frequency STM in the GHz regime. As a final note we argue that upscaling the fabrication to full waver processing should be straightforward and may help to push smart tips towards the mainstream.

#### REFERENCES

- M. Leeuwenhoek, R. A. Norte, K. M. Bastiaans, D. Cho, I. Battisti, Y. M. Blanter, S. Gröblacher, and M. P. Allan, *Nanofabricated tips for device-based scanning tunneling microscopy*, Nanotechnology **30**, 335702 (2019).

- [2] C. J. Chen, *Introduction to scanning tunneling microscopy* (Oxford University Press, 1993).

- [3] Y. J. Song, A. F. Otte, V. Shvarts, Z. Zhao, Y. Kuk, S. R. Blankenship, A. Band, F. M. Hess, and J. A. Stroscio, *Invited review article: A 10 mk scanning probe microscopy facility*, Rev. Sci. Instrum. 81, 121101 (2010).

- [4] S. Pan, E. W. Hudson, and J. Davis, <sup>3</sup>*He refrigerator based very low temperature scanning tunneling microscope*, Review of scientific instruments **70**, 1459 (1999).

- [5] I. Battisti, G. Verdoes, K. van Oosten, K. M. Bastiaans, and M. P. Allan, *Definition of design guidelines, construction, and performance of an ultra-stable scanning tunneling microscope for spectroscopic imaging, Review of Scientific Instruments* 89, 123705 (2018).

- [6] M. Crommie, C. Lutz, and D. Eigler, *Imaging standing waves in a two-dimensional electron gas*, Nature **363**, 524 (1993).

- [7] L. Petersen, P. Hofmann, E. Plummer, and F. Besenbacher, *Fourier transform-stm:* determining the surface fermi contour, J. Electron. Spectrosc. Relat. Phenom. 109, 97 (2000).

- [8] K. Fujita, M. Hamidian, I. Firmo, S. Mukhopadhyay, C. K. Kim, H. Eisaki, S.-I. Uchida, and J. C. Davis, *Spectroscopic imaging stm: Atomic-scale visualization of electronic structure and symmetry in underdoped cuprates*, in *Strongly Correlated Systems: Experimental Techniques*, edited by A. Avella and F. Mancini (Springer Berlin Heidelberg, Berlin, Heidelberg, 2015) pp. 73–109.

- [9] A. Yazdani, E. da Silva Neto, and P. Aynajian, *Spectroscopic imaging of strongly correlated electronic states*, Annu. Rev. Condens. Matter Phys. **7** (2016).

- [10] Ø. Fischer, M. Kugler, I. Maggio-Aprile, C. Berthod, and C. Renner, *Scanning tun-neling spectroscopy of high-temperature superconductors*, Rev. Mod. Phys. **79**, 353 (2007).

- [11] R. Wiesendanger, Spin mapping at the nanoscale and atomic scale, Rev. Mod. Phys. 81, 1495 (2009).

- [12] M. Bode, Spin-polarized scanning tunnelling microscopy, Rep. Prog. Phys. 66, 523 (2003).

- [13] M. T. Randeria, B. E. Feldman, I. K. Drozdov, and A. Yazdani, *Scanning josephson spectroscopy on the atomic scale*, Physical Review B **93**, 161115 (2016).

- [14] M. Hamidian, S. Edkins, S. H. Joo, A. Kostin, H. Eisaki, S. Uchida, M. Lawler, E.-A. Kim, A. Mackenzie, K. Fujita, *et al.*, *Detection of a cooper-pair density wave in Bi*<sub>2</sub>*Sr*<sub>2</sub>*CaCu*<sub>2</sub>*O*<sub>8+r</sub>, Nature **532**, 343 (2016).

- [15] D. Cho, K. M. Bastiaans, D. Chatzopoulos, and G. D. Gu, A strongly inhomogeneous superfluid in an iron-based superconductor, Nature, 541–545 (2019).

- [16] M. Assig, M. Etzkorn, A. Enders, W. Stiepany, C. R. Ast, and K. Kern, A 10 mk scanning tunneling microscope operating in ultra high vacuum and high magnetic fields, Rev. Sci. Instrum. 84, 033903 (2013).

- [17] H. Von Allwörden, A. Eich, E. J. Knol, J. Hermenau, A. Sonntag, J. W. Gerritsen, D. Wegner, and A. A. Khajetoorians, *Design and performance of an ultra-high vacuum spin-polarized scanning tunneling microscope operating at 30 mK and in a vector magnetic field*, Rev. Sci. Instrum. 89, 1 (2018).

- [18] S. Loth, M. Etzkorn, C. P. Lutz, D. Eigler, and A. J. Heinrich, *Measurement of fast electron spin relaxation times with atomic resolution*, Science **329**, 1628 (2010).

- [19] S. Baumann, W. Paul, T. Choi, C. P. Lutz, A. Ardavan, and A. J. Heinrich, *Electron* paramagnetic resonance of individual atoms on a surface, Science **350**, 417 (2015).

- [20] K. Bastiaans, T. Benschop, D. Chatzopoulos, D. Cho, Q. Dong, Y. Jin, and M. Allan, *Amplifier for scanning tunneling microscopy at mhz frequencies*, Review of Scientific Instruments 89, 093709 (2018).

- [21] F. Massee, Q. Dong, A. Cavanna, Y. Jin, and M. Aprili, *Atomic scale shot-noise using cryogenic mhz circuitry*, Review of Scientific Instruments **89**, 093708 (2018).

- [22] K. Bastiaans, D. Cho, T. Benschop, I. Battisti, Y. Huang, M. Golden, Q. Dong, Y. Jin, J. Zaanen, and M. Allan, *Charge trapping and super-poissonian noise centres in a cuprate superconductor*, Nature Physics 14, 1183 (2018).

- [23] U. Kemiktarak, T. Ndukum, K. Schwab, and K. Ekinci, *Radio-frequency scanning tunnelling microscopy*, Nature **450**, 85 (2007).

- [24] K. Bastiaans, D. Cho, D. Chatzopoulos, M. Leeuwenhoek, C. Koks, and M. Allan, *Imaging doubled shot noise in a josephson scanning tunneling microscope*, Physical Review B 100, 104506 (2019).

- [25] O. Kashuba, B. Sothmann, P. Burset, and B. Trauzettel, *Majorana stm as a perfect detector of odd-frequency superconductivity*, Physical Review B **95**, 174516 (2017).

- [26] B. Jäck, Visualizing dissipative transport dynamics at the nano-scale with superconducting charge qubit microscopy, (2019), arXiv:1910.03583 [cond-mat.mes-hall].

- [27] S. Hasegawa, *Roadmap of scanning probe microscopy*, (Springer Berlin Heidelberg, 2007) Chap. 12.

- [28] S. Hasegawa, Multi-probe scanning tunneling microscopy, in Scanning Probe Microscopy: Electrical and Electromechanical Phenomena at the Nanoscale, edited by S. Kalinin and A. Gruverman (Springer New York, New York, NY, 2007) pp. 480–505.

- [29] J. Yang, D. Sordes, M. Kolmer, D. Martrou, and C. Joachim, *Imaging, single atom contact and single atom manipulations at low temperature using the new scien-taomicron lt-uhv-4 stm*, The European Physical Journal Applied Physics 73, 10702 (2016).

- [30] M. Kolmer, P. Olszowski, R. Zuzak, S. Godlewski, C. Joachim, and M. Szymonski, *Two-probe STM experiments at the atomic level*, Journal of Physics: Condensed Matter **29**, 444004 (2017).

- [31] M. Kolmer, P. Brandimarte, J. Lis, R. Zuzak, S. Godlewski, H. Kawai, A. Garcia-Lekue, N. Lorente, T. Frederiksen, C. Joachim, et al., Electronic transport in planar atomicscale structures measured by two-probe scanning tunneling spectroscopy, Nature communications 10, 1573 (2019).

- [32] L. Gurevich, L. Canali, and L. P. Kouwenhoven, *Scanning gate spectroscopy on nan*oclusters, Appl. Phys. Lett. **76**, 384 (2000).

- [33] G. Dubuis, Y. Yacoby, H. Zhou, X. He, A. T. Bollinger, D. Pavuna, R. Pindak, and I. Bozovic, Oxygen displacement in cuprates under ionic liquid field-effect gating, Scientific reports 6, 32378 (2016).

- [34] A. T. Bollinger, G. Dubuis, J. Yoon, D. Pavuna, J. Misewich, and I. Božović, Superconductor-insulator transition in  $La_{2-x}Sr_xCuO_4$  at the pair quantum resistance, Nature 472, 458 (2011).

- [35] I. Battisti, K. M. Bastiaans, V. Fedoseev, A. De La Torre, N. Iliopoulos, A. Tamai, E. C. Hunter, R. S. Perry, J. Zaanen, F. Baumberger, et al., Universality of pseudogap and emergent order in lightly doped mott insulators, Nature Physics 13, 21 (2017).

- [36] I. Battisti, V. Fedoseev, K. M. Bastiaans, A. De La Torre, R. S. Perry, F. Baumberger, and M. P. Allan, *Poor electronic screening in lightly doped mott insulators observed with scanning tunneling microscopy*, Physical Review B **95**, 235141 (2017).

# 2

۱\_

1

### **FABRICATION OF SMART TIPS**

Parts of this chapter have been published in Nanotechnology **30(33)**, 335702 (2019) [1].

#### **2.1. INTRODUCTION**

In order to introduce our platform for bringing device-based functionality to STM, we aim to use modern nano- and microfabrication techniques presented here to replace the conventional electrochemically etched, pointy metal wire with an integrated metal tip on a silicon chip. This new platform, which we call smart tip, allows in principle to directly add additional capabilities to a STM tip, most of which we briefly mentioned in the previous chapter.

As stated before, the main challenge in realizing smart tips is to make devices that are fully compatible with conventional STM, yet allow for compatibility with standard nano- and microfabrication processes. Specifically we need: (i) a clear protrusion of the tip relative to the underlying chip, (ii) precise control of the tip shape, and (iii) reliable, reproducible fabrication recipes. To meet these requirements, we developed several fabrication methods each with their own advantages and limitations. Over the course of this chapter we learn about the challenges and, with each new fabrication method, we improve and often simplify our process to finally arrive at the devices we test in Ch. 4.

The first and perhaps most intuitive method (Sec. 2.2.1) is based on the cleaving of a silicon chip to create a pointy chip where the tip overhangs at the apex of the chip. In Sec. 2.2.2 we look at tips made out of tungsten that are brought to and over the edge of the chip by using a through wafer silicon etching process called a Bosch etch. Finally we describe a newly developed fabrication method using suspended silicon nitride (SiN) tips covered with gold to create the on-chip STM smart tips in Sec. 2.3. They prove to be both flexible and fast to make. These are the tips that we present in Sec. 2.3.6 and extensively test in Ch. 4.

#### **2.2.** TOWARDS ON-CHIP STM TIPS

We aim to create a silicon chip that carries a protruding metal tip. Not only does the tip need to be very sharp to make it capable of resolving atoms, we also want to avoid accidental touches of the chip to the sample. Therefore we like to control the shape of the chip as well; ideally we create a pointy chip with the tip overhanging the apex of the chip. There are numerous ways to create a pointy chip, several will be discussed in this chapter.

#### **2.2.1. CLEAVED TIPS**

The most elementary approach is to use the crystal structure of the silicon to our advantage. By simply cleaving the Si along a crystal axis we should be able to create a very well defined and clean break, leaving smooth sidewalls. This technique is often used to (i) break pieces too large to dice or that leave toxic residue such as iii-v materials, (ii) create sidewalls smooth enough to act as mirrors facets in diode lasers [2], (iii) create flat and clean surfaces for scanning probe microscopy when cleaved in ultra-high vacuum [3].

In fact, two examples utilizing cleaved chips to create chip based STM tips have been recently been reported. The first example is a InAs nanowire glued onto the corner of a chip. The chip used there is a square piece of cleaved GaAs [4, 5]. In the second example the authors used a cleaved glass chip coated with a metal layer. The pointy edge of the chip where the two cleave lines meet is so sharp that chip itself can even be used to

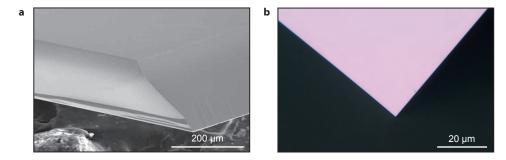

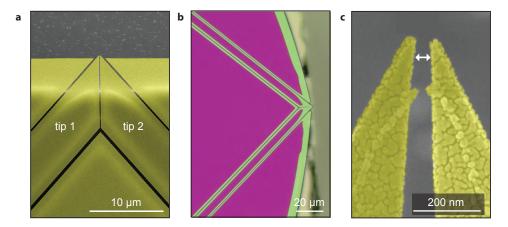

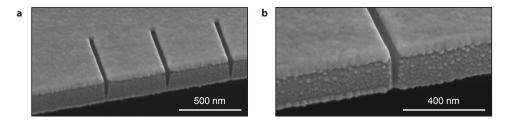

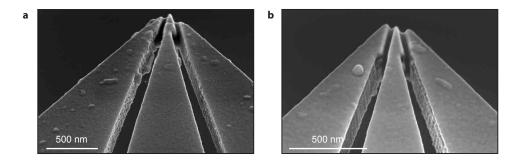

Figure 2.1: **a** SEM image of a cleaved Si(100) chip. The two cleaved planes meet in the center of the image. **b** Top view optical image of a similarly cleaved Si(100) chip.

successfully perform the STM measurements [6].

Fig. 2.1 shows two examples of a cleaved Si(100) chips where cleave lines along [110] and the orthogonal  $[1\overline{10}]$  axes meet in a point. We cleave the chips by making a small scratch with a diamond cutter on the edge of the chip, holding sharp pair of metal tweezers under the scratch and pressing down with different set of soft tip tweezers on either sides of the chip, such that the cleave line travels through the material along the crystal axis and we do not get residue from the scratch on the center of the chip. From the top the cleave lines look very straight and the apex of the chip very sharp. The inclined view from in the SEM image shows that the cleavage planes can have varying slopes indicative of competing (111) and (110) planes as natural cleavage planes [7].

The chips shown in Fig. 2.1 are promising, they show that one can create a sharp apex of the chip, but whether the top or bottom of the chip has the foremost apex remains unpredictable. This can clearly been seen in Fig. 2.1a. In addition, for future fuctionalization of the tips we require full control over the tip shape and we aim to achieve that by including electron beam lithography to define our tips. The tip we define needs to be exactly aligned with the apex of the chip and protrude from there. This turns out the be the major complication of cleaving (by hand) independent of the chosen material. The alignment accuracy that needs to be  $\sim 10 \ \mu m$  is even challenging to achieve with a dedicated tool, where the cleave line is aligned using a sufficiently powerful microscope and precision stage [8].

In summary, although using cleaving to create the appropriate chip shape seems clean and simple, it lacks reproducibility and accuracy without a dedicated and capable tool that is not available here.

#### **2.2.2. DEEP ETCHED SMART TIPS**

#### **INTRODUCTION TO BOSCH ETCH**

Given the limitations of cleaving we proceed to explore the use of Deep Reactive Ion Etching (DRIE). DRIE is a highly anisotropic plasma etch that can create deep etches in silicon at a high etch rate and with excellent directionality [9]. The latter makes is very well suited for high aspect ratio structures and it has to ability to create very straight sidewalls. The high etch rate of typically 5  $\mu$ m/min allows through wafer etches within

reasonable time. Here we use it to cut out the chip we define by a mask layer on top. The main benefits are the straight, smooth sidewalls, the ability to cut out many chips at once with great precision and (therefore) reproducibility.

The type of DRIE we perform here is also called Bosch process or Bosch etch and it usually performed without any cryogenic cooling but rather between  $T=-10^{\circ}C$  and  $T=20^{\circ}C$ . The Bosch etch creates the anisotropy by a alternating between plasma pulses based on two gasses. The first pulse, the longer one, chemically etches the silicon at a high rate using a plasma formed from SF<sub>6</sub> gas. The etcher used here is inductively coupled meaning that the plasma is formed by a coil around the main chamber that creates an oscillating magnetic field that induces an electric field to circulate the plasma. The inductively coupled plasma (ICP) power used to create the ions for the chemical etching mostly sets the number available ions. The two capacitor plates used in traditional Reactive Ion Etching (RIE), that is often used by itself to create a plasma using an oscillating electric field between the plates, are primarily used to control the momentum of the ions that is important for mechanical etching, this is set by the DC bias [10].

The second pulse deposits a passivation layer. For this shorter pulse the  $SF_6$  gas is replaced by  $C_4F_8$ . The plasma now isotropically deposits a protective layer on both the etched silicon and the mask. The physical bombardment of the accelerated ions, the mechanical etching, is very directional and removes the passivation layer only in the bottom of the trench created before. The newly exposed silicon is then chemically etched again by the next  $SF_6$  step. Upon repetition this creates very deep, straight etches. Balancing the etch step and the passivation step is of crucial importance to the profile of the etch and the etch rate of the mask [9].

In this section we will present fabrication schemes, each with their own advantages and disadvantages, all using DRIE to cut out the chip. The first is an initial attempt to create a metallized overhanging structure without the use of electron beam lithography to define the tip shape: the sharpness is merely determined by the thickness of the film in combination with the sharpness of the chip shape that follows the DRIE mask layer. In the second scheme, developed in parallel with the first, we do incorporate EBL to create a sharp metal tip and subsequently try to suspend it.

#### **PLANAR TUNGSTEN TIPS**

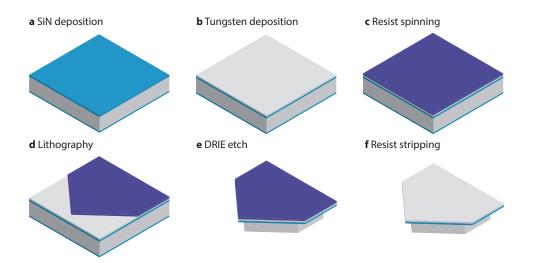

The most important part of the fabrication process at this stage is the creation of overhang. To start off simple and properly test the DRIE process we first proceed with the fabrication of a planar tip made out of tungsten covered SiN and plain tungsten respectively. Planar means the tip consists of a sheet of material that overhangs and its sharpness, as seen from top, is determined by the shape of the chip as shown in Fig. 2.2.

We start with a 200  $\mu$ m thick Si(100) chip covered on both side with 194 nm high stress LPCVD SiN (Fig. 2.2a). Here we choose to deposit a tungsten film, because it is traditionally often used for STM tips and more importantly it can be etched by SF<sub>6</sub> gas that is also used for etching through the chip. We deposit the tungsten layer by RF sputtering at 150W in an Alliance AC450 for 90 s to obtain a film thickness of 50 nm (Fig. 2.2b). We define the shape of the chip using optical lithography for which we first spincoat a 6  $\mu$ m thick layer of AZ9260 photoresist (we spin at 5500 RPM and bake at 110°C for 230 s), see Fig. 2.2c. This may seem very thick but the etch needs to be long in order to go through the full 200  $\mu$ m thick chip.

Figure 2.2: Overview of fabrication steps for the planar SiN supported W tips. Note: The bottom layer of SiN is omitted starting at (e), the layer is still there, however after the Si etch any protruding SiN at the bottom is removed by (the removal of) the adhesive oil applied before the etch.

For the exposure we use a DMO ML-2 laser writer, which uses a scanning laser with a wavelength of 375 nm instead of an UV lamp in combination with a mask. The maskless process allows us to change the design rapidly without having to order/produce a mask for every iteration. The laser beam is 1  $\mu$ m wide and takes 1  $\mu$ m steps with a dose of 600 mJ/cm<sup>2</sup>. The development typically takes place is a 1:3.5 mixture of AZ400K:H2O for 3 min and is stopped by immersion in water for 60 s.

The chip we aim to cut out is now covered by photoresist and the area around it consists of exposed tungsten on top of SiN (Fig. 2.2d). Here we use the DRIE to etch through all layers in a single etch (Fig. 2.2e). The tungsten is only 50 nm thick and etched well by SF<sub>6</sub> plasma [11]. Etching the SiN will be less efficient, but works [11]. We start by placing the chip on a silicon carrier wafer with a drop of oil under the chip for thermal anchoring. The 4 inch carrier wafer is required to load chips into the etcher. To prevent the carrier wafer from being etched they are coated with 4.3  $\mu$ m SiO<sub>2</sub>, dramatically extending their lifetime due to the low etch rate of SiO<sub>2</sub>. The etch itself consists of a 40-45 min sequence of alternating pulses, a 7 s SF<sub>6</sub> etch (flow 200 sccm, source power 2000 W, DC bias 60 W) followed by a 2 s C<sub>4</sub>F<sub>8</sub> passivation step (flow 100 sccm, others the same), all at T=10°C. In addition to etching straight down through the chip, the DRIE also creates an overhang of the SiN/W planes of 1  $\mu$ m with these settings (Fig. 2.2e).

The last step before we obtain the final device is resist removal (Fig. 2.2e). Submerging the chips in heated acetone at  $45^{\circ}$ C for 30 min does not seem to completely remove the resist layer, but rather leave thin sheets of residual resist on the chip. Prolonged exposure to N–Methyl–2-pyrrolidone (NMP) at 80°C for 60 min does fully remove the resist layer in the majority cases, but cleanliness remains a concern. To wash of the NMP and dry the chips when we take them out we dip them twice in IPA and blow dry them with

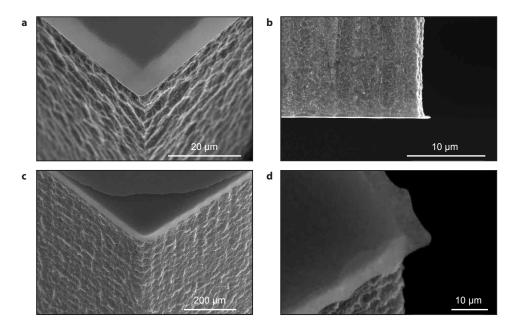

Figure 2.3: SEM images of the SiN supported W planar tips. **a** The apex of a successfully fabricated tip where the light gray parts are the overhanging SiN/W. The overhang measures 6.5  $\mu$ m perpendicular to the side of the chip. **b** Side view of a suspended device to show the straight silicon sidewall and the overhang created by the Bosch process. **c** Similar to (a) but here the tungsten has retracted while the SiN seems unaffected. **d** Planar tungsten tip made by almost identical fabrication process but without the layer of SiN under the tungsten.

#### N2 gas.

Fig. 2.3 shows examples of the resulting devices. In Fig. 2.3 a we show the device we set out to create: clear overhang of the SiN/W plane and nicely etched Si sidewalls, further demonstrated in Fig. 2.3b. Note that the sharpness of the plane and its waving sides (Fig. 2.3d) are a result of the profile created by the lithography. However using (nearly) identical process we also obtained devices where tungsten layer seems to be removed in the last ~8  $\mu$ m from the apex as shown in Fig. 2.3c. At first hand the most likely explanation is the lack of resist at the very end of the process, but the resist layer is 6  $\mu$ m thick, whereas a typical Bosch etch requires ~ 4  $\mu$ m. We present another interesting observation in Fig. 2.3d, where we use an almost identical fabrication process but starting with a bare Si chip without any SiN. Again the overhang is created by the Bosch etch using SF<sub>6</sub> gas, indicating that the SiN plane is not per se necessary to protect the tungsten and that the Bosch etch has difficulty etching through the SiN layer and affects the W laterally. If that is indeed what happens we could use a succession of dedicated etches: an SF<sub>6</sub> based W etch, an CF<sub>3</sub> based SiN etch and lastly the Bosch etch.

In conclusion, we have seen that planar W tips can in principle create workable devices, but come with complications: (i) even though their planar nature makes them intrinsically (somewhat) sharp, we do not have control over the tip shape at the nanoscale, (ii) extending to device based STM will require additional steps that we show in Sec. 2.2.2 and, (iii) proper removal of the resist, attacked by the long etch, appears hard and that raises concerns about the cleanliness of the tips.

#### SIN SUPPORTED TUNGSTEN TIPS

In order to move towards device based STM tips that include more complicated patterns such as two tips or on-chip circuitry, we strive for the ability to lithographically define the tips. To achieve this at the such a small length scale we use electron beam lithography to define the metal tips and contact pads. The fabrication is an extension of Sec. 2.2.2, where we replace the deposition of tungsten on the full chip (Fig. 2.2b) by a contact pad and an increasingly narrow line that will become the tip as shown in Fig 2.4.

The metal tips are created by a liftoff process where we spin on a layer of ARP-6200.09 resist (baked at T=150°C for 3 min), write the structures with an electron beam (the spot size is 29 nm, beam step size 2.5 nm and the dose 320  $\mu C/cm^2$ ), deposit the tungsten and lift off the non-exposed parts by dissolving the resist in NMP at T=80°C for over 60 min while stirring. Next we will proceed to create the final chip shape, again following (Fig. 2.2). Only this time we need to carefully align the chip mask to the tungsten tip

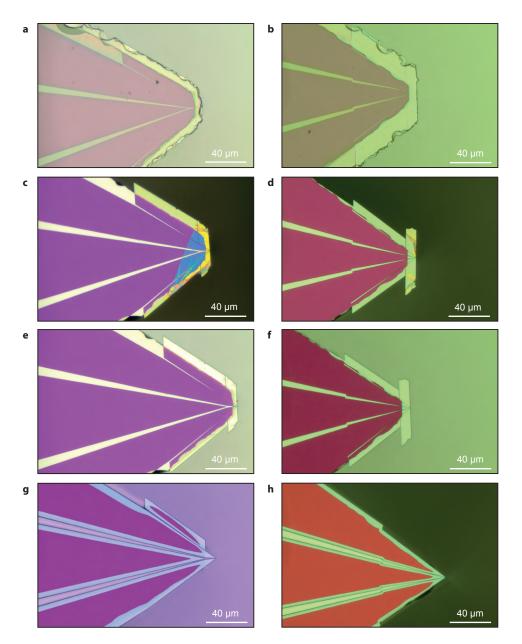

Figure 2.4: **a** Optical microscope (dark field) image of a mask alignment test on several closely packed lines etched into SiN. Although the mask is centered quite well on the lines, a slight tilt is still clearly present. **b** SEM image of a lithographically defined tungsten tip supported by a SiN sheet. The overhanging SiN sheet is almost transparent and the tungsten line is gray. Notice the alignment is off by about a micron. **c** Top view SEM image of a device similar to (a), but here the Bosch etch damaged the silicon, SiN and tungsten along the edges of the tungsten structure. (d) SEM image perpendicular to the tip shown in (c) clearly shows the damaged SiN and the etch extending into the silicon as well.

to ensure the tip is at the apex of the chip. The laser writer has the ability to align to markers using either and optical microscope (magnification of 40 x plus 4x digital zoom) or a laser microscope (magnification of approx. 200x), however it proves difficult to align with a precision smaller than 2  $\mu$ m. It can also occur that the rotation is not corrected for properly like in Fig. 2.4a. Therefore the tips do not always align perfectly to the apex of the overhanging SiN sheet but slightly next to it, e.g. in Fig. 2.4a,b,c.

Fig. 2.4b shows a somewhat successful device where the tungsten tip does extend all the way to the edge of the chip, albeit the alignment is still slightly off. In case it is successful the metal tip can be the foremost point that provides the tunneling, to be sure it is we will place the tip under a small angle, but more on that in Ch. 3. If necessary a short dip in a HF solution can help to make the tungsten protrude by etching the SiN. Note that this way the overhang of can never be more that the thickness of the SiN and thinning down the SiN may create additional complications such as bending or reduced stability. In some cases the metal does not fully extend to the edge of the SiN sheet and is outside of the <200 nm range where we can retract the SiN with HF. Here again the tungsten near the edge is slightly etched.

Another complication is shown in Fig. 2.4c,d. We notice that along the sides of the tungsten line the tungsten, SiN and underlying silicon are etched. This comes as a surprise since the tungsten, a material that can be etched by the  $SF_6$  plasma, is protected by the resist on top and the SiN on the bottom. Even if the  $SF_6$  makes it through from the side it should barely etch SiN like we observe here due to the lack of mechanical etching. While the origin of this behavior remains mysterious we made the following observations: (i) we tested several tungsten widths and narrower lines are more affected, (ii) it may well be connected with the withdrawal of tungsten in Sec. 2.2.2 and (iii) it occurs frequently.

In conclusion, using lithographically defined tungsten tips that are supported by a SiN plane yields very mixed results and comes with challenges that seem hard (but not impossible) to overcome and of which the nature is, at this moment, not always clear. Implementing a dedicated SiN etch instead of a Bosch etch through all layers may drastically improve the yield of the process in the future. However in the next section we move to a more simple fabrication scheme where we shape the SiN and put the metal on the chips at the very last, thereby avoiding the problems that occurred here.

#### **2.3. FABRICATION OF SIN BASED SMART TIPS**

#### **2.3.1. OVERVIEW**

Reading through the previous sections it becomes apparent that the two methods described each have their limitations. While the use of cleaving is fast, clean and elegant, it is very difficult to align the sharp apex of the chip to where the tip structure is defined. In addition, to get the chip in the exact shape needed and not only following the crystal structure of the material, one would need additional dicing step to further shape the chip to easily fit in the STM (depending on the tip holder design).

In this work we aim to make these tips a platform for potential applications and therefore we want to be able to lithographically define a variety of tip shapes and bring them to and over the edge of the chip. The Bosch etch method, where we etch through

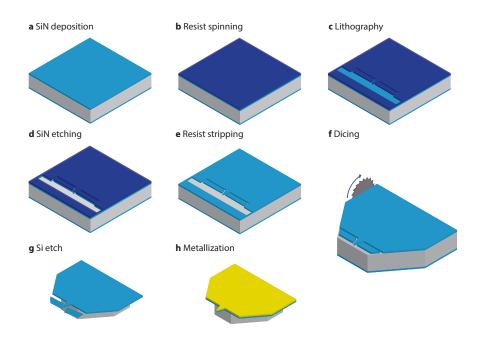

Figure 2.5: Overview of fabrication steps for STM smart tips. Note: 1) resist layer to protect the chip during dicing is not displayed for visual clarity. It is applied after (e) and removed before (g). 2) The bottom layer of SiN is omitted starting at (g), the layer is still there, however after the Si etch any protruding SiN at the bottom is removed by the adhesive oil applied during the etch.

the full wafer, can be aligned to the pre-patterned tip shape fairly well, but in the creation of the overhang the tungsten tips seem to be attacked. In this section we will present our final fabrication method to create smart tips with a single tip that utilizes SiN to greater extent.

Using SiN as a base for our suspended STM tips has a number of key advantages. First, it has a large selectivity to the Si etch we use to suspend the tip, allowing for clear protrusion. Making the tips solely out of metal without underlying SiN would also limit the choice of metal to those compatible with the etch described below. Second, it has a high mechanical stiffness, yielding robust tips that are resistant to tip treatment, as discussed later. Finally, it allows for a process where the metallic layer is added as a last step. This allows us to avoid any contamination by chemicals such as etchants and resists.

#### 2.3.2. PATTERNING SIN TIP

Our process starts with a 500  $\mu$ m thick Si(100) chip covered on both sides with a 200 nm thick layer of high stress low-pressure chemical vapor deposition (LPCVD) silicon nitride (SiN) (Fig. 2.5a). A 550nm thick layer of ARP-6200.13 resist on the top side is patterned using electron beam lithography (Raith EBPG5200, 100 kV, dose 370  $\mu$ C/cm<sup>2</sup>, spotsize

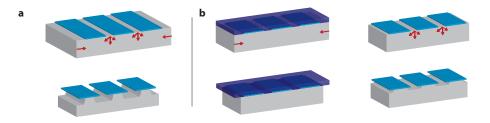

23 nm, beam step size 2.5 nm). After exposure to the electron beam, we develop the chip in Pentyl Acetate (1 min) and MIBK:IPA 1:1 (1 min) followed by an IPA rinse (1 min), see (Fig. 2.5b,c). The pattern, consisting of the tip shape and two shields, is transferred into the SiN layer using a CHF<sub>3</sub> etch for 5 min at 20°C (Fig. 2.5d). The shields are slabs of SiN on both sides of the tip, which we include to minimize the undercut of the Si once the overhang is created: the 50 nm lines around the shields reduce the etch rate of the Si etch significantly compared to a large exposed region without shields. We then clean the chip by two successive 1 min immersions into N-N-Dimethylformamide (DMF) followed by a boiling piranha solution at 135°C to remove all traces of resist and other organic contamination.

#### 2.3.3. **DICING**

In order to bring the tip close to the edge we will proceed with dicing the chip (Fig. 2.5f). There are two main reasons to choose dicing over a Bosch etch, where we can cut out multiple chips at once: it allows us to easily vary the shape for each new iteration until we find settle on a final design and a Bosch etch requires a soft or hard mask and an additional etch step, both can be time consuming and introduces additional challenges. For the latter, in case of a soft mask, the removal of the thick and heat affected resist can yield inconsistent results as we have seen in Sec 2.2.2.

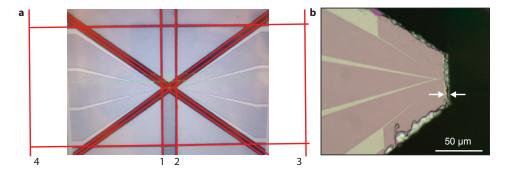

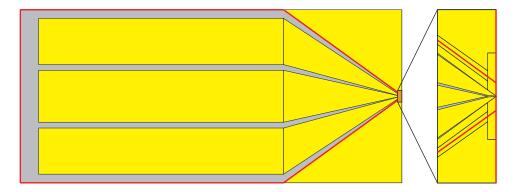

Before we dice the chip we first protect it against any residual debris from the dicing process by applying a new layer of photoresist. Out of a typical 10x10 mm<sup>2</sup> chip we cut out two smart tips adjacent to each other, as shown in Fig. 2.6a, to ensure the small features of the tip are in the center of the chip so ensure optimal resist conditions for the EBL. For the dicing we use a Disco dicer DAD 3220 where we stick the chip on a dedicated, 140  $\mu$ m thick sticky sheet. The dicing shares a lot of the requirements we also set for the Bosch etch: (i) smooth sidewalls, such that the overhanging tip will be the

Figure 2.6: **a** Screen capture of a chip after dicing as seen through the microscope of the dicer. For illustrative purposes the image is taken on low magnification, the alignment of the blade is done at high magnification. The black areas are diced, the red lines indicate the sequence of individual cuts as indicated by the numbers. The chip is bigger than the field of view, but the final shape of the chip follows the (red) dice lines. **b** Optical microscope image of a chip after dicing. The silicon (gray) left after the dicing extends up to 6  $\mu$ m beyond the SiN (pink). Note that the chips has a different lithographic pattern than described in this section, however the principle and the front shields are the same.

most protruded feature, (ii) minimal chipping of the Si and, (iii) alignment accuracy.

The first we obtain by choosing the optimal blade but we also make sure we dice at least 50  $\mu$ m into the underlying tape. This prevents any roughness at the bottom of the chip. To find the optimal blade and settings we tested several different blades and speeds with which the blade moves forward and found that the ZH05-SD2000-N1-90 at 3 mm/s yields the best result in terms of chipping and sidewall smoothness. Residual roughness on the sidewall is further smoothed out by the isotropic Si etch described in the next section.

The second requirement is minimal chipping of the Si. Contrary to for example a Bosch etch, the blade can cause more roughness not only on the sidewalls, but also it can chip away small pieces of Si along the dice line near the top surface (Fig. 2.6). To align the dice consistently down to a few micron from the patterned tip, we need to minimize the amount of chipping. Our choice for the ZH05-SD2000-N1-90 blade at a feed speed of 3 mm/s makes a significant difference, but there is another trick that helps reduce the chipping: dressing the blade. By dicing through a block of very hard material (or dressing board) one can wear softer materials off the blade and thereby increase the exposure of the diamonds in the blade. This process makes the blade wear faster but reduces chipping. Typically we dress the blade before we dice each chip and perform the two critical dices (number 1 and 2 in Fig. 2.6a) first as the chipping worsens with each dice.

To align accurately to the patterned tips we need to calibrate the width of the blade accurately by a so called hairline adjustment. We perform a single dice on the outskirts of the same chip and with the settings that will be used for the actual dices and put the lines that indicate the width of the blade throughout the procedure on the width we get from the test line.

The full procedure works as follows. First we dress the blade, remove the dressing board and load our chip that sits on the sticky sheet into the dicer. We proceed to make a first cut and perform the hairline adjustment. Then, with a sequence of individually aligned dices as indicated in Fig. 2.6 we cut out the shape we need. Lines 1 and 2 are the ones close to the tips and are therefore the first after dressing. Lines 3 and 4 follow keeping the same alignment, that way we ensure that when the chip stands upright, the bottom is exactly parallel to the top where the tips protrudes. The cross lines 5-8 run through the shields typically around 20  $\mu$ m away from the tip on each side. Finally we dice lines 9 and 10 parallel to each other, these set the width of the chip to 3 mm. After completing all the lines we unload the tape holding the chip and dry it, expose it to UV light to reduce the stickiness of the tape, making it easier to remove the two tips. For tips longer than 10 mm or write two tips next to each other and dice the chips in two parts. Now we have two (smaller) chips each housing a single device.

#### 2.3.4. SUSPENDING SIN TIP

The residue created by the dicing process is washed away with the removal of the protective photoresist layer. After this cleaning step, we isotropically remove part of the Si substrate using a dry reactive-ion etch based on SF<sub>6</sub>. The etch is performed by a plasma of  $F^-$  ions formed inside an ICP etcher. Reactive ion etching is often a combination of chemical reactions, the  $F^-$  ions reacting with the Si, and ion bombardment, where the ions are accelerated by a DC bias into the sample hence removing material. Here, however, to prevent any anisotropy in the etch we do not put a DC bias except for a short ignition pulse < 1 s, resulting in an isotropic Si etch.

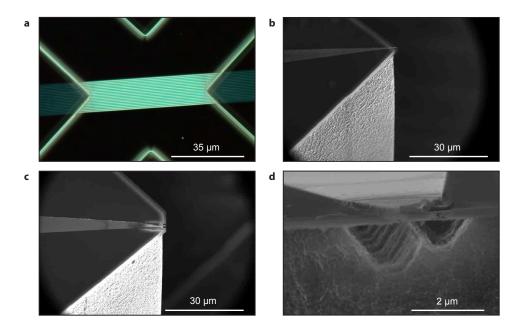

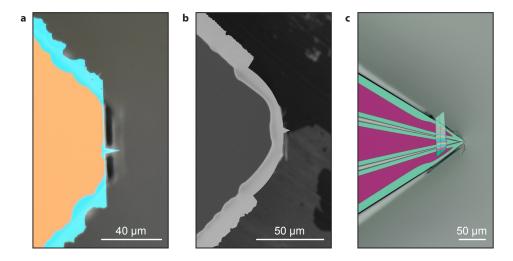

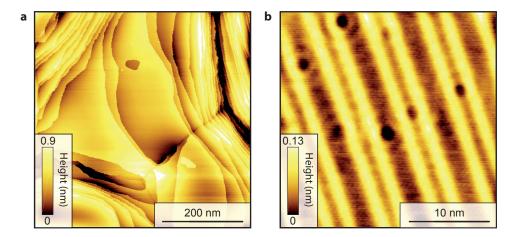

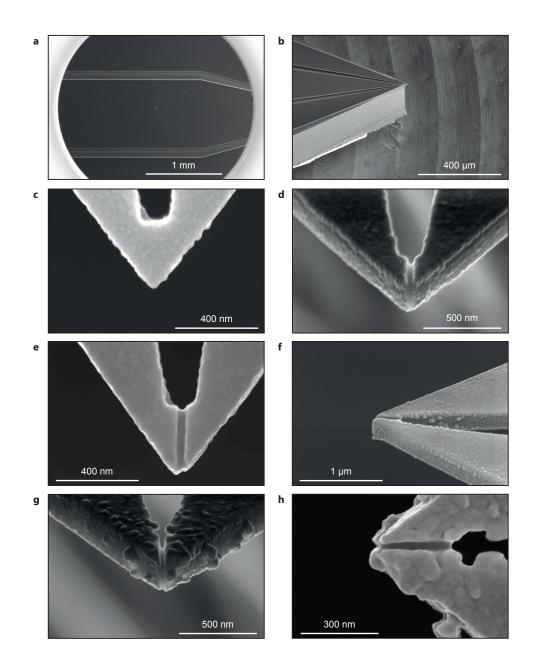

For improved selectivity of the SiN over the Si the chip is cooled to  $-50^{\circ}$ C. During a typical etch the thickness of the SiN reduces from 200 nm to ~120 nm. The exposed Si sidewalls are removed at a rate of around 4  $\mu$ m/min until both the tip and the two shields protrude by about 10–12  $\mu$ m, causing the shields (10  $\mu$ m) to fall off (Fig. 2.5g, 2.7). The straight sides next to the tip can be made very small or even rounded, as shown in Fig 2.7b to avoid accidental touches when aligning to a sample, this would not have been possible using an anisotropic KOH wet etch.

In approximately 20% of devices, one or both of the released shields lands on top of the chip (Fig. 2.7c). Spraying acetone followed by IPA in the appropriate direction often suffices to remove them, depending on the placement of the shield. For these single tip devices where the complete plane will be metallized to create a single contact, the shields do not cause any problems unless they protrude beyond the tip itself. Later in Sec. 5.3.2 we will see that the irregular release can be a result of resist residue being present in the trenches and can cause significant yield problems, here the latter is not the case.

#### **2.3.5. METALLIZATION**

The final step in fabricating the STM tip involves depositing a metal on the chip through sputtering to ensure proper coverage of both the top and the side of the SiN tip (Fig. 2.5h). Here, we choose to deposit 20 nm of gold (Leica ACE200) as the tip material; it is relatively

Figure 2.7: **a** Optical microscope image of a SiN tip after release off the shields where the orange part is still attached to the underlying silicon and the green parts is suspended. Notice that two shields next to the tip have reduced the overhang at the straight (right) side compared to top and bottom side. **b** SEM image of smart tip with a rounded profile around the tip. **c** Optical image of a smart tip containing multiple probes that demonstrates the improper release of the shield on top of the chip. Here the purple parts connect to the silicon and the green parts are suspended.

straightforward to use other interesting materials for the tip. The main boundary conditions for choosing materials are good adhesion to the SiN and compatible stress level in the film. In the next section we also show that we can use tungsten covered SiN tips, for these we typically sputter ~50 nm tungsten using a Alliance Concept AC450 (150 W RF power at  $2 \times 10^{-7}$  bar base pressure). Evaporation of the metal film is also possible and will be discussed in Sec. 5.3.1.

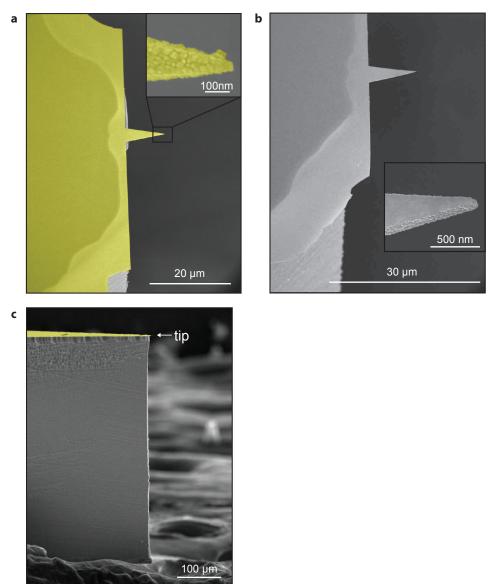

#### **2.3.6. SMART TIP DEVICES**

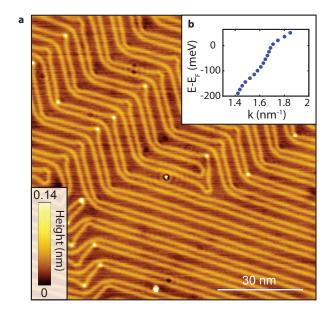

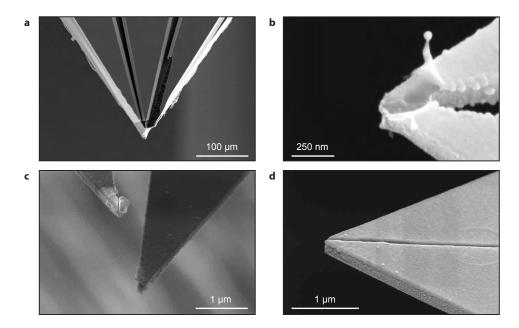

Images of a typical devices are shown in Fig. 2.8(a-c). The diameter of the apex of the tip depends on the initial thickness of the SiN, the electron beam spot size and dose, the SF<sub>6</sub> etch time and temperature, and the metal film thickness. However, as can be seen from Fig. 2.8(c), the tip diameter is mostly determined by the grain size of the metal film. Our tips achieve radii of a few (tens of) nanometers for the gold film, is comparable to specialized commercially available metal wire tips. The ("macroscopic") tip sharpness for the tungsten tips defined by the curvature of the foremost part of the film has a radius in the order of the film thickness of the tungsten. The tungsten film has however a fine grain structure which in practice determines the tip sharpness at the scale of the junction itself. Here, the stress in the film causes a slight upward bend in the overhanging tip. The severity of the effect depends on the geometry: the bending in a geometry like in Fig. 2.8 is below a micron. If the suspended tip does not connect to the surrounding plane very adiabatically but forms a narrow line the bending seems to increase. This could affect us once we start looking at other geometries in Ch. 4. The overall yield of the fabrication as described in this section is around 80%.

#### **2.4.** CONCLUSION

Throughout this chapter we have worked towards a smart tip fabrication method that is fast, (relatively) easy to implement and flexible such that it can act as a platform. The latter stipulates that we need control over the shape of the tip and we obtain this by incorporating electron beam lithography. Furthermore, to create the overhang of the tip with high yield we need the lithographically defined tips to be very close to the edge of the chip before we create the overhang. We discovered that, while able of making very sharp, pointy chips, cleaving chips does not suffice here because it lacks the above mentioned ability to align it accurately.

We conclude that the creation of the chip shape and (simultaneously) the overhang can be achieved using a Bosch etch through the full chip. We have shown this first with chips covered with LPCVD SiN and sputtered tungsten. Later we incorporated lithographically defined tungsten films to increase tip sharpness and to work towards adaptable designs. Although the etch itself shows great promise the optical resist based mask proved hard to remove and raises concerns about cleanliness of the tips (and chips). For the sharper tungsten tips supported by a plane of SiN we have encountered a more mysterious problem where the small structures that form the tip are somehow attacked by the etch despite being protected on top and bottom.

It may very well be that all the complication we mentioned above can be overcome with further optimizations, however, a simpler and intrinsically clean process became apparent. By creating the tips out of lithographically defined SiN, which is almost inert to the Si etch used here and which can be thoroughly cleaned using a wide variety of chemicals such as a piranha solution, we circumvent all the obstacles we encountered.

Figure 2.8: **a-c** SEM images of a smart tip from the top (a,b) and the side (c). **a** The freestanding tip made of Au (colored in yellow) covered SiN has a length of 10  $\mu$ m and a tip radius of approximately 20 nm. The light yellow area is suspended, while the dark yellow parts are still attached to the underlying Si. **b** Smart tip covered by W that shows finer grain size but slightly more bending. **c** Side profile of a smart tip.

Only at the very last we metallize the tip and thereby ensure its cleanness.

#### **REFERENCES**

- M. Leeuwenhoek, R. A. Norte, K. M. Bastiaans, D. Cho, I. Battisti, Y. M. Blanter, S. Gröblacher, and M. P. Allan, *Nanofabricated tips for device-based scanning tunneling microscopy*, Nanotechnology **30**, 335702 (2019).

- [2] R. K. Sink, *Cleaved-facet group-III nitride lasers*, Ph.D. thesis, University of California, Santa Barbara (2000).

- [3] J. Garleff, J. Ulloa, and P. Koenraad, Scanning probe microscopy in nanoscience and nanotechnology 2, edited by B. Bhushan (Springer Science & Business Media, 2010) Chap. 11.

- [4] K. Flöhr, K. Sladek, H. Yusuf Günel, M. Ion Lepsa, H. Hardtdegen, M. Liebmann, T. Schäpers, and M. Morgenstern, *Scanning tunneling microscopy with InAs nanowire tips*, Applied physics letters **101**, 243101 (2012).

- [5] K. Flöhr, M. Liebmann, K. Sladek, H. Y. Günel, R. Frielinghaus, F. Haas, C. Meyer, H. Hardtdegen, T. Schäpers, D. Grützmacher, *et al.*, *Manipulating InAs nanowires with submicrometer precision*, Review of scientific instruments 82, 113705 (2011).

- [6] T. Siahaan, O. Kurnosikov, B. Barcones, H. Swagten, and B. Koopmans, *Cleaved thinfilm probes for scanning tunneling microscopy*, Nanotechnology **27**, 03LT01 (2015).

- [7] J. Garleff, J. Ulloa, and P. Koenraad, Scanning probe microscopy in nanoscience and nanotechnology 2, edited by B. Bhushan (Springer Science & Business Media, 2010) Chap. 11.

- [8] Electron Microscopy Sciences, Cleaving and scribing systems and tools, (2019).

- [9] J. Yeom, Y. Wu, J. C. Selby, and M. A. Shannon, *Maximum achievable aspect ratio in deep reactive ion etching of silicon due to aspect ratio dependent transport and the microloading effect*, Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena 23, 2319 (2005).

- [10] M. D. Henry, *ICP etching of silicon for micro and nanoscale devices*, Ph.D. thesis, California Institute of Technology (2010).

- [11] K. R. Williams, K. Gupta, and M. Wasilik, *Etch rates for micromachining processing-part ii*, Journal of microelectromechanical systems 12, 761 (2003).

\_ I

\_ I

# **BALIZATION OF THE SMART TIP**

Ι\_\_

#### **3.1. INTRODUCTION**

In this chapter we describe the design and realization of a homebuilt, stable, low temperature scanning tunneling microscope that we built specifically but not exclusively for the new smart tip platform. Specifically, because the ability to house the smart tips instead of traditional wire tips comes with additional requirements concerning the tip holder and the wiring. Not exclusively, because we aim to build a versatile and low consumption STM where we can also use traditional tips, exchange tips easily, prepare a wide variety of samples, etc., while retaining excellent performance at low operational cost. Throughout this chapter we witness how this large variety of demands guides the design of the STM. While the STM described here is (mostly) designed and constructed in-house, it is more accurate to call it a hybrid where we combine commercially available parts to a full system that meets our requirements. This way, at the core, we mostly rely on proven parts made by specialized companies and we reduce the workload.

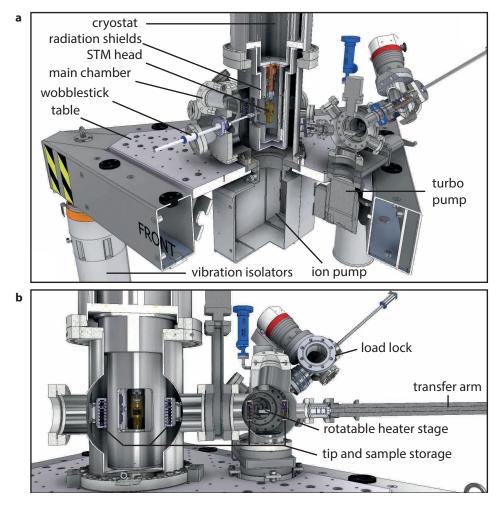

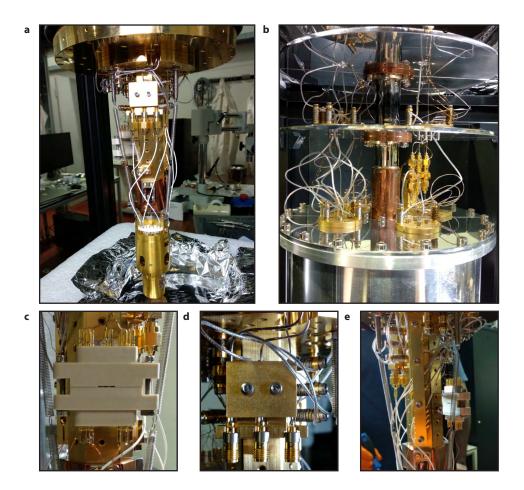

We start out with a short overview of the full system to present an overview of the overall design, what all components look like and where they are placed with respect to each other. Afterwards we land on the individual components. We motivate our choices, describe in detail how the parts work (together) and report on their abilities. First we focus on the heart of the system, the STM head, where tip and sample meet (Sec. 3.2). Many of the system's features are determined by the STM head and it has a large effect on the subsequent design choices. A good example is the top mounted cryostat we describe in Sec. 3.3 that we use to achieve a base temperature of 4.2 K. With both the cryostat and STM head in place we look at the wiring of the STM and how the wires are precooled by the cryostat in (Sec. 3.4). Afterwards in Sec. 3.5 and Sec. 3.6 we look at two other key specification, the ultra-high vacuum system and vibration isolation, respectively.

#### **3.1.1. OVERVIEW**

The main strength of scanning tunneling microscopy is the ability to visualize conducting materials with subatomic resolution. That in itself has led to a tremendous amount of structural information of many materials at the atomic scale. One can think of several examples such as lattices, lattice deformations, structural phase transition, but also atomic ensembles. The latter is particularly interesting since it shows that the position of atoms on surfaces can also be manipulated by the tip. All of this is a result of the exponential current-distance dependence of tunneling process between tip and sample and clever engineering. The first gives rise to the extreme sensitivity of the tunneling current to height changes. To resolve a so-called topography, a spatially resolved atomic height map, one needs to be able to approach the tip to within a nanometer (typical 0.5 nm) from the sample and scan it over the surface using a feedback circuit. The feedback between tip and sample can for example be used to keep the tip at a constant height throughout a scan to acquire a topograph.

STM is not just an advanced imaging technique for topography, it can also be used for spectroscopy. This is called Spectroscopic Imaging STM (SI-STM) or Scanning Tunneling Spectroscopy (STS). By measuring the differential conductance dI/dV we acquire information about the local density of states (LDOS) of the sample, given that the LDOS of the tip is constant in energy [1]. During such a measurement the feedback is switched off. The real strength lies in the acquisition of a spectroscopic map (a spectrum at each

Figure 3.1: Overview of the full smart tip microscope. The inside of the cryostat and the STM head are made visible by virtually cutting open the CAD render. The main parts are individually labelled. **a** Inclined view to show the majority of the vacuum system, the vibration isolation table and the STM head including its surrounding radiation shields. **b** Front view render of the main chamber, preparation chamber and load lock.

point in space, i.e. 256x256 pixels) that consist of  $10^4 \cdot 10^5$  spectra. These maps can provide a plethora of information about the electronic structure on the atomic scale. They typically take several days up to a week of continuous measurement with prolonged periods out of feedback demanding an extremely stable tip sample junction. The stability requirements are much more stringent than the ability to resolve atoms.

To prepare samples such as metal films, graphene based systems or other quantum materials such as cuprate high- $T_c$  superconductors we need ultra-high vacuum (UHV) with pressures down to  $10^{-10}$  mbar to prevent dirt from accumulating on the sample

surface. Most materials we want to study show interesting physics at low temperatures therefore we build the STM for operation down to 4.2 K. Low temperatures also helps the vacuum by condensing residual gasses to the cold surfaces, benefits the energy resolution of the spectra [1] and reduces drift in the piezo's.

#### **3.2. STM HEAD**

A key ingredient to low noise performance is a stable tip-sample junction. Therefore it is of great importance that the STM head, the construction containing the tip, the sample and everything that allows the scanning, is very rigid. Since the invention of STM by Binnig and Rorher in 1981 [2], several STM head designs have been developed. Two famous examples are the beetle type head and the Pan head pioneered by Besocke [3] and Pan et al. [4], respectively. The first is often adapted for multiprobe STM, where two or more metal wire tips can be individually manipulated. The latter has emerged as the preferred choice for spectroscopic imaging STM's due to its very rigid, compact and reliable design. Over the last two decades several innovations have lead to increasingly stable STM heads culminating in recent ultra-stable STM heads made primarily out of sapphire [5, 6].

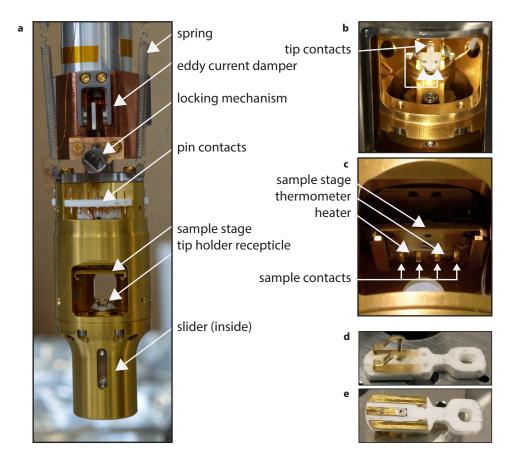

The nature of the smart tip platform allows us to simply replace the metal tip wire with a chip based tip. The study of quantum materials by spectroscopic imaging STM requires stability over multiple days often out of feedback, therefore we prefer a Pan type STM head among other reasons. The examples of sapphire based STM designs given above [5, 6] show best in class stability, but they do sacrifice flexibility: a smaller and shorter piezotube has a higher resonance frequency but a smaller scan range and incorporating an exchangeable tip holder may prove very difficult. Instead the tip is directly mounted into a small cone on the piezo tube. The reduced scan range is not a problem, but the absence of a tip holder means the vacuum must be broken in order to exchange tips. Here we need to be able to replace tips frequently. In addition we want to be able to study a large variety of samples including exfoliated flakes such as (twisted bilayer) graphene, where we need to land the tip on a ~micron sized flake on a large chip. Therefore we need the sample to be on a piezo driven course motion XY stage with a range of several millimeter.

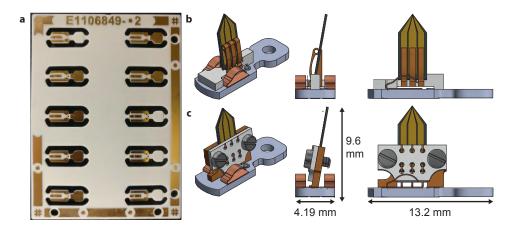

Besides the ability to exchange tips we also need multiple electrical contacts interfacing the tip holder to the of smart tip device. Fortunately it does not force us to custom build a STM head, since several commercially available Pan style STM heads are already equipped with three electrical contacts. This is due to the popularity of combined STM/AFM systems using a qPlus sensors [7]. Tip holders that are compatible with STM and AFM require three contacts.

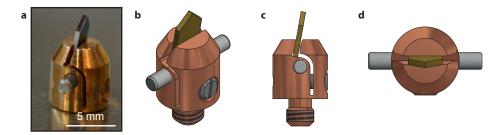

Here we integrated the PanScan STM head made by RHK [8] into a 4 K bath cryostat described in Sec. 3.3. The head itself is shown in Fig. 3.2a and consist of the following main parts from bottom to top: the body, the slider for course Z motion, the piezo tube for the scanning, the tip holder receptacle, the sample stage that holds the sample and allows for course XY movement and finally the eddy current damper. The slider is a rigid prism clamped in the body by two piezo stacks on each of the three flat sides. The piezo stacks generate slip stick motion and thereby jointly make the slider move up to ~8 mm in Z direction towards/away from the sample. We typically apply pulses with an ampli-

Figure 3.2: **a** Picture of the RHK STM head with all important parts indicated. Note that no sample or tip are loaded. **b** Close up of tip holder receptacle with three electrical contacts. **c** Close up of sample stage with four electrical contacts to the sample plate. **d**,**e** Pictures of the top (d) and bottom (e) of tip holder.

tude of  $\pm 150$  V and a pulse duration of 1 ms at 4.2 K, in ambient conditions lower voltages typically suffice.