# Online Condition Monitoring Methodology for Power Electronics Package Reliability Assessment

Martin, Henry A.; Smits, Edsger C.P.; Poelma, René H.; van Driel, W.D.; Zhang, GuoQi

DOI

10.1109/TPEL.2024.3352747

**Publication date**

**Document Version** Final published version

Published in

**IEEE Transactions on Power Electronics**

Citation (APA)

Martin, H. A., Smits, E. C. P., Poelma, R. H., van Driel, W. D., & Zhang, G. (2024). Online Condition

Monitoring Methodology for Power Electronics Package Reliability Assessment. *IEEE Transactions on Power Electronics*, 39(4), 4725-4734. https://doi.org/10.1109/TPEL.2024.3352747

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# Online Condition Monitoring Methodology for Power Electronics Package Reliability Assessment

Henry A. Martin<sup>®</sup>, *Member, IEEE*, Edsger C. P. Smits<sup>®</sup>, René H. Poelma<sup>®</sup>, *Senior Member, IEEE*, Willem D. van Driel<sup>®</sup>, and GuoQi Zhang<sup>®</sup>, *Fellow, IEEE*

Abstract—This article introduces an online condition monitoring strategy that utilizes a transient heat pulse to detect package thermal performance degradation. The metric employed is the temperature-dependent transient thermal impedance " $Z_{th}(t, T_{amb})$ ." The proposed methodology offers quantitative insights into package thermal performance degradation and effectively pinpoints the presence of multiple failure mechanisms. A thermal test chip assembled in a power quad flat no-lead package is used in this study to demonstrate the methodology. The packaged devices are first characterized to determine the transient pulse duration, a critical parameter to monitor a specific region of interest. Subsequently, package thermal performance degradation is continuously monitored online during thermomechanical cycling lifetime experiments. The validity of the measurement results is later confirmed through acoustic imaging and cross-sectional analysis. The changes observed in  $Z_{th}(t, T_{amb})$  over thermal cycling correspond to the delamination of the active metal layers on the die and cohesive failure on the die attach. This article further includes a comparative summary, highlighting the distinctions between the proposed and industry-standard test methods. In conclusion, the importance of online condition monitoring to detect early signs of failure is emphasized, and the proposed methodology's practical applicability in real-life scenarios is briefly discussed.

*Index Terms*—Application-driven reliability qualification, silver sintering, thermal cycling, thermal test chips (TTCs), transient thermal impedance.

Manuscript received 5 July 2023; revised 25 October 2023 and 1 December 2023; accepted 5 January 2024. Date of publication 11 January 2024; date of current version 16 February 2024. This work was supported in part by the Delft University of Technology and in part by the Chip Integration Technology Center. Recommended for publication by Associate Editor K. Ma. (Corresponding author: Henry A. Martin.)

Henry A. Martin is with the Electronics Components Technology and Materials Group, Delft University of Technology, 2628 CD Delft, The Netherlands, and also with the Chip Integration Technology Center, 6534 AT Nijmegen, The Netherlands (e-mail: henry.martin@citc.org).

Edsger C. P. Smits is with the Chip Integration Technology Center, 6534 AT Nijmegen, The Netherlands (e-mail: edsger.smits@citc.org).

René H. Poelma is with the Electronics Components Technology and Materials Group, Delft University of Technology, 2628 CD Delft, The Netherlands, and also with Nexperia BV, 6534 AB Nijmegen, The Netherlands (e-mail: rene.poelma@nexperia.com).

Willem D. van Driel is with the Electronics Components Technology and Materials Group, Delft University of Technology, 2628 CD Delft, The Netherlands, and also with Signify NV, 5656 AE Eindhoven, The Netherlands (e-mail: w.d.vandriel-1@tudelft.nl).

GuoQi Zhang is with the Electronics Components Technology and Materials Group, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: g.q.zhang@tudelft.nl).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPEL.2024.3352747.

Digital Object Identifier 10.1109/TPEL.2024.3352747

#### I. INTRODUCTION

N TODAY'S rapidly evolving technological landscape, ensuring power electronics package reliability is crucial as the scaling of More than Moore and mission-profile-based applications is becoming significantly important [1]. Recent advancements in power electronics reliability research are provided in [2]. Surveys conducted across various highly demanding industrial applications indicate power semiconductor devices to be particularly susceptible to failures [3], [4], [5], [6], [7], [8]. Power devices in field-critical applications undergo various stresses, including electrical overstress, mechanical vibrations, environmental humidity, and temperature fluctuations. While electrical, mechanical, and chemical-related issues are essential considerations for package reliability, thermal breakdowns pose a particularly severe challenge [9], [10]. Thermal bottlenecks and thermomechanical challenges primarily arise from the packaging materials' inhomogeneities. The mismatch in thermal expansion coefficients between the semiconductor die and the package substrate creates residual stresses, ultimately leading to thermal performance degradation.

Power packages are commonly subjected to rigorous stress tests such as active power cycling [11] and temperature cycling [12] to ensure reliability and meet qualification standards [13], [14]. However, the "test-to-fail" approach mostly involves offline monitoring and necessitates destructive techniques to identify failures. Hence, there is a clear need for online condition monitoring strategies to detect early signs of failure and gain quantitative insights. Further references to condition monitoring methods, online measurements, and lifetime reliability models are provided in [15], [16], [17], [18], [19], [20], [21], [22], and [23].

In this research, we present a novel methodology for identifying the temperature-dependent transient thermal impedance, denoted as " $Z_{\rm th}(t,T_{\rm amb})$ ," by utilizing a transient pulse. Our methodology demonstrates the following in this article:

- 1) online monitoring of package thermal performance degradation during accelerated lifetime testing;

- quantitative insights into the package degradation behavior and the ability to detect the presence of multiple failure mechanisms;

- 3) applicability of the proposed methodology on functional power devices [MOSFETs and insulated-gate bipolar transistors (IGBTs)] to facilitate application-driven qualification in real-life scenarios.

0885-8993 © 2024 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

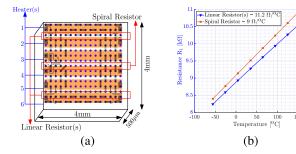

Fig. 1. (a) Layout of the TTC, depicting its geometry, in-built heaters, and resistors. (b) Resistance sensitivity of linear and spiral resistors evaluated at eight temperature points ranging from -55 to  $150\,^{\circ}$ C, demonstrating a linear temperature dependence.

The following section covers the semiconductor device selection, packaging materials, and the experimental methodology. The experimental results and analysis are presented subsequently with a brief discussion on practical challenges. Finally, a comparison to the industry standard thermal characterization methods is summarized.

#### II. EXPERIMENTAL METHODS

#### A. Sample Preparation

Silicon-based thermal test chips (TTCs) are specialized devices fabricated using the same process technology as semiconductor devices. These test chips feature lithographically defined heating and temperature sensing elements designed to optimize and evaluate package thermal performance. Several research efforts have been devoted to developing TTCs for interconnect material characterization and package reliability assessment [24], [25], [26], [27]. Since TTCs realistically represent thermal challenges that actual power components experience in operation, we chose them as a test vehicle in this study to demonstrate the online monitoring methodology. However, it is worth noting that the methodology can also be applied to functional power devices like MOSFETs and IGBTs by utilizing their temperature-sensitive electrical parameters for both heating and temperature sensing purposes.

The TTC chosen for this study contains six heaters and three resistance-based temperature detectors (RTDs) [see Fig. 1(a)]. The temperature dependence of the linear and spiral RTDs was measured at eight different temperatures ranging from -55 to 150 °C, revealing a linear relationship [see Fig. 1(b)]. The differences in resistance sensitivity between the linear and spiral RTDs arise from their geometrical variations. Normalizing the resistance sensitivity with the base resistance yields the resistor material's temperature coefficient resistance. In the rest of this article, Heater-3 was used for heating, and the spiral resistor was used for temperature sensing. Further details about the TTC are provided in [25] and [28].

The choice of interconnect material is a critical factor in package assembly. High-temperature Pb-rich solders have been favored in power electronics for their high melting point ( $\geq$  300 °C) and low stiffness ( $\sim$ 45–60 GPa). However, their usage

has been progressively reduced due to concerns about lead toxicity. An alternative technology for die attachment has emerged in the form of sintering metal particles (lead-free compositions). Metal precursors (Ag/Cu) in paste form are fused under heat and pressure. A review of die-attach materials for high-temperature applications, recent advancements in sintering materials, and lifetime modeling are provided in [29], [30], [31], [32], and [33].

The package assembly process involved in this study is further enumerated as follows.

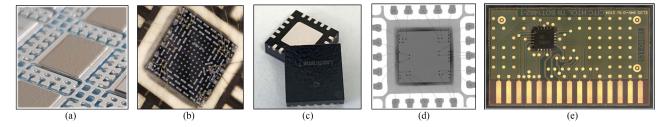

- 1) A pressureless micro-Ag sinter material in the form of wet paste was screen printed onto a silver-metalized copper lead frame [see Fig. 2(a)].

- 2) The TTC was then wet mounted over the sintering paste and sintered in a nitrogen-filled oven at 150 °C for 60 min, followed by an additional 60 min at 200 °C. After sintering, electrical connections were established using 99.99% pure gold wire bonds with a bond wire diameter of 25  $\mu$ m and a bond bump of 50  $\mu$ m [see Fig. 2(b)].

- 3) Subsequently, the entire stack was transfer molded using an epoxy molding compound, and individual packages were then singulated [see Fig. 2(c)].

- 4) The integrity of the package was further assessed through X-ray inspection, which offers high contrast with lowdensity materials like silicon and polymers compared to heavy metals such as gold and silver. This enables the detection of inhomogeneities in wire bonds and die attachments. An X-ray image of an overmolded package is presented in Fig. 2(d), illustrating the absence of voids or wire bond failures.

- 5) The packages were soldered onto an especially designed test board with four-point Kelvin connections extending up to the device, as depicted in Fig. 2(e). The solder joint interface was assumed to remain stable during the lifetime test.

#### B. Experimental Setup

A dedicated setup was developed for online monitoring of the package condition during thermomechanical cycling lifetime (TMCL) testing, as illustrated schematically in Fig. 3. The test boards, soldered with power quad flat no-lead (PQFN) packages [see Fig. 2(e)], were securely placed on a test socket inside a temperature cycling oven. The electrical connections from the test socket were extended to the sourcing and measuring equipment using a multiplexer (switch matrix), allowing for sequential measurements. The source unit has 40-V compliance at 1 A in continuous mode and 20 V at 10 A in pulsed mode. A trigger synchronization and communication protocol (TSP) was established between the instruments to ensure proper synchronization and communication. A dedicated control program exchanges data between the master computer and the TMCL oven. A user-defined MATLAB program manages all instrument communications.

The measurement conditions were fine-tuned to optimize the RTD sensitivity. Various input currents were applied to the test chips to determine the optimal measurement currents ( $\leq 0.3 \text{ mA}$ )

Fig. 2. Illustration of the steps involved in the package assembly process. (a) Micro-Ag sinter material screen printed on a lead frame. (b) Sintering of a test chip onto the lead frame with wire bonding. (c) Molded, singulated, and laser marked PQFN packages. (d) X-ray inspection of a molded package. (e) PQFN soldered to a test board for online measurements.

Fig. 3. Schematic of the experimental setup for online condition monitoring during accelerated lifetime testing. Packaged devices, soldered to the test boards, are placed in dedicated slots inside a temperature-cycling oven. Test boards are connected to a source measurement unit (SMU) and a digital multimeter (DMM) through a multiplexer for sequential measurements.

with minimal self-heating effects. The measuring equipment has a resolution of 1  $\mu V$  for measurements in the 10-V range, and the accuracy was determined to be within  $\pm 0.1$  mV. Further information regarding measurement variation, repeatability, and reproducibility can be found in [28]. While the electrical layout depicted in Fig. 3 pertains to the test chip configuration, the test setup also features dedicated slots designed to measure up to 15 MOSFETs and/or IGBTs sequentially.

### C. Experimental Characterization

The thermal characterization methodology employed in this study is an adaptation of the JESD51-14 transient dual interface test method [34]. To analyze the package thermal performance, it is necessary to measure the transient thermal impedance  $Z_{\rm th}(t)$ . This parameter represents the packaging materials' ability to dissipate heat, and it is a sum of individual layer resistances  $R_{\rm th}$ . In this study, Heater-3 was used for heating, and the spiral resistor (RTD-2) was used to measure the change in electrical resistance due to heating, which further translates to device temperature. To ensure efficient heat dissipation, the test boards were clamped onto a water-cooled heat sink, and thermal characterization was conducted with and without a thermal interface material (TIM).

A continuous current of 100 mA (equivalent to approximately 0.7 W or 32 W/cm<sup>2</sup> at 25 °C ambient) was supplied to Heater-3 for a duration of 100 s. This current value was selected in

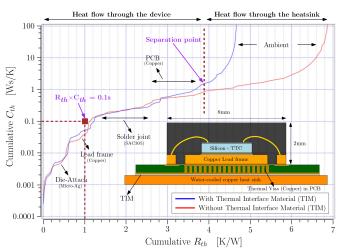

Fig. 4. Cumulative resistance  $(R_{\rm th})$ —capacitance  $(C_{\rm th})$  network graph from the measured data. The PQFN on a test board, mounted on a water-cooled heat sink, allows heat flow from the device toward the heat sink. Analysis with and without a TIM identifies the key heat dissipation information, notably at the die-attach interface, within a 0.1-s transit time window.

consideration for online monitoring experiments during thermal cycling. The intention was to apply a brief localized heat pulse that would generate sufficient heat for package thermal performance analysis without deviating beyond the limits set for thermal cycling. The resulting changes in the resistance of RTD-2 were measured to determine the device temperature. During the 100-s heating period, the device and packaging materials reached a 1-D steady state, allowing the extraction of the resistance—capacitance network. This was achieved by computing the structure function, as described in [35], [36], and [37]. The TDIM-Master software provided by JEDEC [34] was used for time-constant spectrum deconvolution and Foster—Cauer transformation. The computed results of the structure function are depicted in Fig. 4, along with a schematic representation of the PQFN package on a printed circuit board (PCB) mounted to a heat sink

Based on the thermal characterization measurements depicted in Fig. 4, the following conclusions and assumptions were drawn to support the online condition monitoring experiments.

Fig. 4 illustrates the separation point distinguishing the heat flow paths between the device (PQFN + PCB) and the heat sink. Regarding heat flow through the device, the

- primary sources of resistance are the package solder joint interface and the PCB.

- 2) Given that the die-attach interface is the region of interest, a transient pulse duration of 0.1 s was chosen for localized heating and online condition monitoring, as highlighted in Fig. 4. The transient pulse duration of 0.1 s was chosen to limit the influence of the solder joint and the PCB materials.

- 3) The 0.1-s heating window defines a thermal resistance boundary of 1 K/W (see Fig. 4). Due to thermal aging, the packaging material's thermal resistance might shift, subsequently altering the boundary conditions for a 0.1-s heating interval. Since the region of interest is to monitor the die-attach interface, we assumed that the thermal resistance shift of the die-attach layer over the lifetime testing would not exceed the thermal resistance boundary.

# D. Online Condition Monitoring Methodology

Packaging materials undergo degradation over time, influenced by operational and environmental conditions. Package degradation may cause an increase in thermal resistance and impede heat dissipation, resulting in elevated device temperatures. Traditional thermal characterization methods, such as MIL-STD-883E, involve invasive means to measure the device junction and its case temperatures to determine the "steady-state" thermal impedance [38]. This method has been surpassed by transient thermal impedance measurements proposed by Székely [35], which has been adopted as the JEDEC standard JESD51-14 [34]. These approaches are suitable for offline monitoring and thermal characterization.

In this study, we introduce a novel "temperature-dependent transient-pulse test method" to obtain the temperature-dependent transient thermal impedance, denoted as  $Z_{\rm th}(t,T_{\rm amb})$ . The transient time is the transient pulse duration illustrated in Fig. 4, and the temperature dependence is established by measuring  $Z_{\rm th}(t)$  at different temperature ambients during TMCL testing. This approach allows for characterizing the package's thermal behavior under dynamic conditions.

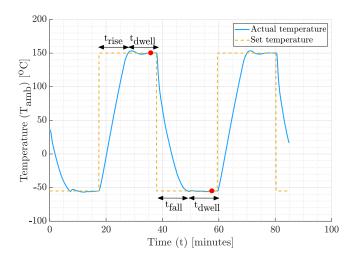

The TMCL tests were in accordance with the guidelines outlined in the JESD22-A104 standard [12] and automotive norms AEC-Q101 [14]. The PQFNs with TTC soldered to the PCB underwent thermal cycling from -55 °C (compression state) to 150 °C (expansion state), as illustrated in Fig. 5. The temperature cycling rate was maintained at approximately one to two cycles per hour, with a rise time ( $t_{rise}$ ) and fall time ( $t_{fall}$ ) of around 10 min. The dwell time ( $t_{\text{dwell}}$ ) was dependent on the time required for the oven to reach a stable temperature. Although thermal cycling is a relatively slow process for power device aging, the transient pulse measurements for online monitoring take only a few second per device. Once the oven's temperature stabilized, a short transient heat pulse of 0.1 s was applied using Heater-3, and the device temperature was measured using RTD-2. It is important to be aware that the measurements were conducted without a water-cooled heat sink due to thermal cycling.

Fig. 5. Graph illustrating the temperature cycling profile adapted according to JEDEC standards for automotive-grade discrete semiconductor devices. The devices are cycled at one to two cycles per hour.  $Z_{\rm th}$  ( $t=0.1~{\rm s}$ ) was measured during every cycle once the oven reached a stable temperature, as indicated by a red dot in the graph.

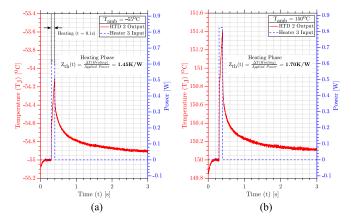

Fig. 6. (a) Measurements at  $-55\,^{\circ}$ C. (b) Measurements at  $150\,^{\circ}$ C. A 0.1-s 100-mA heat pulse applied to Heater-3, with junction temperature ( $T_{j}$ ) measured using RTD-2 at different ambient temperatures ( $T_{amb} = -55$  and  $150\,^{\circ}$ C). The applied power input varied with  $T_{amb}$  due to the temperature sensitivity of the heater material. Differences observed in  $Z_{th}(t)$  at different  $T_{amb}$  result from the temperature-dependent thermal properties of packaging materials, where silicon plays a significant role.

The transient pulse response of RTD-2 measured at -55 and  $150\,^{\circ}\mathrm{C}$  is shown in Fig. 6, along with the applied input power for the heater. The initial fluctuations observed within the first  $0.2\,\mathrm{s}$  are a measurement artifact resulting from the trigger range settings of the sourcing equipment. The differences in power input at -55 and  $150\,^{\circ}\mathrm{C}$  are due to the temperature sensitivity of the heater material. Hence, the temperature change  $\Delta T$  was normalized with the applied input power to obtain the transient thermal impedance  $Z_{\rm th}(t)$ . The  $Z_{\rm th}(t)$  parameter was determined during the heating phase since the heating time chosen was not long enough for the device to reach a steady state. Besides, the test chip has separate structures for heating and sensing, with heating power remaining relatively constant during the heating pulse time and no electrical crosstalk occurring to the sensing

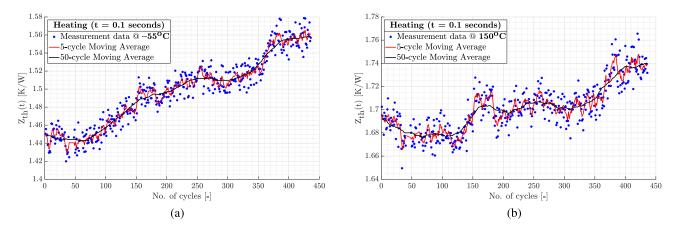

Fig. 7. (a) Measurement data at -55 °C. (b) Measurement data at 150 °C. The measurements were halted at 436 cycles, as the acquired data were deemed sufficient to demonstrate the methodology.

element. Hence, in accordance with JESD51-14 standards, it is acceptable to extract  $Z_{th}(t)$  during the heating phase.

$Z_{\rm th}(t)$  obtained from Fig. 6 exhibits strong temperature dependence, which can be attributed to the temperature-dependent thermal properties of the packaging materials. The micro-Ag sinter die attach and the copper lead frame exhibit minimal temperature dependence within the thermal cycling temperature range [39], [40]. However, the thermal properties of the semiconductor substrate (Silicon) undergo significant changes with temperature [41]. Therefore, the observed change in temperature  $\Delta T$  between -55 and 150 °C (see Fig. 6) is influenced by the temperature-dependent properties of the silicon substrate. A theoretical explanation of the temperature-dependent properties of the packaging materials and their impact on the relative change in temperature  $\Delta T$  is provided in [28]. The change in temperature-dependent transient thermal impedance " $Z_{th}(t, T_{amb})$ " parameter over "N" thermal cycles indicating the package's health is demonstrated in the subsequent section.

It is important to be aware that an increment in  $Z_{\rm th}(t)$  would suggest degradation and the dissimilarities at different temperatures  $Z_{\rm th}(t,T_{\rm amb})$  would signify the degradation behavior.

#### III. EXPERIMENTAL RESULTS AND DISCUSSION

#### A. Online Condition Monitoring Results

The transient thermal impedance  $Z_{\rm th}(t)$  obtained from the transient pulse measurements (see Fig. 6) was continuously monitored during thermal cycling until a sufficient amount of data on package degradation were obtained to demonstrate the online monitoring methodology. Ideally,  $Z_{\rm th}(t)$  should remain constant (within the measurement variability) over time. However, due to continuous cyclic loading, the packaging materials tend to degrade, resulting in an increase in the  $Z_{\rm th}(t)$  value. Since the transient time is kept short (t=0.1 s), the obtained timetransient  $Z_{\rm th}$  information reflects the behavior of the materials near the die, such as die attachment, as observed in experimental characterization (see Fig. 4). The measurement results of 436 thermal cycles at -55 and  $150\,^{\circ}{\rm C}$  are presented in Fig. 7.

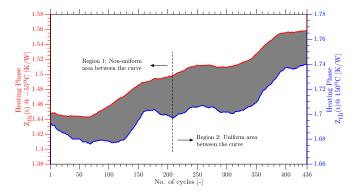

Fig. 8. Differences in the measurements at -55 and 150 °C are visualized by highlighting the area between the curves. Two distinct regions (Region-1 and Region-2) can be identified within the highlighted area. Region-1 indicates a nonuniform increase between the curves, and Region-2 indicates a relatively uniform increase.

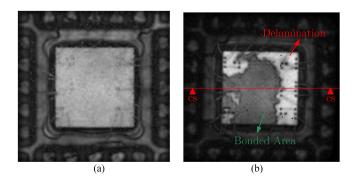

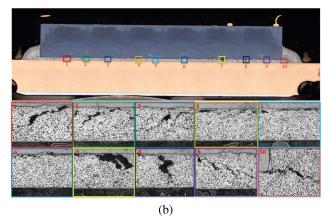

Fig. 9. (a) Reference PQFN sample at zero cycle. (b) Device under test after 436 thermal cycles. A sequential lateral scan (C-scan) analysis reveals signs of delamination near the overmold-die interface, clearly distinguishable from bonded areas in the thermally cycled sample. Further cross sectioning of the delaminated sample is highlighted in (b).

To facilitate the visual interpretation of the measurement data and identify the degradation trend, simple moving averages (SMAs) were calculated for the variable vector  $Z^i_{\rm th}(t)$  over N observations. The five-cycle moving average highlights short-term fluctuations in the measurements, while the 50-cycle moving

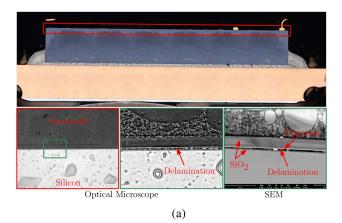

Fig. 10. (a) Cross-sectional micrographs focused near the overmold-die interface indicate delamination of titanium metal layers from the silicon dioxide passivation layer on the test chip. (b) Cross-sectional micrographs focused near the die-attach interface indicate a cohesive failure within the bulk of the micro-Ag sintered die-attach material. Notably, fractures align parallel to the die in the center and are inclined toward the bulk along the edges.

average smooths out variations and reveals long-term trends. The 50-cycle SMA data at  $-55\,^{\circ}\mathrm{C}$  [see Fig. 7(a)] indicate a gradual increase in thermal impedance, signifying the degradation of packaging materials due to repeated thermal cycling-induced expansion and contraction. Similarly, the 50-cycle SMA data at 150  $^{\circ}\mathrm{C}$  [see Fig. 7(b)] also suggest comparable indications of package degradation. However, comparing the measurement data at -55 and  $150\,^{\circ}\mathrm{C}$  indicates dissimilarities in the  $Z_{th}(t)$  trend. Consequently, the 50-cycle SMA data from -55 and  $150\,^{\circ}\mathrm{C}$  were plotted together for further analysis, as depicted in Fig. 8.

Two distinct regions, namely, Region-1 and Region-2, can be observed by comparing the area between the curves. In Region-1, the area between the curves shows a nonuniform increasing trend, while in Region-2, the area remains relatively uniform with marginal variations. One possible explanation for such distinct regions can be due to the interplay of multiple failure mechanisms influencing the measurements of  $Z_{th}(t)$ . Under compression, defects such as delamination and/or inplane fractures may grow, leading to larger thermal resistances. Conversely, the defects might close during expansion, resulting in lower thermal resistance. Such behavior can induce different thermal responses at -55 and 150 °C, as observed in Fig. 8. This reasoning aligns well with the nonuniform increasing trend observed in Region-1. However, beyond ~210 cycles (Region-2), the thermal resistances increase uniformly at -55 and 150 °C. This suggests that the dominant failure mechanism in Region-1 may differ from that in Region-2. It is important to note that the interpretation provided here based on the experimental results represents one of several possible explanations. The device was subjected to acoustic imaging [confocal scanning acoustic microscopy (CSAM)] to further investigate and provide quantitative evidence, followed by cross sectioning to gather comprehensive insights.

# B. Failure Analysis

CSAM is a highly effective imaging technique used for nondestructive identification of delaminations occurring at buried interfaces within electronic packages [42], [43]. Fig. 9(a) illustrates CSAM imaging obtained from a reference zero-hour sample, where no indications of delaminations were detected. However, a notable contrast emerges when examining the device under test after 436 thermal cycles, as displayed in Fig. 9(b). Delaminations near the overmold-die interface are clearly visible in the image. Although the exact cause of these delaminations remains unknown, we consider them to be a significant contributing factor to the observed increase in thermal impedance during online monitoring. To conduct further analysis, the sample was cross sectioned, and the location of the cross section is indicated in Fig. 9(b).

The tested PQFN package was potted in an epoxy resin and meticulously cross sectioned by polishing at a step of 25  $\mu$ m with 150 r/min and 5-N force. After the completion of the polishing procedure, a comprehensive analysis of the sample was conducted. The cross-sectioned sample was examined using an optical microscope and an electron microscope near the overmold-die interface. This analysis aimed to identify the root cause of the delamination observed during CSAM imaging. Upon the close inspection of the cross-sectional images taken in proximity to the overmold-die interface [see Fig. 10(a)], it became evident that the active-metal layers consisting of a 100-nm titanium film on the silicon substrate had experienced delamination from the silicon dioxide passivation layer. This delamination is most likely attributed to residual stresses originating from the manufacturing process or thermomechanical stresses encountered during testing.

Further analysis was conducted on the cross-sectional sample, focusing on the region near the die-attach interface. Fractures within the micro-Ag sinter die-attach material were observed [see Fig. 10(b)]. These fractures exhibited a distinct pattern. The fractures aligned parallel to the die interface at the center, while toward the edges, the fractures were inclined into the bulk of the silver sinter material. Repeated thermomechanical loading conditions caused the die-attach interface to endure cumulative stress damage from continuous expansion and contraction. The fracture behavior exhibited by the micro-Ag pressureless sinter material raises concerns regarding its reliability. Therefore,

TABLE I

ONLINE MONITORING METHODOLOGY PROPOSED IN THIS ARTICLE AGAINST THE INDUSTRY STANDARDS MIL-STD-883E AND JESD51-14

|                           | MIL-STD-883E<br>Thermal Characteristics<br>Testing Method                                                                                                                           | JESD51-14<br>Transient Dual Interface<br>Test Method                                                                                                                                                                        | Proposed Methodology<br>Temperature Dependent<br>Transient-Pulse Test Method                                                                                                                                                                               |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose                   | To determine the Junction-to-Case thermal impedance of a package.                                                                                                                   | To determine the packaging materials individual layer contribution towards Junction-to-Case thermal impedance.                                                                                                              | To determine the package's thermal performance degradation based on temperature-dependent (ambient) transient thermal impedance.                                                                                                                           |

| Application / Suitability | Thermal Characterization.     Offline monitoring during accelerated lifetime testing.                                                                                               | Thermal Characterization.     Offline monitoring during accelerated lifetime testing.                                                                                                                                       | Thermal Characterization.     Online monitoring during accelerated lifetime testing.                                                                                                                                                                       |

| Methodology               | 1. Measure the device junction and case (package substrate) temperature at steady-state by external sensors (extrinsic) and/or temperature sensitive device parameters (intrinsic). | Measure the change in the device junction temperature (extrinsic or intrinsic) to compute the resistance – capacitance network.     Requires a water-cooled heat sink to achieve one-dimensional conductive heat flow path. | Pre-characterization is required based on JESD51-14 test method to identify the transient pulse duration.     Ambient conditions to be recorded.     Measure the change in the device junction temperature (intrinsic) by applying a transient heat pulse. |

| Measurement parameters    | "Steady-state" thermal impedance — $Z_{th-JC}(t = \infty)$                                                                                                                          | "Transient-state" thermal impedance - $Z_{th-JC}(t)$                                                                                                                                                                        | "Temperature-dependent transient-<br>state" thermal impedance - $Z_{th}(t,T_{amb})$                                                                                                                                                                        |

| Advantages                | Easy to implement.     Less computational effort.     Precise estimation of Junction-to-case package thermal impedance.                                                             | Accurate thermal characterization.     Enables estimating the individual layer thermal resistance-capacitance network.     Non-destructive method.                                                                          | Fast and accurate measurements.     Online monitoring.     The presence of multiple failure mechanisms can be identified.     Advanced data analytics can improve identifying degradation trends.     Includes the advantages of JESD51-14 test method.    |

| Limitations               | Invasive method.     Offline monitoring.                                                                                                                                            | Assumes one-dimensional heat flow.     High signal-to-noise ratio.     High computational effort.     Offline monitoring.                                                                                                   | Requires further tests and validation.     Additional refinements are needed for real-life applications.     Lifetime reliability models are needed to understand the aging mechanisms.     Includes the limitations of JESD51-14 test method.             |

further research on sintering materials is crucial to identify an optimal replacement for high-Pb solders.

Based on the findings from CSAM and cross-sectional analysis, the following conclusions can be drawn, which align in line with the online monitoring measurement results shown in Fig. 8.

- Two distinct failure mechanisms were identified: 1) delamination of active metal layers from the passivation layer, confirmed by CSAM and cross-sectional analysis; and b) die-attach failure. The micro-Ag pressureless sinter material experienced significant long-term fractures under repeated cyclic loading conditions.

- 2) The analysis quantifies the experimental results and confirms the presence of multiple failure mechanisms.

# C. Discussion

The online condition monitoring methodology proposed in this study has demonstrated its capability for real-time assessment of the package's health and performance, particularly during accelerated lifetime tests (thermal cycling). Nevertheless, it is essential to acknowledge the practical challenges that accompany this methodology and its applicability in real-life situations.

The proposed method has demonstrated its effectiveness in monitoring package thermal performance degradation. However, with a complex interplay of multiple failure

- mechanisms (see Fig. 8), it remains challenging to decouple the influence solely from the experimental results. Hence, the methodology requires further testing and validation.

- 2) The thermal resistance of the various packaging layers might shift over time due to aging. Based on the experimental results (see Fig. 7), the relative change in thermal resistance  $\Delta Z_{\rm th}(t,T_{\rm amb})$  over 436 thermal cycles was  $\sim$ 0.1 K/W, which remains within the thermal resistance boundary highlighted in Fig. 4. Hence, in this particular testing condition, the assumption to consider a 0.1-s heating interval was appropriate. However, this needs to be verified for different package geometries.

- 3) Temperature significantly affects the semiconductor material's conductivity and carrier mobility. By utilizing the temperature-sensitive parameters, the transient thermal impedance based on a transient pulse can be determined in functional power devices (MOSFETs and IGBTs). Hence, the methodology is not bound to TTCs as demonstrated in this study but can be applied to other temperature-sensitive devices.

- 4) Additional refinements are required for monitoring the devices online in real-life scenarios. The transient thermal impedance must be measured in real time at a predefined interval without disrupting the system operation. It is also necessary to capture the ambient conditions (temperature, humidity, etc.) while measuring the transient

- thermal impedance. The objective is to create a continuous longitudinal dataset spanning the device's lifespan, analyzing its real-time thermal performance in correlation to environmental factors.

- 5) In this study, moving averages were used to reduce measurement variation and identify the degradation trend. Recent advances in machine learning techniques involving artificial neural networks and convolutional neural networks enhance prognostic monitoring and enable failure mode classification [44], [45].

# IV. COMPARISON OF THE PROPOSED METHODOLOGY AGAINST THE INDUSTRY STANDARD TEST METHODS

Despite the aforementioned practical challenges, the proposed methodology provides compelling reasons for its adaptation as an online condition monitoring tool for package reliability assessment. For decades, measuring the package thermal impedance has been a standard practice in the industry, serving as a pivotal metric for evaluating package thermal performance. Established standards, such as MIL-STD-883E [38] and JESD51-14 [34], have provided guidelines for determining the steady-state and transient-state thermal impedance. This research takes a step further in determining the temperaturedependent transient thermal impedance. This innovative approach leverages transient heat pulses to identify the changes in thermal resistance within a specific region of interest. Notably, the transient time is instrumental in delineating the boundary conditions for continuous monitoring. A comprehensive summary is presented herein, comparing the proposed methodology with established industry-standard test methods outlined in MIL-STD-883E and JESD51-14. This comparison spans various facets: purpose, suitability, measurement methodology, metric employed, advantages, and limitations (see Table I).

Besides, several research efforts have been devoted to establishing online condition monitoring based on diverse prognostic device health management measurement methodologies. These measurement methods can be broadly classified as follows: contact (probing) [15], [16] and contactless techniques, thermal and nonthermal (electrical, acoustic [43], [46], etc.) methods, extrinsic methods involving sensors [47], [48], [49], [50], and intrinsic methods (temperature-sensitive parameters [51]), and reliability modeling methods [22], [23]. Notably, most of these measurement techniques necessitate physical or visual access to the device and are intrusive to device operation, limiting their practical applicability in real-life scenarios. In contrast, the methodology proposed in this study monitors the package's thermal performance without requiring physical or visual access. This characteristic underscores its potential as a viable solution for online monitoring in real-life applications.

#### V. CONCLUSION

In response to the increasing demand for reliable power semiconductor devices in field-critical applications, particularly in environments prone to thermal breakdown, an online condition monitoring methodology was introduced in this study. The methodology facilitated the real-time detection of thermal degradation within packaged devices. An accelerated

lifetime test (thermal cycling) was conducted in this study to validate the methodology. Based on the changes monitored in the temperature-dependent transient thermal impedance  $Z_{\rm th}(t,T_{\rm amb})$ , we were able to understand the package degradation behavior and identify the presence of multiple failure mechanisms.

The proposed methodology was demonstrated using a TTC integrated into a PQFN package as a test platform. The transient dual-interface test method from JESD51-14 was adapted to determine the optimal transient pulse duration, a critical parameter for acquiring thermal performance data within the region of interest. During TMCL testing, an increase in  $Z_{\rm th}(t)$  was observed at different ambient temperatures ( $T_{\rm amb}$ ), indicating thermal degradation due to cyclic loading. Disparities in measurements at different temperature ambients hinted at multiple failure mechanisms, later confirmed through CSAM analysis and cross-sectional inspection.

The proposed methodology has proven effective for online monitoring and offers quantitative insights into the degradation behavior. In this article, we further discussed the practical challenges associated with the methodology and highlighted distinctions between the proposed and industry-standard methods. The applicability of the online monitoring methodology in real-life applications requires additional refinements, which were briefly discussed. The experiments were demonstrated with TTCs in a PQFN package subjected to thermal cycling. However, the methodology can also be applied to functional power semiconductor devices and other accelerated aging processes. The significance of the proposed method lies in the early detection of signs of failure or degradation, thereby preventing unexpected system downtime and additional costs.

#### ACKNOWLEDGMENT

The authors would like to extend their gratitude to fellow researchers from the Delft University of Technology and the Chip Integration Technology Center for their valuable support in this work.

# REFERENCES

- A. B. Kahng, "Scaling: More than Moore's law," *IEEE Des. Test Comput.*, vol. 27, no. 3, pp. 86–87, May/Jun. 2010.

- [2] H. Wang and F. Blaabjerg, "Power electronics reliability: State of the art and outlook," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 6, pp. 6476–6493, Dec. 2021.

- [3] S. Yang, A. Bryant, P. Mawby, D. Xiang, L. Ran, and P. Tavner, "An industry-based survey of reliability in power electronic converters," *IEEE Trans. Ind. Appl.*, vol. 47, no. 3, pp. 1441–1451, May/Jun. 2011.

- [4] B. Hahn, M. Durstewitz, and K. Rohrig, "Reliability of wind turbines: Experiences of 15 years with 1,500 WTs," in *Proc. Euromech Colloq.*, *Wind Energy*, P.S. J. Peinke and S. Barth, Eds., Springer-Verlag, Germany, 2007, pp. 329–332.

- [5] Q. Chai, C. Zhang, Z. Dong, and Y. Xu, "Operational reliability assessment of photovoltaic inverters considering voltage/VAR control function," *Electr. Power Syst. Res.*, vol. 190, 2021, Art. no. 106706.

- [6] L. Moore and H. Post, "Five years of operating experience at a large, utility-scale photovoltaic generating plant," *Prog. Photovolt.: Res. Appl.*, vol. 16, pp. 249–259, 2008.

- [7] K. Hu, Z. Liu, Y. Yang, F. Iannuzzo, and F. Blaabjerg, "Ensuring a reliable operation of two-level IGBT-based power converters: A review of monitoring and fault-tolerant approaches," *IEEE Access*, vol. 8, pp. 89988–90022, 2020.

- [8] M. H. M. Sathik, S. Prasanth, F. Sasongko, and J. Pou, "Lifetime estimation of off-the-shelf aerospace power converters," *IEEE Aerosp. Electron. Syst. Mag.*, vol. 33, no. 12, pp. 26–38, Dec. 2018.

- [9] A. Sundaram and R. Velraj, "Thermal management of electronics: A review of literature," *Thermal Sci.*, vol. 12, pp. 5–26, 2008.

- [10] F. Blaabjerg, H. Wang, I. Vernica, B. Liu, and P. Davari, "Reliability of power electronic systems for EV/HEV applications," *Proc. IEEE*, vol. 109, no. 6, pp. 1060–1076, Jun. 2021.

- [11] Power Cycling Standards, Standard JESD22-A122A, JEDEC Solid State Technology Association, 2016.

- [12] Temperature Cycling Standards, Standard JESD22-A104F.01, JEDEC Solid State Technology Association, 2023.

- [13] European Center for Power Electronics, "Qualification of power modules for use in power electronics converter units in motor vehicles," ECPE European Center for Power Electronics e.V., Nuremberg, Germany, Tech. Rep. AQG-324, 2019.

- [14] Automotive Electronics Council, "Stress test qualification for automotive grade discrete semiconductors," Automotive Electronics Council, Cary, IL, USA, Tech. Rep. AEC-Q101-REV-C, 2005.

- [15] A. Hanif, Y. Yu, D. DeVoto, and F. Khan, "A comprehensive review toward the state-of-the-art in failure and lifetime predictions of power electronic devices," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4729–4746, May 2019.

- [16] G. Susinni, S. A. Rizzo, and F. Iannuzzo, "Two decades of condition monitoring methods for power devices," *Electronics*, vol. 10, no. 6, 2021, Art. no. 683.

- [17] S. Yang, D. Xiang, A. Bryant, P. Mawby, L. Ran, and P. Tavner, "Condition monitoring for device reliability in power electronic converters: A review," *IEEE Trans. Power Electron.*, vol. 25, no. 11, pp. 2734–2752, Nov. 2010.

- [18] D. Kim et al., "Online thermal resistance and reliability characteristic monitoring of power modules with Ag sinter joining and Pb, Pb-free solders during power cycling test by SiC TEG chip," *IEEE Trans. Power Electron.*, vol. 36, no. 5, pp. 4977–4990, May 2021.

- [19] E. Ugur, C. Xu, F. Yang, S. Pu, and B. Akin, "A new complete condition monitoring method for SiC power MOSFETs," *IEEE Trans. Ind. Electron.*, vol. 68, no. 2, pp. 1654–1664, Feb. 2021.

- [20] N. Duan, T. Bach, J. Shen, and R. Rongen, "Comparison of in-situ measurement techniques of solder joint reliability under thermo-mechanical stresses," *Microelectronics Rel.*, vol. 54, no. 9, pp. 1753–1757, 2014.

- [21] A. Prisacaru, P. J. Gromala, M. B. Jeronimo, B. Han, and G. Q. Zhang, "Prognostics and health monitoring of electronic system: A review," in Proc. 18th Int. Conf. Thermal, Mech. Multi-Phys. Simul. Exp. Microelectron. Microsyst., 2017, pp. 1–11.

- [22] Z. Ni, X. Lyu, O. P. Yadav, B. N. Singh, S. Zheng, and D. Cao, "Overview of real-time lifetime prediction and extension for SiC power converters," *IEEE Trans. Power Electron.*, vol. 35, no. 8, pp. 7765–7794, Aug. 2020.

- [23] L. Ceccarelli, R. M. Kotecha, A. S. Bahman, F. Iannuzzo, and H. A. Mantooth, "Mission-profile-based lifetime prediction for a SiC MOSFET power module using a multi-step condition-mapping simulation strategy," *IEEE Trans. Power Electron.*, vol. 34, no. 10, pp. 9698–9708, Oct. 2019.

- [24] B. Siegal and J. Galloway, "Thermal test chip design and performance considerations," in *Proc. 24th Annu. IEEE Semicond. Thermal Meas. Manage. Symp.*, 2008, pp. 59–62.

- [25] R. Sattari, H. v. Zeijl, and G. Zhang, "Design and fabrication of a multi-functional programmable thermal test chip," in *Proc. 23rd Eur. Microelectron. Packag. Conf. Exhib.*, 2021, pp. 1–7.

- [26] R. Sattari, D. Hu, X. Liu, H. van Zeijl, S. Vollebregt, and G. Zhang, "Transient thermal measurement on nano-metallic sintered die-attach joints using a thermal test chip," *Appl. Thermal Eng.*, vol. 221, 2023, Art. no. 119503.

- [27] H. Martin et al., "Heterogeneous integration of diamond heat spreaders for power electronics application," in *Proc. IEEE 73rd Electron. Compon. Technol. Conf.*, 2023, pp. 118–125.

- [28] H. A. Martin, R. Sattari, E. C. P. Smits, H. W. van Zeijl, W. D. v. Driel, and G. Q. Zhang, "In-situ reliability monitoring of power packages using a thermal test chip," in *Proc. 23rd Int. Conf. Thermal, Mech. Multi-Phys. Simul. Exp. Microelectron. Microsyst.*, 2022, pp. 1–10.

- [29] K. Siow, "Die-attach materials for high temperature applications in microelectronics packaging," in *Materials, Process, Equipment, and Reliability*. Berlin, Germany: Springer, 2018, pp. 181–196.

- [30] M. Schaal, M. Klingler, and B. Wunderle, "Silver sintering in power electronics: The state of the art in material characterization and reliability testing," in *Proc. 7th Electron. Syst.-Integr. Technol. Conf.*, 2018, pp. 1–18.

- [31] H. Martin, X. Cao, J. Wijgaerts, E. Smits, B. Xia, and R. d. Wit, "Improving semiconductor reliability of silver sintering die-attach adhesives for large die on copper lead frames," in *Proc. 24th Eur. Microelectron. Packag. Conf.*, 2023, pp. 1–8.

- [32] X. Hu et al., "Microstructure analysis based on 3D reconstruction model and transient thermal impedance measurement of resin-reinforced sintered Ag layer for high power RF device," in *Proc. 24th Int. Conf. Thermal, Mech. Multi-Phys. Simul. Exp. Microelectron. Microsyst.*, 2023, pp. 1–7.

- [33] A. Mathew et al., "Lifetime modelling of sintered silver interconnected power devices by FEM and experiment," in *Proc. 22nd Int. Conf. Ther*mal, Mech. Multi-Phys. Simul. Exp. Microelectron. Microsyst., 2021, pp. 1–9.

- [34] Transient Dual Interface Test Method for the Measurement of the Thermal Resistance Junction to Case of Semiconductor Devices With Heat Flow Through a Single Path, Standard JESD51-14, JEDEC Solid State Technology Association, 2010.

- [35] V. Székely, "A new evaluation method of thermal transient measurement results," *Microelectron. J.*, vol. 28, no. 3, pp. 277–292, 1997.

- [36] M. Rencz, A. Poppe, E. Kollar, S. Ress, and V. Szekely, "Increasing the accuracy of structure function based thermal material parameter measurements," *IEEE Trans. Compon. Packag. Technol.*, vol. 28, no. 1, pp. 51–57, Mar 2005

- [37] M. Rencz and V. Szekely, "Structure function evaluation of stacked dies," in *Proc. 20th Annu. IEEE Semicond. Thermal Meas. Manage. Symp.*, 2004, pp. 50–54.

- [38] Thermal Characteristics Test Method for Microelectronic Devices, Test Method Standard for Microcircuits MIL-STD-883E-1012.1 1980.

- [39] A. A. Wereszczak, D. J. Vuono, H. Wang, M. K. Ferber, and Z. Liang, "Properties of bulk sintered silver as a function of porosity," Oak Ridge Nat. Lab., Oak Ridge, TN, USA, Tech. Rep. ORNL/TM-2012/130, 2012.

- [40] N. Simon, E. Drexler, and R. Reed, "Properties of copper and copper alloys at cryogenic temperatures," Nat. Inst. Standards Technol., Boulder, CO, USA, Tech. Rep. PB-92-172766/XAB; NIST/MONO-177, 1992.

- [41] C. Prakash, "Thermal conductivity variation of silicon with temperature," *Microelectron. Rel.*, vol. 18, no. 4, 1978, Art. no. 333.

- [42] H. Yu, "Scanning acoustic microscopy for material evaluation," Appl. Microsc., vol. 50, 2020, Art. no. 25.

- [43] F. Bertocci, A. Grandoni, and T. Djuric-Rissner, "Scanning acoustic microscopy (SAM): A robust method for defect detection during the manufacturing process of ultrasound probes for medical imaging," *Sensors*, vol. 19, 2019, Art. no. 4868.

- [44] X. Yang, Y. Zhang, X. Wu, and G. Liu, "Failure mode classification of IGBT modules under power cycling tests based on data-driven machine learning framework," *IEEE Trans. Power Electron.*, vol. 38, no. 12, pp. 16130–16141, Dec. 2023.

- [45] D. Santamargarita, D. Molinero, E. Bueno, M. Marrón, and M. Vasić, "On-line monitoring of maximum temperature and loss distribution of a medium frequency transformer using artificial neural networks," *IEEE Trans. Power Electron.*, vol. 38, no. 12, pp. 15818–15828, Dec. 2023.

- [46] S. Levikari, T. J. Kärkkäinen, C. Andersson, J. Tammminen, and P. Silventoinen, "Acoustic detection of cracks and delamination in multilayer ceramic capacitors," *IEEE Trans. Ind. Appl.*, vol. 55, no. 2, pp. 1787–1794, Mar./Apr. 2019.

- [47] E. R. Motto and J. F. Donlon, "IGBT module with user accessible on-chip current and temperature sensors," in *Proc. 27th Annu. IEEE Appl. Power Electron. Conf. Expo.*, 2012, pp. 176–181.

- [48] Y. Zhou et al., "Dynamic junction temperature estimation via builtin negative thermal coefficient (NTC) thermistor in high power IGBT modules," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2017, pp. 772–775.

- [49] H. Luo, J. Mao, C. Li, F. Iannuzzo, W. Li, and X. He, "Online junction temperature and current simultaneous extraction for SiC MOSFETs with electroluminescence effect," *IEEE Trans. Power Electron.*, vol. 37, no. 1, pp. 21–25, Jan. 2022.

- [50] L. Ceccarelli, H. Luo, and F. Iannuzzo, "Investigating SiC MOSFET body diode's light emission as temperature-sensitive electrical parameter," *Microelectron. Rel.*, vol. 88–90, pp. 627–630, 2018.

- [51] L. Zhang, P. Liu, S. Guo, and A. Q. Huang, "Comparative study of temperature sensitive electrical parameters (TSEP) of Si, SiC and GaN power devices," in *Proc. IEEE 4th Workshop Wide Bandgap Power Devices* Appl., 2016, pp. 302–307.

Henry A. Martin (Member, IEEE) received the M.Sc. degree in mechanical engineering from the Eindhoven University of Technology, Eindhoven, The Netherlands, in 2020. He is currently working toward the Ph.D. degree with the Electronic Components Technology and Materials Group, Delft University of Technology, Delft, The Netherlands.

He is also a Researcher with the Thermal High-Performance Packaging Program, Chip Integration Technology Center, Nijmegen, The Netherlands. His current research interests include prognostics for die

attachments, heterogeneous thermal solutions (integrated diamond heat spreaders and package-level active cooling), wide-bandgap device characterizations, packaging technologies for power, thermal simulations, and compact modeling.

**Edsger C. P. Smits** received the Ph.D. degree (*cum laude*) in organic electronics from the University of Groningen, Groningen, The Netherlands, in 2009.

He then joined the TNO Holst Centre, Eindhoven, The Netherlands, where he worked on oxide-based thin-film transistors for displays, flexible and stretchable sensors, and electronics for biomedical applications. He currently leads the power packaging activities with the Chip Integration Technology Center, Nijmegen, The Netherlands. His research interests include mini and micro-LED displays, laser transfer,

flexible and stretchable electronics, and chip packaging.

**René H. Poelma** (Senior Member, IEEE) received the Ph.D. degree (*cum laude*) from the Laboratory of Electronic Components Technology and Materials, Delft University of Technology, Delft, The Netherlands, in 2016.

He is currently a Senior Principal Engineer specializing in new packaging technologies, materials, simulation techniques, and processes with Nexperia BV, Nijmegen, The Netherlands. He is a Guest Researcher with the Department of Microelectronics, Delft University of Technology. His research interests include

advancing new packaging solutions, heterogeneous integration, and addressing challenges related to power density, device frequency, manufacturability, and reliability in high-demanding environments and applications.

Dr. Poelma is the IEEE Electronics Packaging Society Chair of Benelux Chapter 8.

Willem D. van Driel received the B.S. and M.S. degrees from the Eindhoven University of Technology, Eindhoven, The Netherlands, in 1992 and 1994, respectively, and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2007, all in mechanical engineering.

He has more than 25 years of track record in the reliability domain. His application areas range from health care, gas and oil explorations, and semiconductors. He is currently a Fellow Scientist with Signify NV (formerly Philips Lighting), Eindhoven. He is

also a Professor with the Delft University of Technology, Delft, The Netherlands. He is the Chair of the organizing committee of the IEEE International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems. He has authored and coauthored more than 350 scientific publications, including journals, conference papers, book or book chapters, and invited keynote lectures. His research interests include solid-state lighting, microelectronics and microsystems technologies, virtual prototyping, virtual reliability qualification, and designing for the reliability of microelectronics and microsystems.

**GuoQi Zhang** (Fellow, IEEE) received the Ph.D. degree in stability of composite structure from the Delft University of Technology, Delft, The Netherlands, in 1993.

He is a Member of the Netherlands Academy of Engineering, and a Chair Professor for "Micro/Nanoelectronics System Integration and Reliability" with the Delft University of Technology, Delft, The Netherlands . He chaired the "More than Moore" team of European's Technology Platform for micro/nanoelectronics and served as Co-Chair of

the Academic Council of the Dutch National Innovation Program on "Micro/nanoelectronics and embedded system." He was the NXP Senior Director of Technology Strategy and a Philips Research Fellow. His research interests include multilevel heterogeneous system integration and packaging, multiphysics and multiscale modeling and optimization of micro/nanoelectronics, digital twin and designing for reliability, and wide-bandgap semiconductors sensors and components.

Dr. Zhang is the founding Secretary-General of IEEE International Technology Roadmap of Wide-Bandgap Power Semiconductors.