**Delft University of Technology**

## Calibration Techniques for Power-efficient Residue Amplifiers in Pipelined ADCs

Sehgal, R.K.

DOI 10.4233/uuid:a6a5f8a8-e328-44d8-a265-dfe2b75a9bf8

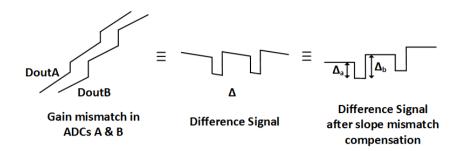

Publication date 2021

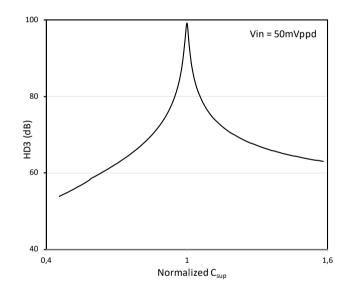

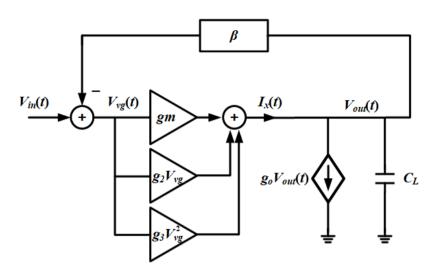

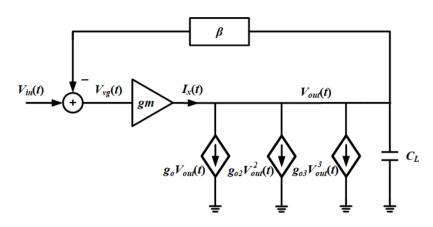

**Document Version** Final published version

Citation (APA)

Sehgal, R. K. (2021). Calibration Techniques for Power-efficient Residue Amplifiers in Pipelined ADCs. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:a6a5f8a8-e328-44d8a265-dfe2b75a9bf8

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# Calibration Techniques for Power-efficient Residue Amplifiers in Pipelined ADCs

# Calibration Techniques for Power-efficient Residue Amplifiers in Pipelined ADCs

Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus Prof.dr.ir. T.H.J.J. van der Hagen chair of the board of Doctorates to be defended publicly on Monday 5 July 2021 at 15:00 o'clock

by

Rohan SEHGAL Master of Science in Electrical Engineering, Delft University of Technology, the Netherlands born in New Delhi, India This dissertation has been approved by the promoters.

Composition of the doctoral committee:

| Rector Magnificus         | chairperson                                    |  |  |  |  |

|---------------------------|------------------------------------------------|--|--|--|--|

| Prof.dr.ir. K. Bult       | Delft University of Technology, promotor       |  |  |  |  |

| Prof.dr. K.A.A. Makinwa   | Delft University of Technology, promotor       |  |  |  |  |

| Independent members:      |                                                |  |  |  |  |

| Prof.dr.ir. L.C.N. Vreede | Delft University of Technology                 |  |  |  |  |

| Prof.dr. P.J.A. Harpe     | Eindhoven University of Technology             |  |  |  |  |

| Prof.dr. N. Sun           | Tsinghua University                            |  |  |  |  |

| Dr.ir. J. Craninckx       | IMEC Belgium                                   |  |  |  |  |

| Prof.dr.ir. W.A. Serdijn  | Delft University of Technology, reserve member |  |  |  |  |

| Other members:            |                                                |  |  |  |  |

| Dr.ir. F. van der Goes    | Broadcom Netherlands                           |  |  |  |  |

Keywords: CMOS, Pipelined Analog-to-Digital Converter, Discrete-time Amplifier, Digital Calibration, Linearization.Printed by: Ipskamp, Enschede

Copyright © 2021 by R. Sehgal

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

"Whatever can go wrong, will go wrong"

Edward A. Murphy Jr.

"There are no wrong notes in jazz"

Miles Davis

# Contents

| 1        | Intr                              | oduction 1                                                |  |  |  |  |

|----------|-----------------------------------|-----------------------------------------------------------|--|--|--|--|

|          | 1.1                               | Pipelined ADCs                                            |  |  |  |  |

|          | 1.2                               | Residue Amplifier                                         |  |  |  |  |

|          | 1.3                               | Thesis Objective                                          |  |  |  |  |

|          | 1.4                               | Thesis Organization                                       |  |  |  |  |

|          | Refe                              | rences                                                    |  |  |  |  |

| <b>2</b> | Review of Pipelined ADCs 9        |                                                           |  |  |  |  |

|          | 2.1                               | Pipelined ADC Architecture                                |  |  |  |  |

|          |                                   | 2.1.1 Sub-blocks                                          |  |  |  |  |

|          |                                   | 2.1.2 Sources of Error                                    |  |  |  |  |

|          | 2.2                               | ADC Error Reduction Techniques                            |  |  |  |  |

|          |                                   | 2.2.1 Digital Calibration                                 |  |  |  |  |

|          | 2.3                               | Conclusion                                                |  |  |  |  |

|          | Refe                              | rences                                                    |  |  |  |  |

| 3        | Analysis of Residue Amplifiers 27 |                                                           |  |  |  |  |

|          | 3.1                               | Settling Behavior of Discrete-time amplifiers             |  |  |  |  |

|          |                                   | 3.1.1 Noise                                               |  |  |  |  |

|          |                                   | 3.1.2 Distortion                                          |  |  |  |  |

|          | 3.2                               | Discrete-time Amplifiers with Negative Feedback           |  |  |  |  |

|          |                                   | 3.2.1 Gain Error                                          |  |  |  |  |

|          |                                   | 3.2.2 Noise                                               |  |  |  |  |

|          |                                   | 3.2.3 Distortion                                          |  |  |  |  |

|          | 3.3                               | Power Efficiency                                          |  |  |  |  |

|          |                                   | 3.3.1 SNR-limited case                                    |  |  |  |  |

|          |                                   | 3.3.2 SNR and Gain error-limited case                     |  |  |  |  |

|          | 3.4                               | Conclusion                                                |  |  |  |  |

|          | Refe                              | rences. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $52$ |  |  |  |  |

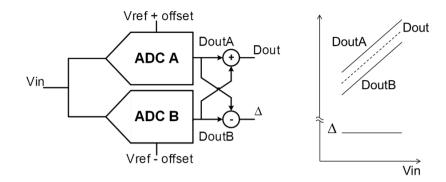

| <b>4</b> | $\mathbf{Spli}$      | t-ADC                    | C Calibration                         | 53  |

|----------|----------------------|--------------------------|---------------------------------------|-----|

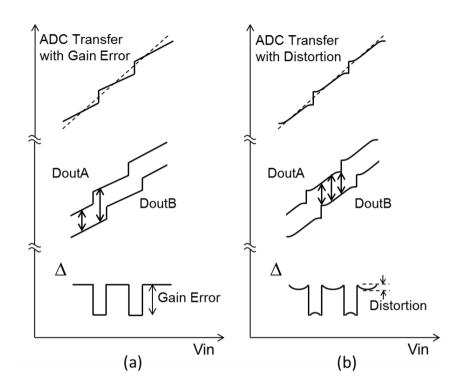

|          | 4.1                  | Split-A                  | ADC Calibration Principle             | 54  |

|          |                      | 4.1.1                    | Gain Error                            | 55  |

|          |                      | 4.1.2                    | Distortion                            | 58  |

|          |                      | 4.1.3                    | Mismatch between Split-ADCs           | 60  |

|          |                      | 4.1.4                    | Calibration Non-orthogonalities       | 61  |

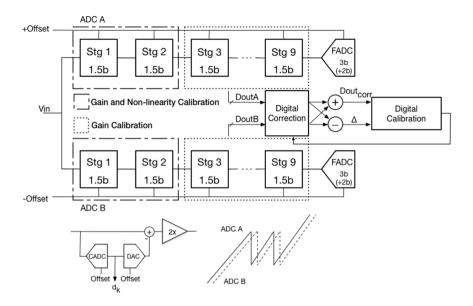

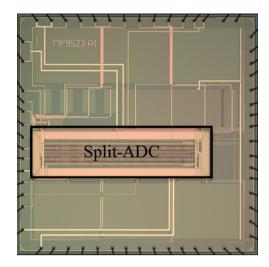

|          | 4.2                  | Protot                   | ype Split-ADC Implementation          | 62  |

|          |                      | 4.2.1                    | ADC Architecture                      | 62  |

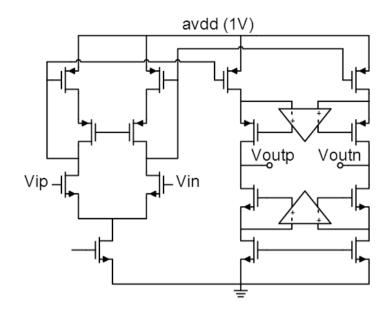

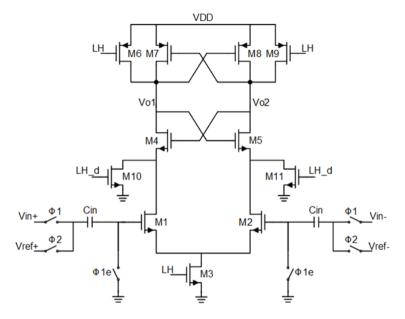

|          |                      | 4.2.2                    | Op-amp                                | 64  |

|          |                      | 4.2.3                    | Comparator                            | 65  |

|          |                      | 4.2.4                    | Analog Input Interface                | 66  |

|          | 4.3                  | Measu                    | rement Results                        | 66  |

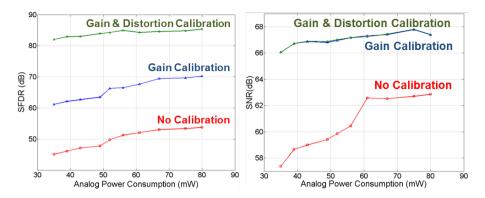

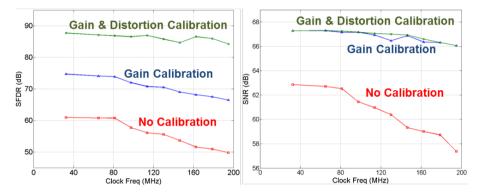

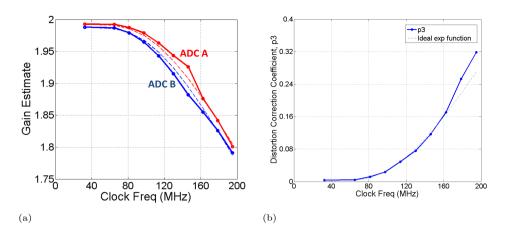

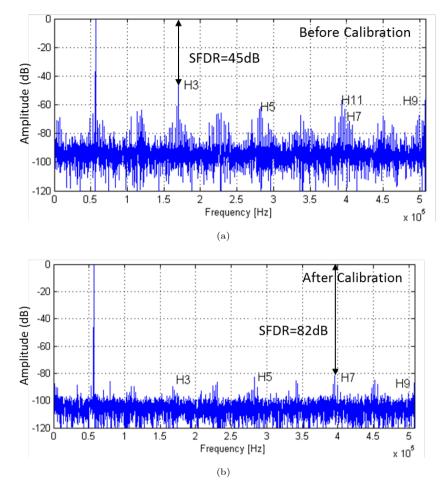

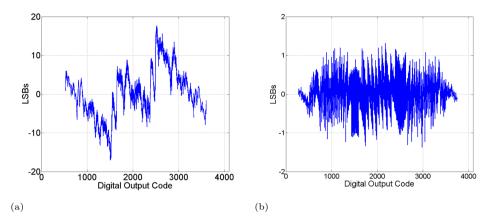

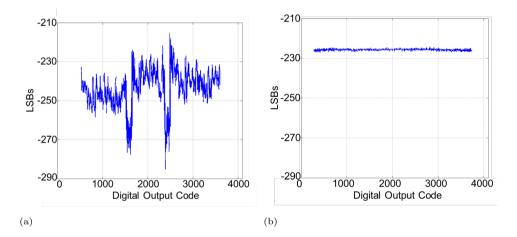

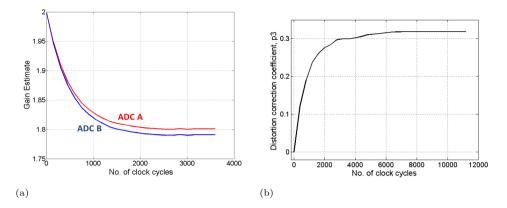

|          |                      | 4.3.1                    | Calibration Performance               | 71  |

|          | 4.4                  | Conclu                   | sion                                  | 72  |

|          | Refe                 | rences.                  |                                       | 73  |

| <b>5</b> | $\operatorname{Res}$ | idue A                   | mplifier with Analog Error Correction | 75  |

|          | 5.1                  | Analog                   | g Error Correction                    | 76  |

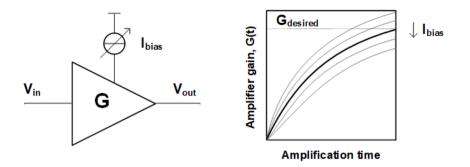

|          | 5.2                  | Gain I                   | Error Correction                      | 77  |

|          | 5.3                  | .3 Distortion Correction |                                       |     |

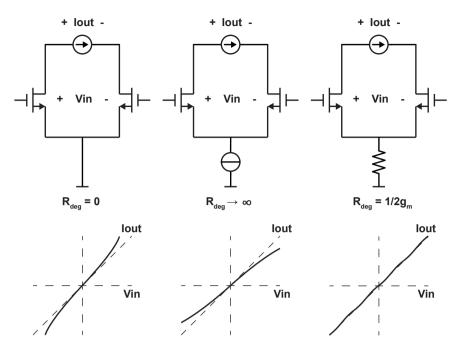

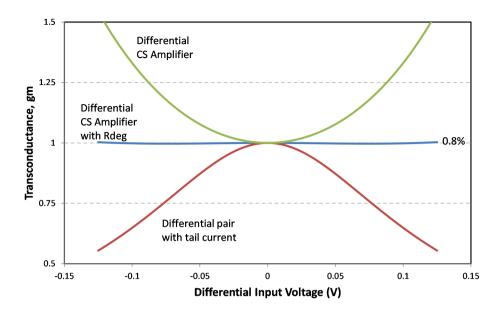

|          |                      | 5.3.1                    | Linearization Principle               | 81  |

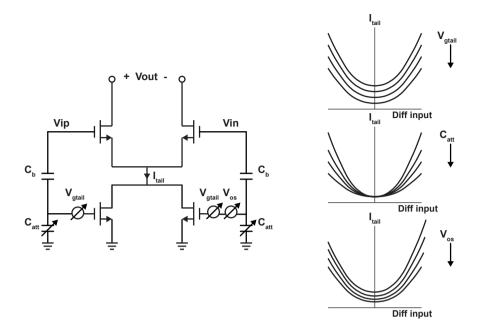

|          |                      | 5.3.2                    | Proposed Linearized Amplifier         | 84  |

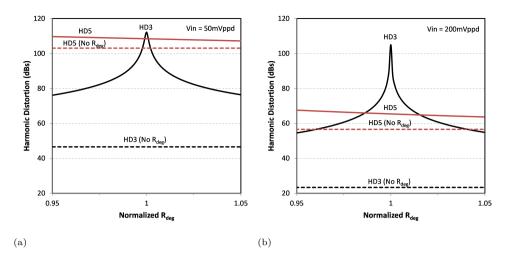

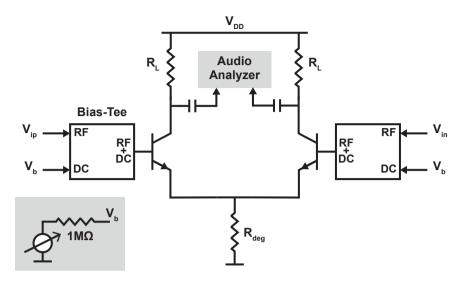

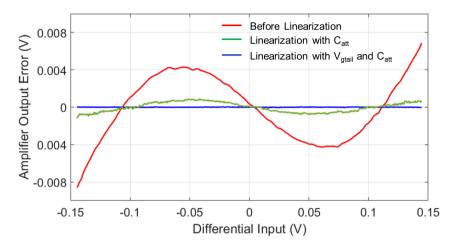

|          |                      | 5.3.3                    | Verification                          | 87  |

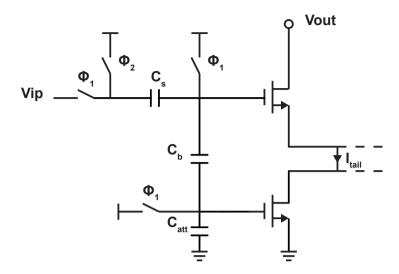

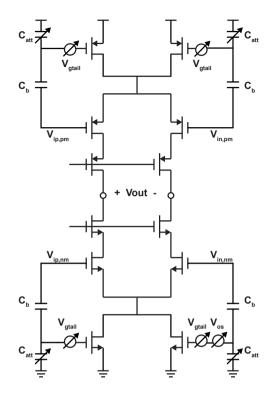

|          | 5.4                  | MOS I                    | Implementation                        | 89  |

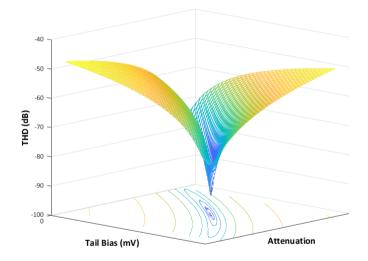

|          |                      | 5.4.1                    | Linearization Parameters              | 89  |

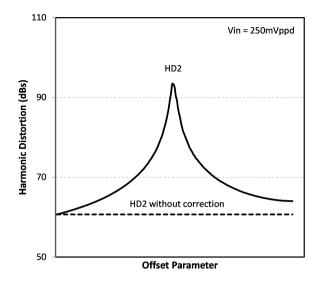

|          |                      | 5.4.2                    | Even-order Distortion                 | 93  |

|          | 5.5                  | Design                   | Considerations                        | 94  |

|          |                      | 5.5.1                    | Higher-order Effects                  | 95  |

|          |                      | 5.5.2                    | Noise                                 | 95  |

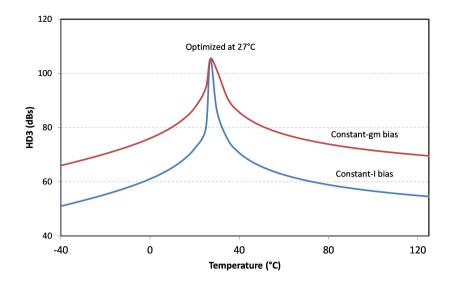

|          |                      | 5.5.3                    | Temperature Dependence                | 97  |

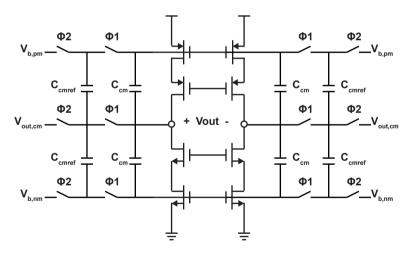

|          |                      | 5.5.4                    | Common-mode Rejection                 | 98  |

|          | 5.6                  | Power                    | Efficiency                            | 98  |

|          | 5.7                  | Conclu                   | 1sion                                 | 100 |

|          | Refe                 | rences.                  |                                       | 102 |

| 6                      | $\mathbf{A} \mathbf{S}$ | plit-ADC with a Linearized Integrating Amplifier                                  | 105 |  |  |

|------------------------|-------------------------|-----------------------------------------------------------------------------------|-----|--|--|

|                        | 6.1                     | ADC Architecture                                                                  | 106 |  |  |

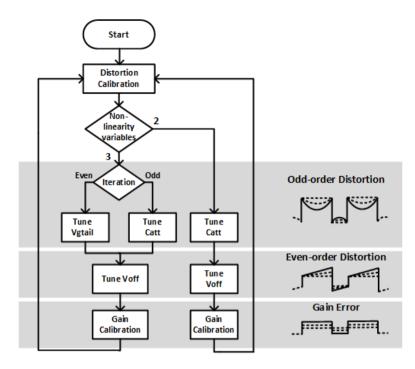

|                        |                         | 6.1.1 Calibration Architecture                                                    | 107 |  |  |

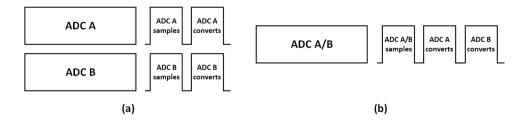

|                        |                         | 6.1.2 "Split-over-time"-ADC $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 109 |  |  |

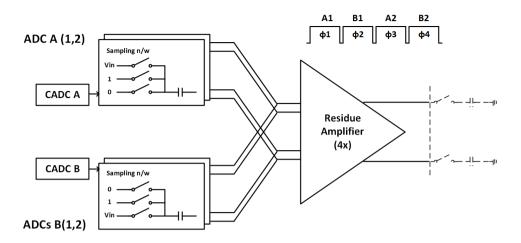

|                        | 6.2                     | ADC Implementation.                                                               | 111 |  |  |

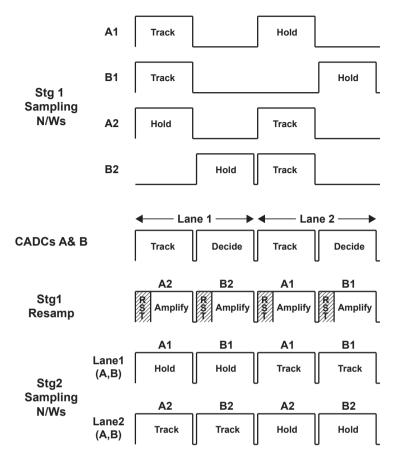

|                        |                         | 6.2.1 Timing                                                                      | 111 |  |  |

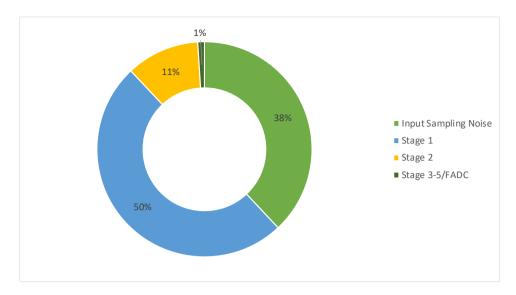

|                        |                         | 6.2.2 Noise Budget                                                                | 112 |  |  |

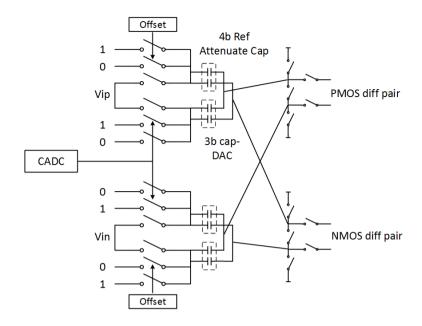

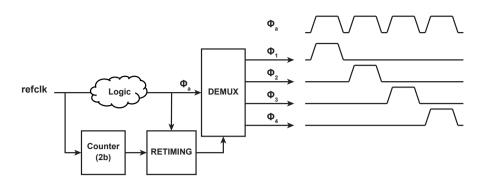

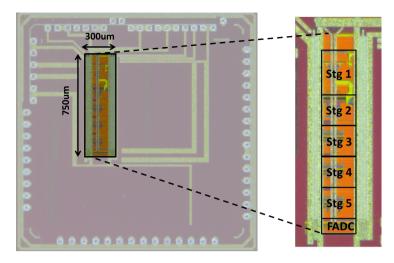

|                        |                         | 6.2.3 ADC Sub-blocks                                                              | 115 |  |  |

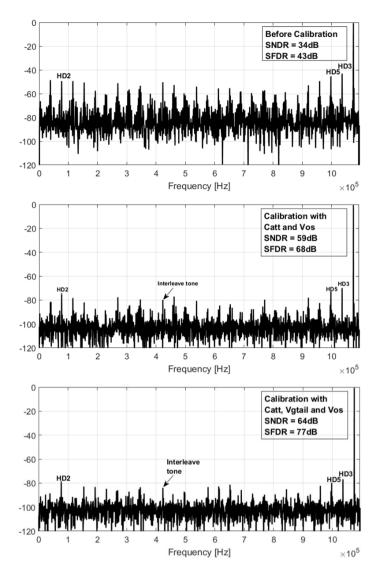

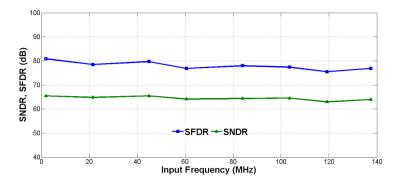

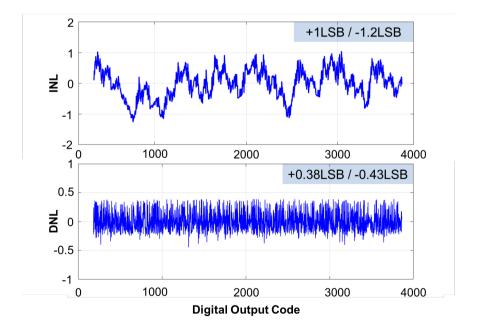

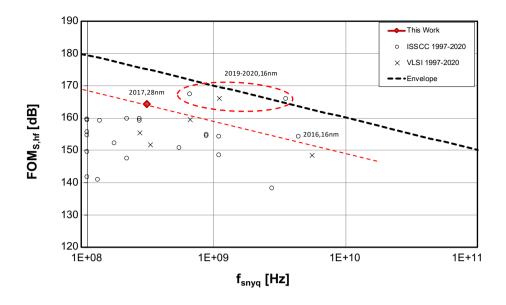

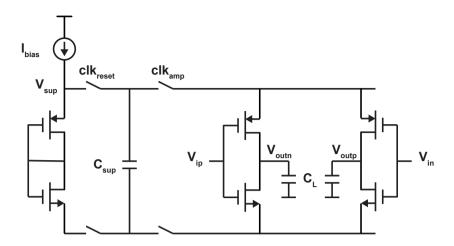

|                        | 6.3                     | Measurement Results                                                               | 120 |  |  |

|                        | 6.4                     | Conclusion                                                                        | 125 |  |  |

|                        | Refe                    | rences                                                                            | 126 |  |  |

| 7                      | Con                     | clusions                                                                          | 129 |  |  |

|                        | 7.1                     | Main Findings                                                                     | 129 |  |  |

|                        | 7.2                     | Future Scope of Work                                                              | 132 |  |  |

|                        | Refe                    | rences                                                                            | 136 |  |  |

| AF                     | PEN                     | NDICES                                                                            | 138 |  |  |

|                        |                         |                                                                                   |     |  |  |

| Α                      |                         | pendix                                                                            | 139 |  |  |

|                        |                         | Open-loop Amplifier Distortion Analysis                                           |     |  |  |

|                        |                         | Closed-loop Amplifier Distortion Analysis.                                        |     |  |  |

|                        | Refe                    | rences                                                                            | 146 |  |  |

| В                      | App                     | pendix                                                                            |     |  |  |

| Su                     | Summary                 |                                                                                   |     |  |  |

| Sa                     | Samenvatting            |                                                                                   |     |  |  |

| Ac                     | Acknowledgments         |                                                                                   |     |  |  |

| $\mathbf{Lis}$         | List of Publications    |                                                                                   |     |  |  |

| $\mathbf{A}\mathbf{b}$ | About the Author        |                                                                                   |     |  |  |

1

# Introduction

Major advances have been made in telecommunications over the last two decades, which have resulted in one of the most disruptive technologies of our times – the internet. The demand for internet has led to a proliferation of wireline and wireless network infrastructure around the globe, with new generations being adopted every few years. During the course of this doctoral research alone, we have seen the wireless networks evolve from 3G to 4G and now to 5G. This growth in connectivity across the world has transformed how economies, societies and geopolitics function. High bandwidth networks have allowed corporations to operate seamlessly across borders, made social media, e-commerce and cryptocurrencies ubiquitous and given countries more tools to interfere in each other's democratic processes. For better or for worse, this explosion in networking and the internet has unalterably changed the world and a significant part of this has been fueled by innovation in wireline and wireless technologies.

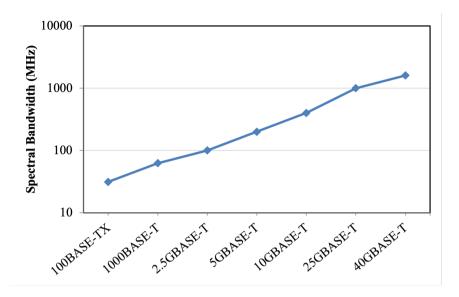

Focusing on wireline transceivers in Ethernet physical layer interface (PHY) chips, the industry has transitioned from 10BaseT to 10GBaseT in the space of 20 years, with 25GBaseT now on the horizon. This >1000x improvement in throughput is also reflected in the spectral bandwidth, which has grown exponentially, as shown in Figure 1.1. To accomplish this, a lot of work has gone into improving each aspect of the Ethernet PHY, ranging from cables and magnetics to system-level innovation. However, the onus of driving this trend has largely been on the analog front-ends,

Figure 1.1: Ethernet standards with input spectral bandwidth specification

which have become faster and more precise while consuming less power, allowing the use of more complex modulation schemes to make the most out of the available channel bandwidth.

## 1.1. PIPELINED ADCs

Looking at the 10GBaseT PHY implementations, for example, nearly all the PHYs on the market use an ADC with >9.5b ENOB, sampling at a rate of at least 800MS/s. To achieve such high sampling rates while maintaining a high resolution, primarily two techniques are employed – time-interleaving [1] and pipelining [2]. In time-interleaved ADCs, multiple ADC lanes are used in parallel to digitize the input signal. By sampling the signal sequentially, N number of ADC lanes can collectively sample the input signal at N times the rate of a single lane. While simplifying the design of the individual lane, time-interleaving imposes serious penalties on the overall ADC performance. Using multiple ADC lanes in parallel increases the load seen by the preceding buffer (or sample-and-hold) proportionally. In addition, any kind of mismatch between the ADC lanes – gain, timing and offset – generates spurious tones in the combined ADC output, severely limiting the overall ADC resolution. These two factors place a critical limitation on the number of lanes that can be interleaved to realize high-speed ADCs.

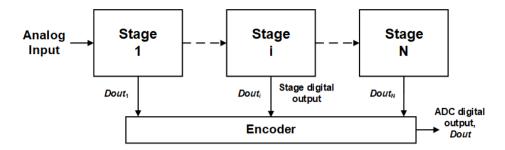

Figure 1.2: Pipelined ADC architecture

The other alternative, pipelining, does not suffer from either of the above drawbacks, making it a very attractive option. As shown in Figure 1.2, pipelining involves breaking the signal quantization process into multiple steps that can be implemented by multiple stages operating concurrently. Each stage now resolves a few bits, and passes on the remaining unquantized signal, or the residue, to the next stage. Considering that each stage is resolving only a few bits, the stages can be simplified and operated at a faster speed, allowing the ADC to achieve faster overall sampling rates at the cost of only increased data latency.

One of the key techniques that enable pipelining is residue amplification. In order to relax the noise requirements for later stages, amplifiers are used to boost the residue signal from the preceding stages. Since any amplifier non-ideality will corrupt the residue transferred to the following stages, the accuracy of the residue amplifier directly determines the accuracy of the ADC. Because of this, it often ends up being one of the most critical and power-hungry blocks in the signal chain.

#### 1.2. Residue Amplifier

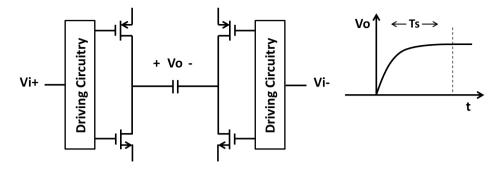

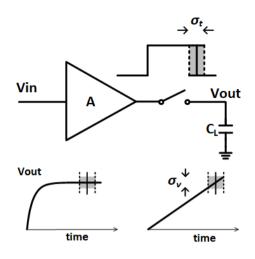

A lot of research has been undertaken on designing power efficient residue amplifiers, resulting in many innovative topologies. The common denominator in all these topologies, however, is the basic amplifier core, which can be described in its simplest form as four transistors charging a load capacitor in a fixed interval of time, as shown in Figure 1.3. These transistors are driven by a signal derived from the differential input and charge the capacitor to a differential output voltage with a certain amount of gain. The accuracy of this gain is usually limited by two constraints –

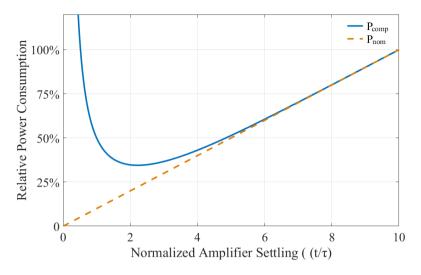

• Settling time: As most analog-to-digital converters operate on a sampledand-held voltage input, the residue amplifier is usually a discrete-time circuit.

Figure 1.3: Core amplifier with circuit overhead and settling

Since the amplifier is normally reset prior to amplification, it takes a certain amount of time for the amplifier output voltage to reach its final value. If the amplifier is considered to be a single-pole system, its output voltage typically experiences an exponentially settling behavior. Hence, as the settling time for the amplifier is increased, the gap between its output voltage to its final steady-state desired value reduces. However, as most amplifiers are class-A, which burn a fixed amount of current during every instant of amplification, a longer settling time invariably results in higher power dissipation.

• **Circuit overhead:** Since the gain of the open-loop four-transistor core amplifier will vary over Process, Voltage and Temperature (PVT) variations beyond the desired accuracy requirements of a residue amplifier, some circuit overhead has to be used to improve the accuracy of the amplifier. Traditionally, this overhead has been in the form of high-gain amplifier stages and negative feedback, which, together, can provide a very accurate gain and low distortion. This, however, comes at the expense of significantly higher power dissipation.

The power efficiency of the residue amplifier will essentially be determined by how this core amplifier is utilized. Hence, we need to find solutions that allow us to use the core amplifier with the lowest possible settling and circuit overhead while achieving the desired gain accuracy.

There are several error sources in an amplifier that could degrade the accuracy of residue amplification in a pipelined ADC. The most significant of these are noise, linear gain error and distortion. Although all of these error sources limit the ADC dynamic range, they have significantly distinct characteristics and need to be tackled differently. Due to its stochastic nature, noise poses a fundamental limit on the ADC accuracy and, although certain choices can be made at architectural level to optimize it, we have to scale up a design and its power dissipation in order to achieve a certain noise performance.

Absolute gain error and distortion, on the other hand, are more deterministic and can be suppressed in multiple ways. As mentioned previously, a classic approach is to use negative feedback with a very high loop-gain. However, this approach results in a very large circuit overhead and requires a lot of settling. Another more recent approach to achieve accurate residue amplification is to combine the amplifiers with some form of digital calibration. By fixing the errors in digital post-processing, the specifications on the residue amplifiers can be significantly relaxed. Considering that device scaling has made digital processing available at an increasingly lower footprint, this exchange of analog complexity for digital processing generally results in a lower overall ADC area and power dissipation. As a result, a lot of work has been published on utilizing digital calibration to fix the linear gain error and distortion arising from the residue amplifier, and achieving a much improved ADC figure of merit (FoM).

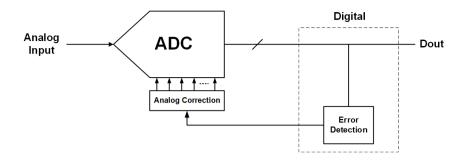

While digital calibration does shift some of the circuit overhead from the amplifier, it has certain limitations. The digital calibration can be broken into two parts – error *detection* and *correction*. While the error detection logic can be run at a slow rate, the error correction part of the calibration has to run at the full ADC speed. For high speed and high resolution correction logic, the area and power consumption can be significant.

Another major constraint of digital calibration is its finite resolution. The accuracy of digital correction is limited by the backend resolution. For a perfect calibration of distortion in an ADC stage's residue signal, a precise estimate of the residue is required from its backend. And any imperfection in the backend will have a detrimental impact on the calibration accuracy. Furthermore, a residue amplifier with a significant amount of gain error and distortion will usually lead to a loss in the ADC dynamic range, something that cannot be restored through calibration.

#### 1.3. Thesis Objective

As discussed above, while digital calibration is an excellent way of realizing accurate residue amplifiers, it does suffer from certain limitations. This means that digitally assisted residue amplifiers can only go so far in improving the residue amplifier power efficiency, and we need to investigate more ways to further push the envelope.

If we shift the error correction to the analog domain, while keeping the error

detection in digital, we draw upon the best of both worlds. By using error estimation in digital along with a deterministic calibration method with fast convergence, the digital logic can be duty cycled to render its power consumption negligible. And more importantly, with the help of analog correction, we fix errors at the source, achieving a better calibration accuracy and a higher ADC dynamic range. Also, with analog-domain linearization, we can use much more power efficient amplifier topologies at much larger input swings which would not be possible solely with digital post-processing due to their high inherent nonlinearity.

In this thesis, we try to find the optimum design for digitally assisted residue amplifiers, by adopting a two-pronged approach –

- 1. Using very simple amplifier structures closely resembling the basic core amplifier along with low settling accuracy, with the help of linearization in the analog domain, and

- 2. a deterministic calibration architecture which allows us to calibrate linear gain errors and distortion in background while achieving a fast convergence

### 1.4. THESIS ORGANIZATION

The rest of the thesis is organized as follows. Chapter 2 provides an overview of pipelined ADCs and their main ADC sub-blocks. We also discuss the major sources of error in these sub-blocks and their impact on the ADC performance, along with a brief introduction to digital calibration and how it can be used to relax the design restrictions on these sub-blocks.

In Chapter 3, the settling behavior of discrete-time amplifiers is analyzed in detail. By looking at how noise and distortion vary in a discrete-time amplifier, we can identify design strategies to optimize their power consumption for achieving the best possible dynamic range.

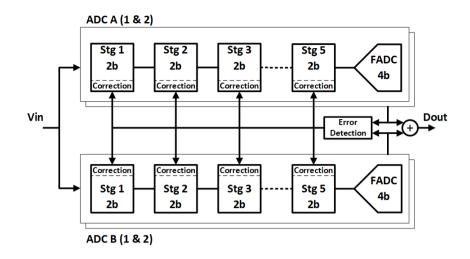

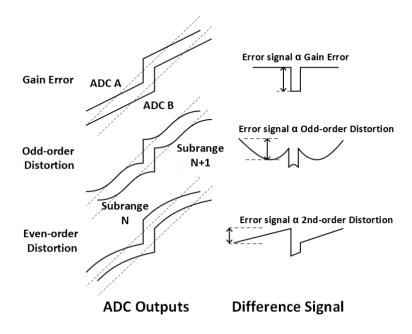

Chapter 4 discusses the split-ADC calibration architecture, and how it can be used to calibrate gain and non-linearity errors emanating from the residue amplifier. A prototype split-ADC was implemented and its measurement results are presented to demonstrate the effectiveness and convergence speed of the calibration algorithm.

In Chapter 5, we discuss the principles of analog correction of amplifier gain and distortion, and some amplifier topologies based on analog linearization. The proposed amplifier topology is implemented as part of a custom split-ADC, whose architecture and circuit details are presented in Chapter 6, along with the ADC measurement results. Finally, Chapter 7 concludes the thesis, summarizes the original contributions of this dissertation and outlines future scope of work.

## References

- W. C. Black and D. A. Hodges, "Time interleaved converter arrays," *IEEE J. Solid-State Circuits*, vol. 15, pp. 1022–1029, Dec. 1980.

- [2] S. H. Lewis and P. R. Gray, "A pipelined 5MHz 9b ADC," in ISSCC Dig. of Tech. Papers, 1987.

# 2

# **Review of Pipelined ADCs**

This chapter presents an overview of the pipelined ADC architecture. We will briefly review the operation of a pipelined ADC and of all its major sub-blocks, and the effect of their nonidealities on the ADC resolution.

One of the attributes that truly distinguishes pipelined ADCs from other ADC architectures is residue amplification, and the residue amplifier often occupies a significant portion of an ADC's error and power budget. Over the last two decades, several techniques have been proposed to relax the design requirements on the residue amplifier and simplify their design. We will review some of the prominent error correction techniques published in the literature in recent years, with a major focus on digital calibration.

# 2.1. PIPELINED ADC ARCHITECTURE

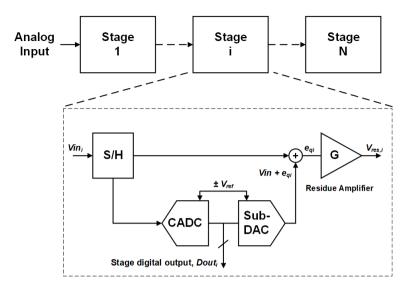

In a pipelined ADC, the quantization of the sampled input signal is performed over a cascade of multiple stages, as shown in Figure 2.1. Each stage consists of a coarse ADC which digitizes the input signal,  $V_{\text{in},i}$ , based on the ADC references,  $\pm V_{\text{ref}}$ , with a certain resolution,  $N_i$ . The coarse estimate of the signal,  $D_{\text{out},i}$ , is then subtracted from the input signal with the help of a sub-DAC and the remaining portion of the input signal, the residual quantization error,  $e_{qi}$ , is passed on to the next stage for further quantization. This residual quantization error can essentially

Figure 2.1: Pipelined ADC architecture overview

be expressed as -

$$e_{qi} = V_{\text{in},i} - D_{\text{out},i} \left(\frac{V_{\text{ref}}}{2^{N_i}}\right)$$

(2.1)

where  $D_{\text{out},i}(V_{\text{ref}}/2^{N_i})$  is the coarse ADC's output mapped onto the ADC reference voltage by the sub-DAC. Once the subsequent stage has sampled and started quantizing this residual signal, the previous stage is free and can be used to convert the next input signal sample. By operating the stages concurrently, the sampling speed of the overall ADC can be the same as that of each stage, while the overall ADC resolution equals the total number of bits resolved by all the stages. This allows pipelined ADCs to operate at high speeds without incurring limits on resolution or exponential growth in area, albeit at the expense of additional latency.

As the signal gets quantized through the stages, the number of bits left to be resolved reduces. However, the magnitude of the residual quantization error passed on from one stage to the next also decreases. This means that each stage needs to be designed with the same dynamic range. To relax the resolution required from later stages, some gain,  $G_{a,i}$ , can be added within each stage to scale up the residual signal to the full-scale range. The resulting amplifier output, the stage residue,  $V_{\text{res},i}$ , can be expressed as –

$$V_{\text{res},i} = G_{a,i}e_{qi} = G_{a,i}\left(V_{\text{in},i} - D_{\text{out},i}\left(\frac{V_{\text{ref}}}{2^{N_i}}\right)\right)$$

(2.2)

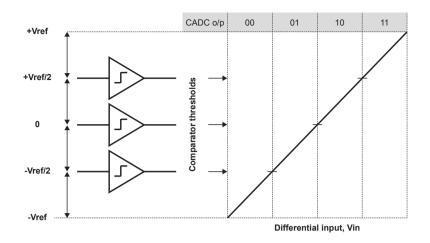

Figure 2.2: 2-bit Flash-type coarse ADC

Equation (2.2) basically represents the transfer function of the pipeline ADC stage, and shows how the stage residue voltage that is passed on to the subsequent stages for further quantization is scaled up to the full-scale input range. Due to this, the LSB size for the subsequent pipeline ADC backend also increases by the same gain. This lowers the resolution requirements for the latter stages, allowing them to be scaled down to optimize the overall ADC power dissipation.

#### 2.1.1. Sub-blocks

Each stage in a pipelined ADC (excluding the backend) consists of three primary building blocks – coarse ADC, sub-DAC and the residue amplifier. In this subsection, we will briefly review the operation of these three blocks.

a. **Coarse ADC:** The coarse ADC (CADC) samples and performs quantization on the input signal. Since the digitization in a pipelined ADC is spread over multiple stages, the coarse ADC is normally a low-resolution quantizer. Traditionally, the coarse ADCs used in the pipelined ADCs have been implemented using the flash architecture [1]. This is because for low resolution and highspeed, flash ADCs can be a good choice due to their simplicity. Figure 2.2 shows the transfer characteristic for a flash-type coarse ADC designed for a 2b/stage pipelined ADC.

Recently, SAR ADCs are increasingly being used as coarse ADCs due to their lower circuit overhead and power dissipation [2, 3]. This is because in advanced

technology nodes, SAR ADCs have been shown to be fast enough to be used for pipelining in high-speed ADCs. And since they require less analog circuitry than flash ADCs, SAR ADCs are generally more power efficient. These pipelined SAR ADCs have demonstrated excellent figures of merit (FoM) and show a lot of promise for high-speed medium-resolution applications in finer technology nodes. However, in the course of this thesis, the flash architecture was preferred for implementing the CADC due to its lower complexity and ease of design.

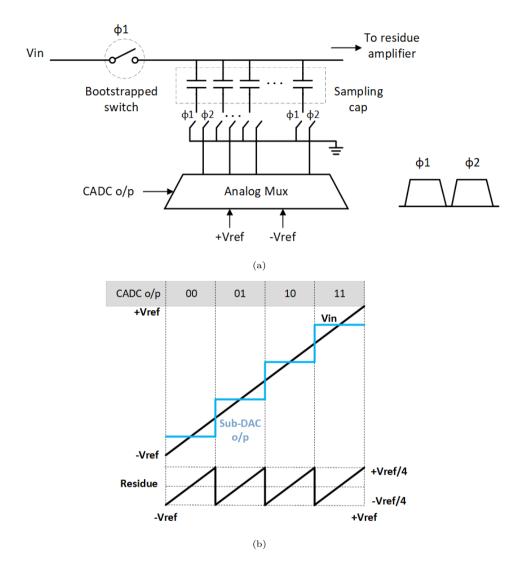

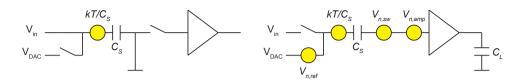

b. **Sub-DAC:** In order to generate the residue signal for subsequent stages, the CADC's output,  $D_{\text{out},i}$ , needs to be subtracted from the stage input signal. The sub-DAC is primarily used to generate the analog equivalent of the CADC's digital output, which can then be subtracted from the input signal. The most common sub-DAC topology employs a capacitive DAC, which can also be used to sample and hold the input signal, as shown in Figure 2.3(a). The cap-DAC is operated in two phases – during the track phase, it tracks and samples the input signal on the cap-DAC unit capacitors. In the hold phase, the unit capacitors of the DAC are connected to the positive and negative reference voltages based on the coarse ADC's estimate. Through charge redistribution, the residual quantization error, as shown in Figure 2.3(b), is generated on the top-plate of the cap-DAC.

The cap-DAC size is instrumental in determining the performance specifications of all the circuits around it – top- and bottom-plate switches, reference buffer and the residue amplifier – and the ADC stage itself. Since the cap-DAC is used for sampling the input signal, its total capacitance is determined by the kT/C noise limit and the ADC noise budget reserved for it. Apart from the noise budget, the entire sampling network also has to meet the bandwidth and linearity requirements. The top-plate sampling switch experiences the largest signal swing and is often the most challenging switch to design. Usually, some form of clock boosting has to be used to meet its linearity requirements. The bottom-plate switches are relatively simpler and are designed primarily to have low parasitic capacitance. These switches can be simplified by using reference attenuation. By switching only a part of the sampling capacitance to the reference voltages, the ADC reference voltages are effectively attenuated. This allows the use of larger voltages, such as the supply rails, as the two ADC reference voltages, making it easier to drive the switches.

Figure 2.3: Capacitive sub-DAC architecture along with its output and residue voltage

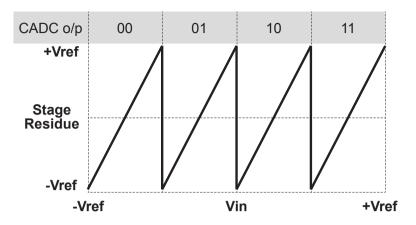

c. Residue Amplifier: As the signal passes through successive stages, the residue gets progressively smaller. In order to simplify the dynamic range requirements for the later stages, pipelined ADCs usually include some form of inter-stage residue amplification. To maintain the same signal swing for all the stages, ideally, the residue amplifier gain,  $G_{a,i}$ , should be equal to  $2^{N_i}$ , where  $N_i$  is the number of bits resolved by that stage's coarse ADC. The stage residue w.r.t input signal is shown in Figure 2.4 for a 2-bit pipelined stage,

Figure 2.4: Residue amplifier output w.r.t input signal,  $V_{in}$

with a gain of 4x.

This stage gain is eventually taken into account when the stage output bits are combined in the digital encoder. The digital inverse of the ADC stage transfer function in (2.2) can be formulated to calculate the digital equivalent of the stage input,  $D_{in,i}$ , by using the digital encoder gain,  $G_{d,i}$ , of the *i*-th ADC stage along with the backend ADC code as –

$$D_{\mathrm{in},i} = D_{\mathrm{out},i} + \frac{D_{\mathrm{res},i}}{G_{\mathrm{d},i}}$$

(2.3)

where  $D_{\text{res},i}$  is the backend ADC code for the *i*-th stage and is essentially the digital representation of its output residue voltage calculated in (2.2). If we ignore the quantization error in  $D_{\text{res},i}$ , then Equations (2.2) and (2.3) can be combined as -

$$D_{\mathrm{in},i} = D_{\mathrm{out},i} + \frac{G_{\mathrm{a},i}}{G_{\mathrm{d},i}} \left( V_{\mathrm{in},i} - D_{\mathrm{out},i} \left( \frac{V_{\mathrm{ref}}}{2^{N_i}} \right) \right)$$

(2.4)

As seen from (2.4), by accurately matching the digital gain in the encoder with the analog gain in the ADC stage, the ADC stage digital outputs can be combined to produce the ideal digitized input.

#### 2.1.2. Sources of Error

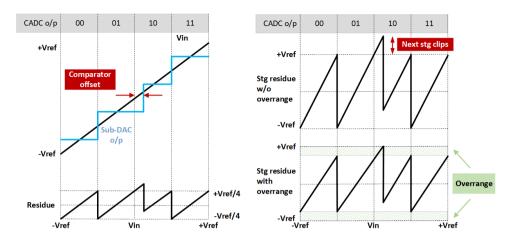

As shown earlier in Figure 2.2, the comparator thresholds in the CADC are placed to divide the ADC input range into four equal subranges. Based on the subrange the

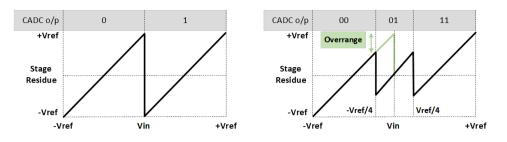

Figure 2.5: The effect of comparator offset in a CADC on a pipeline ADC stage with and without overrange

input signal is present in, the corresponding sub-DAC voltage level is selected. This sub-DAC output is subtracted from the sampled input and the resulting residue is amplified by the residue amplifier to generate the residue signal for the next stage.

Since each block serves a different purpose in a pipeline stage, any non-idealities in these sub-blocks have a distinct impact on the ADC performance. In this subsection, we will discuss some of the major sources of errors in these three pipelined ADC sub-blocks and how they can cause errors in the overall ADC output code.

a. **Coarse ADC:** Since the generation of the residue relies on the CADC's estimate of the input signal, any inaccuracies in the comparator thresholds will affect the stage residue signal. The primary source of error in CADC is often the comparator offset, which shifts the ADC subranges, as illustrated in Figure 2.5. As this shift in the ADC subrange is not taken into account by the sub-DAC or the residue amplifier, this can push the output of the residue amplifier outside the input range of the next stage, while saturating the amplifier itself. This can lead to missing codes in the ADC output.

In order to relax the comparator offset requirements, some redundancy can be added to the subranges of the pipelined stage in the form of overrange. This can be done by reducing the residue amplifier gain a bit to create some spare headroom for CADC offset. In the example shown in Figure 2.5, the amplifier gain for the 2-bit stage is reduced from its ideal value (4x) in order to create the overrange. A lower gain ensures that, in the presence of any offset in the

Figure 2.6: Comparison of stage residue signal in 1-bit vs 1.5-bit/stage

CADC, the stage residue will stay within the range of the next pipeline stage.

Another way of creating overrange is by adding extra comparators in the CADC to reduce the nominal input of the residue amplifier. One of the most popular architectures imbibing this method is the 1.5-bit/stage pipelined ADC [4]. In this architecture, an extra comparator is added to a nominally 1-bit ADC stage, with a residue amplifier gain of 2x. By strategically placing the comparator thresholds, an overrange of  $V_{\rm ref}/2$  (and a redundancy of 0.5bit) is created, as shown in Figure 2.6. This allows for the comparators to have an input-referred offset of up to  $\pm V_{\rm ref}/4$  without saturating the next stage.

It should be noted that adding redundancy does not correct the errors arising due to the comparator offset, but only makes the ADC sufficiently tolerant of these errors. While the presence of overrange significantly relaxes the comparator requirements, it does incur a power penalty. Since the ADC resolution is a function of the overall gain seen in the pipeline chain, adding redundancy by reducing stage gain also reduces the ADC resolution. Similarly, increasing the resolution of the CADC without changing the stage gain will have no effect on the ADC resolution. However, the circuit overhead introduced by the addition of overrange is significantly smaller compared to the relaxation achieved in comparator design, making it a widely used technique to optimize ADC design.

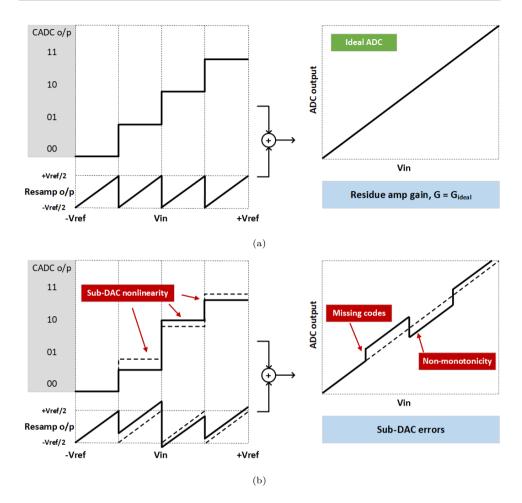

b. **Sub-DAC:** As the stage residue comprises of the sampled input and the sub-DAC output, any nonlinearity in the sub-DAC output will directly show up in the stage residue. This DAC nonlinearity could originate due to, for instance, mismatch between the unit capacitors in the capacitive-DAC. The effect of sub-DAC nonlinearity is illustrated in Figure 2.7 which compares the ADC output transfer curve of an ideal ADC with that of an ADC with a nonlinear

Figure 2.7: ADC output transfer for (a) an ideal ADC and (b) an ADC with nonlinear sub-DAC

sub-DAC. The ADC output curve is obtained by combining the CADC output of the pipelined ADC stage with the stage residue. In the ideal ADC, as shown in Figure 2.7(a), the sub-DAC output levels are perfectly linear. As a result, the ADC subranges align perfectly after encoding the stage residue with the stage CADC bits. Any nonlinearity in the sub-DAC output levels will shift the subranges of the stage residues as shown in Figure 2.7(b). This misalignment amongst the ADC subranges creates abrupt jumps in the ADC output code as the input signal transitions between the ADC subranges. These jumps can cause significant harmonic distortion and potentially missing codes and non-monotonicity in the ADC transfer characteristic. In order to prevent any missing codes or non-monotonicity, the abrupt jumps caused by these misalignments need to be lower than  $\pm \frac{1}{2}$  LSB of the ADC. This requirement can be used to define the maximum error allowed in the sub-DAC of the *i*-th stage of a pipeline ADC,  $\delta_i$ , as [5] -

$$|\delta_i| \le \frac{FS}{2^{1+r_i}} \tag{2.5}$$

where FS is the full-scale range of the ADC and  $r_i$  is the combined resolution of *i*-th stage and the later stages.

c. **Residue Amplifier:** The residue amplifier scales up the residue of the current stage to the full-scale range of the next stage's quantizer. Since it is directly in the signal path, its non-idealities have a pivotal effect on the quality of the ADC output. The most significant amplifier non-idealities are offset, gain error, distortion. The residue amplifier's offset will have two effects. The ADC output code will contain the cumulative offset from the residue amplifiers in all the stages. Since a lot of applications do not place any restrictions on the ADC offset, the cumulative offset is normally not an issue. The main drawback of the amplifier offset is that it shifts the stage residue, hence, consuming part of the stage overrange.

The residue amplifier gain has much more stringent requirements. It has to match the radix used in the encoder to combine the bits from the ADC stages. Any deviation in the amplifier gain from that radix value creates a misalignment amongst the subranges at the CADC transitions, leading to errors in the ADC output code, as illustrated in Figure 2.8, which shows the discontinuities in the ADC output transfer function arising from gain error and amplifier nonlinearity. The specification for the residue amplifier gain error can again be derived by using the same method as the sub-DAC, resulting in -

$$|\sigma_i| \le \frac{1}{2^{1+r_{i+1}}} \tag{2.6}$$

where  $\sigma_i$  is the relative gain error in the *i*-th stage and  $r_{i+1}$  is the combined ADC resolution remaining after the *i*-th stage.

Figure 2.8: Effect of amplifier (a) gain error and (b) nonlinearity on ADC output code

# 2.2. ADC Error Reduction Techniques

Considering the accuracy requirements on the residue amplifier discussed in the previous section, using a conventional high-gain high-bandwidth closed-loop amplifier topology for a high-speed high-resolution pipelined ADC could be very expensive in terms of area, complexity and power consumption. In this section, we will focus on alternative, more efficient strategies for reducing the ADC errors due to amplifier non-idealities.

As the residue amplifier is one of the most power-hungry blocks inside the pipelined ADC, it has been the subject of extensive research over the last three decades. Several techniques have been proposed to relax the requirements from residue amplifiers. These can broadly be divided into three groups. The first involves the use of analog techniques that allow the amplifier to achieve the required gain and linearity performance without using multiple high-gain stages. Some of the examples include gain-boosting [6], correlated double sampling (CDS) [7], correlated level shifting (CLS) [8], virtual ground reference buffers (VGRB)[9], etc. When compared to a conventional high gain high linearity opamp, these techniques often result in significant power savings and a much simpler amplifier. However, all these techniques incur certain penalties. Gain-boosting is an extremely effective technique to increase the DC gain of the amplifier. However, power still needs to be spent on increasing the amplifier bandwidth to make the most of the higher DC gain. Both CDS and CLS introduce an additional phase of amplification in order to sample the error signal from the first amplification (called the estimation) phase. In the VGRB technique, the reference buffers used to drive the cap-DAC in the amplification phase are referenced to the virtual ground of the closed-loop amplifier instead of the system ground. This effectively bootstraps the entire capacitance of the cap-DAC, removing it from the feedback network of the opamp and theoretically resulting in a feedback factor of 1. However, this improvement in the feedback factor is seriously limited by the gain of the reference buffer and the additional parasitics added by the reference buffers.

In a conventional opamp-based charge amplifier, the charge transfer from the sampling capacitor to the load capacitor settles exponentially and it concludes when the opamp's virtual ground signal reaches zero. Many designs have been published which have tried replacing these conventional op-amps with alternative circuits. These circuits, like zero-crossing based circuits (ZCBC) [10–12], ring amplifiers [13], pulse bucket brigade [14], charge pumps [15], etc, exhibit higher power efficiency because, instead of exponential settling, they rely on slew-based charging. For instance, in the ZCBC technique, instead of an amplifier, a current source is used to charge the load capacitor, with a high-precision comparator monitoring the zero-crossing point. This approach allows the amplification to be essentially open-loop. ADCs incorporated with these alternative topologies have demonstrated excellent power efficiency. However, their inherent accuracy is limited and, without the help of any of the previously mentioned accuracy-enhancing analog techniques or digital processing, these topologies are only suitable for low- to medium-resolution applications.

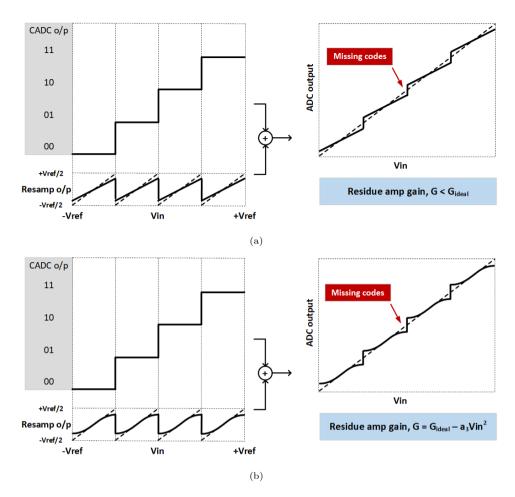

The last group of techniques involves the use of digital calibration. In this approach, the residue amplifiers are allowed to possess insufficient gain and accuracy,

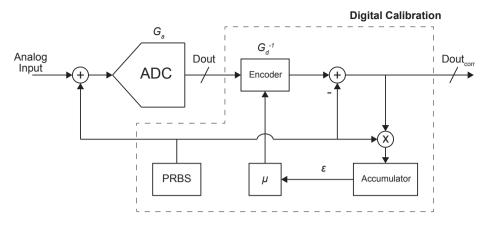

Figure 2.9: Digital calibration principle

and the resulting errors are detected and calibrated in digital post-processing. Since they are no longer required to achieve full gain accuracy, the residue amplifiers can be designed with simpler and more power-efficient topologies. Although implementing digital calibration entails its own set of complexities, a significant part of the calibration hardware is often not in the signal path, allowing it to operate at a much lower rate. As Moore's law enables cheaper and lower power digital processing, such digitally-assisted amplifiers have quickly become the most widely adopted solution for residue amplification. In this section, we will cover some of the basics of digital calibration of residue amplifier gain and nonlinearity.

#### 2.2.1. DIGITAL CALIBRATION

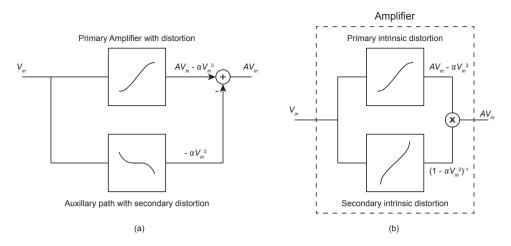

Digital calibration basically involves the estimation of the error(s) in the residue amplifier by analyzing the effect of the corresponding non-ideality on the ADC's digital output. By observing certain signatures generated in the ADC output code by the respective error(s), the magnitude of the amplifier's corresponding non-idealities can be estimated. As shown in Figure 2.9, this error estimation is typically carried out on the ADC output by a digital state machine, and often involves a calibration signal. And based on the estimated error signal, a correction term is applied to counteract the corresponding amplifier non-ideality. This is nominally also performed in the digital backend while encoding the ADC output bits, by adjusting the radix (gain error) or adding an input-dependent correction term (gain nonlinearity).

The nature of the error estimation process plays an important role in deciding the speed, complexity and the efficacy of the calibration algorithm. ADC errors can

Figure 2.10: Correlation-based background calibration technique with PRBS signal

be estimated in two different modes – foreground and background. In the foreground mode [16–18], the ADC is taken offline by switching its input to a known calibration test signal, normally during startup. By analyzing its response to that test signal, the errors can be quickly determined. Since the ADC input is known, the amount of averaging required to suppress the interference of any other signal on the error estimation process is very low. Such deterministic methods typically achieve very fast convergence, while providing good calibration accuracy and low calibration logic power.

While foreground mode calibration methods can provide quick and accurate estimates of ADC errors, they cannot be used after startup. This limits their suitability in applications where it is necessary to track and calibrate the ADC errors during normal operation. For instance, in applications that involve large temperature and supply variations during the operation of the chip, it might be difficult to ensure the ADC resolution with just a foreground calibration at startup. For these applications, it is necessary to continuously monitor the ADC errors in background, while it is processing the input signal. Some approaches attempt to partially solve this by using a queue-based approach [19, 20], in which, during the normal operation of the ADC, some of the samples are reserved for calibration. During these samples, the ADC is no longer processing the input signal. While this approach helps the calibration engine to continuously monitor the PVT conditions, it comes at the cost of ADC throughput.

Using a background calibration algorithm [21–23] makes it possible to continuously track the ADC errors without sacrificing the ADC throughput. However, since

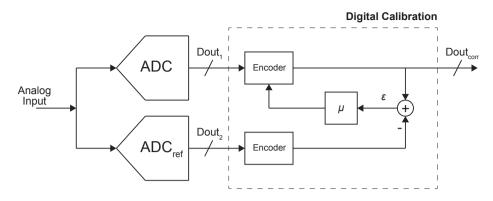

Figure 2.11: Deterministic background calibration technique with a parallel ADC path

the ADC is digitizing the normal input signal, it becomes a lot more complicated to decorrelate and extract the error signal from the ADC output. One of the ways to do that is by injecting a pseudo-random based binary sequence (PRBS) (+1,-1) as the calibration signal, as shown in Figure 2.10. This PRBS signal can be injected into the CADC or the sub-DAC of the pipeline stage, or directly into the input signal. In the digital backend, the digital equivalent of the PRBS signal is subtracted from the encoded ADC output. The resulting digital output contains the digitized ADC input and an error signal that is proportional to the difference between the analog and the digital radix. The error signal can be extracted by correlating this digital output with the PRBS signal through multiplication with the PRBS code, and then averaging the resulting product. This error signal can subsequently be used, with a certain gain, to adjust the radix in the encoder. To reliably separate the error signal from the input, a sufficiently random PRBS signal is required along with a lot of averaging, especially for amplifier nonlinearity calibration (empirically shown to be  $2^N$  samples, where N bits is the desired ADC resolution [22]). Although these correlation-based approaches do not add any major additional analog hardware, they require a lot of ADC samples to perform a reasonably accurate calibration.

Some deterministic background calibration approaches have also been published in the literature [24–28]. These usually employ an auxiliary path such as a slow, accurate reference ADC which operates in parallel [24–26], as illustrated in Figure 2.11. The output of the ADC under calibration is compared to the reference ADC, and the difference between the two outputs provides the error signal. Since the linearity of the reference ADC limits the accuracy of the main ADC, the reference ADC is often also calibrated. These approaches, like the foreground methods, can converge quickly while providing an accurate estimate of the error signal. However, they trade off calibration speed with higher power dissipation and area arising from the additional reference ADC. Some variants of this approach have tried to mitigate the additional hardware penalty by utilizing the ADCs in both the parallel paths for digitizing the input signal. Split-ADC technique [27, 28] is one of the primary examples of this and will be covered in more detail in the upcoming chapters.

## 2.3. Conclusion

In this chapter, one of the most popular ADC architectures – the pipelined ADC – has been reviewed. The key building blocks of a pipelined ADC - CADC, sub-DAC and the residue amplifier - were discussed in detail, along with the effect of their non-idealities on the ADC performance. Finally, some of the prominent techniques used to mitigate the effect of these circuit non-idealities were reviewed, with special emphasis on digital calibration.

#### REFERENCES

- S. H. Lewis and P. R. Gray, "A pipelined 5MHz 9b ADC," in ISSCC Dig. of Tech. Papers, 1987.

- [2] S. Louwsma, M. V. A. van Tuijl, and B. Nauta, "A 1.35 GS/s 10 b 175 mW timeinterleaved A/D converter in 0.13μm cmos," *IEEE J. Solid-State Circuits*, vol. 43, pp. 778–786, Apr. 2008.

- C. Lee and M. Flynn, "A 12 b 50 MS/s 3.5 mW SAR-assisted 2-stage pipeline ADC," pp. 239–240, 2010.

- [4] S. H. Lewis and et al., "A 10-b 20-Msample/s analog-to-digital converter," *IEEE J. Solid-State Circuits*, vol. 27, pp. 351–358, Mar. 1992.

- [5] S. H. Lewis, "Optimizing the stage resolution in pipelined, multistage, analog-todigital converters for video-rate applications," *IEEE Trans. Circuits Syst.-II*, vol. 39, pp. 516–523, Aug. 1992.

- [6] K. Bult and G. Geelen, "A fast-settling CMOS op amp for SC circuits with 90-dB DC gain," *IEEE J. Solid-State Circuits*, vol. 25, pp. 1379–1384, Dec. 1990.

- [7] K. Nagaraj and et al., "Switched-capacitor circuits with reduced sensitivity to amplifier gain," *IEEE Trans. Circuits Syst.*, vol. 34, pp. 571–574, May 1987.

- [8] B. R. Gregoire and U. K. Moon, "An over-60dB true rail-to-rail performance using correlated level shifting and an opamp with only 30dB loop gain," *IEEE J. Solid-State Circuits*, vol. 43, pp. 2620–2630, Dec. 2008.

- [9] H. H. Boo, D. S. Boning, and U. K. Moon, "A 12b 250MS/s pipelined ADC with virtual ground reference buffers," *IEEE J. Solid-State Circuits*, vol. 50, pp. 2912–

2921, Dec. 2015.

- [10] T. Sepke and et al., "Comparator-based switched-capacitor circuits for scaled CMOS technologies," in *ISSCC Dig. of Tech. Papers*, pp. 220–221, 2006.

- [11] L. Brooks and H. S. Lee, "A zero-crossing-based 8b 200MS/s pipelined ADC," in ISSCC Dig. of Tech. Papers, pp. 460–461, 2007.

- [12] S. K. Shin and et al., "A 12bit 200MS/s zero-crossing-based pipelined ADC with early sub-ADC decision and output residue background calibration," *IEEE J. Solid-State Circuits*, vol. 49, pp. 1366–1382, June 2014.

- [13] B. Hershberg and et al., "Ring amplifiers for switched capacitor circuits," *IEEE J. Solid-State Circuits*, vol. 49, p. 2928–2942, Dec. 2012.

- [14] N. Dolev, M. Kramer, and B. Murmann, "A 12-bit, 200-MS/s, 11.5-mW pipeline ADC using a pulsed bucket brigade front-end," pp. 98–99, 2008.

- [15] I. Ahmed, J. Mulder, and D. A. Johns, "A low-power capacitive charge pump based pipelined ADC," *IEEE J. Solid-State Circuits*, vol. 45, pp. 1016–1027, May 2010.

- [16] A. N. Karanicolas, H. S. Lee, and K. L. Bacrania, "A 15-b 1-Msample/s digitally self-calibrated pipeline ADC," *IEEE J. Solid-State Circuits*, vol. 28, pp. 1207–1215, Dec. 1993.

- [17] I. E. Opris, L. D. Lewicki, and B. C. Wong, "A single-ended 12-bit 20 Msample/s selfcalibrating pipeline A/D converter," *IEEE J. Solid-State Circuits*, vol. 33, pp. 1207– 1215, Dec. 1998.

- [18] A. Verma and B. Razavi, "A 10-bit 500-MS/s 55-mW CMOS ADC," IEEE J. Solid-State Circuits, vol. 44, pp. 3039–3050, Nov. 2009.

- [19] C. R. Grace, P. J. Hurst, and S. H. Lewis, "A 12-bit 80-MSample/s pipelined ADC with bootstrapped digital calibration," *IEEE J. Solid-State Circuits*, vol. 40, pp. 3039– 3050, May 2005.

- [20] B. D. Sahoo and B. Razavi, "A 12-bit 200-MHz CMOS ADC," *IEEE J. Solid-State Circuits*, vol. 44, pp. 2366–2380, Sep. 2009.

- [21] J. Ming and S. H. Lewis, "An 8b 80Msample/s pipelined ADC with background calibration," in *ISSCC Dig. of Tech. Papers*, pp. 42–43, 2000.

- [22] B. Murmann and B. E. Boser, "A 12-bit 75-MS/s pipelined ADC using open-loop residue amplification," *IEEE J. Solid-State Circuits*, vol. 38, p. 2040 – 2050, Dec. 2003.

- [23] A. Panigada and I. Galton, "A 130 mw 100 MS/s pipelined ADC with 69dB SNDR enabled by digital harmonic distortion correction," *IEEE J. Solid-State Circuits*, vol. 44, p. 3314 – 3328, Dec. 2009.

- [24] K. Dyer and et al., "Analog background calibration of a 10-b 40 MS/s parallel pipelined ADC," in ISSCC Dig. of Tech. Papers, pp. 142–143, 1998.

- [25] X. Wang, P. Hurst, and S. Lewis, "A 12-bit 20-Msample/s pipelined analog-to-digital converter with nested digital background calibration," *IEEE J. Solid-State Circuits*, vol. 39, pp. 1799–1808, Nov. 2004.

- [26] H. Wang and et al., "Nested digital background calibration of a 12-bit pipelined ADC without an input SHA," *IEEE J. Solid-State Circuits*, vol. 44, pp. 2780–2789, Oct. 2009.

- [27] J. Li and U.-K. Moon, "Background calibration techniques for multi-stage pipelined ADCs with digital redundancy," *IEEE Trans. Circuits Syst.-II*, vol. 50, pp. 531–538, Sep. 2003.

- [28] J. McNeill and et al., ""Split ADC" architecture for deterministic digital background calibration of a 16-bit 1-MS/s ADC," *IEEE J. Solid-State Circuits*, vol. 40, pp. 2437 – 2445, Dec. 2005.

# 3

# Analysis of Residue Amplifiers

One of the key steps in the digitization of an analog signal is sampling. This imposition of a time stamp on the input signal makes an ADC an inherently discretetime system. As a consequence, all the major ADC sub-blocks, including the residue amplifiers, operate in a discrete-time environment with their operation synchronized to a periodic clock.

Discrete-time amplifiers are characterized by the fact that their operation is divided into different phases. For any given input sample, the amplification typically starts after a complete reset and the output voltage develops across a memory element, such as a capacitor. As a result, most of the metrics of a discrete-time amplifier -gain, SNR and THD- are dynamic and transient in nature.

In the past, residue amplifiers were allowed to settle completely and reach a steady-state, making their noise and distortion performance analogous to a continuoustime amplifier. However, as ADC speeds have increased, there has been a concerted focus on lowering their power consumption by moving to residue amplifiers that only settle partially. Due to the advent of low-cost digital processing, digital calibration has become a popular approach, whereby the inaccuracies of the residue amplifiers are detected and corrected for with the help of digital post-processing of the ADC output. While digital calibration can reduce the effect of insufficient gain and linearity in the residue amplifier on the ADC output linearity, it can not compensate

Figure 3.1: Operation of a discrete-time amplifier

for the loss of dynamic range. Hence, in order to optimize the power dissipation of the residue amplifiers, they need to be designed to achieve a certain performance before digital calibration is used to fill in the gap. However, due to their discretetime behavior, the dynamic nature of a residue amplifier's performance can make it difficult to identify the optimum point of operation for calibration-assisted residue amplifiers.Hence, it is important to analyze the discrete-time amplifiers used for residue amplification in time-domain.

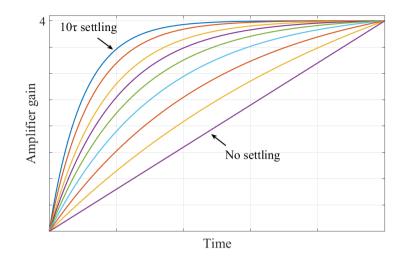

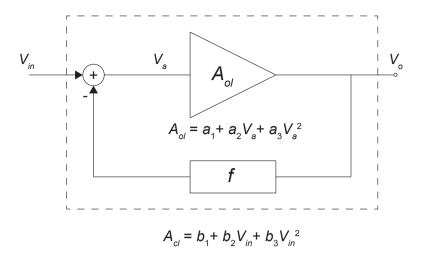

In this chapter, we will develop time-domain expressions for the most important design metrics of a residue amplifier - gain, noise, and distortion. We will consider the behavior of residue amplifiers in open- and closed-loop configurations, and identify ways to optimize their power efficiency in the presence of digital calibration.

### 3.1. Settling Behavior of Discrete-time amplifiers

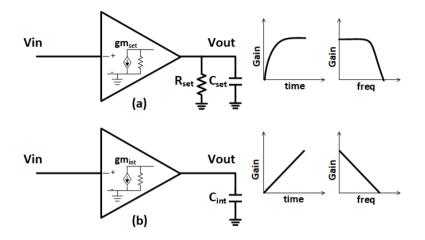

Residue amplifiers can be implemented either as open- or closed-loop configurations. Each configuration comes with certain advantages and drawbacks. Due to their simplicity, we will first analyze the behavior of discrete-time open-loop amplifiers.

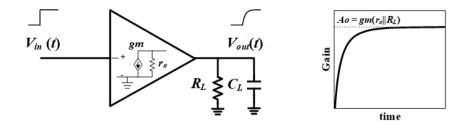

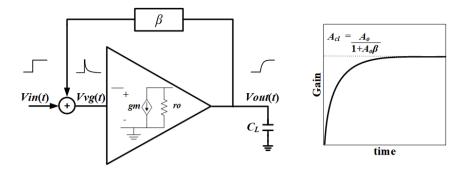

Figure 3.1 shows a single-pole open-loop amplifier with an input transconductance of  $g_m$  and an output resistance of  $r_o$  (or admittance of  $g_o$ ), yielding an intrinsic dc gain,  $A_o$ , of  $g_m r_o$  (or  $g_m/g_o$ ). As the intrinsic gain of the amplifier can be fairly large, it is often loaded by an additional load resistor,  $R_L$ , to achieve the desired gain. When driving this load resistor, along with a load capacitor of  $C_L$ , the amplifier output voltage response,  $V_{out}(t)$ , to a voltage input,  $V_{in}(t)$ , will settle with finite speed towards a steady-state gain of  $g_m R_{out}$ , where  $R_{out}$  is  $r_o || R_L$ . This output voltage response can be calculated by using the following differential equation

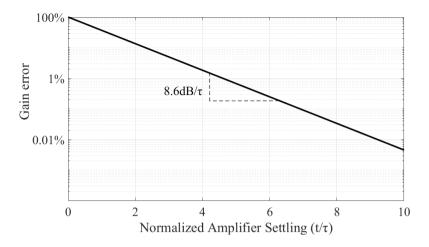

Figure 3.2: Gain error vs amplifier settling accuracy

$$I_x(t) = g_m V_{in}(t) = C_L \frac{dV_{out}(t)}{dt} + g_{out} V_{out}(t)$$

$$(3.1)$$

where  $I_x(t)$  is the output current produced by the input transconductance,  $g_m$ , and  $g_{out}$  is the output admittance  $(1/R_{out})$ . Since a discrete-time amplifier operates on a sampled-and-held input, we can consider the input signal to be a step function of amplitude  $V_{in}$ . Hence, with the help of Laplace transform, equation (3.1) can be used to calculate  $V_{out}(t)$  as –

$$V_{out}(t) = A(1 - e^{-t/\tau})V_{in}, \quad t \ge 0$$

(3.2)

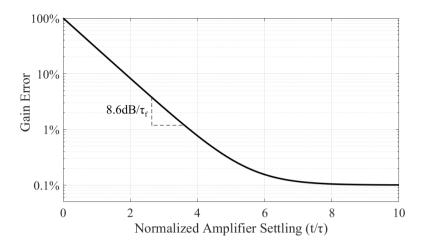

where A is the steady-state gain  $(g_m R_{out})$  and  $\tau$  is the time constant  $(R_{out}C_L)$  that defines the settling speed of the amplifier. Equation (3.2) describes a purely first-order exponential settling, resulting from the single-pole nature of the amplifier. Considering A to be the desired gain, the amplifier gain error over time can be derived as –

$$\varepsilon_g(t) = A - A(1 - e^{-t/\tau})V_{in} = Ae^{-t/\tau}, \quad t \ge 0$$

(3.3)

The gain error is plotted in Figure 3.2 with respect to amplifier settling, which is expressed as  $t/\tau$ . It can be seen that the gain error decreases at the rate of  $20\log_{10}(e)$  or 8.6dB for every unit  $\tau$  of settling. This particular rate of decrease in the amplifier gain error also indicates first-order settling and can be used to characterize the settling response of an amplifier.

From (3.3), we can conclude that the gain error for a discrete-time amplifier is a function of time. This means that the amplifier makes a smaller gain error if it is allowed a longer amplification time. This transient behavior can also be seen in the amplifier's noise and linearity performance, and its power dissipation. Hence, in order to properly understand the design trade-offs, we will analyze the openloop amplifier's noise and linearity performance w.r.t the amplifier settling in the following sub-sections.

#### 3.1.1. Noise

To calculate the noise power of the discrete-time amplifier shown in Figure 3.1, we need to consider the noise power spectral density from all the noise sources in the amplifier. To simplify the analysis, let us assume that the only noise sources are the input devices and the load resistor. Ignoring the contribution of flicker noise, the output-referred noise current power spectral density can be expressed as -

$$\overline{i_{o,n}^2(t)} = kT\left(g_m + \frac{1}{R_L}\right) \tag{3.4}$$

Using the Langevin form of the stochastic differential equation for the amplifier in Figure 3.1, the output-referred noise power can be calculated as shown in [1] –

$$\overline{v_{o,n}^2(t)} = \frac{kT}{C_L} \left(1+A\right) \left(1-e^{-2t/\tau}\right) + \frac{kT}{C_L} e^{-2t/\tau}$$

(3.5)

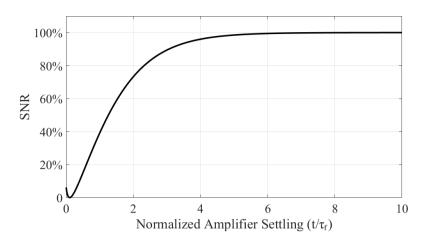

Since the load capacitor is assumed to undergo a complete reset before the amplification begins, this results in the capacitor sampling a noise power of  $kT/C_L$  at t=0. Based on the output noise power and the signal gain derived previously, the amplifier SNR can be expressed as –

$$SNR(t) = \frac{V_{out}^2(t)}{v_{o,n}^2(t)} = \frac{\left\{A\left(1 - e^{-t/\tau}\right)\right\}^2}{\frac{kT}{C_L}\left(1 + A\right)\left(1 - e^{-2t/\tau}\right) + \frac{kT}{C_L}e^{-2t/\tau}}$$

(3.6)

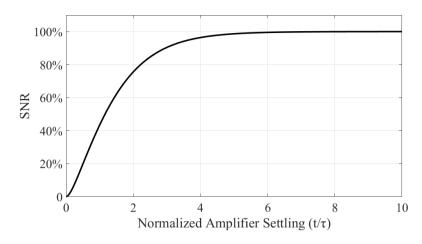

Figure 3.3 shows the output-referred SNR versus amplifier settling. It can be seen that the amplifier is able to achieve more than 90% of its final SNR in the first three time-constants of settling.

Figure 3.3: Settling behavior of SNR of an open-loop discrete-time amplifier

#### 3.1.2. DISTORTION

Along with noise and gain error, amplifier distortion is amongst the most significant sources of error in residue amplification. Any nonlinear mechanism inside the amplifier could generate distortion components which will corrupt the linearity of the amplifier output. Since nonlinearity in the residue signal results in unwanted spurs in the ADC's digital output, any amplifier distortion will have a detrimental impact on the ADC's resolution. This makes it one of the most important design constraints for the amplifier.

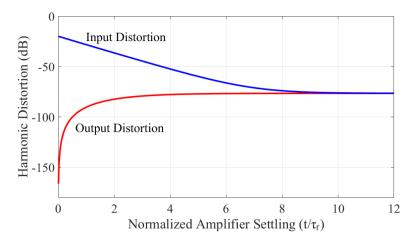

Just like gain error and noise, amplifier distortion also shows a transient behavior in discrete-time amplifiers. Although we only care about the amplifier's linearity at the moment its output is sampled, it is important to know how the distortion components within the amplifier vary with time in order to optimize the amplifier power efficiency. In this sub-section, we will analyze the settling behavior of the distortion components arising from the input transconductance and the output impedance of an open-loop amplifier.

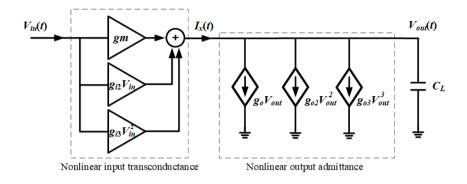

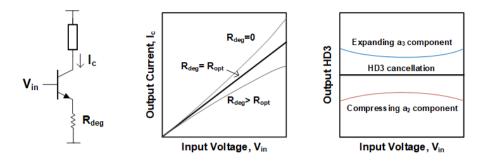

A non-linear single-stage amplifier modeled with input and output distortion sources is shown in Figure 3.4. For ease of calculation, the analysis is performed with admittances instead of impedances, and we ignore the effect of  $R_L$ . The input transconductance is modeled with second- and third-order distortion coefficients,  $g_{i2}$ and  $g_{i3}$ , respectively. Hence, the distortion components arising at the output due to the nonlinear  $g_m$  can be calculated by replacing the  $g_m$  in (3.1) with the nonlinear  $g_m$  characteristic (detailed derivation presented in Appendix A). As a result, the

Figure 3.4: Amplifier distortion model

second-order input distortion component can be expressed as -

$$V_{out,in}^{(2)}(t) = \frac{g_{i2}}{g_o} (1 - e^{-t/\tau}) V_{in}^2, \quad t \ge 0$$

(3.7)

Similarly, the third-order distortion component can be calculated as -

$$V_{out,in}^{(3)}(t) = \frac{g_{i3}}{g_o} (1 - e^{-t/\tau}) V_{in}^3, \quad t \ge 0$$

(3.8)

Apart from the input transconductance, a voltage-dependent output impedance is also a major source of amplifier distortion. Depending on the voltage headroom available to the transistors, a relatively large signal swing at the output may end up modulating the amplifier output impedance, usually compressing the overall amplifier gain.

Since the output distortion depends on the magnitude of output voltage itself, its settling behavior is different from the input distortion. We can calculate it by again assuming the output impedance to have second- and third-order non-linearity as shown in Figure 3.4. If the amplifier output admittance can be written as –

$$g_{out} = g_o + g_{o2}V_{out}(t) + g_{o3}V_{out}^2(t)$$

(3.9)

then using a similar analysis as for the input distortion (presented in Appendix A), the second- and third-order output distortion components can be calculated as –

$$V_{out,out}^{(2)}(t) = \frac{g_{o2}g_m^2}{g_o^3} \left\{ 1 - 2\left(\frac{t}{\tau}\right)e^{-t/\tau} - e^{-2t/\tau} \right\} V_{in}^2, \quad t \ge 0$$

(3.10)

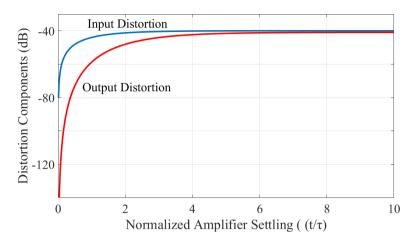

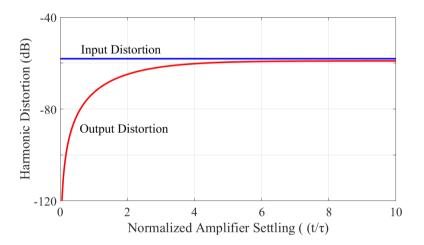

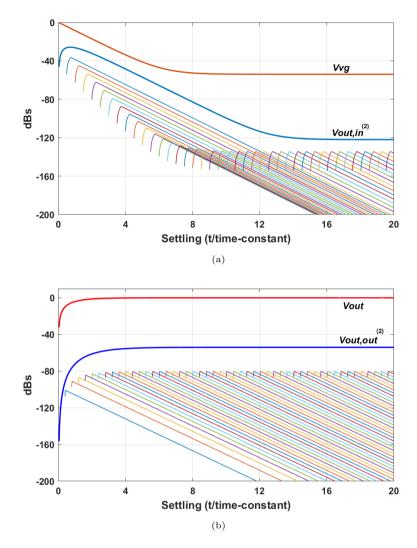

Figure 3.5: Settling behavior of amplifier distortion components

Figure 3.6: Settling behavior of harmonic distortion originating from the amplifier input transconductance and output impedance

$$V_{out,out}^{(3)}(t) = \frac{g_{o3}g_m^3}{g_o^4} \left\{ \left(1 - e^{-t/\tau}\right) + \frac{3}{2}e^{-t/\tau}\left(1 - e^{-2t/\tau}\right) + 3e^{-t/\tau}\left(1 - e^{-t/\tau}\right) - 3\left(\frac{t}{\tau}\right)e^{-t/\tau} \right\} V_{in}^3, \quad t \ge 0$$

(3.11)

Figure 3.5 shows the settling behavior of the  $2^{nd}$ -order distortion components arising from input and output nonlinear mechanisms with a magnitude (normalized

Figure 3.7: Amplifier in negative feedback with input, virtual ground and output signals

to the fundamental component) of approximately 0.1%. It can be seen that the input distortion component settles in the same way as the fundamental output signal, while the output distortion component settles a bit slower. This is also illustrated in Figure 3.6 where the two distortion components are plotted after being normalized with the fundamental output signal.

# 3.2. DISCRETE-TIME AMPLIFIERS WITH NEGATIVE FEED-BACK

As discussed in the previous section, the gain of an open-loop amplifier is directly dependent on the input transconductance and the output impedance of the amplifier. This makes the amplifier gain highly sensitive to the amplifier's bias point and its environment, and any kind of PVT variation could have a significant effect on the amplifier gain. Although this sensitivity towards PVT variations could be mitigated by applying design techniques such as a constant- $g_m$  bias, their effectiveness is limited, precluding their use in high-resolution applications.

To make the gain more independent of PVT variations, amplifiers are often used in a negative-feedback configuration, which involves feeding the amplifier output back to its input through a feedback network, as shown in Figure 3.7. For amplifiers with high inherent gain, the output signal is driven in order to completely nullify any signal at the input nodes, creating a virtual ground at its input nodes. As a result, the overall closed-loop gain is completely determined by the feedback factor,  $\beta$ , which is a ratio of passive components, thus, reducing its sensitivity towards process variation, temperature drift, and other environmental changes.

For an amplifier employed in negative-feedback using a passive feedback network

with a gain of  $\beta$ , as shown in Figure 3.7, the overall output voltage  $V_{out}(t)$  can be calculated by using the following series of equations –

$$V_{vg}(t) = V_{in}(t) - \beta V_{out}(t)$$

$$I_x(t) = g_m V_{vg}(t) = C_L \frac{dV_{out}(t)}{dt} + g_o V_{out}(t)$$

(3.12)

where  $V_{vg}(t)$  is the voltage signal at the virtual ground inputs of the amplifier,  $I_x(t)$  is the output current produced by the input transconductance,  $g_m$  and  $g_o$  is the open-loop output transconductance of the amplifier, resulting in an open-loop gain,  $A_o$ , of  $g_m/g_o$ . If the input signal is again considered to be a step function of amplitude  $V_{in}$ , then, with the help of Laplace transform, (3.12) can be used to calculate  $V_{out}(t)$  as –

$$V_{out}(t) = \frac{A_o}{1 + A_o \beta} \left( 1 - e^{-t/\tau_f} \right) V_{in}, \quad t \ge 0$$

(3.13)

where  $\tau_f$  is the loop time-constant and can be expressed as –

$$\tau_f = \frac{\tau}{1 + A_o \beta} \tag{3.14}$$

For an extremely large loop gain  $(A_o\beta \gg 1)$ , the amplifier closed-loop gain settles to simply  $1/\beta$ , making it independent of the amplifier's input  $g_m$  and output impedance. It is also evident from (3.14) that the closed-loop time-constant gets reduced by the loop-gain, thus increasing the 3-dB bandwidth of the amplifier. Apart from the output voltage, the virtual ground signal,  $V_{vg}(t)$ , is also an important indicator of settling in a closed-loop amplifier. By combining equations (3.12) and (3.13),  $V_{vg}(t)$  can be expressed as –

$$V_{vg}(t) = V_{in} - \beta V_{out}(t) = \frac{1 + A_o \beta e^{-t/\tau_f}}{1 + A_o \beta} V_{in}, \quad t \ge 0$$

(3.15)

From (3.15)), it can be seen that the virtual ground signal decays with time at the rate of 8.6dB per  $\tau$  of settling, before settling to a residual value of  $V_{in}/(1+A_o\beta)$ . Just like in the open-loop case, this rate of decay is an indicator of a purely first-order exponential settling, resulting from the single-pole nature of the amplifier.

Monitoring the virtual ground signal provides key insights into how the amplifier behaves in a negative-feedback loop. As evident in (3.15)), the amplifier effectively tries to suppress any signal present at the virtual ground nodes, and while the limit of suppression is determined by the loop gain, the rate of suppression is defined by the closed-loop time constant.

Figure 3.8: Settling behavior of gain error in closed-loop amplifier

#### 3.2.1. GAIN ERROR

Considering the desired gain of the closed-loop amplifier shown in Figure 3.7 to be  $1/\beta$ , the gain error over time can be calculated using (3.15) as -

Gain error,

$$\varepsilon_g(t) = \frac{1}{\beta} - \frac{A_o}{1 + A_o\beta} (1 - e^{-t/\tau_f})$$

$$= \frac{1 + A_o\beta e^{-t/\tau_f}}{1 + A_o\beta} \frac{1}{\beta}, \quad t \ge 0$$

(3.16)

The gain error expression above consists of a static and a dynamic part. The static part represents the residual steady-state gain error due to the limited loop-gain. The dynamic part of the gain error describes the initial part of the amplification when the amplifier is still settling at a rate of  $8.6 \text{dB}/\tau_f$ , as shown in Figure 3.8.

Using (3.16), and (2.2) from chapter 2 that describes the resolution required in the ADC stage, the loop gain and bandwidth requirements for a closed-loop residue amplifier of an ADC stage can be expressed as –

Relative gain error =

$$\frac{1 + A_o \beta e^{-t/\tau_f}}{1 + A_o \beta} \le \frac{1}{2^{1+r_{i+1}}}$$

(3.17)

where  $r_{i+1}$  is the combined ADC resolution remaining after the *i*-th stage. Hence, for a fully settled amplifier, the minimum required DC loop gain can be calculated as –

$$\frac{1}{1+A_o\beta} \le \frac{1}{2^{1+r_{i+1}}} \tag{3.18}$$

or,

$$A_o \ge \frac{2^{1+r_{i+1}}}{\beta} \tag{3.19}$$

To put that into perspective, for the first stage of a 12-bit pipelined ADC with 1-bit per stage architecture, the residue amplifier (with a gain of 2x) needs to achieve a relative accuracy of at least  $1/2^{12}$ . In order to accomplish this without any calibration, the amplifier needs to possess an open-loop DC gain of more than 8192 or 78dB.

Along with sufficient DC gain, the amplifier also needs to possess a certain bandwidth in order to achieve the gain with the required accuracy within the specified amplification period. This bandwidth requirement can also be calculated from (3.17), by assuming the op-amp to have sufficiently high DC gain ( $A_o\beta \gg 1$ ). In that case, for an amplification period of  $t_s$ , (3.17) can be simplified to –

$$e^{-t_s/\tau_f} \le \frac{1}{2^{1+r_{i+1}}} \tag{3.20}$$

or,

$$t_s \ge (1 + r_{i+1})\tau_f \ln 2 \tag{3.21}$$

Assuming  $t_s$  to be half of the ADC clock period, the 3-dB bandwidth of the closed-loop amplifier can be written as –

$$f_{3dB} \ge \frac{(1+r_{i+1})f_s \ln 2}{\pi}$$

(3.22)

or,

$$f_u \ge \frac{(1+r_{i+1})f_s \ln 2}{\pi\beta} \tag{3.23}$$

where  $f_s$  is the ADC sampling frequency and  $f_u$  is the unity-gain frequency of the op-amp and is expressed as  $\beta f_{3dB}$ . Based on the above expression, it can be seen that if the 12-bit pipelined ADC in the previous design example was to be operated at a speed of 200MS/s, then the amplifier in the first stage will need a unity-gain bandwidth of nearly 1GHz to completely settle to the desired gain with the required accuracy.

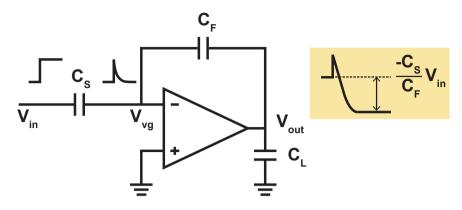

#### 3.2.2. Noise

In order to analyze the noise performance of the closed-loop amplifier, we consider an inverting amplifier with a capacitive feedback network, as shown in Figure 3.9, with all the capacitors being completely reset before the beginning of the amplification period. When an input step of  $V_{in}$  is applied at t = 0, it propagates through the capacitive network and generates spikes at the virtual ground input and the amplifier output nodes. These voltage spikes can be expressed as –

Figure 3.9: Closed-loop charge amplifier

$$V_{vg}(t = 0^{+}) = V_{in} \frac{C_S(C_L + C_F)}{C_S C_F + C_S C_L + C_F C_L}$$

$$V_{out}(t = 0^{+}) = V_{in} \frac{C_S C_F}{C_S C_F + C_S C_L + C_F C_L}$$

(3.24)

After the initial kick, the amplifier begins to drive the output in order to reduce the virtual ground signal to zero through negative feedback. As the amplifier output is settling, the transient closed-loop gain of the inverting amplifier can be expressed by taking a ratio of the amplifier output with the input step. Assuming the DC loop gain to be sufficiently large, the overall closed-loop gain,  $A_{cl}(t)$ , can be derived as –

$$A_{cl}(t) = \frac{C_S C_F}{C_S C_F + C_S C_L + C_F C_L} e^{-t/\tau_f} - \frac{C_S}{C_F} \left(1 - e^{-t/\tau_f}\right)$$

$$= \frac{-C_S}{C_F} \left(1 - \frac{(C_L + C_F)(C_S + C_F)}{C_S C_F + C_S C_L + C_F C_L} e^{-t/\tau_f}\right)$$

(3.25)

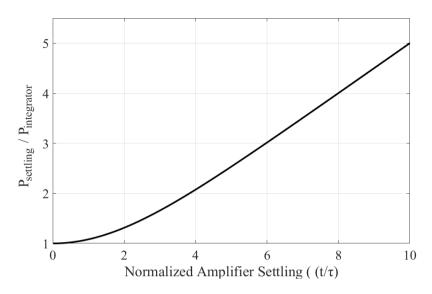

where  $\tau_f$  is the time constant of the closed-loop amplifier. The first part in the equation represents the steady-state gain,  $-C_S/C_F$ , and the second half represents the gain error due to limited settling in the amplifier. Neglecting any other sources of noise in the amplifier, the noise current density from the input transistor is given by  $4kTg_m$ , with  $g_m$  being the input transconductance. If the noise bandwidth is limited only by  $C_L$ , then the output-referred noise power at time t can be calculated using the analysis in [2] –