**Delft University of Technology**

## Multi-functional LED Module Integration and Miniaturization for Solid State Lighting Applications

Liu, Pan

DOI 10.4233/uuid:1f879b34-73f1-42e1-96c0-92f85289e13e

**Publication date** 2019 **Document Version**

Final published version

#### Citation (APA)

Liu, P. (2019). Multi-functional LED Module Integration and Miniaturization for Solid State Lighting Applications. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:1f879b34-73f1-42e1-96c0-92f85289e13e

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy** Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# Multi-functional LED Module Integration and Miniaturization for Solid State Lighting Applications

# Proefschrift

ter verkrijging van de grad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus, Prof.dr.ir. T.H.J.J. van der Hagen, voorzitter van het College voor Promoties, in het openbaar te verdedigen op donderdag 24 januari 2019 om 10:00 uur

door

# Pan LIU

Master of Science in Sustainable Energy Technology, Technische Universiteit Delft, Nederland geboren te Tianjin, China. Dit proefschrift is goedgekeurd door de

Promotor: Prof. dr. G.Q. Zhang Copromotor: Dr. ing. H.W. van Zeijl

Samenstelling promotiecommissie:

Rector Magnificus, Prof. dr. G.Q. Zhang Dr. ing. H.W. van Zeijl

Onafhankelijke leden: Prof. dr. ir. P.M. Sarro Prof. dr. ir. W.D. van Driel Prof. dr. ir. K.M.B. Jansen Prof. dr. ir. J.M.J. den Toonder Dr. ir. R.H. Poelma

Reserve: Prof. dr. P.J. French voorzitter Technische Universiteit Delft Technische Universiteit Delft

Technische Universiteit Delft Technische Universiteit Delft Technische Universiteit Delft Technische Universiteit Eindhoven Nexperia B.V.

Technische Universiteit Delft

Keywords: Solid State Lighting, Miniaturization, Wafer Level Integration

Printed by: ProefschriftMaken || www.proefschriftmaken.nl Cover by: Pan Liu Copyright © 2018 by Pan Liu ISBN 978-94-6380-220-8 An electronic version of this dissertation is available at http://repository.tudelft.nl/.

To youth and happiness in Holland, To love of my dear family, To life

# Contents

| Summary                                                                         | ix   |

|---------------------------------------------------------------------------------|------|

| Samenvatting                                                                    | xiii |

| Chapter 1 Introduction                                                          | 17   |

| 1.1 Solid State Lighting                                                        | 19   |

| 1.2 Challenge for Miniaturized Solid State Lighting Applications                | 20   |

| 1.3 Thesis Outline                                                              | 26   |

| References                                                                      |      |

| Chapter 2 LED Packaging Technologies                                            | 29   |

| 2.1 Solid State Lighting System                                                 |      |

| 2.2 Packaging Methods                                                           | 32   |

| 2.3 Thermal Analysis for LED Lamps                                              | 33   |

| 2.4 Model Set Up and Simulation Analysis                                        |      |

| 2.4.1 Case 1. SMD High Power LED on an FR4 PCB                                  | 36   |

| 2.4.2 Case 2. SMD High Power LED on an FR4 PCB and Aluminum Substrate           | 37   |

| 2.4.3 Case 3. COB High Power LED on an FR4 PCB                                  | 37   |

| 2.4.4 Case 4. COB High Power LED on a ceramic PCB                               | 38   |

| 2.4.5 Case 5. COH High Power LED on an Aluminum Substrate                       | 39   |

| 2.5 Conclusion                                                                  | 42   |

| Reference                                                                       | 43   |

| Chapter 3 Driver Integration for Miniaturized Solid State Lighting Applications | 45   |

| 3.1 G4 Retrofit LED Driver Analysis                                             | 47   |

| 3.1.1 Linear Driver                                                             | 48   |

| 3.1.2 Switch Mode Driver                                                        | 49   |

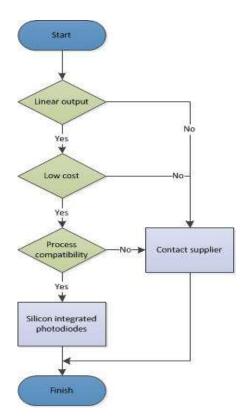

| 3.2 Design Methodology for Driver Integration                                   | 50   |

| 3.2.1 On-chip Components                                                        | 50   |

| 3.2.2 Off-chip Components                                                       | 51   |

| 3.3 Conclusion                                                                  | 52   |

| Reference                                                                       | 53   |

| Chapter 4 Monolithic Wafer Level Integration                                    | 55   |

| 4.1 Monolithic Integrated Rectifier                                             | 58   |

| 4.1.1 Design and Fabrication                                                    | 58   |

| 4.1.2 Test and Characterization                                                 | 64   |

| 4.2 Spice Model of Schottky Diodes                                         | 69  |

|----------------------------------------------------------------------------|-----|

| 4.2.1 Forward IV Measurement                                               |     |

| 4.2.2 Capacitance Measurement                                              |     |

| 4.2.3 Breakdown Voltage Measurement                                        | 71  |

| 4.3 Simulation of Rectifiers Using DIMES BiCMOS7 Schottky Diode Model      |     |

| 4.4 Characterization of Integrated Rectifier Fabricated in BiCMOS7 Process | 74  |

| 4.5 Temperature Sensor                                                     | 76  |

| 4.6 Light Sensor                                                           | 80  |

| 4.7 Conclusion                                                             | 83  |

| Reference                                                                  | 85  |

| Chapter 5 Wafer Level Packaging with Flex/Rigid Substrate                  | 87  |

| 5.1 3D Wafer level Packaging                                               | 89  |

| 5.2 Flex/Rigid Substrate                                                   |     |

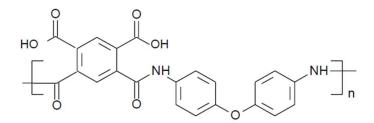

| 5.2.1 Polyimide                                                            |     |

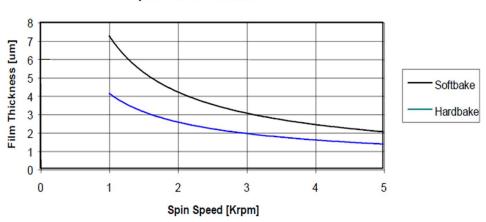

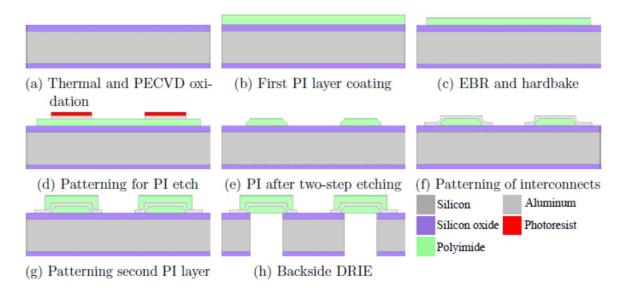

| 5.2.2 Polyimide Process                                                    |     |

| 5.3 Rigid/Flex Package Design                                              | 100 |

| 5.4 Package Characterization                                               | 105 |

| 5.4.1 Flex/Rigid Package Characterization                                  | 105 |

| 5.4.2 Flex/Rigid Package Characterization with integrated driver circuit   | 106 |

| 5.5 Conclusion                                                             | 112 |

| References                                                                 | 113 |

| Chapter 6 Flexible Substrate Based Presence Sensing Antenna                | 115 |

| 6.1 Flexible Substrate                                                     | 117 |

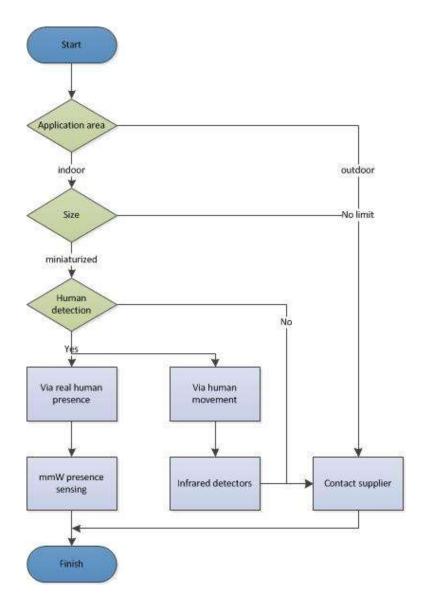

| 6.2 Presence Sensor                                                        | 117 |

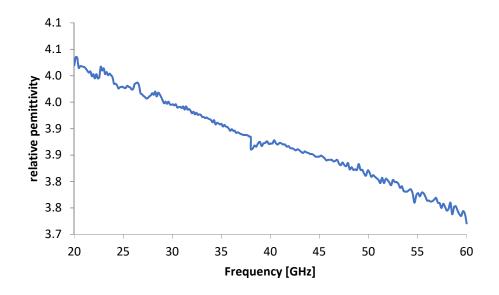

| 6.2.1 Choice of Antenna Substrate                                          | 119 |

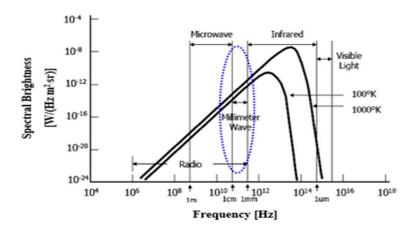

| 6.2.2 Choice of Operate Frequency                                          | 121 |

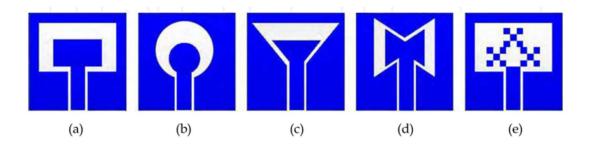

| 6.2.3 Choice of Antenna Type                                               | 122 |

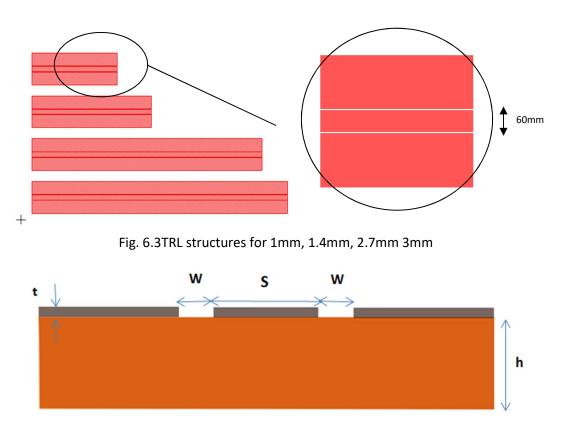

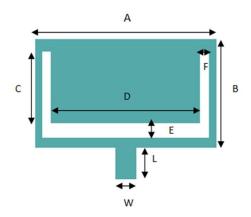

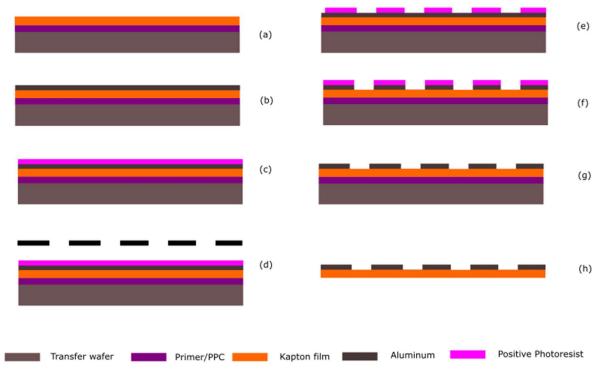

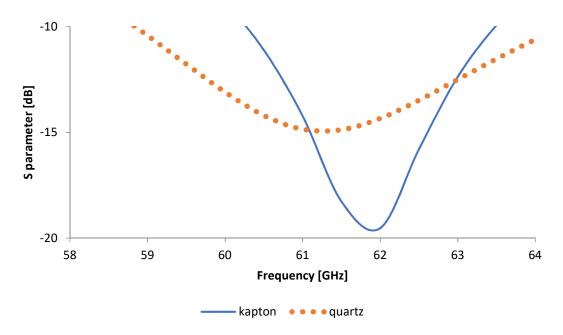

| 6.3 Antenna Design and Characterization                                    | 123 |

| 6.4 CPW Vertical Transition                                                | 126 |

| 6.5 Conclusion                                                             | 130 |

| Reference                                                                  | 131 |

| Chapter 7 Conclusions                                                      | 133 |

| Acknowledgements                                                           | 139 |

| Curriculum Vitæ                                                            |     |

| Education                                                                  | 145 |

| Work         |  |

|--------------|--|

| Publications |  |

| Awards       |  |

Summary

# Summary

Summary

#### Summary

Solid State Lighting (SSL) develops towards small size, high lumen output, high working temperature, and multi-functional applications. These trends are more desirable in miniaturized LED applications such as retrofit G4 LED devices. Retrofit G4 LEDs were chosen in this work as a technical carrier due to the miniaturized size challenge and high lumen requirements. The solutions for miniaturized retrofit G4 can also be extended to other applications of consumer lighting applications with similar requirements.

In Chapter 1, seven retrofit G4 LEDs are analyzed and compared for size, lumen output, number of LED dies, and system efficacy. Currently, there is no real retrofit G4 LED which gives high lumen output similar to traditional halogen G4 lamps. This is mainly due to the big size capacitor requirement and poor thermal management. Therefore, working temperatures of LED dies, capacitors and rectifier (Schottky diodes) were further analyzed via thermal infrared imager. Thermal management in such miniaturized SSL applications is crucial for not only lumen output but also reliability. A rectifier composed of Schottky diodes suffers high reverse leakage current under high working temperatures. Electrolytic capacitors lifetime drops by 50% for each 10  $^{\circ}$ C rise in the operating temperature. Furthermore, such capacitors are usually too bulky for miniaturized systems such as G4 LED applications.

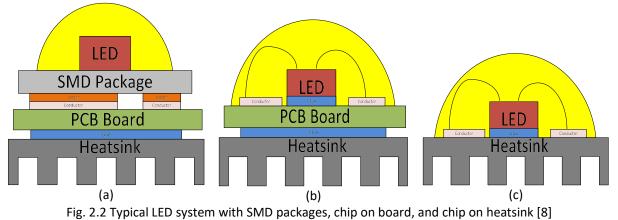

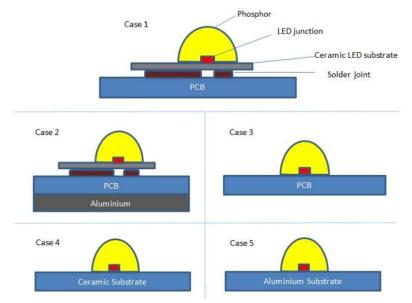

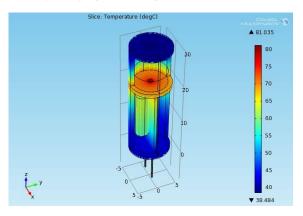

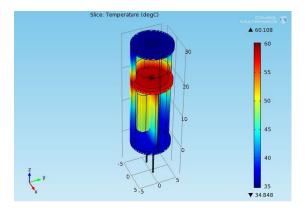

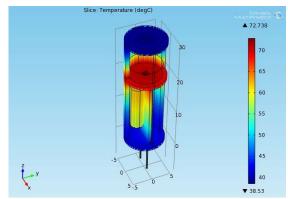

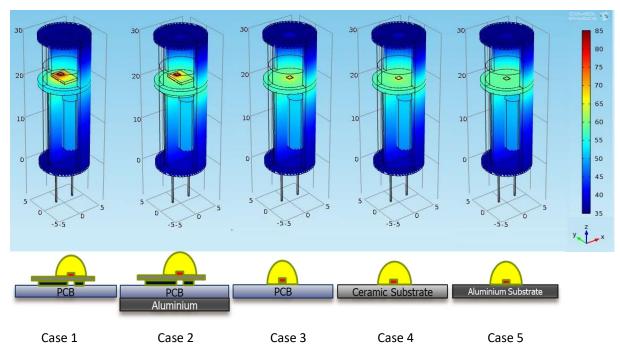

Therefore, in Chapter 2, chip level packages with different packaging methods are investigated for lower junction temperature. A LED product with traditional surface mounted devices (SMD) technology was chosen. The simulation calculation was compared for Chip on board (COB), and Chip on Heatsink (COH) technology. Compared with traditional SMD, COH package lowers the junction temperature by 30% and brings a 27% drop of the total thermal resistance. The total power from the LED with COB or COH technology can, therefore, be pushed from 1 W to 1.5 W within the limited volume.

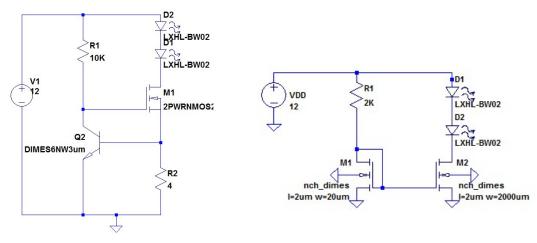

However, with all chip level packages, it is still not possible to generate enough lumen output within the limited size compared to traditional halogen G4 lamps. Therefore, Chapter 3 focused on the driver topology to power up more LED dies within the small form factor. Both the linear mode and switch mode driver were investigated. Linear driver brings inductor-free topology which saves volume. However, the linear driver suffers from low energy efficiency and not possible for smart sensor control. Therefore, switch mode driver was introduced. With the help of the control IC, the driver can power up multiple LEDs and give control to sensor systems. With both modes of LED drivers, components involved were then divided as off-chip and on-chip categories.

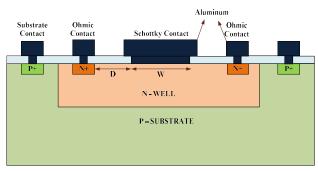

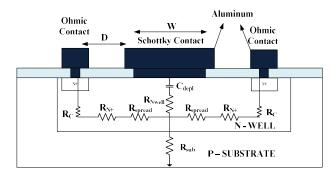

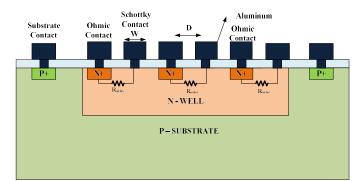

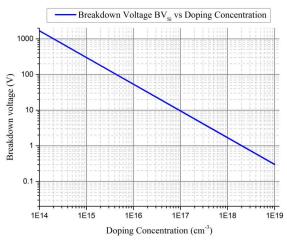

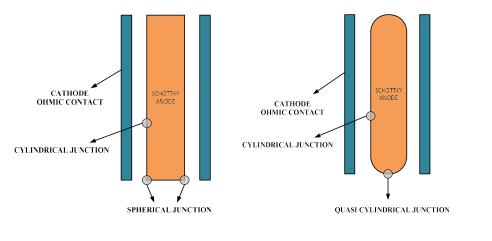

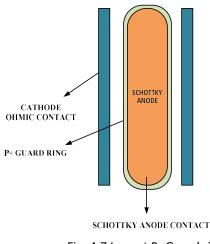

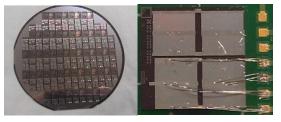

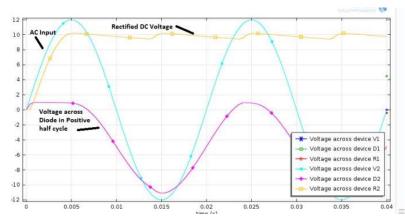

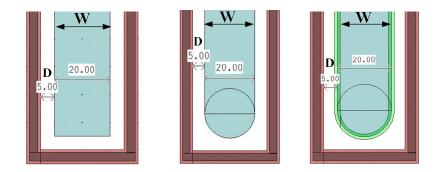

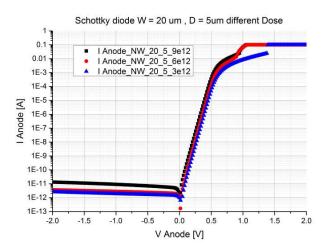

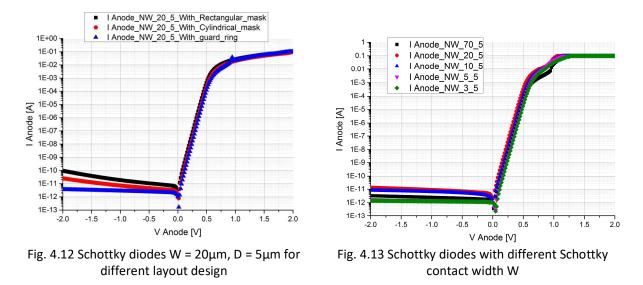

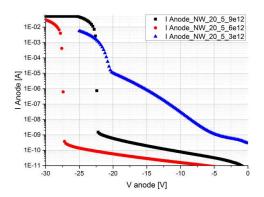

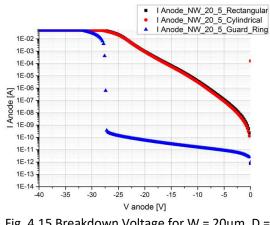

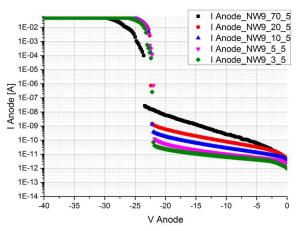

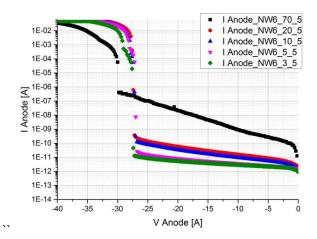

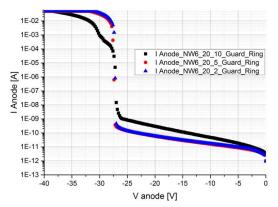

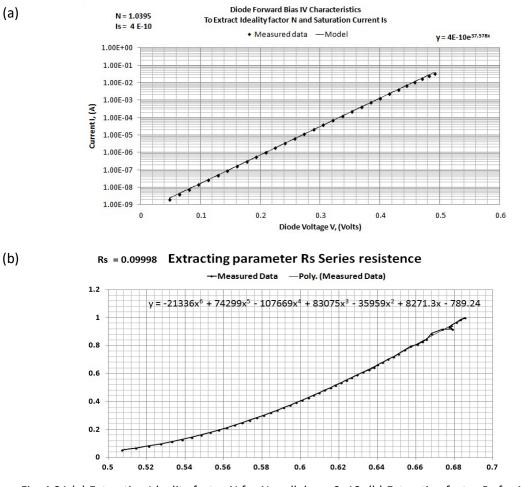

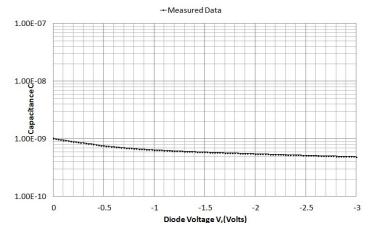

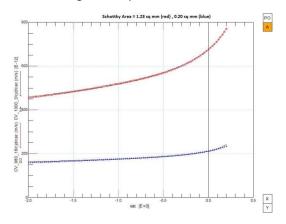

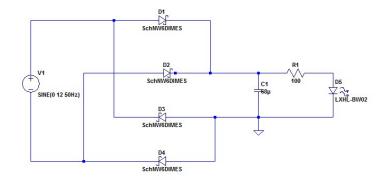

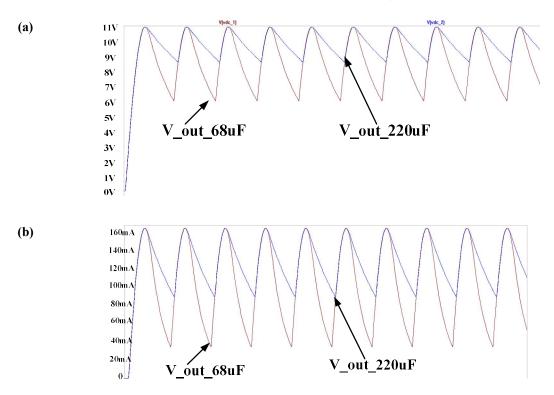

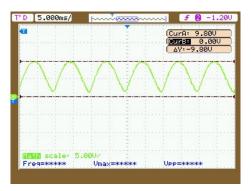

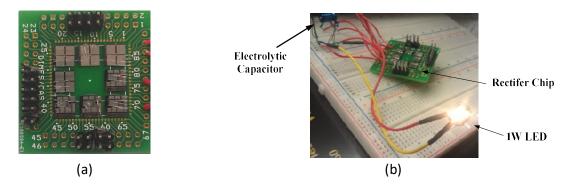

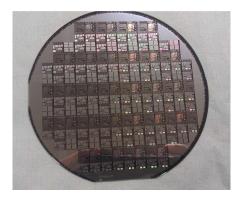

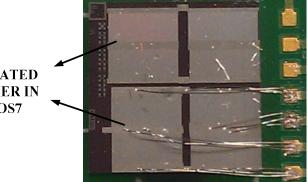

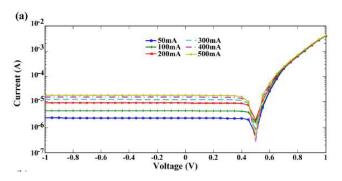

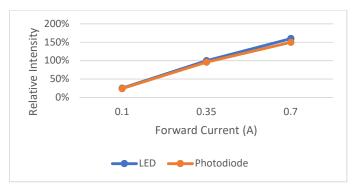

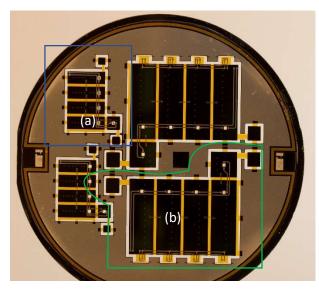

Therefore, Chapter 4 focused on monolithic wafer level integration (WLP) on a silicon substrate. Silicon substrate is chosen in this work due to the low voltage application, excellence thermal conductivity, and the possibility for on-chip device integration. In Chapter 4, a rectifier composed of four Schottky diodes was monolithically integrated on silicon. Such Schottky diodes with guard ring structures processed under a standard BiCMOS process can reach a breakdown voltage of 27 V. The breakdown voltage mainly relies on n-well doping concentration. Based on the integrated Schottky diodes, a WLP rectifier was tested as part of the G4 LED driver in Chapter 4. In order to guarantee the high-quality light output, the spice model of Schottky diode was derived from characterization, thus have the whole driver circuit simulated to avoid light flicker. Not only Schottky diodes, smart sensors targeting for SSL applications were also investigated for monolithic wafer level integration. Temperature sensor and light sensor based on silicon were studied. The methodology of how to choose such sensors in miniaturized SSL systems is also presented in Chapter 4.

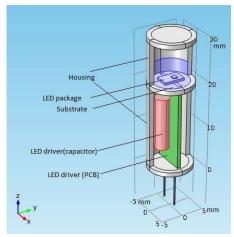

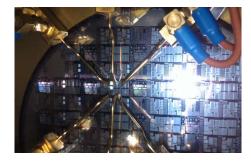

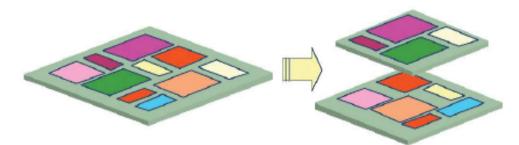

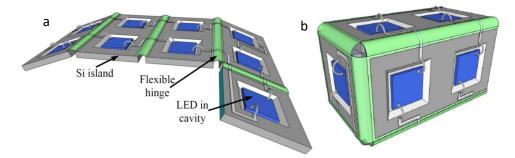

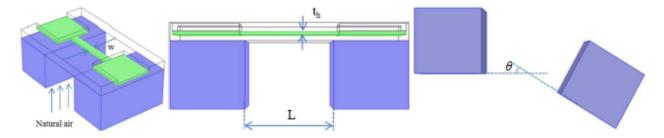

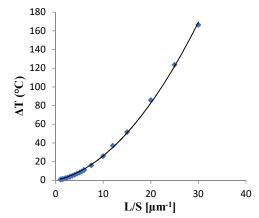

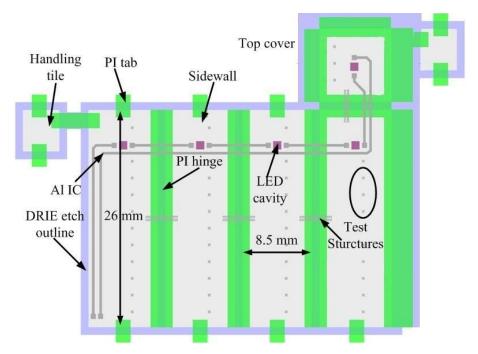

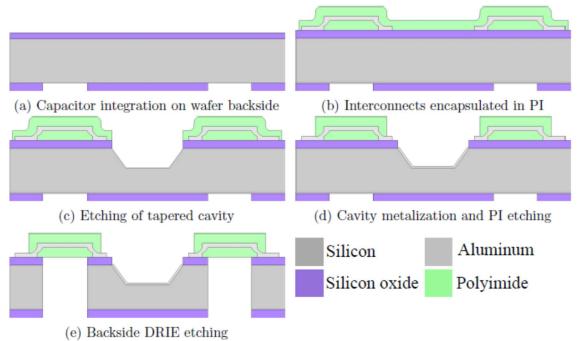

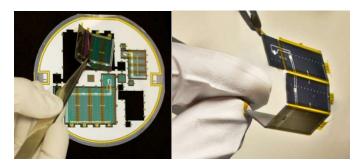

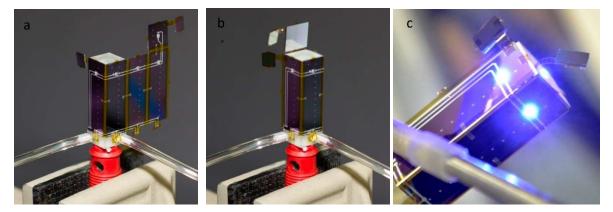

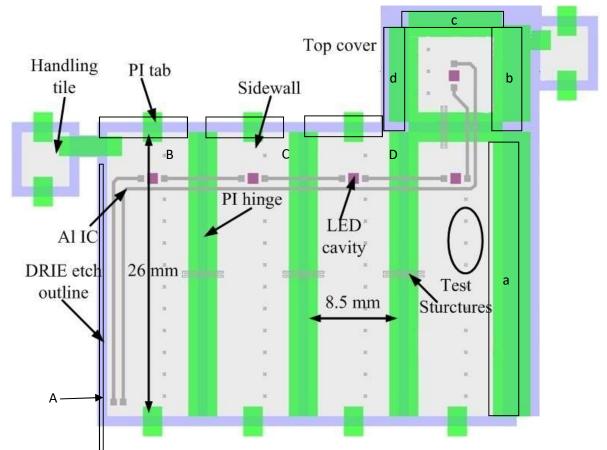

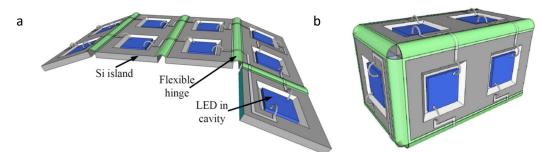

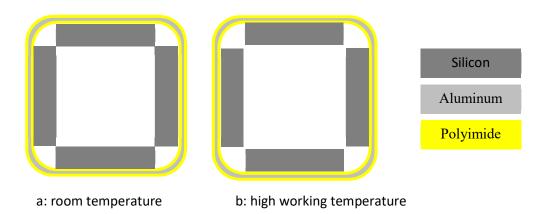

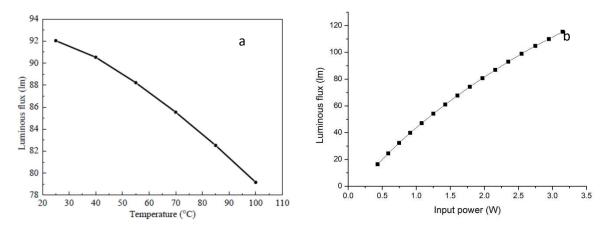

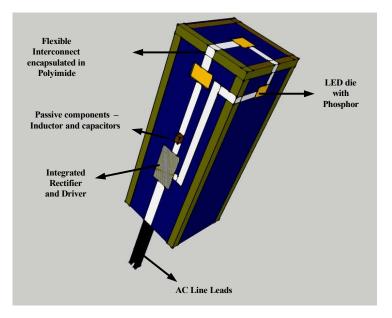

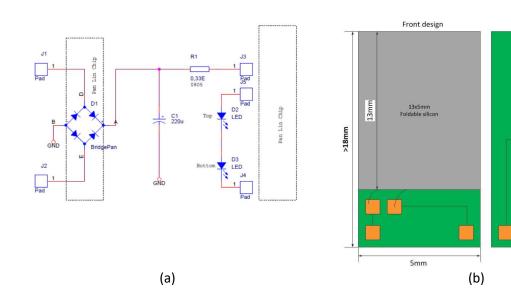

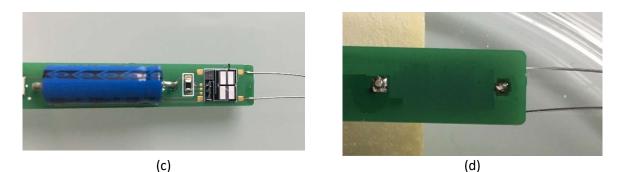

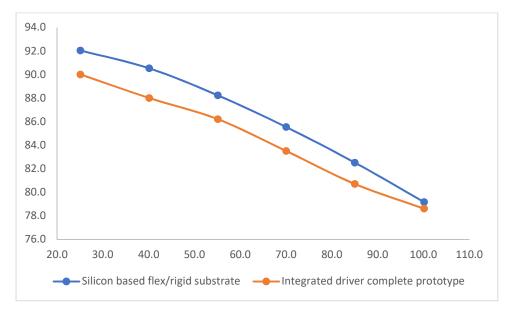

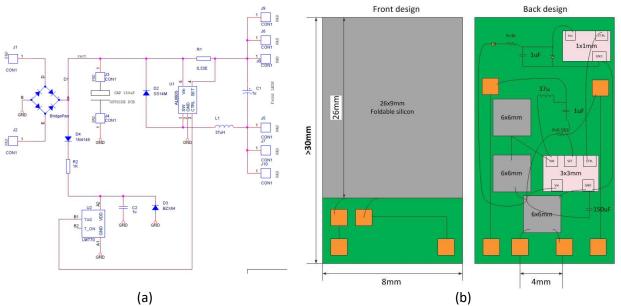

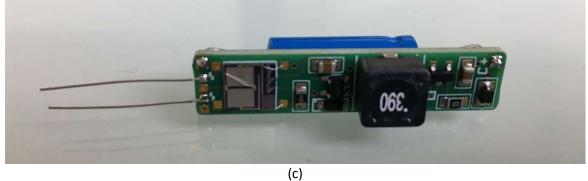

After this initial test, it is clear that in order to get more lumen output, more LED dies need to be integrated. However, wafer level process is usually 2D, thus not possible to shrink the size as small as traditional G4. Therefore, Chapter 5 reports a silicon-based rigid/flex substrate used in this work for miniaturization. A 2D wafer level process enabled silicon substrate to be planarly fabricated, then easily released and assembled into 3D for uniform light distribution. Five silicon islands equipped with LED dies placed with a light reflection layer on silicon were connected by Aluminium/Polyimide interconnects. Such flexible Aluminium/Polyimide interconnects, with designed Mean Time To Failure (MTTF) up to 25,000 hours, allowed bending angles up to 90°. Such flexible hinges also brought a "breeze" effect for this novel WLP flexible package when heated up which allows further absorbing of the tension caused by thermal expansion. The final Rth of the package is only 2.3 k/W thanks to the superior thermal conductivity of the silicon substrate. The package can work up to 2 W input to reach 85 lumen output, with the working temperature at 85 °C. Such 3D substrate folding provided volume saving together with possibilities for device integration, heat management, smart control, etc. The main application of such designed WLP package is in general aimed at retrofit G4 LEDs.

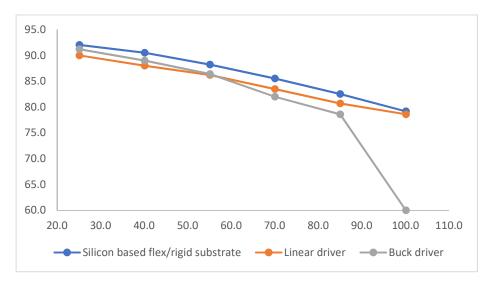

Based on the integrated rectifier, smart sensors, and flexible substrate developed, two prototypes were built and are described in Chapter 5. One is based on inductor free linear driver, with the total size only 1/4 of the original G4 LED and increased lumen output up to 90 lm (increased 60 % compared with original G4 LED). The other is a switch mode buck driver with a similar total size as the original G4 LED, but with lumen output increase up to 64 %. Furthermore, smart control for light output was also demonstrated by dimmed light when reaching high working temperatures (>85 °C). Such a platform enables wafer level integration for both monolithic and heterogeneous devices. However, these two prototypes are still missing heatsink/heat pipes for better thermal management.

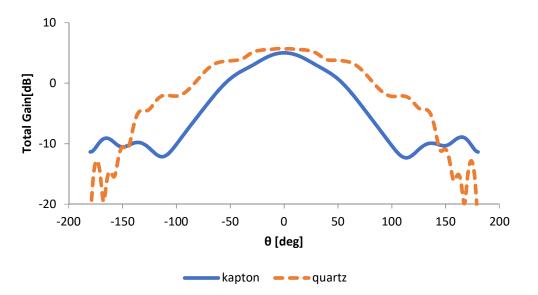

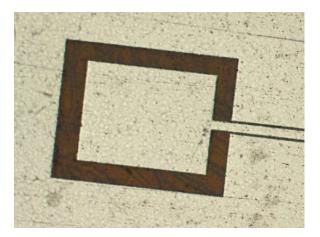

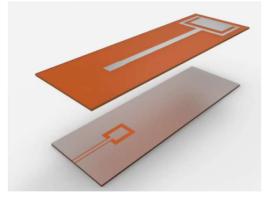

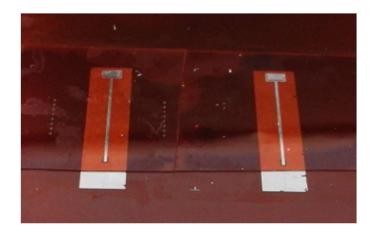

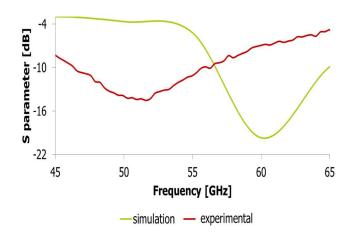

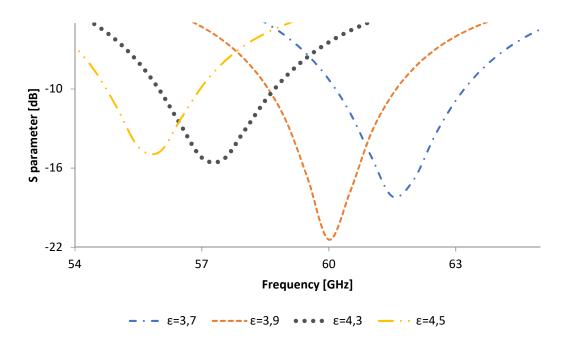

It is worth to mention, that since flexible substrate was introduced in the system for size reduction, flexible substrate based sensors were also investigated in Chapter 6. Polyimide mentioned in Chapter 5 was chosen as presence sensor antenna material. A millimeter wave (mmW) sensor operated at 60 GHz with flexible antenna composed of Polyimide and aluminum were simulated, designed, and further tested. A vertical transition between microstrip and CPW lines was also investigated. Such Polyimide (PI) based antenna provides comparable performance compared with traditional antenna fabricated on Quartz substrate, but at a much lower price.

In summary, silicon-based rigid/flex substrate demonstrated great potential for SSL applications aimed at miniaturization and multi-functions, with combining the silicon-based wafer level integration technologies and the flex interconnects for volume saving and improved reliability.

Samenvatting

Samenvatting

#### Samenvatting

Solid State Lighting (SSL) ontwikkelt zich in de richting van klein formaat, hoge lichtopbrengst, hoge bedrijfstemperatuur en multifunctionele toepassingen. Deze trends zijn meer wenselijk in geminiaturiseerde LED-toepassingen zoals retrofit G4 LED-apparaten. Retrofit G4-LED's werden in dit werk gekozen als een technische drager vanwege de uitdaging met verkleinde afmetingen en hoge lumenvereisten. De oplossingen voor geminiaturiseerde retrofit G4 kunnen ook worden uitgebreid naar andere toepassingen van consumentenverlichtingsapplicaties met vergelijkbare vereisten.

In hoofdstuk 1 worden zeven retrofit G4-LED's geanalyseerd en vergeleken op grootte, lichtopbrengst, aantal LED-stempels en systeemeffectiviteit. Op dit moment is er geen echte retrofit G4 LED die een vergelijkbaar hoge lichtopbrengst geeft als traditionele halogeen G4-lampen. Dit komt voornamelijk door de grote condensatorbehoefte en slecht thermisch beheer. Daarom werden werktemperaturen van LED-chips (dies), condensatoren en gelijkrichter (Schottky-diodes) verder geanalyseerd met behulp van een thermische infraroodbeeldvormer (imager). Thermisch beheer in dergelijke geminiaturiseerde SSL-toepassingen is cruciaal voor niet alleen de lumen-output, maar ook de betrouwbaarheid. Een gelijkrichter die is samengesteld uit Schottky-dioden lijdt onder hoge werktemperaturen aan een hoge omkeerlekstroom. De levensduur van de elektrolytische condensatoren gewoonlijk te volumineus voor geminiaturiseerde systemen zoals G4 LED-toepassingen.

Daarom worden in hoofdstuk 2 chipniveau-pakketten met verschillende verpakkingsmethoden onderzocht voor lagere junctietemperatuur. Er is gekozen voor een LED-product met traditionele SMD-technologie (surface mounted devices). De simulatieberekening werd vergeleken voor Chip on board (COB) en Chip on Heatsink (COH) -technologie. In vergelijking met traditionele SMD verlaagt het COH-pakket de junctietemperatuur met 30% en brengt het een daling van 27% van de totale thermische weerstand met zich mee. Het totale vermogen van de LED met COB- of COH-technologie kan daarom binnen het beperkte volume van 1 W naar 1,5 W worden geschakeld.

Bij alle chipniveau-pakketten is het echter nog steeds niet mogelijk om voldoende lichtop-output te genereren binnen de beperkte afmeting in vergelijking met traditionele halogeen G4-lampen. Daarom richtte Hoofdstuk 3 zich op de driver-topologie om meer LED-chips (dies) in te schakelen binnen de kleine vormfactor. Zowel lineaire modus als schakelmodus drivers werden onderzocht. De lineaire driver brengt met zich mee inductor-vrije topologie die volume bespaart. De lineaire driver heeft echter een lage energie-efficiëntie en is daarom niet mogelijk voor slimme sensorbesturing. Daarom werd de driver voor de schakelmodus geïntroduceerd. Met behulp van de besturings-IC kan de bestuurder meerdere LED's inschakelen en de besturing van sensorsystemen regelen. Met beide modi van LED-drivers werden de betrokken componenten vervolgens verdeeld als niet-on-chip- en on-chip-categorieën.

Daarom concentreerde Hoofdstuk 4 zich op monolithische wafer-niveau-integratie (WLP) op siliciumsubstraat. Siliciumsubstraten zijn in dit werk gekozen dankzij de lage spanningstoepassing, uitstekende thermische geleidbaarheid en de mogelijkheid voor on-chip apparaatintegratie. In hoofdstuk 4 was een gelijkrichter die uit vier Schottky-diodes bestond monolithisch geïntegreerd op silicium. Dergelijke Schottky-diodes met beschermingsringstructuren verwerkt onder een standaard BiCMOS-proces, kunnen een doorslagspanning van 27 V bereiken. De doorslagspanning hangt hoofdzakelijk af van de n-well dotering concentratie. Op basis van de geïntegreerde Schottky-diodes werd in hoofdstuk 4 een WLP-gelijkrichter getest als onderdeel van de G4 LED-driver. Om de hoge kwaliteit van de licht-output te garanderen, werd het spice-model van de Schottky-diode afgeleid van de karakterisering, waardoor het hele stuurcircuit werd gesimuleerd om lichtflikkering te voorkomen. Niet alleen Schottky-diodes, maar ook slimme sensoren gericht op SSL-toepassingen werden onderzocht voor monolithische integratie op

substraatniveau. Temperatuur en licht sensoren op basis van silicium werden bestudeerd. De methode voor het kiezen van dergelijke sensoren in geminiaturiseerde SSL-systemen wordt ook gepresenteerd in hoofdstuk 4.

Na deze eerste test is het duidelijk dat er meer LED-chips (dies) moeten worden geïntegreerd om meer lichtopbrengst te krijgen. Het proces van substraatniveau is echter meestal 2D, dus het is niet mogelijk om de grootte zo klein te maken als de traditionele G4. Daarom rapporteert hoofdstuk 5 een op silicium gebaseerd rigide/flex-substraat dat in dit werk wordt gebruikt voor miniaturisatie. Een 2D substraatniveau proces heeft het mogelijk gemaakt om het siliciumsubstraat vlak te fabriceren, vervolgens de structuur eenvoudig los te maken van het substraat en assembleren in 3D voor uniforme lichtverdeling. Vijf siliciumeilanden uitgerust met LED-chips (dies) geplaatst met een lichtreflectie-laag op silicium werden verbonden door middel van aluminium/polyimide verbindingen. Dergelijk flexibel aluminium/polyimide verbindingen, met ontworpen Mean Time To Failure (MTTF) tot 25.000 uren, staan buighoeken toe tot 90°. Dergelijke flexibele scharnieren brachten ook een "bries" -effect met zich mee voor dit nieuwe WLPflexibele pakket wanneer het wordt opgewarmd, waardoor de spanning die wordt veroorzaakt door thermische uitzetting verder wordt geabsorbeerd. De uiteindelijke R<sub>th</sub> van de verpakking is slechts 2,3 k/W dankzij de superieure thermische geleidbaarheid van het siliciumsubstraat. Het pakket kan tot 2 W input verwerken om 85 lumen output te bereiken, met een werktemperatuur van 85 °C. Dergelijke 3Dsubstraatvouwing bood volumebesparingen samen met mogelijkheden voor apparaatintegratie, warmtebeheer, slimme besturing, enz. De hoofdtoepassing van een dergelijk ontworpen WLP-pakket is in het algemeen gericht op retrofit G4-LED's.

Op basis van de geïntegreerde gelijkrichter, slimme sensoren en het ontwikkelde flexibele substraat zijn twee prototypen gebouwd en beschreven in hoofdstuk 5. Eén is gebaseerd op een inductorvrije lineaire driver, met een totale afmeting van slechts 1/4 van de originele G4 LED en verhoogd lumen output tot 90 Im (toegenomen 60% vergeleken met de originele G4 LED). De andere is een schakelmodus buck-driver met een vergelijkbare totale grootte als de originele G4-led, maar met lumen-output verhoogt deze tot 64 %. Bovendien werd slimme controle voor de lichtop-output ook gedemonstreerd bij gedimd licht bij het bereiken van hoge werktemperaturen (> 85 °C). Een dergelijk platform maakt integratie op substraatniveau mogelijk voor zowel monolithische als heterogene apparaten. Echter, deze twee prototypen missen nog steeds heatsink/heat pipes voor beter thermisch beheer.

Het is de moeite waard om te vermelden dat, omdat flexibel substraat in het systeem werd geïntroduceerd voor het verkleinen van de afmetingen, sensoren op basis van flexibel substraat ook werden onderzocht. Polyimide genoemd in Hoofdstuk 5 werd gekozen als antennemateriaal van de aanwezigheidssensor. Een millimetergolf (mmW) -sensor op 60 GHz met flexibele antenne samengesteld uit Polyimide en aluminium werden gesimuleerd, ontworpen en verder getest. Een verticale overgang tussen microstrip- en CPW-lijnen werd ook onderzocht. Een dergelijke op polyimide (PI) gebaseerde antenne biedt vergelijkbare prestaties in vergelijking met traditionele antennes die zijn gefabriceerd op kwartsubstraat, maar voor een veel lagere prijs.

Samengevat toonde silicium-gebaseerd rigide / flex-substraat een groot potentieel voor SSL-toepassingen gericht op miniaturisatie en multi-functies, met een combinatie van op silicium gebaseerde wafer-niveauintegratietechnologieën en de flex-interconnects voor volumebesparing en verbeterde betrouwbaarheid. Chapter 1 Introduction

# Chapter 1 Introduction

# 1.1 Solid State Lighting

Electronics systems influence every aspect of our lives and play a vital role in day to day activities. The semiconductor industry is a key driver for the development of many industries such as education, transportation, biomedical, communication and entertainment, etc. One of the most influential developments in the semiconductor industry over the last decade has been with the advent of Solid State Lighting (SSL) for the general lighting application. Similar to the history of electronics which turns from vacuum tube era to the semiconductor revolution, lighting industry today is also following the similar path which turns traditional incandescent bulb to SSL systems.

Technology for the lighting industry began with the invention of the incandescent bulb by Thomas Alva Edison in 1879. Later in the year 1906, General Electric patented the first tungsten light bulb. Though incandescent lamps are very cheap to manufacture, they were inefficient as they convert only about 1% to 5% of the consumed electricity into usable light. The next generation of lighting technology followed by the introduction of the fluorescent lamp in the 1930s. These lamps have improved efficiency than incandescent bulbs but contain small amount toxic gases like mercury which is harmful to the environment. Due to the above drawbacks of incandescent and fluorescent lamps, there is a need for the lighting industry to create lighting systems that are efficient, have lower manufacturing cost and reduced pollution[1]. For this development, there has been a lot of interest in the field of Solid State Lighting as it provides good potential for energy efficient, safe and affordable lighting solutions. Solid State Lighting, commonly called SSL, is a novel lighting technology basically composed of light emitting diode (LEDs), microelectronics drivers, and a housing. Such a technology brings lighting industry from incandescent glass bulbs into the domain of electronics, enables a lighting system with microelectronics and MEMS functionalities, such temperature sensing, presence sensing and other functions [2]. In the recent survey, the lighting market, including light sources(LEDs), electronics and luminaries are estimated to increase from €50 billion in 2010 to €70 billion by the year 2020 [3].

Solid State Lighting refers to light obtained from semiconductor devices. The first report on electroluminescence was published by Henry J Round in 1907 when he found that current passed through carborundum diode emitted light. But the invention of Light Emitting Diode is credited to Russian scientist Losev who correctly explained the phenomena of light emission in silicon carbide diodes used in his work on radio receivers [4]. Light Emitting Diodes are p-n junction diodes which forward biased emit light by spontaneous recombination of electron-hole pairs and simultaneous emission of photons. LEDs are made from silicon carbide material or III–IV semiconductor like gallium arsenide, gallium nitride. The light emitted from LED occupies a narrow spectrum, and the specific wavelength or color depends on the band gap of the material. Early developed LEDs emit mainly red, blue, and green light which used as indicators, displays in electronic systems due to their low lumen/watt till the early '90s.

The development of white LEDs in mid-'90s provided interest to use LEDs as an alternative to general lighting. Most white light LEDs use an LED emitting at a shorter wavelength (e.g. blue) and a wavelength converter (e.g. phosphor). The light emitted by the blue LED is absorbed by the phosphor material and converted as white light with a longer wavelength. [1] Such invention has accelerated the growth of SSL-systems since white light is widely applied in the consumer market. SSL systems offer new possibilities to the lighting industry since it is energy saving, high reliability, good color rendering, and low power dissipation. LED is a highly energy efficient lighting technology which has the potential to fundamentally

change the future of lighting. However, the design of the LED lighting system, as a multi-domain system, is complex and different from conventional lighting. It provides many design and reliability challenges in the area of electrical, packaging, optical and luminaries. The design of Solid State Lighting (SSL) system is different from the conventional lighting system design, but closer to a microelectronics system design.

Despite many advantages, the high price of the SSL system is still the main drawback for consumers. Novel SSL applications, though with advanced features, still need to compete with low-cost existing solutions in the consumer market. Though energy saving leads to fewer energy bills on lighting, the initial high cost of LEDs compared with traditional lighting is still the greatest barrier in switching to LED technology from conventional lighting. Therefore, EU and China have already established regulations to foster such transition, to ensure less energy consumption and less CO<sub>2</sub> emission. Depending on the application, the packaging of the current luminaries accounts for up to 60% of the overall manufacturing costs [1]. Therefore, creative packaging solutions are necessary to bring the costs down, e.g. wafer level packaging, which will be illustrated later in this work.

# 1.2 Challenge for Miniaturized Solid State Lighting Applications

One key market for SSL lighting is consumer lighting, in which retrofit lamps play a very important role. Retrofit LED lighting allows to combine the advantages of solid state lighting with the existing infrastructure. Among these retrofit LED products, G4 LEDs are considered as a real challenge due to the intrinsic miniaturized size. Therefore, challenges for such miniaturized SSL application is representative. The solutions can be extended to solve other retrofit problems. Therefore, G4 retrofit LEDs were chosen as a technical carrier in this work.

Halogen incandescent bulbs usually operate at high temperature (surface temperature around 250°C - 350°C), so protective glass and plastic shell is usually needed as thermal shields for security reasons [5]. G4 Halogen lamps, as shown in Fig. 1.1, offer a white light source with excellent color rendering and a large amount of visible and infrared energy due to the high operating temperature. Some hot spots on the bulb wall itself can approach as high as 700°C. This heat generation is, on one hand, critical to the self-cleaning effect of halogen lamps to prolong the lifetime of the filament. On the other hand, the high temperature has consequences for the lamp architecture by safety requirements and applications. The efficiency of a typical 12V G4 halogen lamp ranges from 14-18 lumen/Watt (lm/W), not taken into account the fixture losses and transformer losses. Therefore, a G4 halogen lamp, as a traditional consumer light source, needs to be improved due to its low energy efficiency and short lifetime.

Fig. 1.1 Traditional G4 halogen lamp (Halogen Capsule lamp, 20W, G4, Warm white, 310 lumen) [6]

The comparison between LED retrofit lamps and halogen lamps were listed in Table 1.1. Today still more than 90% of consumer luminaries sold today are designed for conventional G4, due to its very tiny size. There is a strong desire for a G4 LED capsule replacing the very inefficient conventional halogen lamp,

within the limited volume. Furthermore, it is also very challenging to generate the desired lumen within the limited volume which have been historically constrained by the limitation of halogen bulbs. Lumen, symbolled as Im, is a universal measure unit of total quantity of visible light emitted by a source. Lamps used for lighting are commonly labeled with their light output in lumens. Therefore, effective solutions are focusing on how to get more lumen output from retrofit miniaturized SSL applications in this work. In order to reach this goal, two main challenges are identified for small form factor applications: thermal management and functional driver electronics integration.

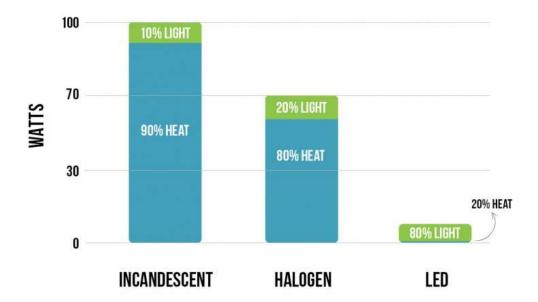

At this moment, there are a variety of products from different companies providing G4 LED retrofit lamps. However, none of them can compete with traditional halogen lamps. Besides its high cost, the lumen output is the biggest issue, which is closely related to thermal management. In incandescent light sources, 90% heat is dissipated through the glass encapsulation and for a large part by radiation (Fig. 1.2). Halogen bulbs are similar to incandescent light, but more efficient. This is because a small amount of halogen gas mixes with tungsten vapor within the bulbs allows it to work at a much higher temperature. However, it is worth to mention that halogen lamps produce a considerable amount of infrared (IR) and ultraviolet (UV) radiation that not only leads to energy waste but also damages to fabrics and artwork. But for LED lighting, since they do not produce heat in the form of infrared (IR) radiation (unless if they are IR LEDs), waste heat is much less compared by traditional light sources. Most of the heat is dissipated through the package and mainly by convection. Due to current packaging technologies, it is difficult to provide more than 100 lm within a limited space. Furthermore, none of the products on the market has the same size as traditional G4, which makes it even more difficult to compete with traditional lighting products. As a start, 7 commercially available G4 LED products were firstly chosen to be analyzed, as shown in Table 1.2. With respect to their technology concepts, design approaches, packaging materials, and performance, these products fall into two categories: high performance and small volume.

Fig. 1.2 Energy consumption comparison with the equivalent light output of incandescent lamps, halogen lamps, and LED lamps [7]

| Type of lamps      | Characteristics                                        | Main challenges                                                                                                         |  |  |

|--------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| Halogen lamps      | white light                                            | Be more energy efficient.                                                                                               |  |  |

|                    | Excellent beam control                                 | Through 3 times longer life than<br>incandescent bulbs, a lifetime of halogen<br>lamps is only around 3600 hours.       |  |  |

|                    | Compact size                                           |                                                                                                                         |  |  |

|                    | High lumen maintenance                                 | Color control/rendering.                                                                                                |  |  |

|                    | Short lifetime (1-3 years)                             | IR and UV radiation can be damaging to fabrics and artwork.                                                             |  |  |

|                    | Large amounts of visible and infrared                  |                                                                                                                         |  |  |

|                    | light                                                  | Working temperature can lead to skin burns if touched.                                                                  |  |  |

| LED retrofit lamps | Significant energy savings                             | Size limitation for electronics e.g.                                                                                    |  |  |

|                    | Long lifetime up to 50,000 hours                       | Capacitor (without proper electronic<br>design, a capacitor for energy storage<br>can be as large as a G4 halogen lamp) |  |  |

|                    | Minimized maintenance and related                      |                                                                                                                         |  |  |

|                    | costs                                                  | Lumen output to be comparable with                                                                                      |  |  |

|                    | Cool burning                                           | halogen lamps (e.g. high energy                                                                                         |  |  |

|                    | Instant ON/OFF, no warm-up time                        | efficiency, high energy density)                                                                                        |  |  |

|                    | Compatible controls                                    | Thermal management within the size limitation (e.g. miniaturized heatsink,                                              |  |  |

|                    | No mercury or lead, RoHS compliant                     | active cooling devices, etc. )                                                                                          |  |  |

|                    | Extremely low ultraviolet (UV) and infrared (IR) light |                                                                                                                         |  |  |

Table 1.1 Comparison of Traditional halogen lamps with LED retrofit lamps and main challenges

Table 1.2. State of the art of Retrofit G4 LEDs characteristics

| ``      | Lumen | Size             |                | No. Power |     | System             | category    |

|---------|-------|------------------|----------------|-----------|-----|--------------------|-------------|

|         | (lm)  | Diameter<br>(mm) | Length<br>(mm) | LEDs      | (W) | efficacy<br>(Im/W) |             |

| halogen | 350   | 9                | 32             | -         | 20  | 18                 |             |

| 1       | 56    | 13               | 37             | 1         | 1   | 56                 | Small       |

| 2       | 110   | 9                | 34             | 24        | 1.5 | 73                 | volume      |

| 3       | 180   | 30               | 4              | 12        | 2.4 | 75                 |             |

| 4       | 60    | 14               | 41             | 4         | 0.8 | 75                 | High        |

| 5       | 140   | 14               | 36             | 6         | 2   | 67                 | performance |

| 6       | 120   | 19               | 45             | 5         | 2   | 60                 |             |

| 7       | 250   | 17               | 41             | 18        | 2.2 | 114                |             |

Firstly, LEDs with different power input were chosen in these products. 6 out of 7 products were using mid-power LEDs instead of high power LEDs. Mid-power LEDs have been applied more and more in recent years, due to uniformity, tuneable string voltage, and low price. However, mid-power LED packages are usually bigger than high-power ones. On the other hand, high-power LEDs are more compact, usually with high flux, and more reliable. For high-performance category, usually more LEDs are applied.

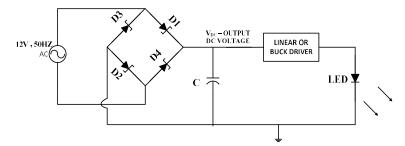

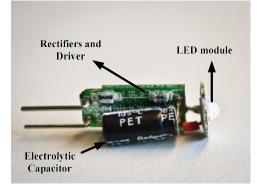

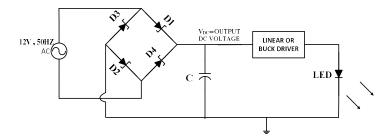

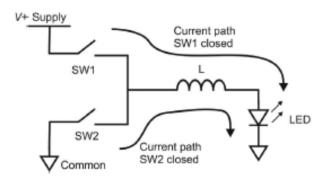

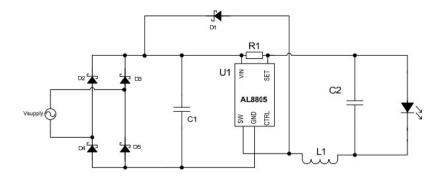

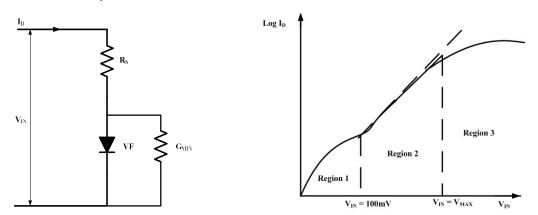

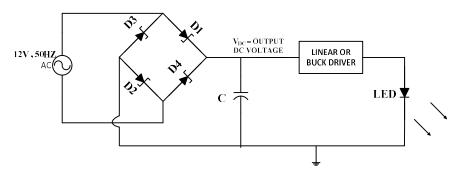

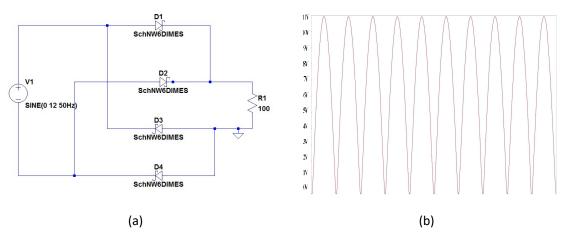

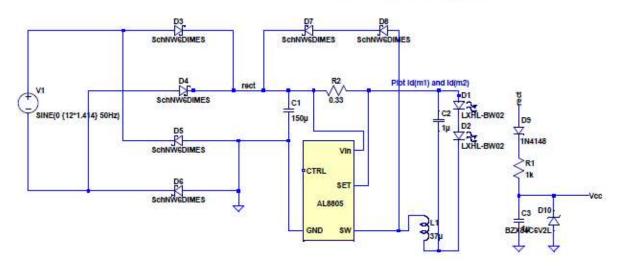

Secondly, let us take a look at the topology of the driver design. Despite a various number of LEDs and different design concepts, the driver systems for G4 LEDs are similar. The input voltage requirement of G4 LED capsule is 12V AC. A driver for a G4 LED usually contains four Schottky diodes as a rectifier, a large capacitor for energy storage, and an IC driver. A common topology design of the driver is shown in Fig. 1.3. The input 12V AC is first converted into DC by a bridge rectifier. The bridge rectifier commonly uses Schottky diodes due to their low forward voltage drop and high current conduction. After the rectifier, there are mainly two methods to maintain a constant current in LED driver systems: a linear driver or a switch mode driver. However, no matter which driver system is applied, a sizable capacitor is necessary. The capacitor is too bulky for the total system in terms of the size, and brings reliability problems when it becomes too close to LED chips.

Fig. 1.3 Schematic of a low power 12V LED system

Thirdly, thermal management is paid special attention since it is crucial for a lifetime. For improved thermal management, heat sinks are also designed according to different technology concepts. Therefore, such designs usually go along with large form factors, typically 3 times the size of conventional G4 halogen lamps. Because high junction temperature will induce thermal activation of non-radiative electron-hole recombination, it is important to keep junction temperature low to have a reliable system.

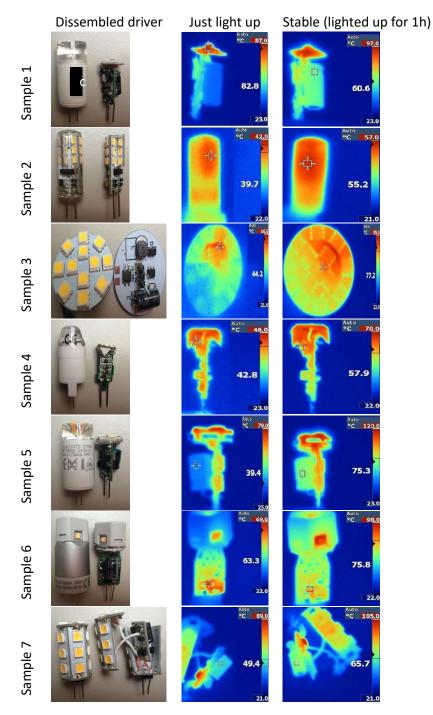

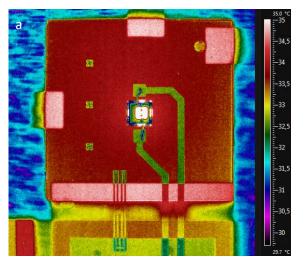

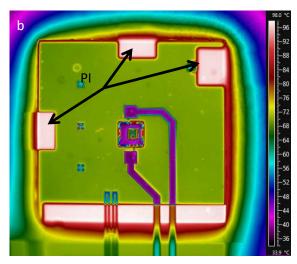

Therefore, for better understand the thermal behavior of these 7 LED retrofit G4 products, all drivers are separated and a thermal infrared imager is applied to each driver to find the location(s) with the highest working temperature (see Fig. 1.4). The measurements were carried out when the lamp is the just light up and when they are stable (after 1 hour). This is due to the fact that in most failures of LED lamps, driver systems are identified as a weak point, and among driver failure mechanisms, the high temperature is the most influential factor.

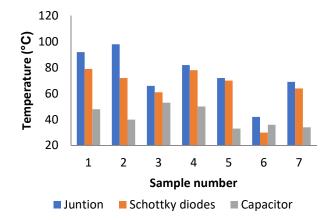

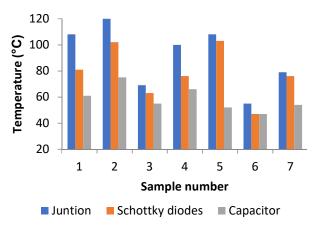

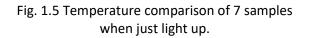

The measurements were focused on the LED, PCB, Schottky diodes, and capacitors (see Fig.1.5 and Fig. 1.6). Junction temperatures are the highest in the system. When just light up, we noticed in sample 3, 4, 5 and 7, the temperature of Schottky diodes are almost as high as LEDs, while the temperature of LEDs is the highest in the system. After 1 hour, the temperature of the Schottky diodes of sample 3, 5, 6 and 7 are still almost as high as LEDs. The temperature increase of Schottky diodes ranges from 2 to 33 °C among different samples. In silicon-based commercialized Schottky diodes, the increase of temperature

leads to a reduction of the forward voltage of drops 1.2mV/°C [2]. But more severe, the reverse leakage current is increased with temperature, which leads to thermal instability. Therefore, it is important to have Schottky diodes with better reliability or apply them in a better thermal managed system.

Fig. 1.4 Dissembled driver and infrared camera photos of seven samples.

More specifically, the capacitor was recognized as the most vulnerable component in most LED drivers. Therefore, we take close look at capacitors applied in G4 LEDs. 6 out of 7 products are using electrolytic

capacitors as energy storage, whose lifetime is relatively short compared to LED dies. Due to the small form factor, the capacitors are heated up by 10 to 35 °C from just light up to 1-hour stable operation. The lifetime of an electrolytic capacitor drops by 50% for each 10 °C rise in the operating temperature. A typical electrolytic capacitor can survive 10000 h at 105°C, while most LED products claim themselves with a lifetime of 25000 h. [3] Furthermore, electrolytic capacitors are usually bulky which brings crucial problems to miniaturized applications such as G4 LEDs. To sum up, the electrolytic capacitor is too big and not reliable enough for miniaturized systems such as G4 LED applications.

Consequently, G4 LED applications require novel capacitor technologies with higher temperature tolerance and smaller form factors. Thin film capacitors are one of the promising replacement, since they are with longer lifetime compared with electrolytic capacitors. Dielectric, ferroelectric, and piezoelectric thin films are excellent candidates for multifunctional miniaturized applications, with respect to performance, size, and cost. High dielectric constant materials such as BaTiO3, PbZrxTi1-xO3 (PZT) are reported in [4]. Besides ultrahigh-k dielectric materials, large capacitance areas are also interested by researchers, such as high-density trench capacitors [5]. With DRIE etching, the lateral size of these capacitors can be minimized by three orders of magnitude in comparison with thin film, without the need for ultra-high k materials.

Furthermore, it worth to mention that none of these 7 G4 LED products on the market were equipped with smart control. With smart lighting, you can easily change your home atmosphere with a single touch, or dim them, or change the color temperature. Besides improved customer experiences, implementing an advanced LED lighting system offers energy and maintenance savings. Presence sensing and light sensing can save energy when there is no need. Temperature sensors can protect the LED luminaires from overheat. However, with these 7 G4 LED products, it is difficult to combine smart sensing due to the size limitation and high working temperature. Therefore, it is essential to develop a new packaging concept for miniaturize G4 LED size, and provides multi-functional controls.

To sum up, with a detailed analysis of G4 LED drivers, challenges for miniaturized SSL applications are:

1) small form factor;

2) high temperature under stable operation;

- 3) reliability risks for capacitors and Schottky diodes during high working temperature;

- 4) smart control for further energy saving.

Therefore, a new package developed targeting at these challenges will be introduced in the following of this work. To develop such miniaturized and multi-functional package, we need to first take a close look into packaging methods of the LED dies, to estimate how much lumen we could maximum get out this G4 size. Based on this limitation, we can decide how many LED dies are needed in this system. Hence, the driver circuit can be simulated to improve the efficiency and guarantee high-quality light output. Based on the simulation results, the components needed for the driver can be then divided into on-chip components and off-chip components. On-chip components are possible to fabricate in-house with BiCMOS process to be monolithically integrated on a silicon wafer. Off-chip components then need to be packaged to fit in the miniaturized system. Based on such requirements, a silicon-based rigid/flex substrate is then investigated and tested for this G4 retrofit LED application.

## 1.3 Thesis Outline

As mentioned before in introduction, retrofit G4 LED was chosen as a technical carrier for this miniaturized SSL system integration, due to its size limitation and high lumen output expectation. Therefore, state of the art products was analyzed by an infrared camera to identify the critical components (e.g. capacitor, rectifier, etc.). To improve lumen output in such a small form factor, better thermal management and smart control are needed for improved performance and reliability.

Based on such request, different packaging methods were compared for G4 LED packages in Chapter 2. Such comparison offers insight for thermal management of critical components. For better understand the driver circuit and the components involved, G4 LED driver was analyzed in Chapter 3. Two modes of the driver were introduced, linear mode driver and switch mode driver, respectively. Components related to the two set up were divided into on-chip components and off-chip components based on inhouse available technology.

Silicon wafer level integration was then introduced for on-chip components in Chapter 4. Monolithic integrated Schottky diodes behave as rectifiers for G4 LED. Spice models of in-house fabricated Schottky diodes, NPN transistors, resistors, etc. were generated. Simulation-based on these spice models guaranteed a high quality of light output. Temperature sensor and light sensor were also investigated for on-chip integration. Design methodology for such sensors in miniaturized applications was also introduced. Based on these in-house fabricated devices, integrated driver system was initially tested in Chapter 4.

However, lumen output tested in Chapter 4 were not enough for G4 retrofit, therefore more LEDs need to integrate into the system. As a result of that, a silicon-based 3D rigid/flex substrate was introduced in this thesis for multifunctional LED module integration and miniaturization. Such substrate is not only suitable for wafer level integration for SSL applications, but also possible to combine the advantage of silicon integration for LED, driver electronics, and sensors, and the folding properties for miniaturization. This is due to the benefits of the silicon substrate who offers numbers of possibility for device integration, either monolithically or heterogeneously. Meanwhile, the high thermal conductivity of silicon provides fast heat dissipation for LED dies.

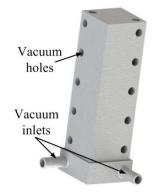

Therefore, in Chapter 5, such a micro-machining technology platform is proposed, fabricated, and tested. A new method of photolithography for 3D packages is developed. Wafer level device integration developed in Chapter 3 and 4 can be further combined with such a platform. Chapter 5 also demonstrated this 3D WLP performance with different driver scenarios.

Since flexible substrate was introduced in the system for size reduction in Chapter 5, flexible substrate based sensors were also investigated in Chapter 6. A polyimide-based flexible antenna for millimeter wave presence sensing was simulated, designed, and tested. A vertical transition between microstrip and CPW lines also enables the signal transfer through polyimide substrate to IC chips with a bond wire-free connection. This opens the door for sensors integration on a flexible substrate, which leads to cost reduction. In the end, a summary of the major findings of each chapter is listed.

## References

- 1. Driel, W., et al., *System Level Reliability for Solid State Lighting Applications*. 2014. 28.

- 2. Schubert, E.F., et al., *Solid-state lighting—a benevolent technology*. Reports on Progress in Physics, 2006. 69(12): p. 3069.

- 3. *Lighting the Future Lighting Roadmap 2013* Top Sector HTSM

- 4. Zheludev, N., *The life and times of the LED a 100-year history.* Nature Photonics, 2007. 1(4): p. 189-192.

- 5. Energy, U.D.o. *Using LED to its best advantage*. LED application series, 2008.

- 6. Available from: www.amazon.de

- 7. https://www.superbrightleds.com/blog/led-vs-incandescent-vs-halogen/707/

Chapter 2 LED Packaging Technologies

# Chapter 2 LED Packaging Technologies

### Chapter 2 LED Packaging Technologies

### 2.1 Solid State Lighting System

Electronics components comprise more than 50% of a complete SSL system cost. [1] Therefore, as already mentioned in the introduction, an SSL system design is much closer to a microelectronics system design. Electronic packaging usually refers to chip-level packaging, board-level packaging, and system-level packaging. Chip-level packages include electronic functional devices (e,g, active, passive, or electromechanical devices, etc.). The board-level packages assemble chips or multi-chips together with additional components, e.g. capacitors, resistors, inductors, switches, etc. System-level packages normally refer to the outer enclosure or shell of the electronics, such as PCB to PCB interconnections. [2,3]

For an SSL system, the main semiconductor IC components of this system are LED dies, power converters and driver circuitry. The assembly process is usually separated into levels from 0 to 5. A summary of SSL system components and its functions is presented in Table 2.1. [2] Level 0 is epitaxial and chip production. Level 1 is chip packaging. level 2 is soldering the LED onto a substrate, e.g. PCB. Level 3 is the LED driver control and integration. Level 4 is lighting source design, and level 5 is the system of lighting. For package free chip production, level 1 can be eliminated. Elimination of level 1 avoids the use of lead frames and bonding wires, therefore reduces the total thermal resistance of the system.

| Level | System                              | Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Function                                                                   |

|-------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|       | Component                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| 0     | LED Die                             | 1 P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | To achieve high luminous efficiency                                        |

| 1     | LED Package                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | For electrical connection, heat dissipation and mechanical stability.      |

| 2     | Multi LED Board                     | Contraction of the second seco | Increasing the number of LEDs for higher lumen output.                     |

| 3     | LED Power<br>Control and<br>Drivers |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | To convert AC to DC and provide constant current and control of the LED.   |

| 4     | Luminaire<br>Designs                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | To enable usage of LED bulb as conventional bulb by using retrofit design. |

| 5     | Lighting System<br>Designs          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Multiply interconnected luminaries for lighting system on a large scale.   |

#### Table 2.1 Levels of SSL System

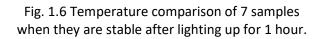

A composition of the cost analysis of a retrofit lamp is shown in Fig. 2.1 (a) [3]. It worth to mention here that cost breakdown might change as a function of time, as shown in Fig. 2.1 (b). As a common A19 60W retrofit lamp, the manufacturing cost is expected to change, especially for LED packages and driver, which are 35% and 15% in the year of 2013 compared with 25% and 10% anticipated by 2020, respectively. Since LED packaging and thermal/mechanical/electronics are crucial for the total system cost, the integration of both packaging and electronics for the SSL system results in the reduction of total system cost.

From Fig. 2.1(a), it is also clear that in the early phase of product development, the major cost component of the LED system is the LED package which contributes to about 30% of the total LED bulb. When taking a close look into level 1 LED packages, the result is clear that packaging methods greatly influence the total cost, as shown in Fig. 2.1 (b). Manufactures are performing more and more packaging activities at a wafer level in order to reduce the total package cost.

Fig. 2.1 (a)Cost breakdown Projection for a typical A19 retrofit lamp (b) Typical cost breakdown for an LED package [3]

Therefore, an essential challenge in LED technology is to choose proper packaging methods that provide circuit support and protection, heat dissipation, signal distribution, manufacturability and serviceability, power distribution. [4] Today, more and more LED lighting manufacturers focus on technology gaps to develop packages with different methods that enable heat to be conducted efficiently away to the environment, especially for high brightness LED applications.[5]

## 2.2 Packaging Methods

The advantages of LEDs are well recognized as energy saving, high efficiency, small size, and lightweight. However, current LED integration technologies are facing challenges to give the desired lumen within the limited volume. LEDs typically have a chip size of 0.2-1.0 mm.[7] Such tiny devices can be applied for a wide range of applications after proper packaging. LED dies, as heat sensitive semiconductor components, are often mounted onto substrates which provide electrical insulation and adequate thermal conductivity. Multiple layers are usually applied to such substrates. However, each layer is a potential risk which brings additional thermal resistivity. With multiple layers and different thermal coefficients of expansion, potential risks are delamination, corrosion, and degradation.

#### **Chapter 2 LED Packaging Technologies**

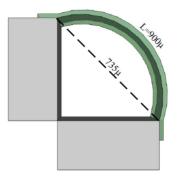

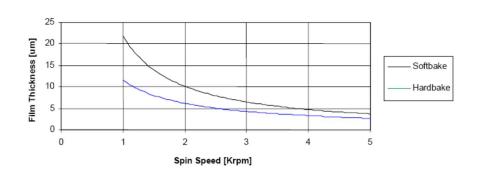

Standard LED package is named Surface Mounted Devices (SMD) package, which contains thermal resistance of LED package, PCB board, heatsink, and applied glue between components. Chip on board (COB) avoided the application of SMD substrate, therefore minimum the thermal resistance. Chip on heatsink (COH) consists of a typical aluminum cooler with a glue bonded chip, which greatly reduced thermal resistance. [8] In this work, we mainly focus on novel chip level packages for solid state lighting applications (chip on board and chip on heatsink), compared with traditional surface mounted devices, as illustrated in Fig. 2.2.

With continuous demands of high performance, low cost, and miniaturized solid state lighting applications, advanced electronic packaging technology will keep facing challenges including innovative thermal management solutions. Thermal management of consumer LED lamps is very important because the excess heat can reduce the light output, produce color shift, and shorten lifetime. Therefore, effective thermal management becomes critical for LED integration methods.

The challenges in thermal management can be viewed in practical as three problems:

1) Heatsink temperature must be maintained at a relatively low level despite high local heat density;

2) High heat loads must meet requirements for critical interfaces (e.g. solder joint) for system connection;

3) The working temperature of critical components (e.g. capacitor) meet the requirement of the desired reliability.

### 2.3 Thermal Analysis for LED Lamps

In LED lamps, the total heat is generated by 3 sources: heat from the LED junction (blue LED), heat from the phosphor, and heat from the LED driver. From these sources, the total generated heat is mainly dissipated in three ways: conduction, convection, and radiation.[9]

Conduction of heat transfer through solid mediums can be described by Fourier's law, and calculated as:

$$\frac{\partial}{\partial x} \Big( k \frac{\partial T}{\partial x} \Big) + \frac{\partial}{\partial y} \Big( k \frac{\partial T}{\partial y} \Big) + \frac{\partial}{\partial z} \Big( k \frac{\partial T}{\partial z} \Big) + \dot{q} = \rho c_p \frac{\partial T}{\partial t}$$

where  $\frac{\partial}{\partial x} \left( k \frac{\partial T}{\partial x} \right) + \frac{\partial}{\partial y} \left( k \frac{\partial T}{\partial y} \right) + \frac{\partial}{\partial z} \left( k \frac{\partial T}{\partial z} \right)$  is the net transfer of thermal energy into the control volume,  $\dot{q}$  is the thermal energy generation, and  $\rho c_p \frac{\partial T}{\partial t}$  is the change in thermal energy storage. k is thermal conductivity(which might be a function of temperature),  $\rho$  is density,  $c_p$  is heat capacity. [10]

For one-dimensional heat conduction, the thermal resistance of solids is introduced. Therefore, heat transfer through conduction can be written as:

$$q_{cond} = \frac{\Delta T}{R}; R = \frac{d}{kA}$$

where A is the cross-section for transferred amount of heat  $q_{cond}$ , d is the thickness,  $\Delta T$  is the temperature difference. In this work, interface heat resistance is neglected since it is quite small compared with the whole thermal resistance of the whole lamp package.

Convection of heat transfer can be regarded as:

$$q_{\rm conv} = hA(T_{\rm s}-T_{\infty})$$

where h is the convective heat transfer coefficient, A is surface area implied in the heat transfer process,  $T_s$  is the system temperature and  $T_\infty$  is the reference temperature. Parameter h is not a constant but depends on the type of convection, surface structure, and other geometrical parameters. [11]

Natural convection is a rather complex mechanism. Thermal expansion causes density differences, and thus hot air rises driven by force of density differences. The velocity of air is usually dependent on the geometric environment.

Radiation of heat transfer between surfaces is usually explained as:

$$q_{rad} = \varepsilon \sigma A T^4$$

where  $\sigma$  is Boltzmann constant (5.6704×10-8 W/m2K4), A is the radiating surface area, T is the temperature,  $\epsilon$  is the emissivity. [12]

The Optical energy loss is partially converted into heat by the efficiency of the phosphor. The energy of lumen output was calculated based on the following equation:

$$\varepsilon_{e,white} \left[ \frac{lm}{W} \right] = WPE (T, I) \cdot \varepsilon_{o,ph} \left[ \frac{lm}{W} \right] \cdot \eta_{QD} \cdot \eta_{ph}(T) \cdot \eta_{pkg}$$

where WPE (T, I) is the output optical power at junction temperature T and forward current I. It is also called wall-plug-efficiency which equals to internal quantum efficiency multiply extraction efficiency and then multiply electrical efficiency.  $\varepsilon_{o,ph}$  is the luminous efficacy of phosphor;  $\eta_{QD}$  is the quantum deficit in pumping phosphor;  $\eta_{oh}$  is phosphor quantum efficiency; and  $\eta_{pkg}$  is package efficiency. [13]

Based on these fundamental equations, a FEM model was build up to analyze the thermal behavior of a selected retrofit G4 LED product, to check the threshold for junction temperature with increased power input.

#### 2.4 Model Set Up and Simulation Analysis

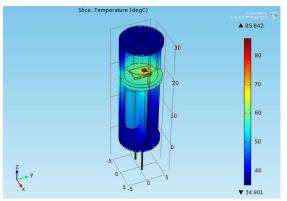

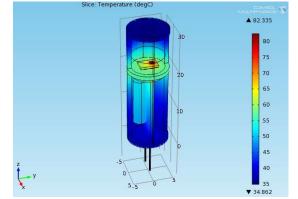

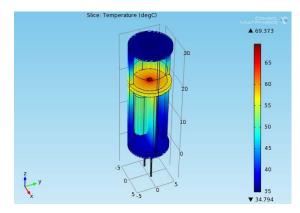

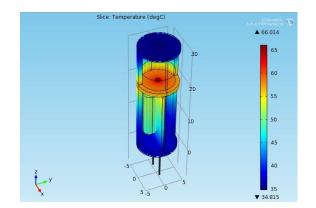

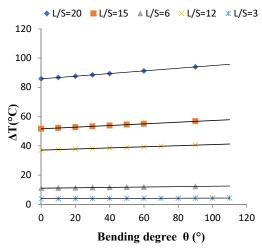

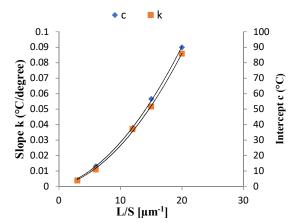

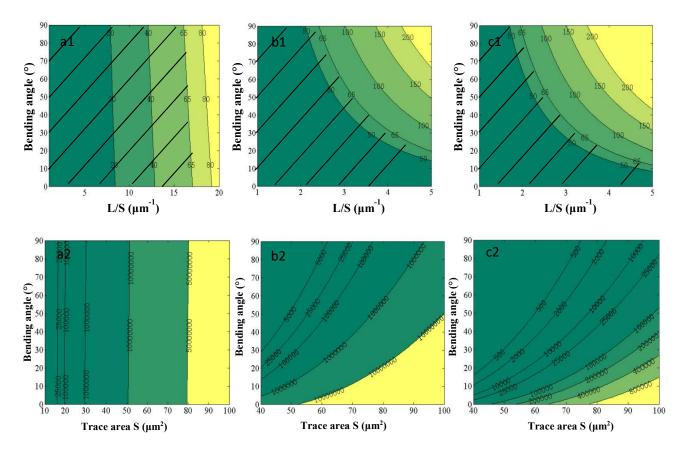

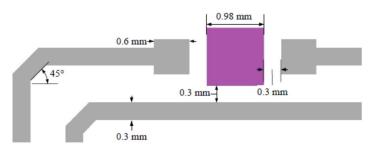

After fully understand the generated heat source and heat dissipation methods, software COMSOLTM Multi-physics 4.2 was used as a finite element method (FEM) tool for simulation. Models based on Finite element method (FEM) simulations were investigated to find a thermal-efficient integration method that enables heat dissipation and more uniformed heat distribution. The heat transfer module was used to calculate the temperature distribution. Through thermal simulation results and experiments, one can specifically determine which design is the best for applications demanding high lumen output within limited space such as G4 LED retrofit lamps.