**Delft University of Technology**

### A 200dB FoM 4-to-5GHz Cryogenic Oscillator with an Automatic Common-Mode Resonance Calibration for Quantum Computing Applications

Gong, Jiang; Chen, Yue; Sebastiano, Fabio; Charbon, Edoardo; Babaie, Masoud

DOI 10.1109/ISSCC19947.2020.9062913

Publication date 2020 **Document Version**

Accepted author manuscript

Published in 2020 IEEE International Solid-State Circuits Conference, ISSCC 2020

#### Citation (APA)

Gong, J., Chén, Y., Sebastiano, F., Charbon, E., & Babaie, M. (2020). A 200dB FoM 4-to-5GHz Cryogenic Oscillator with an Automatic Common-Mode Resonance Calibration for Quantum Computing Applications. In 2020 IEEE International Solid-State Circuits Conference, ISSCC 2020 (Vol. 2020-February, pp. 308-310). Article 9062913 IEEE. https://doi.org/10.1109/ISSCC19947.2020.9062913

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

### A 200dB FOM 4-5GHz Cryogenic Oscillator with an Automatic Common-Mode

## **Resonance Calibration for Quantum Computing Applications**

Low-power, low phase noise (PN) cryogenic frequency generation is required for the control electronics of quantum computers. To avoid limiting the performance of quantum bits, the frequency noise of a PLL should be <1.9kHz<sub>rms</sub> [1]. However, it is challenging for RF oscillators, as the heart of frequency synthesizers to satisfy such a requirement at cryogenic temperatures (CT), since 1) white noise in nanoscale CMOS devices is limited by temperature-independent shot noise; 2) the transistor 1/f noise is much higher, resulting in the oscillator PN being dominated by the 30dB/dec region [1].

Adjusting the oscillator common-mode (CM) resonance at twice the oscillation frequency ( $F_0$ ) is a powerful technique to minimize both white and 1/f noise upconversion in RF oscillators [2-3]. This condition has been previously satisfied even with a single tank by accurately modeling of CM inductance ( $L_{CM}$ ) and *manually* controlling the ratio of single-ended to differential-mode (DM) capacitance ( $X=C_C/C_D$ ) [2-3]. However, in the presence of PVT variations, the parasitic capacitance of the oscillator's core devices and of the switches in the capacitor banks change dramatically, shifting the expected frequency of the CM resonance. Consequently, the oscillator PN degrades significantly if the same control bits for the DM and CM capacitor banks ( $b_{CD}$ ,  $b_{CC}$ ) are used over PVT variations. This penalty is even more severe at CT, since the parasitic single-ended capacitances change significantly due to carrier freezeout in the substrate. In this paper, we propose a digital calibration loop to automatically adjust the configuration of the DM and CM capacitor banks to ensure that the oscillator always operates near its optimum performance, suppressing the oscillator PN at 100kHz offset frequency ( $\Delta$ f) by >10dB over the temperature range from 4K to 300K.

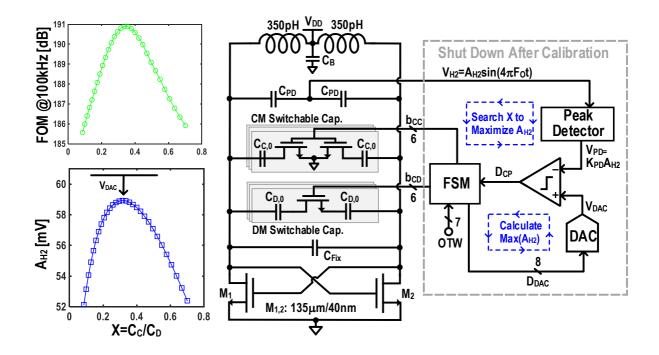

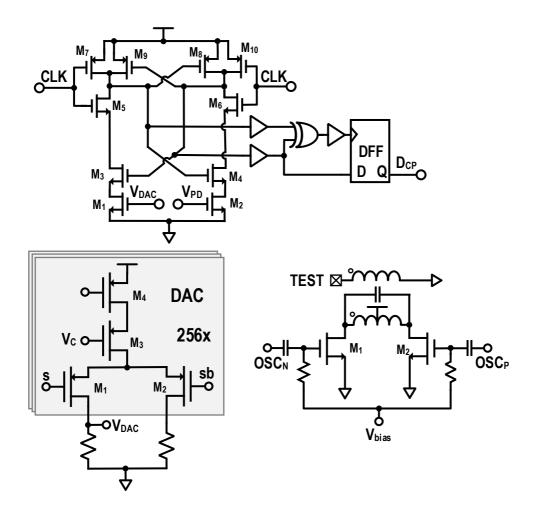

Fig.1 shows the block diagram of the proposed calibration loop and the oscillator schematic. Due to the auxiliary CM resonance at  $2F_0$ , the oscillator FOM, the tank's CM impedance and thus the amplitude of the  $2^{nd}$  harmonic component of the oscillation waveform (A<sub>H2</sub>) are simultaneously maximized for the same X value. Hence, the calibration goal is to find the optimum  $b_{CD}$  and  $b_{CC}$  codes in which A<sub>H2</sub>

is maximized. At the beginning of the calibration, the CM capacitor bank is kept off, while  $b_{CD}$  is set to reach the desired frequency, resulting in the lowest possible X. The 2<sup>nd</sup> harmonic of the oscillation voltage is extracted at the common node of differential capacitors C<sub>PD</sub>. A peak detector with a gain of K<sub>PD</sub> then produces a DC voltage (V<sub>PD</sub>) proportional to A<sub>H2</sub>. V<sub>PD</sub> is compared with the output of an 8-bit DAC (V<sub>DAC</sub>), and the result is fed to a finite-state machine (FSM). For now, suppose that V<sub>DAC</sub> is set exactly to the maximum V<sub>PD</sub> (=K<sub>PD</sub>·A<sub>H2,max</sub>). Initially, X is set at its minimum, and the tank configuration is not optimum; thus V<sub>PD</sub><V<sub>DAC</sub> and comparator output (D<sub>CP</sub>) is one. Consequently, the FSM increases X via reducing b<sub>CD</sub> by 1-LSB and increasing b<sub>CC</sub> by 2-LSBs. In this way, the tank's total capacitance (C<sub>C</sub>+C<sub>D</sub>) and thus F<sub>O</sub> remain almost constant during the calibration. This procedure continues until V<sub>PD</sub>≥V<sub>DAC</sub> and D<sub>CP</sub> becomes zero, indicating that the current b<sub>CD</sub> and b<sub>CC</sub> states are near to the optimum.

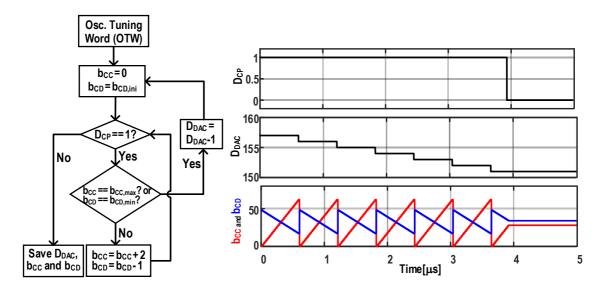

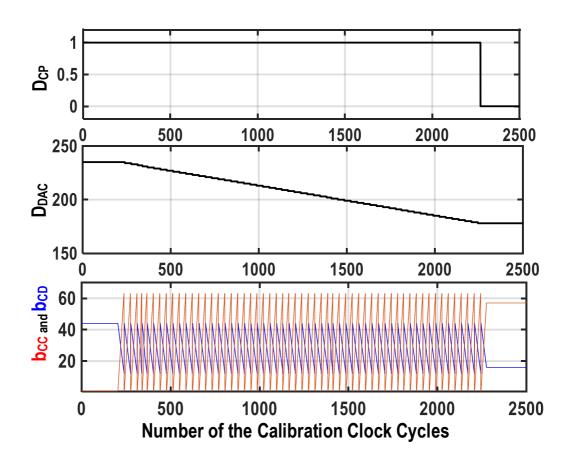

The maximum V<sub>PD</sub>, and hence the required V<sub>DAC</sub> depend on PVT, tank's CM quality factor ( $Q_{CM}$ ), and F<sub>0</sub>. Therefore, a second loop is added to adjust V<sub>DAC</sub>, accordingly. Initially, V<sub>DAC</sub> is intentionally set to a voltage level that is safely higher than the maximum possible V<sub>PD</sub>. Hence, D<sub>CP</sub> is always 1, resulting in X being swept from its minimum to maximum. The FSM then lowers down V<sub>DAC</sub> by 1-LSB and resets X to its minimum possible value again. This process is repeated until D<sub>CP</sub> becomes zero for the first time. At this point, the DAC and b<sub>CD</sub> and b<sub>CC</sub> states are frozen. The calibration circuit is then shut down to save power. In this design, the resistive DAC, comparator, and FSM emulate the behavior of an ADC while minimizing area and complexity. The flow chart of the proposed calibration loop and its related waveforms are shown in Fig.2.

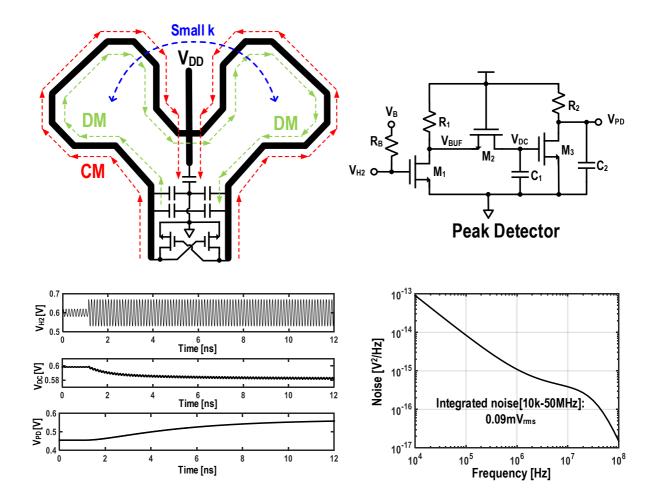

To satisfy the CM resonance condition,  $C_C/C_D$  should be adjusted to (1+k)/(3-5k), where k is the coupling factor between the tank inductors [1]. Prior works employed coils with an even number of turns (either as the tank main inductance [2] or a transformer's secondary windings [3,4]) to achieve k>0, allowing a large  $C_C$ . However, to attain a low PN at a low supply voltage, the tank's DM impedance should be reduced, thus advocating for the use of a single-turn inductor. Since in that case, k becomes negative,  $C_C$ , which includes parasitics, reduces to impractically small values. To minimize the unwanted magnetic

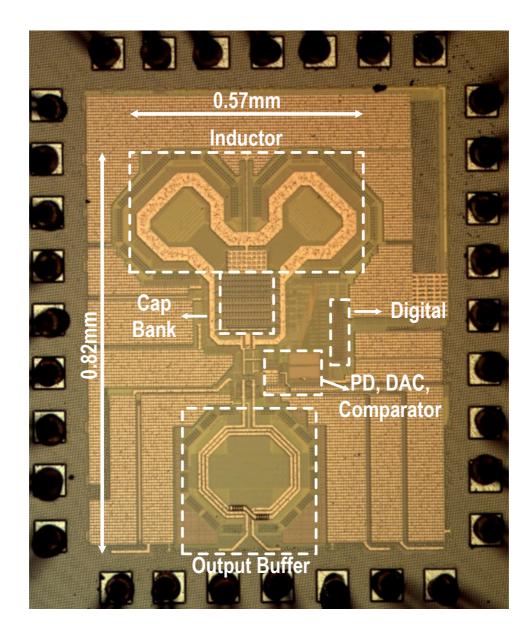

coupling, we use two individual coils placed orthogonally (see Fig.3). Furthermore, the center tap of the inductor is now much closer to the source of the core devices, thus alleviating parasitic  $L_{CM}$  by securing the shortest return path for the CM current. For the same inductance, the area of the proposed inductor is also ~30% lower compared to that of the conventional spiral one, but with a slightly lower DM and CM quality factor due to the partial magnetic-flux cancellation inside each half inductor.

In the peak-detection block in Fig.3, a buffer isolates the oscillator from the detector switching activities. Its output is then connected to the detector core, consisting of an NMOS transistor (M<sub>2</sub>) and a capacitor (C<sub>1</sub>). The voltage drop on the buffer load resistance (R<sub>1</sub>) is designed to be about the threshold voltage of M<sub>2</sub>. Hence, M<sub>2</sub> acts as a switch and only turns on in the negative half cycle of the buffer's output (V<sub>BUF</sub>). During this phase, M<sub>2</sub> ON resistance and C<sub>1</sub> form a low-pass filter to extract the average value of V<sub>BUF</sub> negative cycle, leading to a peak detection gain of ~1/ $\pi$ . Since the fundamental tone of V<sub>BUF</sub> is at 2F<sub>0</sub> (~10GHz), M<sub>2</sub> and C<sub>1</sub> are sized to achieve a few hundreds of MHz corner frequency to provide enough attenuation for V<sub>BUF</sub> high-frequency components and to guarantee the loop settling within ~20nsec, as shown in Fig.3. Another amplifier further boosts the desired signal to relax the requirements on the DAC resolution and the comparator noise. K<sub>PD</sub> of the entire peak detection block is ~6. The simulated noise of the calibration loop referred to the input of the peak detector is ~90µV<sub>rms</sub>, ensuring that the calibrated PN is within 1dB of the optimum, as evident from Fig.1 left.

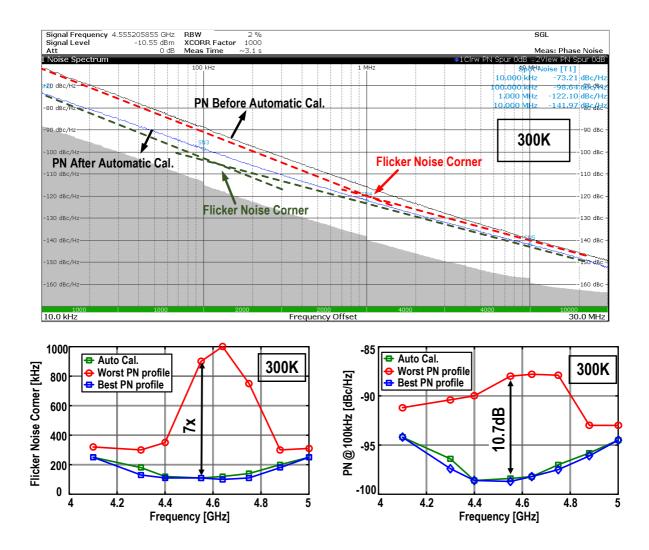

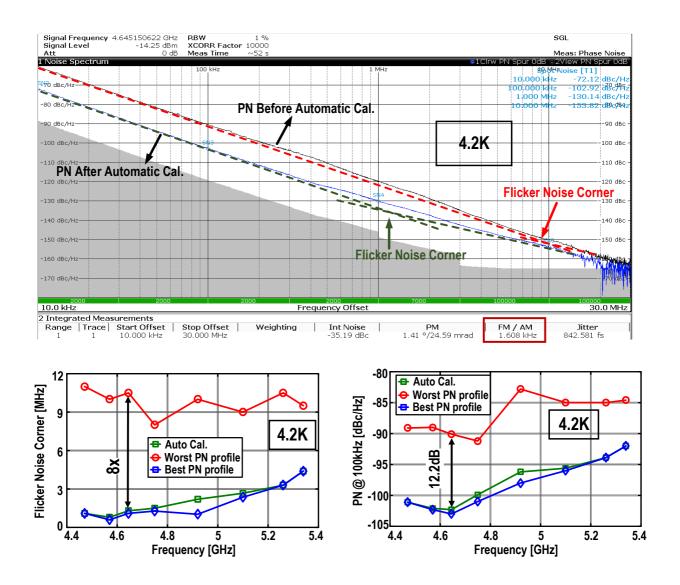

Fabricated in 40nm CMOS, the 0.15mm<sup>2</sup> oscillator consumes 4.3mW and 5.2mW at 300K and 4K, respectively (excluding 0.4mW of the calibration loop). The oscillator PN is measured over all possible  $b_{CC}$  and  $b_{CD}$  states while disabling the calibration to find the best and worst PN profiles for different frequencies. The calibration loop is then activated to investigate the effectiveness of the proposed technique. Fig.4 and 5 show the measured oscillator PN across its tuning range (TR) at 300K and 4K, respectively. The calibration loop successfully finds the optimum  $b_{CC}$  and  $b_{CD}$  codes, suppressing the oscillator PN at  $\Delta f$ =100kHz by 10dB at 300K and 12dB at 4K. It also reduces the 1/f noise corner from 1MHz(10.5MHz) to 130kHz(1.3MHz) at 300K(4K).

Compared to prior art (Fig.6), the FOM achieved at room temperature is limited by the low supply voltage and by the lower tank's quality factor, due to the use of a smaller single-turn inductor and a larger capacitor bank (see Fig.7). However, our work is the only one offering automatic CM resonance calibration, while requiring a negligible area overhead (0.01mm<sup>2</sup>). Thanks to the calibration loop and the optimization of the inductor layout, this work achieves a frequency noise of 1.6kHz and an FOM of 200dB at 4K. It also shows 4× lower 1/f corner, and 6dB higher FOM, compared to the cryogenic oscillator in [1]. The proposed technique will potentially enable the realization of cryogenic low-power low-jitter frequency synthesizers required for the control of quantum computers.

# References

[1] E. Charbon et al., "Cryo-CMOS circuits and systems for scalable quantum computing," *ISSCC*, pp. 264-265, Feb. 2017.

[2] D. Murphy et al., "A VCO with implicit common-mode resonance," /SSCC, pp. 442-443, Feb. 2015.

[3] M. Shahmohammadi et al., " A 1/f noise upconversion reduction technique applied to class-D and class-F oscillators," *ISSCC,* pp. 444-445, Feb. 2015.

[4] C. Lim et al., "An inverse-class-F CMOS VCO with intrinsic-high-Q 1st- and 2nd-harmonic resonances for 1/f<sup>2</sup>-to-1/f<sup>3</sup> phase-noise suppression achieving 196.2dBc/Hz FOM," *ISSCC*, pp. 374-376, Feb. 2018.

[5] M. Garampazzi et al., "Analysis and design of a 195.6 dBc/Hz peak FoM P-N Class-B oscillator with transformer-based tail filtering," in *IEEE Journal of Solid-State Circuits*, vol. 50, no. 7, pp. 1657-1668, July 2015.

Fig. 1: Simulated  $A_{H2}$  and FOM versus X for a class-D/F<sub>2</sub> oscillator (left); the block diagram of the proposed calibration (right).

Fig. 2: Calibration flowchart (left); the comparator output, DAC code, and the control bits of CM and DM capacitor bank during calibration (right).

Fig. 3: Oscillator floor plan with the proposed inductor (top left); the peak detector schematic (top right), and its simulated settling behavior (bottom left); the simulated input referred noise of the calibration loop (bottom right).

Fig. 4: Oscillator measured PN before and after calibration at 4.56GHz (top); Oscillator's performance over its tuning range for the worst, best, and calibrated phase noise profiles (bottom) at 300K.

Fig. 5: Oscillator measured PN before and after calibration at 4.65GHz (top); Oscillator's performance over its tuning range for the worst, best, and calibrated phase noise profiles (bottom) at 4.2K.

|                                    | This Work                                      |                              | ISSCC'2017<br>[1]                              | ISSCC'2015<br>[2]                | ISSCC'2015<br>[3]                              | ISSCC'2018<br>[4]                       | JSSC'2015<br>[5]                     |

|------------------------------------|------------------------------------------------|------------------------------|------------------------------------------------|----------------------------------|------------------------------------------------|-----------------------------------------|--------------------------------------|

| Osc. Topology                      | NMOS<br>CM Resonance<br>Class-D/F <sub>2</sub> |                              | NMOS<br>CM Resonance<br>Class-F <sub>2,3</sub> | NMOS<br>Implicit CM<br>Resonance | NMOS<br>CM Resonance<br>Class-F <sub>2,3</sub> | CMOS<br>CM Resonance<br>Inverse Class-F | NMOS<br>2f <sub>LO</sub> Tail Tuning |

| Temperature [K]                    | 300                                            | 4.2                          | 4.2                                            | 300                              | 300                                            | 300                                     | 300                                  |

| Frequency [GHz]                    | 4.6                                            | 4.65                         | 6.3                                            | 3.3                              | 7                                              | 4.51                                    | 8.4                                  |

| Supply Voltage [V]                 | 0.5                                            | 0.6                          | 1                                              | 0.9                              | 1                                              | 0.6                                     | 1.5                                  |

| Tuning Range                       | 4.1-5<br>(19.8%)                               | 4.4-5.3<br>(18.6%)           | 5.8-7.3<br>(25%)                               | 2.85-3.37<br>(27.2%)             | 5.4-7<br>(25%)                                 | 3.49-4.51<br>(25.5%)                    | 7.4-8.4<br>(12.7%)                   |

| Power [mW]                         | 4.3                                            | 5.3                          | 12                                             | 6.8                              | 10                                             | 1.14                                    | 20                                   |

| PN [dBc/Hz]<br>@100kHz/1MHz/10MHz  | -99.3/<br>-123.1/<br>-143.1                    | -102.9/<br>-130.2/<br>-153.8 | -94/<br>-120/<br>-149                          | -106*/<br>-129.5*/<br>-150.2*    | -102.1/<br>-124.5/<br>-144.5                   | -98.5/<br>-123.7*/<br>-143.7            | -88*/<br>-118*/<br>-146.8            |

| FOM [dBc/Hz]<br>@100kHz/1MHz/10MHz | 186.2/<br>190/<br>190                          | 189/<br>196.3/<br>200        | 179.2/<br>185/<br>194                          | 188/<br>191.5/<br>192.2          | 188.9/<br>191.4/<br>191.4                      | 191/<br>196.2/<br>196.2                 | 173.5/<br>183.5/<br>192.3            |

| Flicker Corner [kHz]               | 130                                            | 1300                         | 5700                                           | 200                              | 130                                            | 300                                     | 600                                  |

| Technology                         | 40nm                                           |                              | 40nm                                           | 28nm                             | 40nm                                           | 65nm                                    | 55nm                                 |

| Osc. Area [mm <sup>2</sup> ]       | 0.14                                           |                              | 0.13                                           | 0.19                             | 0.13                                           | 0.14                                    | 0.17                                 |

| Cal. Area [mm <sup>2</sup> ]       | 0.01                                           |                              | NA                                             | NA                               | NA                                             | NA                                      | NA                                   |

| Inductor                           | One Turn                                       |                              | 1:2 XFMR                                       | Two Turns                        | 1:2 XFMR                                       | 2:4 XFMR                                | One turn+tail<br>Ind.                |

| Common-mode<br>Resonance Cal.      | Auto                                           |                              | Manual                                         | Manual                           | Manual                                         | Manual                                  | NA                                   |

\*Estimated from the measured phase noise plot of the oscillator

Fig. 6: Table of comparison with prior art employing the common-mode resonance technique.

Fig. 7: Die micrograph.

Fig. S.1: Measured settling of the calibration loop. For this measurement, instead of the regular 50MHz clock frequency, a very low-speed clock (0.5kHz) is used for the calibration loop to allow monitoring of the comparator output, DAC code, and  $b_{CC}$  and  $b_{CD}$  states during the calibration via an SPI link. The calibration loop successfully settles from an initial setting (1, 44) to the optimized  $b_{CC}$  and  $b_{CD}$  states (57, 16).

Fig. S.2: Schematics of the comparator, the current steering cell of the 8-b DAC, and the output buffer.

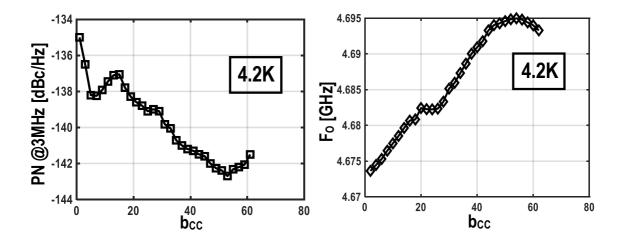

Fig. S.3: Measured PN and oscillation frequency ( $F_0$ ) versus  $b_{CC}$  while sweeping X=C<sub>C</sub>/C<sub>D</sub> at 4.2K. At each sweep step,  $b_{CC}$  is increased by 2-LSBs and  $b_{CD}$  is reduced by 1-LSB. In this way,  $F_0$  remains almost constant during the calibration. When this technique is employed in a PLL,  $F_0$  is first roughly adjusted by the coarse frequency selector, this calibration is then run to find the optimum X, and finally PLL locks to the desired frequency by using tracking bank.