# A defect-oriented test approach using on-Chip current sensors for resistive defects in FinFET SRAMs

Medeiros, G.C.; Bolzani Poehls, L.M.; Taouil, M.; Luis Vargas, F.; Hamdioui, S.

DOI

10.1016/j.microrel.2018.07.092

**Publication date**

**Document Version** Accepted author manuscript

Published in Microelectronics Reliability

Citation (APA)

Medeiros, G. C., Bolzani Poehls, L. M., Taouil, M., Luis Vargas, F., & Hamdioui, S. (2018). A defect-oriented test approach using on-Chip current sensors for resistive defects in FinFET SRAMs. *Microelectronics* Reliability, 88-90, 355-359. https://doi.org/10.1016/j.microrel.2018.07.092

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# A Defect-Oriented Test Approach Using On-Chip Current Sensors for Resistive Defects in FinFET SRAMs

G. C. Medeiros<sup>a</sup>, L. M. Bolzani Poehls<sup>b</sup>, M. Taouil<sup>a</sup>, F. Luis Vargas<sup>b</sup>, S. Hamdioui<sup>a</sup>

<sup>a</sup> Delft University of Technology, Mekelweg 4, 2628 CD Delft, The Netherlands <sup>b</sup> Pontifcal Catholic University of Rio Grande do Sul (PUCRS), Av. Ipiranga 6681, Porto Alegre, Brazil

#### Abstract

Resistive defects in FinFET SRAMs are an important challenge for manufacturing test in submicron technologies, as they may cause dynamic faults, which are hard to detect and therefore may increase the number of test escapes. This paper presents a defect-oriented test that uses On-Chip Current Sensors (OCCS) to detect weak resistive defects by monitoring the current consumption of FinFET SRAM cells. Using OCCS, all our single cell injected resistive defects have been detected within a certain accuracy by applying 5 read or write operations only, independent whether they cause static or dynamic faults. The proposed approach has been validated and the detection accuracy has been evaluated. Simulation results show that the approach is even able to detect weak resistive defects that do not even sensitize faults at the functional level, thus able to increase the reliability of devices.

## 1. Introduction

Technology miniaturization has presented many challenges on conventional planar Complementary Metal-Oxide Semiconductor (CMOS) transistors [1]. FinFET technology has become the best approach to continue the downscaling of Integrated Circuits (ICs) [2] as it shows improved short-channel behaviour and overcomes the growing subthreshold leakage of CMOS technology [3,4]. Nevertheless, to achieve high storage density and access speed, Static Random Access Memories (SRAMs) are produced at the limits of the process equipment and therefore statistically more prone to be affected by manufacturing defects [5]. As a result, these devices must be efficiently tested i.e., a high defect/fault coverage at low cost.

Weak resistive defects are known for causing dynamic faults, a subset of faults that are only sensitized by a sequence of consecutive operations. Many fault-oriented test approaches, such as standard March algorithms, do not target these types of faults [6–8] or are limited by the number of consecutive operations [9–12]. Using exhaustive March tests to sensitize faults results in expensive

manufacturing tests, as the test cost is directly related to the time each product stays on the tester [13]. Disparate approaches, such as monitoring the static or dynamic current consumption of SRAM cells [14–17], have been proposed to improve the detection of weak defects. Nevertheless, their efficacy regarding FinFET devices affected by resistive defects is unknown.

This paper presents a defect-oriented test approach based on On-Chip Current Sensors [18,19] for testing FinFET memories. Rather than focusing on the faults caused by resistive defects, the proposed approach concentrates on their effect on current characteristics. We use OCCSs to monitor identify discrepancies in the consumption of each SRAM cell caused by resistive defects. The results show that all our single cell injected resistive defects have been detected within a certain accuracy by applying only 5 read or write operations, independent whether they cause static or dynamic faults. Furthermore, the proposed approach is able to detect weak resistive defects that do not even sensitize faults at the functional level. The main contributions of this paper are as follows:

• A memory test methodology using OCCS

able to detect weak and strong resistive defects. It can significantly reduce test time, and therefore reduce manufacturing test cost.

- Verification of the proposed approach and evaluation of its detection coverage using Spice simulations.

- Evaluation of the overhead of the proposed scheme.

The remainder of this paper is organized as follows. Section II lays out the background related to FinFET technology and testing. Section III details the proposed methodology based on OCCS, whereas Section IV presents its validation. Then, Section V discusses its detection capability based on simulations and the overhead of the approach. Finally, Section 6 concludes this paper.

## 2. FinFET Technology and Testing

In this section, background information on the FinFET technology and FinFET device testing will be provided.

# 2.1. FinFET technology

FinFETs transistors are quasi-planar, multi-gate devices consisting of vertical stripes of silicon denominated "fins" that are wrapped by a gate structure [20]. This technology's main advantage are reduced Short-Channel Effects (SCEs) as the gate controls multiple sides of the channel [21]. It consequently reduces the leakage current and boosts the technology miniaturization even further. Other advantages of FinFET technology are its improved electrostatic characteristics [22] and its compatibility with the standard CMOS fabrication process [23]. Furthermore, FinFET technology provides specific advantages to SRAM memories' performance and stability. Conventional CMOS SRAM sizes are limited by the random variations of V<sub>TH</sub> caused by Random Dopant Fluctuation (RDF) introduced by high doping [23]. As FinFET devices do not require high doping concentration to control the leakage current [4], its RDF is expressively reduced [24], thus minimizes  $V_{\text{TH}}$  variations and allows the  $V_{\text{DD}}$  to be scaled down [25].

## 2.2. FinFET testing

One of the biggest challenges of SRAM testing is using realistic defect and fault models alongside test solutions with minimal application time [26]. As

companies adopt FinFET technology in their new products, the use of standard memory test procedures that were developed with defect and faults models of planar technologies may not be sufficient to provide the desired fault coverage for FinFET devices. The reason for this are differences in its physical structure and additional manufacturing steps. Harutyunyan et al. investigated the impact of resistive defects in FinFET-based memories and concluded that such memories are more susceptible to dynamic faults [27] than memories designed with planar technologies. Due to this distinction, they proposed a FinFET-specific March algorithm [12] that relies on the execution of up to 8 consecutive operations applied to the same cell. Faults that require more than 8 consecutive operations are not sensitized, and hence not detected. Dynamic coupling faults in FinFET SRAMs have also been reported by Copetti et al. [28]. Consequently, March algorithms for FinFET memories should also address such faults.

Lin et al. [17] investigated the efficacy of using March Tests as well as  $I_{DDQ}$  to detect Gate Oxide Shorts (GOS) in FinFET SRAMs. According to the authors, this type of defects causes more complex fault behaviours in FinFETs than in planar transistors due to their unique structure. They concluded that both methodologies may present limitations for this technology, which can effectively increase the number of test escapes and reduce cell's reliability. Therefore, test solutions that rely on operations executing specific patterns and stressing conditions may not stand to be reliable strategies for investigating the presence of other types of defects in FinFET circuits.

# 3. Methodology

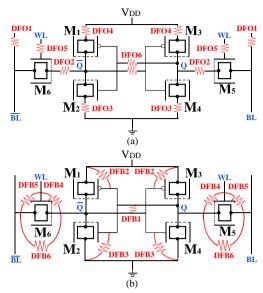

This paper introduces a defect-oriented test approach based on OCCS to detect resistive defects, including weak defects, on FinFET-based SRAMs. Rather than focusing on faults and observing output of operations, the proposed approach concentrates on the impact of resistive defects on the switching current during read and write operations of the memory cells. Fig. 1 illustrates the schematic of the 6T SRAM cell and the injected resistive defects. They are modelled as resistive-open (RO) defects (Fig. 1(a)), which create resistances in existing connections, and resistive-bridge (RB) defects (Fig. 1(b)), which create connections between two different nodes.

Fig. 1. Set of Resistive defects injected in memory cells: (a) Resistive-Open and (b) Resistive-Bridge defects.

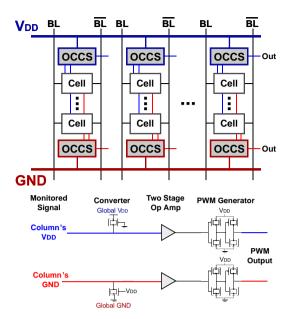

The proposed methodology monitors the current flowing on V<sub>DD</sub> and GND by inserting a set of OCCSs [18,19] (one for  $V_{DD}$  and one GND) in each column of the memory array. The architecture of the proposed approach is presented in Fig. 2. OCCSs are composed of three functional blocks: (1) a current-to-voltage converter, (2) a two-stage operational amplifier, and (3) a Pulse-Width Modulation (PWM) generator. A current-to-voltage converter is inserted prior to the operational amplifier. This single transistor works as a low impedance resistor that generates small voltage changes in V<sub>DD</sub> and GND nodes based on the current consumption of each column. Therefore, any current flowing in the column's cells causes voltage changes in the power supply signal. Owing to these variations, this signal is used as the input for the operational amplifier. It generates pulses that are afterwards modulated by the PWM circuitry to represent the unique behaviours of the monitored current consumption signal. Because resistive defects alter current characteristics, defective cells present a different current consumption compared to their defect-free neighbours. This ultimately creates distinct pulses and modulated signals. Finally, a detection logic circuit compares the signals generated by OCCSs and raises a flag whenever a mismatch is observed.

Defects of different magnitudes have been injected to sensitize their detection conditions. Three scenarios were considered: the defect is too weak to

Fig. 2. Architecture of the proposed hardware-based approach.

sensitize any fault; the defect is strong enough to sensitize dynamic faults; and the defect is strong and sensitizes static faults. The first two scenarios are responsible for the majority of test escapes and reliability problems, and are therefore the focus of the proposed approach. To obtain realistic defect values for the defects in Fig. 1, we use the data presented in [28].

#### 4. Results

## 4.1. Simulation Setup

The simulation platform consists of an 8 x 8 SRAM array, where the bit lines and word lines have capacitive loads which emulate a 16 KB memory array. The peripheral circuitry around the SRAM array ensure proper execution of read and write operations; each memory column had its own write driver, differential sense amplifier, and pre-charger. The frequency is set to 1 GHz, the operating temperature to 27°C, and the supply voltage to 0.9 V.

A Low Power (LP), Multi-Gate (MG) 20nm FinFET compact model developed by [29] that describes Shorted-Gate, Bulk Mode FinFETs transistors was adopted. All circuits and memory peripherals (buffers, decoders, sense amplifiers, prechargers, etc.) were described in Spice using the same compact model.

Table 1 Critical resistances and detection efficacy for the proposed defect-oriented test approach

| Defect | Critical Resistances [28] | Resistance<br>Resolution  |

|--------|---------------------------|---------------------------|

| DFO1   | $13.6~\mathrm{k}\Omega$   | $3.85~\mathrm{k}\Omega$   |

| DFO2   | $145~\mathrm{k}\Omega$    | $1.30~\mathrm{k}\Omega^*$ |

| DFO3   | $72.5~\mathrm{k}\Omega$   | $1.40~\mathrm{k}\Omega^*$ |

| DFO4   | -                         | $1.60~\mathrm{k}\Omega$   |

| DFO5   | $1.52~\mathrm{M}\Omega$   | $82~\mathrm{k}\Omega$     |

| DFO6   | $1.82~\mathrm{M}\Omega$   | $20~k\Omega$              |

| DFB1   | $37.6~\mathrm{k}\Omega$   | $3.60~\mathrm{M}\Omega^*$ |

| DFB2   | $13.7 \text{ k}\Omega$    | $2~\mathrm{M}\Omega$      |

| DFB3   | $46~\mathrm{k}\Omega$     | $4.9~\mathrm{M}\Omega$    |

| DFB4   | $13.65 \text{ k}\Omega$   | $1.7~\mathrm{M}\Omega$    |

| DFB5   | $4.8~\mathrm{k}\Omega$    | $40~\mathrm{k}\Omega$     |

| DFB6   | $11.4~\mathrm{k}\Omega$   | $1.28~\mathrm{M}\Omega$   |

<sup>\*</sup> Weakest defect injected

The current consumption of the cell is analysed using a simple March sequence. This algorithm first initializes all cells, assuring that they are in the same state. Then, it sequentially applies the sequence write '0', read '0', write '1', read '1' (w0, r0, w1, r1) to each row of the array. Thus, the algorithm can be written as \$(w1); \$(w0, r0, w1, r1).

# 4.2. Simulation Results

The detection accuracy of the proposed approach is analysed by comparing OCCSs' outputs of defect-free and defective cells for a given defect. The critical resistance values  $R_{\rm C}$  of a defect is the weakest defect value that is able to sensitize any fault using traditional March-based testing. We analyse the detection capability by sweeping the value of the resistive defect between a certain range. For a RO defect, the lower bound of this range equals to 1/100 of  $R_{\rm C}$ , while the upper bound is set equal to  $R_{\rm C}$ . For RB defects, the opposite applies; the lower bound equals  $100*R_{\rm C}$ , while the upper bound is set equal to  $R_{\rm C}$ .

The results of the experiments are shown in Table 1. The table shows for each defect its R<sub>C</sub> and resistance resolution. The latter is defined as the minimum (for opens) or maximum (for bridges) resistance value that is detectable by the output of the OCCS. For some defects, detection was already possible when the weakest defect for this evaluation

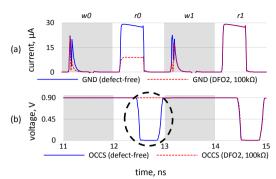

Fig. 3. Simulation of defect DFO2 (a) input of OCCSs (b) output of OCCSs

was injected; such cases are identified with an asterisk. Note that the resistance resolution is always lower with respect to R<sub>C</sub> for resistive-open defects, while higher for resistive-bridge defects. Therefore, the detection capability is better than traditional based March tests.

Next, we will analyse two representative cases in more detail. They are the RO defect DFO2 and RB defect DFB5. Fig. 3 depicts the input and output waveform of the OCCS for defect DFO2=100  $k\Omega$ when the March element  $\psi(w0, r0, w1, r1)$  is executed. Part a of the figure shows the input current to the OCCS that is connected to the ground, while part b the output voltage. The blue lines represent the signals for a defect-free cell, while red dashed lines represent the signals of the cell with the defect present. During the r0 operation, there's a sharp discrepancy in current consumption between cells. This disparity results in the PWM circuit producing two distinct signals at the OCCS's output, highlighted on Fig. 3(b). Other small current disparities are observed during write operations but are not visible at the sensor's output. Note that as the defect value of 100 k $\Omega$  is lower than R<sub>C</sub>=145 k $\Omega$ , this defect cannot be detected by conventional March

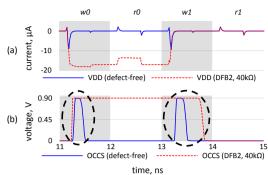

Similarly, Fig. 4 shows the input and output waveform of the OCCS for defect DFB5=40 k $\Omega$  that is connected to  $V_{DD}$ . Again, blue lines represents the defect-free cell, while red dashed lines the defective cell. The discrepancy in consumption during the w0 and r0 operations caused by the resistive-bridge defect results in distinct OCCS output signals. In fact, during the r0 operation, the output of the sensor monitoring the column with the defective cells is a strong '1', while the sensor from the defect-free column outputs a strong '0'. Conventional March tests would not detect this defect as the resistance of  $40 \text{ k}\Omega$  is larger than  $R_{C}$ =4.8 k $\Omega$ .

Fig. 4. Simulation of defect DFB2 (a) input of OCCSs (b) output of OCCSs

## 4.3. Discussion and limitations

Power consumption, test time, and area overhead of the proposed approach were also evaluated. The power consumption was measured during the execution of the adopted March algorithm before and after the insertion of OCCS monitors. Without the monitors, a power consumption of  $806.63~\mu W$  has been measured. An increase of 15% has been observed when the monitors were added.

One of the main advantages of the proposed approach is the reduction in test time. Standard test algorithms can be very time expensive, especially if targeting dynamic, coupling, or linked faults. However, the proposed approach does not rely upon what type of faults are sensitized by the defects, or if there are faults at all. Only 5 operations are necessary to ensure that each cell is put under transition scenarios ('0' to '1', and '1' to '0'). Thus, it can significantly reduce the test time and therefore reduce manufacturing test cost. Moreover, it can also increase the reliability as many weak defects can be detected as well.

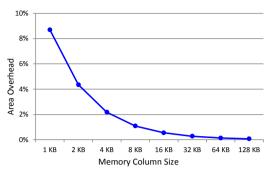

An accurate area overhead cannot be estimated as the compact FinFET model does not have a physical layout. However, a general area overhead can be roughly estimated by comparing the number of fins in a column and the number of fins in two OCCSs (one for V<sub>DD</sub> and one for GND). Note that the word size does not impact the relative area overhead. Fig. 5 shows the area overhead for different column sizes. For a 1 KB memory column, the introduction of sensors has approximately an overhead of 8.69%. For a 4 KB memory column, this overhead decreases to 2.17%. In case the memory contains multiple smaller arrays, the same OCCS can be reused as long as only one memory is active at a time. Therefore, varied memory organizations can be adopted to reduce the area overhead of the approach.

Fig. 5. Area overhead for different column sizes.

# 5. Conclusion

This paper presented a defect-oriented test approach that identifies the presence of resistive defects in FinFET-based SRAM memory cells by connecting OCCS monitors to VDD and GND. All injected resistive defects were detected within a certain accuracy applying 5 operations only, independent whether they caused static or dynamic faults. Compared to other March tests, the proposed approach has a very small test time. In the future, we would like to analyse the impact of inter-cell defects as well.

# Acknowledgements

This work is part of a project that has received funding from the European Union's Horizon 2020 research and innovation programme under the Marie Skłodowska-Curie grant agreement No 722325.

## References

- V. De, S. Borkar, Technology and design challenges for low power and high performance, Proc. 1999 Int. Symp. Low Power Electron. Des. - ISLPED '99. (1999) 163–168. doi:10.1145/313817.313908.

- [2] I. Ferain, C.A. Colinge, J.-P. Colinge, Multigate transistors as the future of classical metal–oxide– semiconductor field-effect transistors, Nature. 479 (2011) 310–316. doi:10.1038/nature10676.

- [3] K. Roy, S. Mukhopadhyay, H. Mahmoodi-Meimand, Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits, Proc. IEEE. 91 (2003) 305–327. doi:10.1109/JPROC.2002.808156.

- [4] K.J. Kuhn, Considerations for Ultimate CMOS Scaling, IEEE Trans. Electron Devices. 59 (2012) 1813–1828. doi:10.1109/TED.2012.2193129.

- [5] P. Girard, A. Bosio, L. Dilillo, S. Pravossoudovitch,

- A. Virazel, Basics on SRAM Testing, in: Adv. Test Methods SRAMs, Springer US, Boston, MA, 2010: pp. 1–19. doi:10.1007/978-1-4419-0938-1\_1.

- [6] L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, S. Borri, M. Hage-Hassan, Resistive-Open Defects in Embedded-SRAM Core Cells: Analysis and March Test Solution, in: 13th Asian Test Symp., IEEE, 2004: pp. 266–271. doi:10.1109/ATS.2004.75.

- [7] S. Borri, M. Hage-Hassan, L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, Analysis of Dynamic Faults in Embedded-SRAMs: Implications for Memory Test, J. Electron. Test. 21 (2005) 169–179. doi:10.1007/s10836-005-6146-1.

- [8] P. Dubey, A. Garg, S. Mahajan, Study of Read Recovery Dynamic Faults in 6T SRAMS and Method to Improve Test Time, J. Electron. Test. 26 (2010) 659–666. doi:10.1007/s10836-010-5176-5.

- [9] S. Hamdioui, Z. Al-Ars, A.J. van de Goor, Testing static and dynamic faults in random access memories, in: Proc. 20th IEEE VLSI Test Symp. (VTS 2002), IEEE Comput. Soc, 2002: pp. 395–400. doi:10.1109/VTS.2002.1011170.

- [10] A. Benso, A. Bosio, S. Di Carlo, G. Di Natale, P. Prinetto, March AB, march AB1: new march tests for unlinked dynamic memory faults, in: IEEE Int. Conf. Test, 2005., IEEE, 2005: pp. 834–841. doi:10.1109/TEST.2005.1584047.

- [11] A. Bosio, S. Di Carlo, G. Di Natale, P. Prinetto, March AB, a state-of-the-art march test for realistic static linked faults and dynamic faults in SRAMs, IET Comput. Digit. Tech. 1 (2007) 237–245.

- [12] G. Harutyunyan, S. Martirosyan, S. Shoukourian, Y. Zorian, Memory Physical Aware Multi-Level Fault Diagnosis Flow, IEEE Trans. Emerg. Top. Comput. (2018) 1–1. doi:10.1109/TETC.2018.2789818.

- [13] J.-C. Yeh, S.-F. Kuo, C.-H. Chen, C.-W. Wu, A Systematic Approach to Memory Test Time Reduction, IEEE Des. Test Comput. 25 (2008) 560– 570. doi:10.1109/MDT.2008.152.

- [14] S.S. Sabade, D.M. Walker, IDDX-based test methods, ACM Trans. Des. Autom. Electron. Syst. 9 (2004) 159–198. doi:10.1145/989995.989997.

- [15] D. Arumi, R. Rodríguez-Montañés, J. Figueras, S. Eichenberger, C. Hora, B. Kruseman, M. Lousberg, IDDQ-based diagnosis at very low voltage (VLV) for bridging defects, Electron. Lett. 43 (2007) 273. doi:10.1049/el:20073573.

- [16] G. Gyepes, V. Stopjaková, D. Arbet, L. Majer, J. Brenkuš, A new IDDT test approach and its efficiency in covering resistive opens in SRAM arrays, Microprocess. Microsyst. 38 (2014) 359–367. doi:10.1016/j.micpro.2014.04.006.

- [17] C.W. Lin, M.C.-T. Chao, C.C. Hsu, Investigation of gate oxide short in FinFETs and the test methods for FinFET SRAMs, in: Proc. IEEE VLSI Test Symp., IEEE, 2013: pp. 1–6. doi:10.1109/VTS.2013.6548929.

- [18] F. Lavratti, L. Bolzani, A. Calimera, F. Vargas, E. Macii, Technique based on On-Chip Current Sensors

- and Neighbourhood Comparison Logic to detect resistive-open defects in SRAMs, in: 2013 14th Lat. Am. Test Work. LATW, IEEE, 2013: pp. 1–6. doi:10.1109/LATW.2013.6562688.

- [19] A.F. Gomez, F. Lavratti, G. Medeiros, M. Sartori, L.B. Poehls, V. Champac, F. Vargas, Effectiveness of a hardware-based approach to detect resistiveopen defects in SRAM cells under process variations, Microelectron. Reliab. 67 (2016) 150– 158. doi:10.1016/J.MICROREL.2016.10.012.

- [20] D. Hisamoto, T. Kaga, Y. Kawamoto, E. Takeda, A fully depleted lean-channel transistor (DELTA)-a novel vertical ultra thin SOI MOSFET, in: Int. Tech. Dig. Electron Devices Meet., IEEE, 1989: pp. 833– 836. doi:10.1109/IEDM.1989.74182.

- [21] S.H. Tang, L. Chang, N. Lindert, Yang-Kyu Choi, Wen-Chin Lee, Xuejue Huang, V. Subramanian, J. Bokor, Tsu-Jae King, Chenming Hu, FinFET-a quasi-planar double-gate MOSFET, in: 2001 IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap. ISSCC (Cat. No.01CH37177), IEEE, 2001: p. 118– 119., doi:10.1109/ISSCC.2001.912568.

- [22] J.P. Colinge, FinFETs and other multi-gate transistors, Springer US, Boston, MA, 2008. doi:10.1007/978-0-387-71752-4.

- [23] D. Bhattacharya, N.K. Jha, FinFETs: From Devices to Architectures, Adv. Electron. 2014 (2014) 1–21. doi:10.1155/2014/365689.

- [24] D. Chen, N.K. Jha, Introduction to Nanotechnology, in: N.K. Jha, D. Chen (Eds.), Nanoelectron. Circuit Des., 2011: pp. 1–22. doi:10.1007/978-1-4419-7609-

- [25] T. Matsukawa, S.O. Uchi, K. Endo, Y. Ishikawa, H. Yamauchi, Y.X. Liu, J. Tsukada, K. Sakamoto, M. Masahara, Comprehensive analysis of variability sources of FinFET characteristics, 2009 Symp. VLSI Technol. (2009) 118–119.

- [26] A. Bosio, L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, Advanced Test Methods for SRAMs, Springer US, Boston, MA, 2010. doi:10.1007/978-1-4419-0938-1.

- [27] G. Harutyunyan, G. Tshagharyan, V. Vardanian, Y. Zorian, Fault modeling and test algorithm creation strategy for FinFET-based memories, in: 2014 IEEE 32nd VLSI Test Symp., IEEE, 2014: pp. 1–6. doi:10.1109/VTS.2014.6818747.

- [28] T.S. Copetti, T.R. Balen, G.C. Medeiros, L.M.B. Poehls, Analyzing the behavior of FinFET SRAMs with resistive defects, in: 2017 IFIP/IEEE Int. Conf. Very Large Scale Integr., IEEE, 2017: pp. 1–6. doi:10.1109/VLSI-SoC.2017.8203483.

- [29] Nanoscale Integration and Modeling (NIMO), Predictive Technology Model (PTM), (2012). http://ptm.asu.edu/.