# There's More to the Picture Than Meets the Eye\*, and in the future it will only become more so

Theuwissen, Albert

DOI

10.1109/ISSCC42613.2021.9366058

Publication date

2021

**Document Version**

Accepted author manuscript

Published in

2021 IEEE International Solid-State Circuits Conference, ISSCC 2021 - Digest of Technical Papers

Citation (APA)

Theuwissen, A. (2021). There's More to the Picture Than Meets the Eye\*, and in the future it will only become more so. In 2021 IEEE International Solid-State Circuits Conference, ISSCC 2021 - Digest of Technical Papers (pp. 30-35). Article 9366058 (Digest of Technical Papers - IEEE International Solid-State Circuits Conference; Vol. 64). https://doi.org/10.1109/ISSCC42613.2021.9366058

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights.

We will remove access to the work immediately and investigate your claim.

# THERE'S MORE TO THE PICTURE THAN MEETS THE EYE\*,

# and in the future it will only become more so

Prof. Dr. Albert Theuwissen

Harvest Imaging (B), Delft University of Technology (NL)

#### Abstract

Over the past five decades, solid-state imaging has gone through a difficult "childhood", changing technology during its "adolescence", and finally growing up to become a mature, "adult" technology that can compete with the human visual system when it comes to image quality. State-of-the-art mobile devices enjoyed by consumers, rely on a multi-disciplinary mixture of analog electronics, digital circuits, mixed-signal design, optical know-how, device physics, semiconductor technology and algorithm development. As a result, the CMOS image sensors utilized in today's mobile phones come close to perfection as far as imaging characteristics are concerned. However this does not mean that further developments in the field are no longer necessary. On the contrary, new technologies and new materials are opening up new dimensions and new applications which complement the classical imaging functionality of the sensors. This trend will ultimately convert the image sensor landscape from image capturing to smart vision. Consequently, the future of solid-state imaging will not revolve around the shooting of beautiful images only, as the market driver will no longer only be limited to the mobile phone market.

#### Introduction

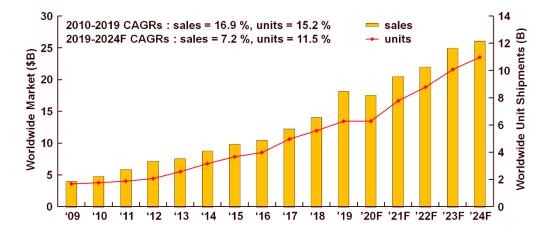

One of the fastest growing markets in the semiconductor industry is being driven by businesses in the solid-state imaging sector. An overview of the world-wide CIS market is illustrated in Figure 1. The actual CAGR (compound annual growth rate) from 2010 until 2019 was 15.2 % in units and 16.9 % in sales, while the forecasted CAGR from 2019 until 2024F is 11.5 % in units and 7.2 % in sales. Existing DRAM fabrication facilities are being converted into CIS (CMOS image sensor)

manufacturing plants to cope with the increasing demand for CMOS image sensors [Business Korea 20]. Despite a small 4 % drop in revenue and nearly flat unit growth due to the disruptions caused by COVID-19 in 2020, in 2024F the CIS sector expects a record high of 26.1 B\$ and 11 Bunits/year [IC Insights 20]. A simple calculation shows that over the course of 2020 (6.3 Bunits, 18.2 B\$), globally 200 image sensors are being produced every second at an average price of 2.9 \$. Realizing this scale of production by the end of 2020 will require a total of 5.4 Mwafers (300 mm diameter), which is equivalent to a silicon area of 76 soccer fields.

This continuous growth is in the first place fueled by the mobile phone industry and automotive markets. As both mobile phones and cars now use multiple cameras, it is expected that those numbers will continue to grow in the near future. More cameras are not only needed to take better pictures, but over time more functionality will be required from the image sensors, such as depth measurement (or 3D sensing) and the collecting of bio-medical data. Other applications, besides mobile phones and automotive applications, with high projected growth rates in the coming 5 years are: medical/scientific systems, security, industrial (including robots and IoT), and toys and games (including VR and AR). The higher-end digital still market is expected to shrink, because of the high quality images delivered today by mobile phones.

This paper will describe the landscape of solid-state imaging, from its start in the '60s of the previous century until 2020, as well as an outlook of what can be expected in the coming years. The paper is organized as follows:

- History: an overview will be given of the major developments in the CCD and the CMOS era.

- CMOS scaling: CMOS technology in general (still) follows Moore's Law, but is this also the case for CMOS image sensor technology? Will the pixels further scale down to dimensions below the wavelength of the incoming light?

- Image processing: the fact that perfect images can be captures by means of non-perfect image sensors is greatly due to the widely and cheaply available processing power of image signal processors (ISPs).

- Human Eye: how close do the imagers match the quality of the human eye, and is there still anything to learn from the human visual system?

- Masterpieces of 3D integration: many of the high quality characteristics and features offered by today's image sensors are the result of the successful 3D semiconductor processes available in the fabrication of CMOS image sensors.

- Future outlook: new materials and new concepts all pave the way for new applications.

- What about privacy and security?: cameras will be ubiquitous. Big Brother could be watching you, anytime, anywhere!

## **History**

The development of solid-state imaging started in the '60s of the previous century. Many important inventions, which still form the basis of today's devices, were already discovered at that time: the integrating photodiode by Gene Weckler [Weckler 67], the first photodiode array and the concept of the active pixel sensor by Peter Noble [Noble 68], the bucket-brigade device by Freek Sangster and Kees Teer [Sangster 69], the charge-coupled devices by Willard Boyle and George Smith [Boyle 70], the floating diffusion amplifier by Walter Kosonocky [Kosonocky 71], the CCD imager by Michael Tompsett [Tompsett 71], and later in the early '70s the correlated double sampling technique by Marvin White [White 74]. It is amazing how much of the today's technology rests on the shoulders of all these (and many more) giants. Despite these numerous advances, the CCD manufacturing technology did not evolve enough in the '70s to facilitate the building of devices with a sufficiently high yield at a reasonable cost. It took more than 10 years for a reproducible and reliable CCD manufacturing process to be developed. It was only in the mid '80s that the first camcorders based on solid-state image sensors were made available to the consumer market. The superior performance of the CCDs of that period was based on the low dark-current and low lag characteristics of the pinned photodiode [Teranishi 82] in combination with the introduction of base-resin micro lenses [Ishihara 83]. Despite the high image quality delivered by CCDs, they could only be fabricated in a dedicated MOS process [Theuwissen 95]. In connection to the CCD image sensor, every camera needed a significant amount of peripheral circuitry around the CCD. All in all, these characteristics made every CCD imaging system quite expensive, voluminous and power-hungry [Fossum 93].

In the early '90s the first papers about solid-state imaging devices fabricated in a standard CMOS process were published [Renshaw 90]. Image quality was rather poor in those passive-pixel devices, but the promise that they could be fabricated in a low cost, standard CMOS process, with all the peripheral circuitry integrated on-chip [Chen 90], gave a boost to the CMOS developments.

With the incorporation of several CCD techniques into the CMOS active-pixel approach, such as correlated double sampling and intra-pixel charge transfer with new fixed pattern noise removal circuits [Fossum 95], as well as the low-voltage pinned photodiode [Guidash 95], the performance level of the CMOS image sensor was brought to the level of CCDs, but with a lower cost and lower power budget compared to CCDs. It was shown again that "Everything that can be made in CMOS, will ultimately be made in CMOS".

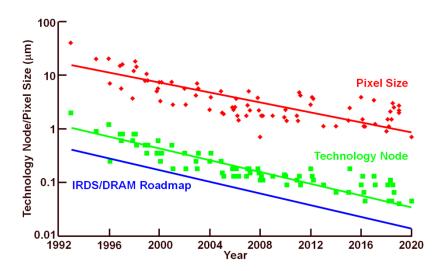

CMOS image sensors for classical image capturing applications became commercially available in the '90s of the previous century. Since that time an enormous evolution has taken place in the improvement of the manufacturing technology of the devices, driven by the goal to increase performance and decrease cost. Part of this evolution is shown in Figure 2: two parameters of published CIS studies (data taken from ISSCC, IEDM and IISW papers) are depicted as a function of time; the pixel size of the CIS is illustrated together with the technology node used to fabricate these pixels. The lower graph shows the IRDS (International Roadmap for Devices and Systems), which corresponds to the most advanced CMOS technology available in the industry [IRDS 20]. In most cases this technology is used to fabricate DRAMs. From Figure 2 a couple of interesting lessons can be learned:

- Over the years, the CIS pixel size has decreased at about the same pace as the technology node. In the vertical direction, the "distance" between the lines is equal to a factor of 20. It is remarkable that this factor of 20 already existed in the early days of CMOS image sensors [Fossum 93]. Despite the fact that over the last 30 years the pixel architecture has changed drastically, the ratio between the pixel size and technology node has almost remained constant. In other words, the CIS technology available to commercially fabricate the image sensors is driving the pixel size. The resolution of the image sensor, which plays a very important role in marketing together with the pixel size, determines to a large extent the CIS chip size and optics form-factor. It can be easily understood that a smaller pixel size has a direct impact on the cost of the CIS. Therefore this price factor is one of the most important driving forces to push for smaller pixels.

- Around 2015 there was hesitation to further shrink of the pixels; a pixel size of 1 µm seemed to be the limit. On the one hand, the technology to fabricate smaller pixels was available, but on the other hand, the performance of the devices with smaller pixels could not achieve an acceptable level (because of the small number of electrons that can be stored in, and low light sensitivity of, pixels of that small size). Recently, efforts to further shrink the pixels have resumed at about the same pace as before. Such a re-start was made possible by the integration in the third dimension (see below).

- By comparing the available CIS technology node with the IRDS, it seems that the CIS technology is following the IRDS but with a delay (in the horizontal direction) of about one decade. This is because a "standard" DRAM technology is not suitable for manufacturing a CIS with an acceptable performance. Issues that need to be solved to adopt a DRAM technology in a CIS technology (to name a few) are:

- Leakage current: a CIS collects every single free electron present in the silicon, even if this electron is generated by leakage or dark current.

The latter can be optimized by lowering the electrical and mechanical stress in the pixels through dedicated processing steps. Leakage currents play a vital role when it comes down to low-light level

- applications, or when the image sensor is operated at higher temperatures,

- Depth of the junctions: image sensors can increase their light sensitivity if photon-generated electrons generated deeper in the silicon can be collected. To do so, deeper junctions are essential,

- Photodiodes: the pinned photodiode used in a CIS needs several extra implants to achieve a complete charge transfer,

- Salicides/silicides: these metallization forms need to be avoided on top of the (photo-)diodes, because they will block the incoming light,

- Threshold voltages: CIS pixels are analog circuit blocks which can benefit from native MOS-transistors to keep the possible voltage swing as large as possible. A large analog output swing enhances the signalto-noise ratio and dynamic range of the image sensors,

- Color filters and micro-lenses: these materials are not available in any "standard" CMOS process.

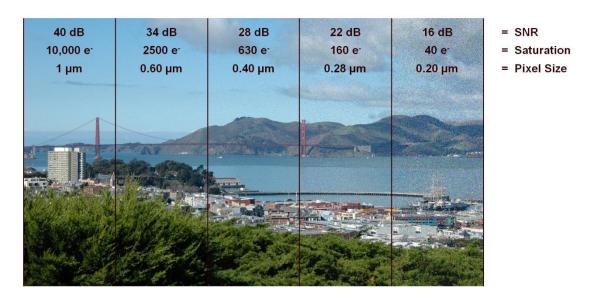

With today's technology node of DRAMs, measuring 10 nm and even smaller, a pixel as small as  $0.20~\mu m \times 0.20~\mu m$  could be fabricated, but unfortunately such a device can only store the bare minimum of electrons. For decent consumer-type images a minimum signal-to-noise ratio of 40 dB is needed. For a photon shot noise limited imager, this translates into a pixel saturation level of 10,000 electrons. To store such a charge packet, a minimum pixel size of around  $0.8~\mu m \times 0.8~\mu m$  is required. The effect of a shrinking maximum charge packet in a pixel is shown in Figure 3. From left to right, the signal-to-noise (SNR) is reduced, starting from 40 dB to 16 dB (as indicated in the figure). The corresponding number of electrons needed to obtain the mentioned SNR as well as the pixel size to store these electrons is indicated as well. As can be seen from left to right, the quality of the image ranges from (almost) perfect to unacceptable. (This is a simulation of a photon shot noise limited case; read noise and cross-talk are not taken into account. Read noise improves with scaling, whereas cross-talk becomes worse with scaling.)

An exception to the aforementioned argument of 40 dB can be the Quanta Image Sensor (QIS) [Fossum 05]. In its simplest form, this device is a kind of binary coded imager: "0" = no photons and "1" = a minimum of 1 photon. Then a few hundred QIS pixels and/or frames finally compose a signal comparable to a single classical CIS pixel.

Building on the advances in semiconductor technologies need not always result in a trend towards smaller dimensions; the opposite can also be true. For instance, wafer scale (300 mm Si wafers) image sensors of 20 cm x 20 cm manufactured in a 65 nm process have been reported [Lee 20], fabricated by making use of clever stitching technologies during the fabrication of the wafers [Theuwissen 98].

## **Masterpieces of 3D Integration**

In the early days of CMOS image sensors, the imagers were fabricated in a "standard" CMOS process with a few extra "imaging" options. However, it soon turned out that high image quality could only be realized with a dedicated CIS fabrication process that is still compatible with CMOS in general. In the race for the ever-shrinking pixel size, the third dimension of the silicon substrate became more and more important. Today CMOS image sensors are masterpieces of 3D integration. Especially the combination of a back-side illuminated imager stacked on the imager signal processor has resulted in a compact, cheap and high-performance imaging system. Methods such as stacking a CCD on a logic chip [Fossum 84] and stacking a CIS on a logic chip [Kioi 90] were already introduced a long time ago. As with many new ideas, however, the realization of these concepts could only be made possible after an immense surge in the development of the technology, in this case hybrid bonding at the pixel level.

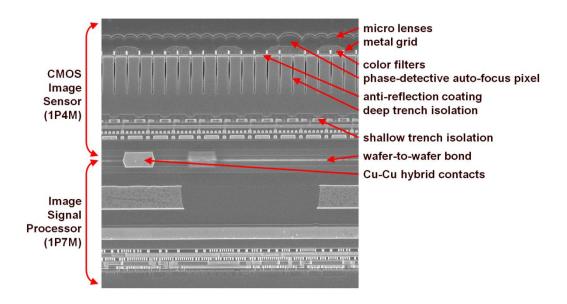

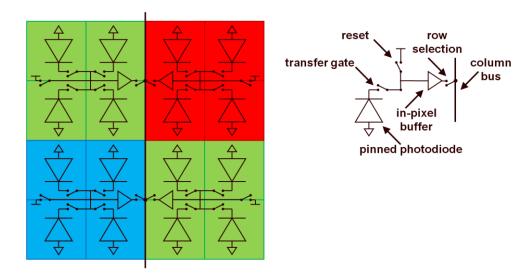

The cross-section shown in Figure 4 (courtesy of TechInsights, reverse engineered Sony IMX586 with 0.8 µm pixel size) represents a Quad Bayer-based CIS. The architecture of such a pixel is shown in Figure 5:

- a basic block contains 4 x 4 pixels,

- every 2 x 2 matrix of pixels is provided with the same color filter and has a common source-follower output stage,

- the latter is connected to a joint column bus.

In Figure 4, from top to bottom (following the photon path) for this back-side illuminated stacked die, what can be recognized is the following:

- The micro-lenses which bring the photons in the middle of the pixel to limit the optical and electrical cross-talk (the micro-lenses are not perfectly centered above the pixels, but they are shifted slightly to the center of the device to compensate for optical artifacts [Agranov 03]),

- The color filters which split the information into the various color planes, mostly red, green and blue. The color filters are deposited between tiny small tungsten walls, allowing the sidewall of the filters to be almost perfect, moreover the tungsten walls also act as waveguides [Watanabe 11]. Notice that the color filters cover two pixels each time. This is the typical filter architecture for the so-called Quad Bayer pattern configuration [Okawa 19],

- Although the color filters and the micro-lenses are expected to have a repetitive structure across the total imaging array, in Figure 4 it can be observed that this is not always the case. In one situation, two pixels, instead of a single one, are covered with a single micro-lens. This architecture is used to create a phase detective auto-focus (PDAF) pixel. This is a pixel with a special feature to indicate whether the image projected on the sensor is in focus or out of focus [Kobayashi 15],

- Below the color filters, dedicated anti-reflective coatings are incorporated to ensure that the maximum number of photons can reach the silicon,

- Inside the silicon, the (volume of the) pixels are defined by deep trench isolations (DTIs), etched from the backside. These trenches can be very deep and very narrow, the side walls of the trenches can be oxidized, and the remaining gaps can be refilled with poly-crystalline silicon or tungsten. The deep trenches have a positive effect on the optical as well as electrical crosstalk [De Munck 06],

- Although not shown, in the "bulk" of the silicon and between the trenches is where the pinned photodiodes are located. This back-side illuminated device was originally fabricated on a thick silicon substrate. The latter is thinned down to about 3 µm to allow back-side illumination,

- At the original front side, the MOS transistors are formed, being separated from each other by means of shallow trench isolations (STIs). From Figure 4 it can be concluded that the repetitive structure of the STI also corresponds to two pixels, which again illustrates the concept of the Quad Bayer design, in which 2 x 2 pixels share the source-follower-based readout structure [Okawa 19],

- The original front side of the image sensor is provided with four layers of interconnect,

- The back-side illuminated image sensor is hybrid-bonded to the processing part by means of a direct Cu-Cu bond pad interconnect. The hybrid bond pads in the active array have no electrical function; only in the periphery of the imager are the Cu-Cu hybrid bond pads used as electrical interconnects [Fontaine 20],

- The digital processing unit below the imager is provided with seven metal layers as the interconnect.

It should be clear that CMOS image sensors combine a complex fabrication technology with know-how in the fields of optics, device physics and electronic design. If pixels continue to reduce in size in the future, integrating them in the third dimension will play an even larger role. For instance, the photodiode will be no longer present along the front side of the silicon, but will be buried into the depth of the silicon as well. To transfer the electrons out of this photodiode, the transfer gate of the pixel will also need to be built vertically into the silicon [Ahn 14].

### **Image Processing**

One should realize that the light sensitivity of a pixel is proportional to the area of the in-pixel photodiode. For a long time, pixels of 5.6  $\mu$ m x 5.6  $\mu$ m were considered the de facto standard, but these days image sensors with a pixel size of 0.7  $\mu$ m x 0.7  $\mu$ m

are already commercially available [Kim 20]. This means that the latter catches only 1.5 % of the photons in comparison with the former pixel.

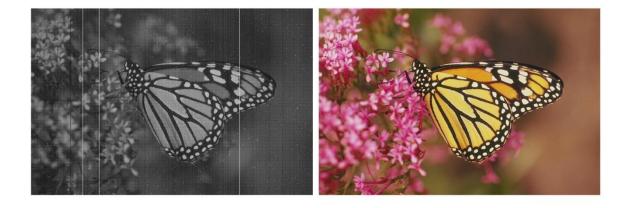

Despite capturing only 1.5 % of the photons, today's imagers deliver a better image quality than was the case a decade ago. This is thanks to progress made over the years in the digital processing of raw data delivered by the sensor. An example of how poor-quality raw image sensor data can result in a decent image is shown in Figure 6: on the left, the raw output signal of an imager with a Bayer CFA pattern is shown with many artefacts such as column defects, pixel defects, temporal noise, spatial noise, lens vignetting, color filter imperfections, and leakage current; on the right, the result is shown after the dedicated digital processing of the data.

Algorithms used to turn the left image into the right one are [Theuwissen 04]:

- Correction of defects or deviating pixels (of all pixels present in an imaging array 0.1 % can be defect; pixels deliver an analog value and their non-uniformity from pixel to pixel can be 1 %),

- Demosaicing (every pixel in a color image sensor is made sensitive to only a single color, but on the display, every pixel requires an RGB value),

- Color correction (as the CFA is not perfect, neither is the color signal delivered by the sensor),

- Correction of fixed-pattern noise (pixel circuitry and column circuitry are analog in nature, so there will be differences between these circuits showing up as a fixed, spatial noise component),

- Sophisticated filtering (of multiple images) to decrease the temporal noise (Johnson noise, 1/f noise, electrical cross-talk, kTC noise, quantization error, RTS noise, etc.),

- Rolling shutter distortion correction,

- etc

All these sophisticated algorithms present in RISC processors are currently being challenged by architectures based on artificial intelligence (AI) and deep learning (DL) neural networks (NN). The first notably promising results of NN in combination with image sensors being published, report demosaicing based on deep machine learning, which makes the final image quality independent of the CFA (color filter architecture) on top of the CIS pixels [Stojkovic 19]. As a consequence the CFA can be optimized for other image quality parameters than simply color fidelity.

Even a perfectly performing image sensor in a real camera cannot comply with all requirements a photographer demands from the camera when capturing a single image. For that reason modern smart phones start taking photos as soon as the user activates the camera function [Zubarev 19]. In fact, when the user taps the "red" button to take a photo, the photo has already been taken and the camera simply selects one of the last pictures stored in the memory. Or in a more sophisticated way, the final photo presented to the user is a combination of several pictures stored in the memory of the camera. In this case not only can a zero shutter lag be created,

but based on the stack of images present in the memory, several optimizations can be realized: errors or shortcomings in one picture are minimized by using the content of other pictures. Examples of this processing method are:

- High dynamic range (combining (sub-)images with different exposure times and/or different gain settings),

- Noise reduction (bilateral filtering of several images),

- Auto-focusing (taking images at different focus settings and choosing the best suited one),

- Super-resolution (using a sensor shift between the shooting of several images),

- Image stabilization (calculating a motion vector from multiple images and using this to correct motion artefacts in the final image),

- etc.

The modern stacking technology with multiple layers (imager, DRAM, logic processor) [Tsugawa 17] makes it possible to combine aforementioned technologies into sophisticated digital processing of multiple images stored in the memory. As can be expected, the digital processing core can and will be partly replaced by Al and/or NN circuitry [PR Newswire 20]. In this way two basic goals can be targeted by means of on-the-fly and embedded artificial intelligence close to the image sensor:

- Improving the functionality and quality of the imaging system, e.g. high dynamic range [Martel 20].

- Embedding analytics (e.g. for security applications) to recognize specific objects, including humans and face recognition.

## **Human Eye**

If a comparison is made between the human visual system and a digital camera, it is remarkable that in some aspects the human eye is (still) far superior to the image sensor (e.g. power dissipation, color fidelity, etc.). However, in other aspects an image sensor easily can beat the human eye (resolution, speed, temperature range, extended wavelengths, etc.) [Dierickx 97]. A significant advantage of the human eye is the ability to process images locally at the level of the retina level ("edge processing"), with combining high resolution in the center and low resolution outside the field of view. In this way minimal information needs to be transported to the brain for further processing, and the transporting is done through a limited number of nerves. Nonetheless, it is still not understood how the human visual system can make those beautiful images all of us can observe through only a single low-performance eye-lens and the limited data transport to the brain based on a sparse, asynchronous stream of digital spike events [Rodieck 18]. Here is where the digital

image sensor still can learn from the human visual system. Until recently, hardly any attention was paid to processing at the sensor level. These days, the first attempts to substantially reduce the output data of an imager have been reported, such as imagers that are put to sleep and only wake up if an event takes place in the scenery [Choi 15], or event-based devices [Finateu 20]. Further incorporation of edge processing at the sensor level will drastically reduce the data traffic off the sensor die. Also in this case, full exploitation of the stacking technology can play an important role in placing AI or NN processing units close to the pixels. Stacking "extends" the volume of the pixels into the third dimension, the extra volume of which can be used to implement more analog and digital circuitry. Embedding edge processing in combination with keeping track of the data and pixel statistics will allow captured images to be processed based on the "experience" of the sensor/camera.

#### **Future Outlook**

In the past the main driver of the solid-state imaging technology was the mobile phone industry. Will this still be the case in the future? Most probably in the short term it will, because smart phones are already being equipped with multiple cameras, one or two on the front side, three or four on the back side. Moreover the consumer trend seems to be the frequent purchasing of increasingly more expensive mobile phones with more camera options and features. It is clear that the camera performance of a mobile phone has become a major selection criterion in the purchase of a specific mobile phone.

Another major solid-state imaging trend is the broadening of the applications for silicon-based cameras, not only for shooting nice pictures, but also for using the image sensor for other purposes. Examples are:

- Extension of the spectrum of the sensors. Important developments have been announced with increased near-IR sensor sensitivity through extra trenches [EE Times 17] or application of pyramidal surface structures [Yokogawa 17]. This will expand the use of silicon detectors to the near-IR field. Applications are: eye trackers, gesture control, food sorting, and distance measurements by means of time-of-flight sensors [Seitz 11],

- Image sensors that can detect the polarization of the light. This characteristic allows a camera to detect the nature of the material (e.g. plastics, metals, etc.), to locate stress in materials, to avoid reflections when looking through glass surfaces, etc. [Gruev 08],

- Determining the energy of an arriving photon. This application will open many doors in the medical world. In X-ray imaging, knowledge of the energy of the incoming photon could reveal more information about possible diseases and could help the medical world to perform better and earlier diagnoses of cancer,

- Detection of the arrival time of incoming photons. This cannot be done with a consumer solid-state sensor, but by means of a Single Photon Avalanche Photodiode (SPAD). In the early days of the SPAD, the resolution was very limited as was the fill factor and photon detection probability. However, advances in the technology in combination with stacking, has led to devices with high resolution and with a high fill factor [Lee 18].

It must also be mentioned that a great amount of research is taking place in the field of non-silicon-based photo converters. For instance, different materials (Perovskites [Hossain 20], organic photo converters [Nishimura], quantum dots [Georgitzikis 19], etc.) are being used in combination with silicon readout integrated circuitry (ROIC). Silicon-based detectors do respond to incoming light up to a wavelength of 1.1 µm. Beyond this wavelength, silicon becomes transparent for incoming photons. However, silicon (CMOS) technology has developed to such a level that it will become extremely difficult to find other materials and technologies that perform better in the (extended) visible spectrum than silicon imagers. The combination of backside illuminated pinned photodiodes and correlated-double sampling results in devices that approach perfection as far as noise and quantum efficiency are concerned [Wang 07] [Ge 17]. However, if the detection of wavelengths outside the "silicon" spectrum is required, these new materials in combination with a Si-CMOSbased ROIC are certainly valuable options. Recently an image sensor in which InGaAs is used as the photon-to-electron converter has been applied on top of a hybrid bonded silicon readout IC [Manda 19].

Certainly one of the most promising new developments in the field of solid-state imaging is the combination of an image sensor stacked on an artificial intelligence processing chip. This new "marriage" is opening up a multitude of new applications and new horizons, including the field of biometric optical sensors. The stacking of a CIS on top of an FPGA was the very first attempt to realize the combination imaging with a programmable processor [Hseih 17]. Since then, the first announcement from academia [Mennet 20] has been made, and even the first product [Sony 20] has been introduced with a stacked CIS - neural network combination. The pixels of the image sensor can be seen as the very first layer of the neural network. The latter can be programmed and trained to comply with various customized requirements. In this way more focus will be placed on edge processing, and embedded imaging solutions will become faster and much smarter. In the recent past, most progress in the field of artificial intelligence is made in the combination of imaging with AI.

#### **Privacy and Security**

Following the evolution of the "Internet of Things" (IoT) concept: it all started with very simple RFID tags (inventory goods and loss prevention), followed by the addition of

more applications (surveillance, security, healthcare, food safety, document management), reaching the point of tracking people's location and object recognition. The next step will be the remote monitoring and controlling of objects. However, for all this "luxury" a substantial privacy price must be paid: Big Brother could be watching us, more closely than ever expected! In the near future, cameras connected wirelessly will be located anywhere and functioning at all times. Examples are: smart doorbell, smart refrigerator, smart traffic lights, smart energy meter, smart banking, smart car, smart office, smart home, smart baggage scanner, smart billboards, smart grocery store, smart toilet, smart ... For all these applications the same rule is valid: Big Brother can "steal" a lot of data to invade in our privacy at any time! In many cases the line between security and privacy is paper thin.

New developments in technology invariably introduce new social issues. In many of the aforementioned examples, images are being collected while it is actually not necessary to have/use full resolution images for that specific application. For instance if a camera is used to count people that are passing through an entrance, then the camera should be used for this specific purpose and not to recognize who is passing through that entrance. Counting people can be achieved without taking and storing images. The danger exists that once the images are taken and stored, they can be used for other purposes as well, even at a later time. Potential risk of data manipulation by means of AI is only a single step away. One should use the advantages of the technology without exploiting the dangers. This way of working is known as "responsible innovation" [van den Hoven 20], and the very first example is now on the market: a "people counter" by means of an event-based image sensor. This imager captures information in which one cannot recognize individuals [Samsung20]. The ISSCC community can play an important role in the R&D of "responsible innovation" technologies in the field of digital image sensors.

Everyone is concerned about losing his/her privacy, but in cases of urgency or danger, one is willing to sacrifice part of his/her privacy in return for a safe harbor. Examples of this concession can be found after great disasters like 9/11 or the corona pandemic. However, once the threat of the disasters has disappeared, the part of the privacy lost is not automatically regained. Governments rely on convincing arguments to take part of the privacy of their people, but are not so easily willing to give back what they have taken away.

## Conclusion

Solid-state imaging has travelled on a long and winding road from its early days in the '60s of the previous century to reach the technology level available today. This paper has strived to give a glimpse into the history, as well as a look at the future, of the solid-state image capturing technology.

"There's more to the picture than meets the eye": a consumer does not realize what happens in a digital camera when he/she taps the red button to take a picture. Although much can and will go wrong while shooting an image (noise, artefacts, limited dynamic range, etc.), thanks to clever and extended digital image processing, near-perfect images are being delivered by the cameras, even if the camera operates in a harsh environment.

"and in the future it will only become more so": the availability of a mature fabrication technology has played a crucial role in bringing solid-state imagers to consumer products. What is more, history is now repeating itself: the methods for stacking an imager on top of an AI/NN processing chip are maturing, opening up a completely new world of technologies and applications. The image sensors will no longer solely be used to shoot nice images, but it will also sense incoming light information. The AI/NN will process the generated data and can result in improved quality images or in object recognition.

A great future lies ahead of imaging engineers, but also an overwhelming responsibility is resting on their shoulders: to respect the privacy of the users of the imaging technologies that are developed by them!

# Acknowledgements

The author would like to express his sincere appreciation to:

- Edoardo, Kofi and Matteo for their help in preparing this paper,

- Eric, Nobu, Johannes, Guy and Vladimir for their reviewing assistance,

- Sarah for her "English" advice,

- All his (former) co-workers, all his (former) colleagues, all his (former) clients and all his (former) competitors for creating a stimulating and challenging environment to work in for 45 years,

- His family for their support throughout this great solid-state imaging journey.

#### References

<u>Agranov 03</u>: G. Agranov et al.: "Crosstalk and Microlens Study in a Color CMOS Image Sensor", IEEE Transactions on Electron Devices, Vol. 50, Jan. 2003, pp. 4-11.

<sup>\*</sup>The title of this talk "There's More to the Picture than Meets the Eye" is originating from a song of Neil Young "Hey Hey, My My" written in 1978.

Ahn 14: J.C. Ahn et al.: "A ¼-inch 8Mpixel CMOS Image Sensor with 3D Back-Side-Illuminated 1.12 µm Pixel with Front-Side Deep Trench Isolation and Vertical Transfer Gate", Digest of Technical Papers International Solid-State Circuits Conference, Feb. 9-13, 2014, pp. 124-125.

<u>Boyle 70</u>: W.S. Boyle and G.E. Smith: "Charge-Coupled Semiconductor Devices", Bell Systems Technical Journal, Vol. 49, 1970, pp. 587-593.

<u>Business Korea 20</u>: "Samsung Electronics to Expand Foundry Facilities for Image Sensors", <a href="http://www.businesskorea.co.kr/news/articleView.html?idxno=46495">http://www.businesskorea.co.kr/news/articleView.html?idxno=46495</a>, May 27, 2020.

<u>Chen 90</u>: K. Chen et al.: "PASIC: A Processor-A/D Converter-Sensor Integrated Circuit", International Symposium on Circuits and Systems, New Orleans (LA), May 1-3, 1990, pp. 1705-1708.

<u>Choi 15</u>: J. Choi et al.: "A 45.5μW 15fps Always-On CMOS Image Sensor for Mobile and Wearable Devices", Digest of Technical Papers International Solid-State Circuits Conference, Feb. 22-26, 2015, pp. 114-115.

<u>De Munck 06</u>: K. De Munck et al.: "High Performance Hybrid and Monolithic Backside Thinned CMOS Imagers Realized Using a New Integration Process", Technical Digest IEDM06, San Francisco (CA), Dec. 11-13, 2006.

<u>Dierickx 97</u>: B. Dierickx: "Comparison between the Human Eye and Silicon Detectors", IEEE Workshop on Charge-Coupled Devices and Advanced Image Sensors, Bruges (Belgium), June 5-7, 1997.

EE Times 17: "Nyxel by Omnivision", www.eetimes.com, Oct. 18, 2017 and Mar. 9, 2020

<u>Finateu 20</u>: T. Finateu et al. "A 1280x720 Back-Illuminated Stacked Temporal Contrast Event-Based Vision Sensor with 4.86 μm Pixels, 1.066GEPS Readout, Programmable Event-Rate Controller and Compressive Data-Formatting Pipeline", Digest of Technical Papers International Solid-State Circuits Conference, Feb. 16-20, 2020, pp. 112-113.

Fontaine 20: R. Fontaine: private e-mail communication, June 10, 2020.

<u>Fossum 84</u>: E.R. Fossum: "Charge-Coupled Analog Computer Elements and Their Application to Smart Image Sensors", PhD thesis Yale Univ., May 1984, p. 10.

<u>Fossum 93</u>: E.R. Fossum: "Active Pixel Sensors: Are CCD's Dinosaurs?", Proc. of the SPIE "Charge-Coupled Device and Solid-State Optical Sensors III, Vol. 1900, 1993, pp. 2-13.

<u>Fossum 95</u>: E.R. Fossum: "CMOS Image Sensors: Electronic Camera on a Chip", Technical Digest IEDM95, Washington (DC), Dec. 10-13, 1995, pp. 17-25.

<u>Fossum 05</u>: E.R. Fossum: "What To Do with Sub-Diffraction-Limit (SDL) Pixels? – A Proposal for a Gigapixel Digital Film Sensor (DFS)", International Image Sensor Workshop, Karuizawa, June 9-11, 2005, pp. 214-217.

<u>Ge 17</u>: X. Ge and A. Theuwissen: "A 0.5e<sup>-</sup> Temporal Noise CMOS Image Sensor with Charge-Domain CDS and Period-Controlled Variable Conversion Gain", 2017 International Image Sensor Workshop, Hiroshima (Japan), May 30 – June 2, 2017, pp. 290-293.

Georgitzikis 19: E. Georgitzikis et al.: "Organic- and QD-Based Image Sensors Integrated on 0.13μm CMOS ROIC for High Resolution Multispectral Infrared Imaging", International Image Sensor Workshop, Snowbird (UT), June 23-27, 2019, paper R43.

<u>Gruev 08</u>: V. Gruev et al.: "Image Sensor with Focal Plane Polarization Sensitivity", 2008 IEEE Intern. Symposium on Circuits and Systems, Seattle (WA), May 18-21, 2008, pp. 1028-1031.

- <u>Guidash 95</u>: M. Guidash et al.: "An Active Pixel Sensor Fabricated Using CMOS/CCD Process Technology", IEEE Workshop on Charge-Coupled Devices and Advanced Image Sensors, Dana Point (CA), Apr. 20-22, 1995, pp. 115-119.

- <u>Hseih 17</u>: B.-C. Hseih et al.: "A 3D Stacked Programmable Image Processing Engine in a 40nm Logic Process with a Detector Array in a 45nm CMOS Image Sensor Technology", International Image Sensor Workshop, Hiroshima (Japan), May 30 June 2, 2017, paper R2.

- <u>Hossain 20</u>: M.I. Hossain et al.: "Color Imaging Sensors with Perovskite Alloys", Presentation on Nano-, Bio-, Info-Tech Sensors and 3D Systems, SPIE Conference Proc. 11378, Apr. 27 May 1, 2020.

- <u>IC Insights 20</u>: "CMOS Image Sensors to Resume Record Run in 2021", <u>www.icinsights.coms/news/bulletins/CMOS-Image-Sensors-To-Resume-Record\_run-In-2021--/</u>, June 11, 2020.

- <u>Ishihara 83</u>: Y. Ishihara and K. Tanigaki: "A High Photosensitivity IL-CCD Image Sensor with Monolithic Resin Lens Array", Technical Digest IEDM83, Washington (DC), Dec. 5-7, 1983, pp. 497-500.

- <u>IRDS 20</u>: "International Roadmap for Devices and Systems, 2020 Edition, Executive Summary", Table ES2, p. 36, 2020, also available at <u>www.irds.ieee.org/editions/2020</u>.

- <u>Kim 20</u>: HC. Kim et al.: "A 1/2.65in 44Mpixel CMOS Image Sensor with 0.7 μm Pixels Fabricated in Advanced Full-Depth Deep-Trench Isolation Technology", Digest of Technical Papers International Solid-State Circuits Conference, Feb. 16-20, 2020, pp. 104-105.

- <u>Kioi 90</u>: K. Kioi et al.: "Monolithic Character Recognition System Implemented as Proto-Type Intelligent Image Sensor by 3D Integration Technology", Technical Digest IEDM90, San Francisco (CA), Dec. 11-14, 1990, pp. 66-69.

- <u>Kobayashi 15</u>: M. Kobayashi et al.: "A Low Noise and High Sensitivity Image Sensor with Imaging and Phase-Difference Detection AF in All Pixels", International Image Sensor Workshop, Vaals (Netherlands), June 8-11, 2015.

- <u>Kosonocky 71</u>: W.F. Kosonocky and J.E. Carnes: "Charge Coupled Digital Circuits", IEEE Journal Solid-State Circuits, Vol. SC-6, 1971, pp. 314-322.

- <u>Lee 18</u>: M.-J. Lee et al.: "High-Performance Back-Illuminated Three-Dimensional Stacked Single-Photon Avalanche Diode Implemented in 45-nm CMOS Technology", IEEE Journ. Quantum Electronics, Vol. 34, Nov. 2018.

- <u>Lee 20</u>: S. Lee et al.: "A 5.2Mpixel 88.4 dB 12inch CMOS X-Ray Detector with 16b Column-Parallel Continuous-Time  $\Sigma\Delta$  ADCs", Digest of Technical Papers International Solid-State Circuits Conference, Feb. 16-20, 2020, pp. 434-435,

- <u>Martel 20</u>: J.N.P. Martel et al.: "Neural Sensors: Learning Pixel Exposures for HDR Imaging and Video Compressive Sensing with Programmable Sensors", IEEE Transactions on Pattern Analysis and Machine Intelligence, Vol. 47, 2020, pp. 1642-1653.

- <u>Manda 19</u>: S. Manda et al.: "High-Definition Visible-SWIR InGaAs Image Sensor Using Cu-Cu Bonding of III-V to Silicon Wafer", Technical Digest IEDM19, San Francisco (CA), Dec. 7-11, 2019, pp. 16.7.1-16.7.4.

- Mennet 20 : L. Mennet et al. : "Ultrafast Machine Vision with 2D Material Neural Network Image Sensors", Nature, Vol. 579, Mar. 2020, pp. 62-67.

Nishimura 18: K. Nishimura et al.: "An 8K4K-Resolution 60fps 450ke- Saturation-Signal Organic-Photoconductive-Film Global-Shutter CMOS Image Sensor with In-Pixel Noise Canceller", Digest of Technical Papers International Solid-State Circuits Conference, Feb. 11-15, 2018, pp. 82-83,

Noble 68: P.J.E. Noble: "Self-Scanned Silicon Image Detector Arrays", IEEE Transactions on Electron Devices, Vol. 15, 1968, pp. 202-209.

Okawa 19: T. Okawa et al.: "A 1/2inch 48M All PDAF CMOS Image Sensor Using 0.8 μm Quad Bayer Coding 2x2OCL with 1.0lux Minimum AF Illuminance Level", Technical Digest IEDM19, San Francisco (CA), Dec. 9-11, 2019, pp. 16.3.1-16.3.4.

<u>PR Newswire</u>: "Sony to Release World's First Intelligent Vision Sensors with Al Processing Functionality", <a href="https://www.prnewswire.com/news-releases">www.prnewswire.com/news-releases</a>, May 14, 2020.

Renshaw 90 : D. Renshaw et al. : "ASIC VISION", Custom Integrated Circuits Conference, Boston, May 13-16, 1990, pp. 7.3.1-7.3.4.

Rodieck 18: R.W. Rodieck: The First Steps in Seeing, Oxford Univ. Press, ISBN 978-0-87893-757-8, 2018, pp. 20-36.

<u>Samsung 20</u>: "SmartThings Vision", <a href="https://www.samsung.com/au/smart-home/smartthings-vision-u999/">https://www.samsung.com/au/smart-home/smartthings-vision-u999/</a>, <a href="https://www.samsung.com/au/smart-home/smart-home/smartthings-vision-u999/">https://www.samsung.com/au/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/smart-home/s

<u>Sangster 69</u>: F. Sangster and K. Teer: "Bucket-Brigade Devices", IEEE Journal Solid-State Circuits, Vol. SC-4, 1969, pp. 131-136.

<u>Seitz 11</u>: P. Seitz: "Review of Optical 3D Ranging Techniques and Key Design Challenges for Required Image Sensors", in International Conference on Solid-State Circuits "Image Sensors for 3D Capture" Forum, San Francisco (CA), Feb. 20-24, 2011.

<u>Sony 20</u>: "Sony to Release World's First Intelligent Vision Sensors with AI Processing Functionality", www.sony.net/SonyInfo/News/Press/202005/20-037E/, June 15, 2020.

<u>Stojkovic 19</u>: A. Stojkovic et al.: "The Effect of Colour Filter Array Layout Choice on State-of-the-Art Demosaicing", Sensors, Vol. 19, No. 14, 2019, paper 3215, pp. 1-16.

<u>Teranishi 82</u>: N. Teranishi et al.: "No Image Lag Photodiode Structure in the Interline CCD Image Sensor", Technical Digest IEDM82, San Francisco (CA), Dec. 13-15, 1982, pp. 324-327,

<u>Theuwissen 98</u>: A. Theuwissen et al.: "Versatile Building-Block Architecture for Large Area, High Performance CCD Imagers", Proceedings of SPIE, Vol. 3301, pp. 37-43, San Jose (CA), Jan. 26-27, 1998.

<u>Theuwissen 95</u>: A. Theuwissen: <u>Solid-State Imaging with Charge-Coupled Devices</u>, Kluwer Academic Publishers, ISBN 0-795-33456-6, 1995, pp. 317-348.

<u>Theuwissen 04</u>: "Image Processing Chain in a Digital Still Camera", Invited talk at IEEE Symposium on VLSI Circuits, Honolulu (HI), June 17-19, 2004, pp. 2-5.

<u>Tompsett 71</u>: M.F. Tompsett et al.: "Charge-Coupled Imaging Devices: Experimental Results", IEEE Transactions Electron Devices, Vol. ED-18, 1971, pp. 992-996.

<u>Tsugawa 20</u>: H. Tsugawa et al.: "Pixel/DRAM/Logic 3-Layer Stacked Image Sensor Technology", Technical Digest IEDM17, San Francisco (CA), Dec. 2-6, 2011, pp. 3.2.1-3.2.4.

van den Hoven 20 : J. van den Hoven : private communication, June 22, 2020.

<u>Wang 07</u>: X. Wang et al.: "Characterization of Buried Channel n-MOST Source Followers in CMOS Image Sensors", 2007 International Image Sensor Workshop, June 7-10, 2007, Ogunquit (ME), pp. 223-225.

Watanabe 11: H. Watanabe: "A 1.4 μm Front-Side Illuminated Image Sensor with Novel Light Guiding Structure Consisting of Stacked Lightpipes", Technical Digest IEDM11, Washington (DC), Dec. 5-7, 2011, pp. 8.3.1-8.3.4.

<u>Weckler 67</u>: G. Weckler: "Operation of p-n Junction Photodetectors in a Photon Flux Integrating Mode", IEEE Journal Solid-State Circuits, Vol. SC-2, No. 3, 1967, pp. 65-70.

White 74: M. White et al.: "Characterization of Surface Channel CCD Image Arrays at Low Light Levels", IEEE Journal Solid-State Circuits, Vol. SC-9, No. 1, 1974, pp. 1-13.

<u>Yokogawa 17</u>: S. Yokogawa: "IR Sensitivity Enhancement of CMOS Image Senor with Diffractive Light Trapping Pixels", Nature Sci. Rep., Vol. 7-3832, 2017, pp. 1-7.

<u>Zubarev 19</u>: V. Zubarev: "Computational Photography", <u>www.vas3k.com/blog/computational photography/</u>, June 30, 2019.

Figure 1. Overview of the world-wide CMOS image sensor market (source: IC Insights).

Figure 2.Evolution of the pixel size, fabrication technology node and the International Roadmap for Devices and Systems (source: ISSCC, IEDM, IISW).

Figure 3. Visualization of the effect of shrinking pixel size and of maximum charge packet on the image quality.

Figure 4. Cross-section of a Quad-Bayer based CIS, stacked on a logic chip by means of Cu-Cu hybrid bonding (source TechInsights).

Figure 5. Architecture of a Quad-Bayer based CIS pixel (left 4 times 2x2 pixel configuration, right detailed circuit of a single photodiode + readout circuitry).

Figure 6. Raw data delivered by the sensor (left) and the final image after dedicated image processing (right).