Inve ) SCE

by

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Thursday July 7, 2022 at 10:00 AM.

Student number: Project duration: Thesis committee: 4445120 November 8, 2021 - July 7, 2022 Prof. Dr. Z. Al-Ars, Prof. Dr. M. A. Zuñiga Zamalloa, TU Delft Ir. J. Petri-König, AMD Ir. G. Gunay, ALTEN

TU Delft, supervisor

An electronic version of this thesis is available at http://repository.tudelft.nl/.

# Preface

During my studies, my interests shifted from high-level software engineering to embedded systems. This eventually led me to fulfill my thesis with the Accelerated Big Data Systems (ABS) group of the Computer Engineering (CE) department. I stepped out of my comfort zone by taking on a hardwareoriented project. Exploring the complexities of hardware design sometimes left me clueless, but in the end proved to be a very rewarding journey. Fortunately, I was not facing the endeavors of this project alone. I would like to thank my parents, girlfriend, brother, sister, and friends who have supported my decisions and provided me with motivation and opportunities to decompress during these sometimes stressful times. Throughout this project, my supervisors provided me with unwavering support, mentoring, and motivation. For that, I express my sincere gratitude to Zaid Al-Ars, Jakoba Petri-König, and Gokhan Gunay. A special thank you is to Jakoba as she continued to supervise my work, respond to my countless messages, and provide me with excellent feedback even after leaving the TU Delft and starting a new job. Lastly, I would like to thank Joost Hoozemans and André Prins for their involvement in the choice of topic for this project and ALTEN for providing me with a place to work, fun colleagues and an introduction into the technical consulting industry.

> Luc Dierick Rotterdam, June 2022

# Abstract

In recent years, the big data era has produced an increasing volume and complexity of data that requires processing. To analyze and process these large amounts of data, applications are being scaled on large clusters using distributed data processing frameworks. A more recent trend utilizes hardware accelerators to offload computationally intensive tasks and reduce compute time and energy consumption. As a result, a rapid growth of data center deployment containing heterogeneous compute infrastructures is observed. Alternative to the more commonly used general-purpose GPUs (GPGPUS), the field programmable gate array (FPGA) is becoming an increasingly popular choice of accelerator. Its effectiveness to accelerate highly parallel applications in combination with the flexibility due to its reconfigurable nature make it well suited for a wide range of applications. As a spatial compute resource, the problem size a single FPGA can process is bounded by the available programmable logic and memory. However, applications that do not require the full resources of an FPGA can be vertically scaled by instantiating multiple instances of the hardware design on a single node. A barrier in the adoption of FPGAs is formed by the complexity of hardware design which requires in depth hardware-specific expertise. Additionally, integrating FPGAs in distributed data processing frameworks is a challenge on itself.

These challenges are being addressed in two directions. High level synthesis (HLS) tools and compilers are being developed to decrease the complexity of hardware design by allowing users to develop FPGA designs in high level languages. Additionally, there is an increased availability of ready-to-use FPGA designs for common applications in hardware libraries such as Vitis libraries [1].

To aid the adoption of FPGAs and improve their accessibility, this work presents OctoRay: a python framework with a focus on ease-of-use that allows users to flexibly and transparently scale applications both vertically and horizontally on FPGA clusters. Scaling a binarized convolutional neural network (CNN) with OctoRay resulted in performance improvements linear to the number of nodes, or copied instances applied. The framework was also used to analyze the cost-efficiency of a cluster of low-end PYNQ-Z1 FPGAs compared to a data center class Alveo U280 FPGA. A partly in hardware accelerated implementation of Full Waveform Inversion (FWI), a seismic imaging algorithm, was developed and used to conduct the investigation. It was concluded that 32 PYNQ-Z1s are required to match the performance of a single Alveo U280 FPGA. An important bottleneck in the performance of the PYNQ-Z1s was the low-performance host processor on which a significant portion of FWI was executed. The small number of resources available on a PYNQ-Z1 limited the attainable accuracy of FWI to a bare minimum. The FWI hardware design with the same specifications made for the high-end FPGA only utilized a fraction of its resources, far from harnessing its full potential. It was concluded that, unlike FWI, applications that do not require the abundance of resources a high-end FPGA offers, but do benefit from rapid development cycles and low energy consumption are suited for a distributed low-end FPGA composition.

# List of Acronyms

- **ADAS** Advanced Driver-Assistance Systems.

- ASIC Application Specific Integrated Circuit.

- **CLB** Configurable Logic Block.

- CPU Central Processing Unit.

- DAG Directed Acyclic Graph.

- DNN Deep Neural Network.

- FPGA Field Programmable Gate Array.

- FWI Full Waveform Inversion.

- GPU Graphics Processing Unit.

- **HDL** Hardware Description Language.

- HLS High Level Synthesis.

- IC Integrated Circuit.

- IP Intellectual Property.

- RTL Register Transfer Level.

- SoC System on Chip.

- VHDL Very high speed integrated circuit Hardware Description Language.

# List of Figures

| 2.1<br>2.2               | Simplified visualization of the components of an FPGA, figure altered from [15] FPGA design flow phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6<br>7           |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2.3<br>2.4<br>2.5        | Dependency graph of parallelism example application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9<br>10<br>11    |

| 3.1<br>3.2               | A high-level overview of the FWI algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14<br>n/s,<br>14 |

| 3.3<br>3.4               | A high-level overview of the FWI algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15<br>17         |

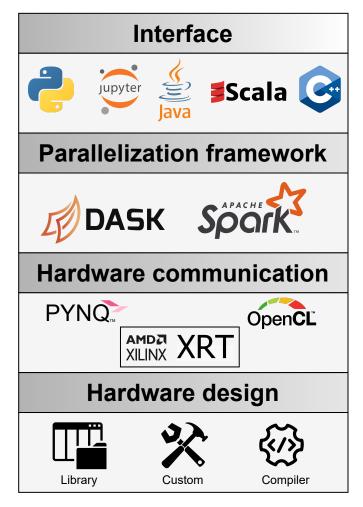

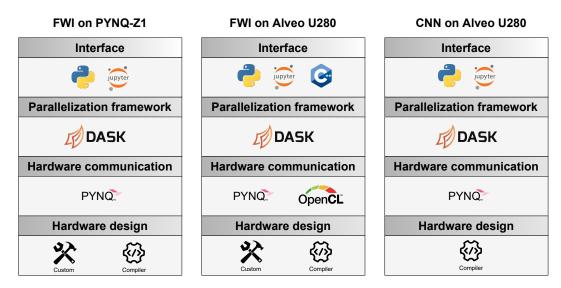

| 4.1<br>4.2<br>4.3<br>4.4 | A high-level representation of the stack necessary to scale applications on FPGAs<br>An overview of the Xilinx Runtime Library (XRT) adapted from [40]                                                                                                                                                                                                                                                                                                                                                                                                                       | 20<br>22<br>24   |

|                          | CNN on Alveo U280.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26               |

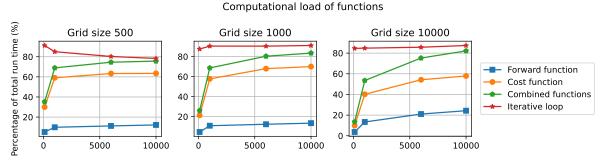

| 5.1                      | An overview of the percentage of run time occupied by the forward, cost, and com-<br>bined functions and the iterative loop for grid sizes 500, 1000, and 10000 and resolutions<br>(sources*receivers*frequencies), $100 = (5 * 5 * 4)$ , $1000 = (10 * 10 * 10)$ , $6000 = (15 * 15)$<br>and $10000 = (20 * 20 * 25)$ .                                                                                                                                                                                                                                                     | * 20)<br>28      |

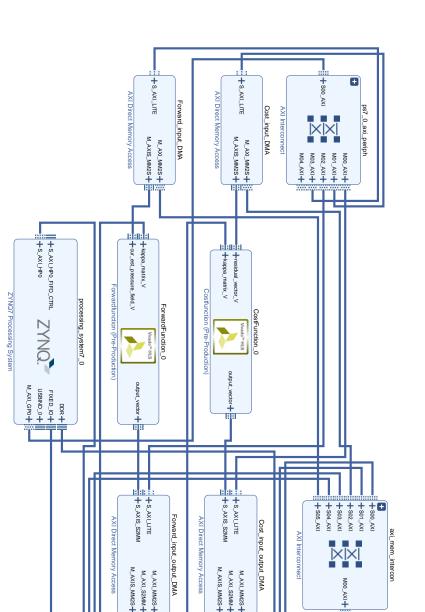

| 5.2<br>5.3               | The Zynq Processing System IP, taken from [44]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30               |

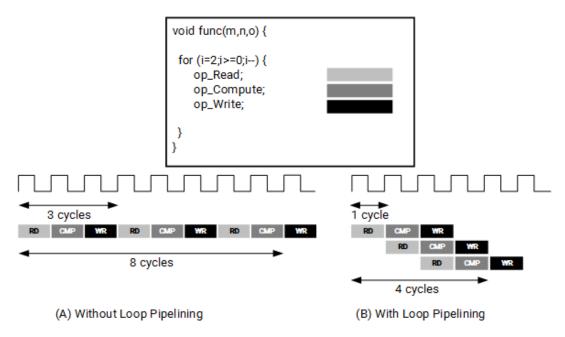

| 5.4<br>5.5               | taken from [46]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32<br>33<br>39   |

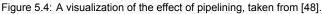

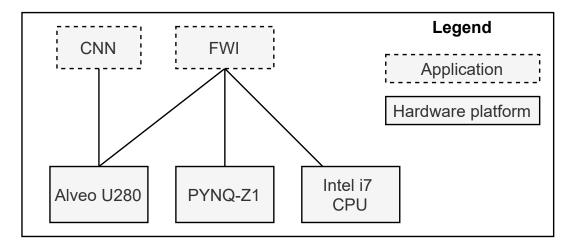

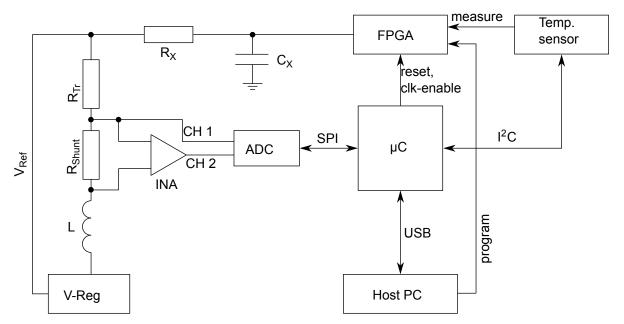

| 6.1<br>6.2               | Topology of hardware platforms and applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44               |

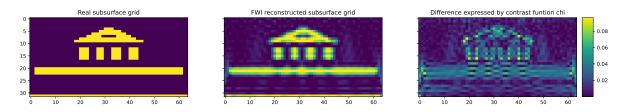

| 6.3                      | University of Kassel. The real subsurface grid of the Delphi temple (left), the reconstructed grid (center), and the difference between the real and reconstructed grid (right) are expressed in chi. The C++ FWI implementation was applied on the full data set of grid size $64 * 32 = 2048$ with                                                                                                                                                                                                                                                                         | 45               |

| 6.4                      | a resolution of sources, receivers, and frequencies $20 * 20 * 15 = 6000$ The real subsurface grid of the Delphi temple (left), the reconstructed grid (center), and the difference between the real and reconstructed grid (right) are expressed in chi. The C++ FWI implementation was applied on the full data set of grid size $64 * 32 = 2048$ with                                                                                                                                                                                                                     | 48               |

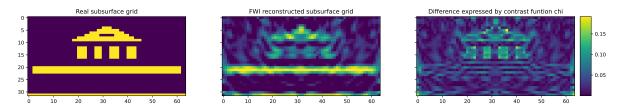

| 6.5                      | a resolution of sources, receivers, and frequencies $7 * 7 * 6 = 294$ . The real subsurface grid of the Delphi temple (left), the reconstructed grid of four independently inverted layers merged back together (center) and the difference between the real and reconstructed grid (right) is expressed in chi. The C++ FWI implementation was applied four times on $64 * 8 = 512$ grid size layers of the total data set. Each layer was inverted with a resolution of sources, receivers and frequencies $7 * 7 * 6 = 294$ and are sourced by white lines in the figure. | 48               |

|                          | separated by white lines in the figure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49               |

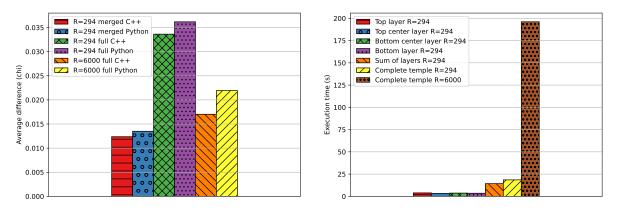

| 6.6  | The accuracy of the CPU implementations is expressed through the contrast function chi (left). The execution time of the C++ implementation for the independent and summed layers of the merged model with a resolution (R) of 294 and of the complete data set with resolutions R=294 and R=6000 (right).                                                                                                       | 49 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

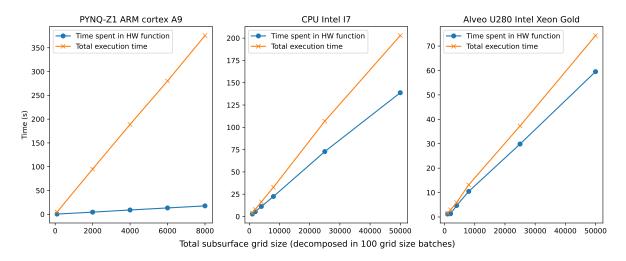

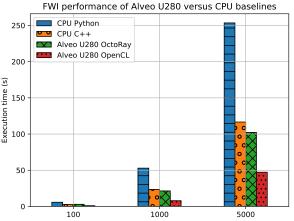

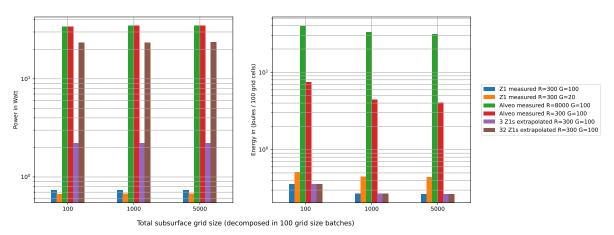

| 6.7  | An overview of the execution time spent in the hardware-accelerated functions for the PYNQ-Z1 and Alveo U280 FPGAs and CPU python implementations. The high utilization PYNQ-Z1 hardware design from Table 6.1 with resolution 294 was used. The python FWI implementation was used for both CPU and PYNQ-Z1. These results do not take initialization and downloading the bitstreams to the FPGAs into account. | 51 |

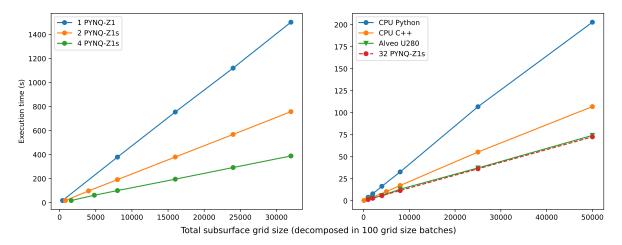

| 6.8  | The left plot shows the performance of FWI with a resolution of 300 and grid size 100 when scaled on 1, 2, and 4 PYNQ-Z1s. The right plot shows the performance of the same FWI configuration for the python and C++ CPU implementation, the Alveo U280,                                                                                                                                                         |    |

| 6.9  | and 32 PYNQ-Z1s                                                                                                                                                                                                                                                                                                                                                                                                  | 51 |

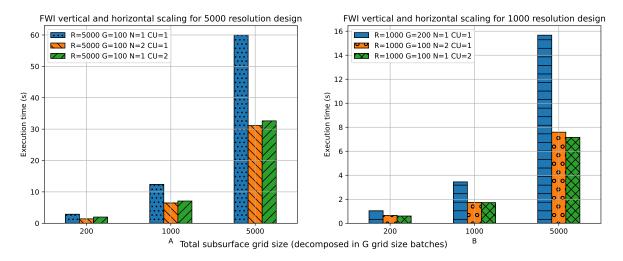

| 6.10 | compute unit or per node, and CU the number of compute units                                                                                                                                                                                                                                                                                                                                                     | 53 |

|      | with OpenCL and the latter in combination with OctoRay and subsequently pynq, on an Alveo U280 FPGA.                                                                                                                                                                                                                                                                                                             | 53 |

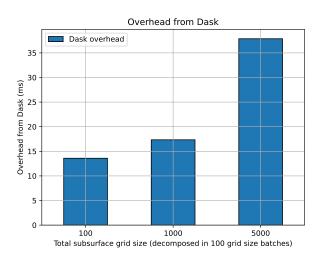

| 6.11 | The overhead in milliseconds induced by Dask for 100, 1000 and 5000 total subsurface grid sizes executed by an 8000 resolution 100 grid size FWI configuration.                                                                                                                                                                                                                                                  | 54 |

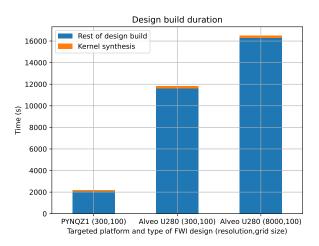

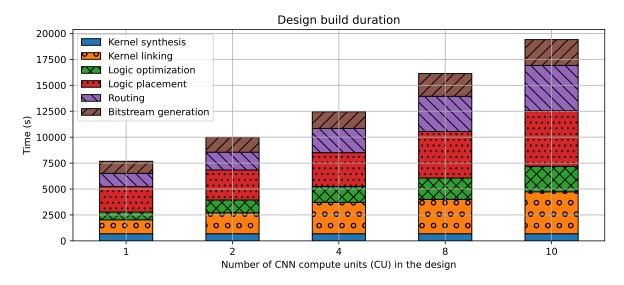

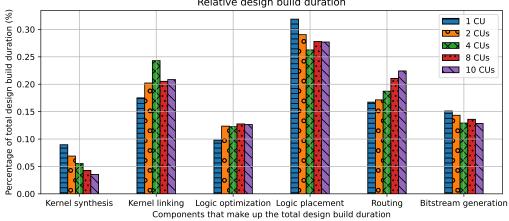

| 6.12 | The total design-build duration is divided into kernel synthesis and the remaining build duration for three hardware designs of FWI.                                                                                                                                                                                                                                                                             | 56 |

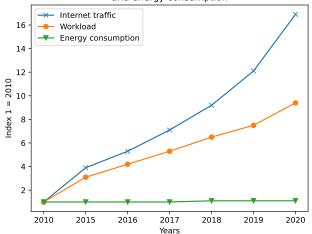

| 6.13 | The global trends in user internet traffic, data center workload, and energy consumption.                                                                                                                                                                                                                                                                                                                        |    |

| 6.14 | The numbers in this graph are relative to 2010. Data was taken from IEA [58] The power and energy consumption of the PYNQ-Z1, and Alveo U280 FPGAs. The power is measured for total grid sizes 100, 1000, and 5000, decomposed in batches of 100 grid cells. The energy is calculated by using the time spent in the accelerated part                                                                            | 57 |

| 6.15 | of the algorithm as the power is also only measured over that part                                                                                                                                                                                                                                                                                                                                               | 58 |

| 6.16 | 10.1.212.126 and the dask worker on alveo3c with IP 10.1.212.127                                                                                                                                                                                                                                                                                                                                                 | 59 |

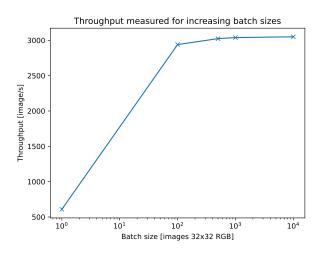

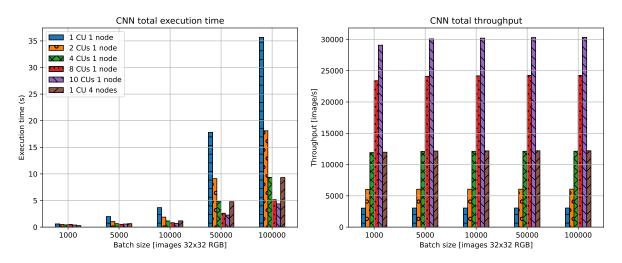

| 6.17 | and 100000 of 32x32 RGB images from the cifar-10 dataset                                                                                                                                                                                                                                                                                                                                                         | 59 |

|      | different components of the total design-build. The throughput in images per second of 1 dask worker executing the CNN application with a 1 instance hardware design for batch sizes 1, 100, 500, 1000 and 10000 of 32x32                                                                                                                                                                                        | 60 |

|      | RGB images.                                                                                                                                                                                                                                                                                                                                                                                                      | 61 |

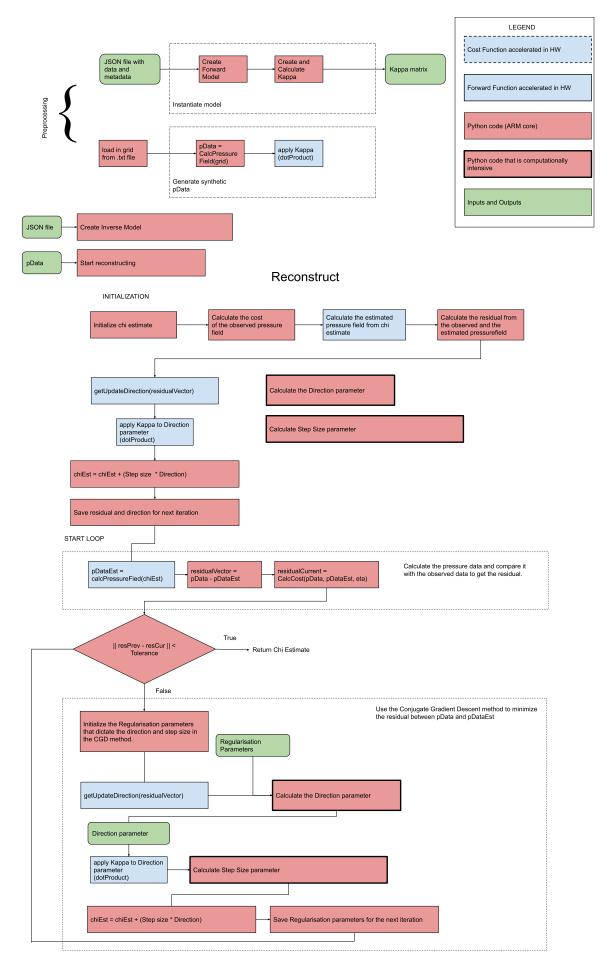

| A.1  | A diagram of the ALTEN provided implementation of FWI using the finite difference for-<br>ward model and a conjugate gradient descent inversion model.                                                                                                                                                                                                                                                           | 68 |

# Contents

| 1 | Intro    | oductio                                     | 1                                                                                              |  |

|---|----------|---------------------------------------------|------------------------------------------------------------------------------------------------|--|

|   | 1.1      | Conte                                       |                                                                                                |  |

|   | 1.2      | Challe                                      | ges                                                                                            |  |

|   |          | 1.2.1                                       | Accessibility                                                                                  |  |

|   |          | 1.2.2                                       | Cost-efficiency                                                                                |  |

|   | 1.3      | Proble                                      | n statement & research questions                                                               |  |

|   | 1.4      | Solutio                                     | and contributions                                                                              |  |

|   | 1.5      | Thesis                                      | outline                                                                                        |  |

| 2 | Bac      | kgroun                                      | 5                                                                                              |  |

| 2 | 2.1      |                                             | ogrammable gate arrays                                                                         |  |

|   | 2.1      | 2.1.1                                       | Design flow                                                                                    |  |

|   |          | 2.1.1                                       | SoC FPGAs                                                                                      |  |

|   |          | 2.1.2                                       |                                                                                                |  |

|   |          | 2.1.3                                       |                                                                                                |  |

|   | <u> </u> |                                             | <b>,</b>                                                                                       |  |

|   | 2.2      |                                             |                                                                                                |  |

|   |          | 2.2.1                                       | 5                                                                                              |  |

|   | <u> </u> |                                             | Vitis unified software platform                                                                |  |

|   | 2.3      |                                             | lity                                                                                           |  |

|   |          | 2.3.1                                       | Task parallelism.   9                                                                          |  |

|   | ~ 4      | 2.3.2                                       | Data parallelism                                                                               |  |

|   | 2.4      | Relate                                      | work                                                                                           |  |

| 3 | Арр      | lication                                    | domains 13                                                                                     |  |

|   | 3.1      | Full W                                      | veform Inversion                                                                               |  |

|   |          | 3.1.1                                       | Background & implementation                                                                    |  |

|   |          | 3.1.2                                       | Scalability characteristics                                                                    |  |

|   | 3.2      | Convo                                       | utional Neural Network                                                                         |  |

|   |          | 3.2.1                                       | Background & implementation                                                                    |  |

|   |          | 3.2.2                                       | Scalability characteristics                                                                    |  |

|   | A 14 a   |                                             | alutiona do                                                                                    |  |

| 4 |          |                                             | <b>19</b><br>Ire-design                                                                        |  |

|   | 4.1      |                                             |                                                                                                |  |

|   |          | 4.1.1                                       | Custom hardware design                                                                         |  |

|   |          | 4.1.2                                       | Hardware designs from libraries                                                                |  |

|   |          | 4.1.3                                       | Compiler-generated hardware designs                                                            |  |

|   |          | 4.1.4                                       | Evaluation                                                                                     |  |

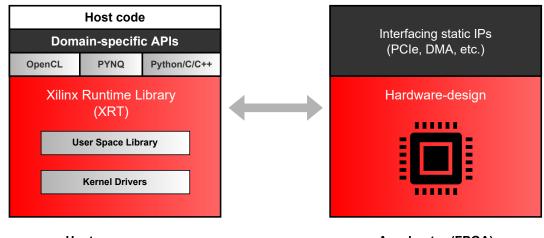

|   | 4.2      |                                             |                                                                                                |  |

|   |          | 4.2.1                                       | XRT                                                                                            |  |

|   |          | 4.2.2                                       | OpenCL                                                                                         |  |

|   |          | 4.2.3                                       | PYNQ                                                                                           |  |

|   |          | 4.2.4                                       | Evaluation                                                                                     |  |

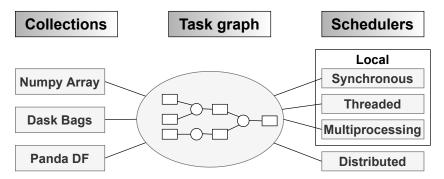

|   | 4.3      | Dorolla                                     |                                                                                                |  |

|   |          |                                             | ization framework                                                                              |  |

|   |          | 4.3.1                                       | Apache Spark                                                                                   |  |

|   |          | 4.3.1<br>4.3.2                              | Apache Spark                                                                                   |  |

|   |          | 4.3.1<br>4.3.2<br>4.3.3                     | Apache Spark.                                                                                  |  |

|   | 4.4      | 4.3.1<br>4.3.2<br>4.3.3<br>Interfa          | Apache Spark.       24         Dask.       24         Evaluation.       24         e.       25 |  |

|   |          | 4.3.1<br>4.3.2<br>4.3.3<br>Interfa<br>4.4.1 | Apache Spark.                                                                                  |  |

|   | 4.5  | Conclusion                               | 6 |

|---|------|------------------------------------------|---|

|   |      | 4.5.1 FWI on PYNQ-Z1                     |   |

|   |      | 4.5.2 FWI on Alveo U280                  |   |

|   |      | 4.5.3 CNN on Alveo U280                  | 6 |

| 5 | Solu | tion architectures and implementations 2 | 7 |

|   |      | FWI hardware design.                     | 7 |

|   |      | 5.1.1 Algorithm analysis                 | 7 |

|   |      | 5.1.2 Hardware kernels                   | 8 |

|   |      | 5.1.3 Design implementation              | 9 |

|   |      | 5.1.4 Design optimization                | 1 |

|   | 5.2  | Hardware communication                   | 4 |

|   |      | 5.2.1 PYNQ                               | 4 |

|   |      | 5.2.2 OpenCL                             | 6 |

|   |      | 5.2.3 Multiple compute units             |   |

|   | 5.3  | Interface                                |   |

|   | 5.4  | OctoRay                                  |   |

|   |      | 5.4.1 Deployment                         |   |

|   |      | 5.4.2 Flexibility and usability          |   |

|   |      | 5.4.3 Accessibility                      | 3 |

| 6 | Res  | llts 4                                   | 4 |

| - | 6.1  | Experimental setups for FWI              | 4 |

|   |      | 6.1.1 CPU                                |   |

|   |      | 6.1.2 PYNQ-Z1 OctoRay                    |   |

|   |      | 6.1.3 PYNQ-Z1 power measurement          |   |

|   |      | 6.1.4 Alveo U280                         |   |

|   | 6.2  | Experimental setup CNN                   | 7 |

|   | 6.3  | FWI results                              | 7 |

|   |      | 6.3.1 Domain decomposition               | 7 |

|   |      | 6.3.2 Scalability                        | 0 |

|   |      | 6.3.3 Performance                        | 3 |

|   |      | 6.3.4 Cost and utilization               |   |

|   |      | 6.3.5 Design-build duration              |   |

|   |      | 6.3.6 Power                              |   |

|   | 6.4  | CNN results                              |   |

|   |      | 6.4.1 Scalability                        |   |

|   |      | 6.4.2 Build design time                  | 0 |

| 7 | Con  | clusions and future work 6               | 2 |

|   | 7.1  | Conclusions                              | 2 |

|   |      | 7.1.1 Accessibility                      | 2 |

|   |      | 7.1.2 FWI acceleration                   | 3 |

|   |      | 7.1.3 Cost-efficient compositions        | 3 |

|   |      | 7.1.4 Scalability                        | 4 |

|   | 7.2  | Future work                              | 4 |

| Δ | Full | Waveform Inversion 6                     | 6 |

| ~ |      | Cost Function C++                        | - |

|   |      | Forward Function C++                     |   |

|   |      | Implementation diagram                   |   |

|   | A.J  |                                          | 0 |

# Introduction

#### 1.1. Context

With the growing deployment of data centers and heterogeneous compute infrastructures, the Field Programmable Gate Array (FPGA) is becoming a serious contributor to the Big Data processing paradigm. This has been emphasized in recent years as leading chip-makers Intel and AMD have, respectively, acquired FPGA vendors Altera and Xilinx. Cloud computing giants such as Amazon AWS, Microsoft Azure, and Google Cloud have adopted FPGAs into their infrastructures right next to silicon alternatives, CPUs, and GPUs. Microsoft, for example, exploits FPGAs for its low-latency performance in Deep Neural Network evaluations and even Bing's search ranking [2].

FPGAs have shown in the past that they are a promising alternative to further accelerate applications, especially highly parallelizable ones. For example, in research areas such as genomics, FPGAs are used to accelerate key algorithms that need to process increasingly larger data sets [3]. Also in distributed Big Data applications FPGAs have shown their worth, for instance, to accelerate compression and decompression algorithms that reduce data storage space and data transmission bandwidth [4]. Unfortunately, due to the high complexity of FPGA development, exploitation of FPGAs used to be reserved for the relatively small group of engineers with in-depth hardware knowledge. Companies such as AMD and Intel have been releasing software tools and frameworks to enable developers with little to no hardware knowledge to use FPGAs. Additionally, in the academic world efforts are being made to further integrate FPGAs into heterogeneous compute infrastructures. Hoozemans et al. provide an overview of the current opportunities, challenges, and their potential solutions for Big Data Analytics acceleration with FPGAs in [5].

Despite these initiatives, there is still a lot to be done to lower the entry barriers and improve accessibility. Compared to CPUs and GPUs, the FPGA ecosystem is still very much in its infancy. Frameworks such as InAccel [6], are proprietary and designed to support expensive data center-class FPGAs. It should be noted that historically, the electrical engineering (EE) community, contrary to the software (SW) community, has been averse to the concept of open-source work [7]. To aid combat this aversity and grow the FPGA ecosystem in a healthy way, there is a need for more open-source frameworks to help a broader public scale and accelerate applications on FPGAs.

In 2020 the largest share of the FPGA market was held by low-end accelerators [8]. This trend is predicted to continue due to different benefits such as low cost, higher energy efficiency, and reduced complexity when using low-end FPGAs compared to their data center-class counterparts. Some application classes, used in sectors like the automotive business and Internet of Things require low-end FPGAs for the previously mentioned benefits. Other classes require the computing performance high-end FPGAs have to offer.

A common aspect, the entire range from low to high-end FPGAs have, is their potential to accelerate highly parallel applications. The size and parallelism available in modern-day Big Data applications

often exceed the computing power of a single FPGA node. By scaling these applications on multiple FPGA nodes, the parallelism can be further exploited resulting in potentially even more significant benefits. This work was performed in collaboration with ALTEN Netherlands and the Accelerated Big Data Systems (ABS) group from TU Delft. ALTEN provided a computationally demanding application with highly parallel features called Full Waveform Inversion to conduct the investigations in this thesis.

# 1.2. Challenges

Two of the main challenges in scaling data analytics applications on FPGAs are accessibility and costefficiency.

#### 1.2.1. Accessibility

The FPGA market has known its challenges since the invention of the FPGA in the early 1980s. In the first 2 decades of development, customer demand dictated the need for FPGAs with more resources to fit their designs. Vendors reacted to this demand by developing modern-day data center-class FPGAs that offer sufficient capacity for the majority of applications [9].

Due to these technological developments, the challenges have shifted from capacity to accessibility and large-scale integration in the data processing paradigm. This challenge is two-fold, due to the complexity and steep learning curve of FPGA design, it is reserved for experienced hardware designers. In addition, there is an absence of support in the form of open-source tools and frameworks for the adoption of application scaling on FPGAs. Developers and engineers with little to no hardware knowledge should be able to transparently and seamlessly scale applications by exploiting the capabilities of FPGAs.

There are current initiatives to increase the accessibility of FPGAs through the introduction of tools such as High Level Synthesis (HLS). HLS enables developers to synthesize FPGA designs from C-like code. Although a step in the right direction, designs generated with HLS are non-optimal implementations and still require in-depth hardware knowledge to fine-tune them into efficient FPGA designs. Another initiative is the concept of build-once, re-use often, where efficient FPGA designs for common applications such as Neural Networks are developed by experienced hardware designers to be made available for the general public. While this concept offers a lot of potential in FPGA adoption, there remains a need for frameworks and support in the data processing toolchains to exploit these ready-to-use hardware designs in a scalable way.

#### 1.2.2. Cost-efficiency

Modern-day data center-class accelerator cards like the Alveo family offer a lot of resources that, if used correctly, can attain enormous performance, throughput, and latency boosts compared to CPUs [10]. At first sight these high-end accelerators may seem adequate for most application classes, but there is no free lunch in engineering and the benefits come at costs such as higher power consumption, costly manufacturing, and expensive development cycles.

#### **Costly manufacturing**

Manufacturing very large integrated circuits is inherently more costly than smaller integrated circuits due to the larger amount of silicon, wafer, and other materials needed. Furthermore, there is a higher chance of defects and yield problems in larger circuits.

#### Expensive development cycle

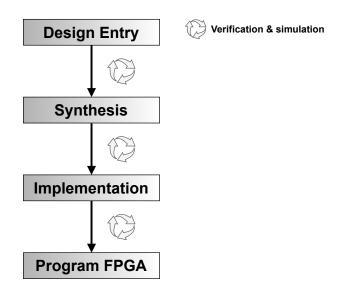

Not only does the cost of manufacturing increase when working with large FPGAs, but other stages of the development cycle also become more expensive. The FPGA design flow, more elaborately discussed in Chapter 2, consists of 4 main phases: design entry, synthesis, implementation, and, programming. In the first phase, a hardware design is written in a Hardware Description Language. In the synthesis phase, this design is translated to a netlist, a collection of logic elements, interconnection resources, and other components necessary to build the design. The implementation phase places and routes the elements from the netlist on the FPGA resources while taking timing, location, and other constraints into consideration.

The synthesis and implementation phases are optimization problems that increase drastically in complexity as the size of the FPGA and design grows. This results in considerably longer, memory and computationally demanding development cycles, often orders of magnitude larger than low-end FPGAs experience. While the development cycle of a low-end FPGA can be performed on an average personal computer, data center-class FPGAs require server-grade machines.

#### Power consumption

Even though FPGAs are considered a silicon alternative that consumes little energy, especially compared to GPUs, there is still a significant difference between small and large FPGAs. Larger FPGAs such as an Alveo U280 have a maximum total power of 225W [11]. A smaller data center-class FPGA, the Alveo U50 has a maximum total power of 75W, which is significantly less, but still an order of magnitude larger than the 10W maximum total power of a low-end accelerator like the PYNQ-Z1 [12].

# 1.3. Problem statement & research questions

In this work, two challenges in the adoption of FPGAs in the data processing paradigm are investigated. There is a lack of tools, frameworks and support for users to easily accelerate and scale data analytics applications on FPGAs. By solving this challenge and enabling seamless scalability over multiple FPGA nodes it becomes possible to consider an alternative cost-efficient composition of multiple low-end FPGAs instead of a single high-end FPGA. This project aims to provide recommendations and solutions to these challenges by using FWI as the primary use case. More precisely, the following research question are answered in this thesis:

- 1. How can FPGAs be used to scale data analytics applications in a transparent and accessible way?

- 2. Can FWI be accelerated and scaled on FPGAs?

- 3. Is a composition of low-end FPGAs a viable alternative to a data center-class FPGA in terms of performance, power efficiency, and cost when accelerating FWI?

- 4. How does vertical and horizontal scaling affect the performance of FPGA accelerated applications?

# 1.4. Solutions and contributions

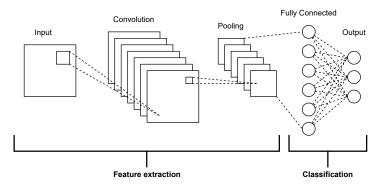

To answer the above-stated research questions several solutions were implemented. The challenge of FPGA accessibility and adoption was addressed by developing OctoRay, a python-based framework that enables users to transparently scale applications on FPGA clusters. A hardware design for the FWI use case was developed and used in combination with OctoRay to accelerate and scale the application on multiple FPGAs. Subsequently it was possible to investigate the viability of using multiple low-end FPGAs alternative to a high-end FPGA for FWI acceleration. The effect of horizontal and vertical scaling was investigated for FWI. An application with different scalability characteristics, a Convolutional Neural Network (CNN) for image classification, was introduced to extend the investigation.

In summary, the contributions of this work are:

- 1. OctoRay, a flexible framework that enables users to scale applications horizontally and vertically with a focus on ease-of-use.

- 2. Design, implementation and evaluation of the FWI algorithm for low-end PYNQ-Z1 and high-end Alveo U280 FPGAs.

- 3. An analysis of the effect of horizontal and vertical scaling for applications with different scalability characteristics CNN and FWI.

- 4. An evaluation of the viability of a multiple low-end FPGA composition as alternative to a high-end FPGA for FWI acceleration.

# 1.5. Thesis outline

In Chapter 2, the concepts, tools, and complementary subjects that serve as a foundation for the understanding of the choices, solutions, and implementations presented in this work are introduced. In Chapter 3, the two applications that were used to benchmark and validate the solutions are presented. This chapter also discusses the characteristics of these applications in terms of scalability. Chapter 4 presents the solutions space considered, successively the chosen solution architectures and implementations are explained in Chapter 5. The experiment setups and the gathered results are presented and discussed in Chapter 6. In Chapter 7, the final chapter of this work, the conclusions made are discussed and recommendations for future work are proposed.

# $\sum$

# Background

This chapter explains the concepts, tools, and other subjects that were used to analyze the problems stated in Chapter 1 and to build the proposed solutions. First, Section 2.1 introduces the Field Programmable Gate Array followed by a description of the design flow and the resources for the targeted platforms in this work. Secondly, the tools from AMD used to implement the solution architectures are discussed in Section 2.2. Having established the platforms and tools required for a single node implementation, concepts to apply scalability are introduced in Section 2.3. Lastly, work related to the adoption of FPGAs with similar approaches as applied in this work are discussed in Section 2.4

## 2.1. Field programmable gate arrays

Field Programmable Gate Arrays were invented in the early 1980s with the goal to accelerate the design process of Application Specific Integrated Circuits (ASIC). The use of FPGAs enabled engineers to design, program, validate and verify hardware designs without having to manufacture actual Integrated Circuits.

As FPGA development matured over the years, they appeared to be useful for much more than simply accelerating ASIC design. In modern days, there are use cases in many different industries for FPGAs. Data centers nowadays are made up of heterogeneous computing infrastructures that aim to make optimal use of the different available hardware options. Like GPUs and ASICs, FPGAs complement CPU clusters in this infrastructure by processing computationally demanding workloads. FPGAs differentiate themselves from ASICs in applications that require rapid development cycles and from GPUs in applications that require low latency as well as energy efficiency [13]. In the automotive industry, FPGAs have taken the upper hand over ASICs when developing Advanced Driver-Assistance Systems, especially due to the reconfigurability characteristic that allows ADAS engineers to easily build on previous designs and reduce the time to market tremendously [14]. As the focus of this work is not on the optimization of FPGA design, only a high-level overview of the internals of an FPGA are presented, the design flow approach, and finally, we introduce the two specific FPGAs that were used during experiments.

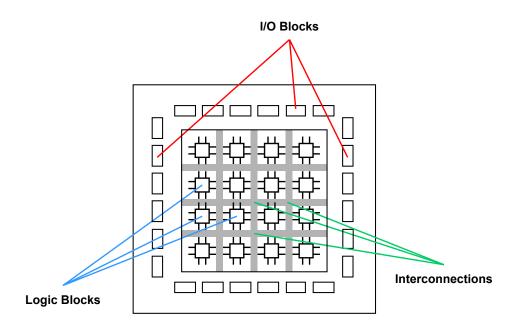

A Field Programmable Gate Array is a unique type of IC that is made up of Configurable Logic Blocks (CLB) and I/O cells which are all connected in a matrix form through interconnection resources, visualized in Figure 2.1. To create functionality, the previously mentioned components are combined into blocks of logic and data. In software design, functions and classes are used to increase code reusability. In hardware design the same applies, to increase the reusability of designs the functional blocks of logic and data are bundled into so-called Intellectual Property (IP) cores. These cores should, when correctly designed, offer portability in a vendor-agnostic manner so that they can be easily integrated in any design methodology. Besides design reusability, IP cores are also fundamental in enabling users with little to no hardware design experience to utilize FPGA functionality.

Figure 2.1: Simplified visualization of the components of an FPGA, figure altered from [15]

#### 2.1.1. Design flow

Different hardware platforms adhere to different design flows to utilize them. Programming CPUs is slightly different from GPUs, but both design flows have in common that they result in a set of software instructions that are executed by the designated hardware platform. The design flows for ASICs and FPGAs are different in that sense, because they result in an IC. The difference between ASICs and FPGAs, is that the former draws the resulting circuit directly into silicon while the latter creates the circuit by connecting the CLBs and other components.

The main phases in FPGA design flow are shown in Figure 2.2. The first phase, design entry, consists of defining the requirements of the system. This can be done with schematics, where the design is drawn with gates and wire, or the more common approach, by describing the design with a Hardware Description Language. Specifically and unambiguously describing the behavior of an IC is not an easy task. Historically, people started describing them on a component level and later rose to a logical level. In the 1980's HDLs such as VHDL and Verilog were introduced. These languages allowed engineers to explicitly describe the behavior of large IC's and the opportunity to simulate and test these systems. The latter significantly reduces the cost of development because circuits could now be validated and tested on performance before being physically created.

Quickly after the introduction of HDLs, engineers started working on tools to abstract even further away from low-level hardware design. They introduced High Level Synthesis which takes a high-level specification of the hardware design in a C-like programming language and compiles it into a Register Transfer Level written in a HDL. High Level Synthesis is still a hot topic that is constantly being developed with the goal to enable software engineers to be able to accelerate their applications on FPGAs at the same rate as experienced hardware designers would. [16]

The next phase in FPGA design flow is synthesis, where the designed system is translated from schematics or HDL into a netlist. A netlist is the collection of logic elements, interconnection resources and other components necessary to build your design.

Figure 2.2: FPGA design flow phases

In the following phase, the components from the netlist are placed and routed onto the matrix of FPGA resources. In this step, the constraints a designer may have posed such as timing, or specific placements are taken into account. Both the Implementation and Synthesis phases apply optimization techniques to use the resources as efficiently as possible. The time, memory, and computing resources necessary to complete these phases increase with the complexity of the design and constraints, as well as with the total amount of FPGA resources available. With complex designs and data center-class FPGAs, the synthesis and implementation phase can take many hours, GBs of storage and RAM.

The final phase in the FPGA design flow is to generate a bitstream from the mapped and routed design and implement it onto an FPGA. At this point, the FPGA is ready to be used.

Each phase of the FPGA design flow is prone to contain errors and undesired behavior. As mentioned before the entire design flow can take a lot of time and resources. To detect possible design flaws and other errors at an early stage, verification and simulation are performed after each phase. After the Design Entry phase, behavioral simulation is performed to check the functionality of the HDL design agnostic of the type of FPGA the design is meant for. In this step, a designer can quickly identify functional or logical errors in the code and fix them.

After synthesis another functional simulation is used to once again verify the correctness of the netlist, but without taking the design constraints into account yet. The final simulation takes place after the Implementation phase. A highly detailed simulation is performed on the placed and routed design. Hardware design is a complicated process in which mistakes and errors are not easily detected. These simulations help designers to overcome these barriers when designing systems.

#### 2.1.2. SoC FPGAs

Like ASICs, FPGAs are often used in a heterogeneous environment where they are responsible for handling critical parts of an application and work in harmony with processors. In such setups, communication between FPGA, memory, and processor is detrimental to performance. As the leading FPGA manufacturers identified this issue they introduced System on Chip FPGAs. A system where the processor and FPGAs are closely integrated, considerably decreasing the number of components and external interconnects [17]. To prevent ambiguity, the FPGA part of a SoC FPGA is called Programmable Logic (PL) and the CPU part including the main memory, is called Processing Subsystem (PS). In this work, the proposed solutions are developed for AMD SoC FPGAs. Therefore the tools and methodologies discussed will apply to AMD boards, it should be noted that similar tools and methodologies exist for Intel and other FPGA vendors. In specific, the experiments have been performed on low-end PYNQ-Z1 and high-end Alveo U280 FPGAs.

## 2.1.3. Platform resources

As previously mentioned, the general architecture of an FPGA consists of CLBs, I/O Blocks and interconnections resources. The fundamental components that are used to build a CLB are look-up tables (LUT) and flip-flops (FF). These components can be used to store data or implement logic. They can for example be used to define an operation or computation by implementing a truth table. Additionally, FP-GAs incorporate different types of memory in the PL. The PYNQ-Z1 FPGA offers two different memory types, block random-access memory (BRAM) and look-up table random-access memory (LUTRAM), the latter is memory built from regular LUTs. The Alveo U280 FPGA contains an additional memory component, ultra random-access memory (URAM). BRAM and URAM are made up of a coarse-grained structure of larger memory blocks of 18Kb for the PYNQZ-1 and two 18, or one 36Kb block for the Alveo U280 [18]. LUTRAM consists of a more fine-grained structure, both boards have 6-input LUTs that can form different size memory blocks ranging from 64 to 512 bits. The previously mentioned memory components are in the PL of the FPGA. The PYNQ-Z1 SoC also contains 512Mb of DDR3 memory in the PS, which stands for Double Data Rate Synchronous Dynamic RAM (SDRAM). The stand alone Alveo U280 has 32 Gbs of on-board DDR4 memory as well as 8 Gb of High Bandwidth Memory version 2 (HBM2). Table 2.1 displays the resources available on the PYNQ-Z1 and Alveo U280 FPGAs.

|            | LUT<br>(x1000) | FF<br>(x1000) | DSP  | BRAM        | URAM        | DDR<br>(GB) | DDR total<br>bandwidth<br>(MBps) | HBM2<br>(GB) | HBM2 total<br>bandwidth<br>(GB/s) |

|------------|----------------|---------------|------|-------------|-------------|-------------|----------------------------------|--------------|-----------------------------------|

| PYNQ-Z1    | 53.2           | 106.4         | 220  | 280 (18Kb)  | -           | 0.5         | 1050                             | -            | -                                 |

| Alveo U280 | 1304           | 2607          | 9024 | 2016 (36Kb) | 960 (288Kb) | 32          | 19200                            | 8            | 430                               |

| Factor     | 24.5           | 24.5          | 41   | 14.4        | -           | 64          | 18.3                             | -            | -                                 |

Table 2.1: An overview of the available resources for the PYNQ-Z1 and Alveo U280 FPGA, The bottom row provides the factor of PYNQ-Z1 to Alveo U280 utilization. [11] [19].

The performance of an application on a SoC FPGA is not entirely dictated by the FPGA resources, the host processor contributes more or less depending on the proportion of the application that is executed outside of the FPGA. The PYNQ-Z1 platform is a SoC FPGA with an integrated Dual-core ARM Cortex-A9, the Alveo U280 is a standalone FPGA. The experiments in this work were performed on the Heterogeneous Accelerated Compute Cluster (HACC) at the ETH university in Zurich, Switzerland, where an Intel Xeon Gold 6234 processor is connected to the Alveo card through two 100 Gbps interfaces. Table 2.2 displays the specifications for the host processors of the targeted boards.

| FPGA       | CPU                  | Maximum frequency<br>(MHz) | Cores | DDR3 (Mb) | DDR4 (Gb) |

|------------|----------------------|----------------------------|-------|-----------|-----------|

| PYNQ-Z1    | ARM Cortex-A9        | 650                        | 2     | 512       | -         |

| Alveo U280 | Intel Xeon Gold 6234 | 4000                       | 16    | -         | 128       |

Table 2.2: An overview of the available resources for the PYNQ-Z1 and Alveo U280 FPGA host processors [12] [20]

## 2.1.4. Direct memory access

Direct Memory Access (DMA) is a computer architecture component that allows direct data transfer between the PS and the PL. AMD provides users with pre-generated DMA IP blocks that handle read and write operations to and from different components. DMA on PYNQ-Z1 boards is used to transfer data through the advanced eXtensible Interface 4 (AXI4) interface between the host DDR and the kernels in the PL. The Alveo U280 utilizes DMA for several purposes. The DMAs can transfer data between the FPGAs DDR or HBM and the host DDR through a Peripheral Component Interconnect Express (PCIe) Gen3x16 interface. Additionally, the DMAs handle data transfer between the FPGA DDR and the kernels in the PL.

# 2.2. Frameworks and toolchains

In the following sections the different frameworks and toolchains used in this MSc. project will be discussed. AMD provides the user with several design tools and projects to target their FPGAs. These tools can be used in combination or standalone.

#### 2.2.1. Vivado design suite

In 2012 AMD released the Vivado sesign suite, a software tool that enabled developers to analyze and synthesize hardware designs written in HDL such as Verilog or VHDL. In addition to its predecessor AMD ISE, Vivado introduces features that enable HLS and SoC development. An important characteristic of Vivado is that its purpose is to create hardware designs for PL. To create the software that interacts with the FPGA, AMD developed a different design suite on top of Vivado, called the Vitis unified software platform.

#### 2.2.2. Vitis unified software platform

Vitis is a collection of software tools that together enable users to develop and exploit ready-to-use FPGA applications from a software oriented perspective. The platform consists of an extensive development kit, a growing ecosystem of hardware-accelerated libraries and other FPGA development related tools. Under the hood, Vitis uses the Vivado Design suite for the FPGA design flow. A relatively new, but key-feature of the platform is the ability to seamlessly duplicate implemented kernels in a hardware-design.

# 2.3. Scalability

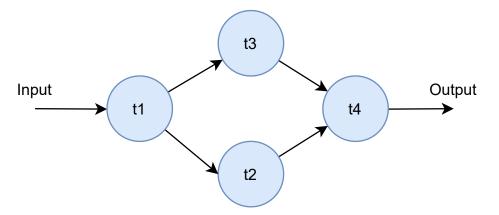

Scalability can be defined by a system or application's ability to increase or decrease in performance and cost in response to changes in the processing demands [21]. In other words, how well can a system handle an increasing work-demand by adding resources to the system. An import aspect of the scalability of an application is the type and amount of parallelism that can be applied. In other words, in how many concurrent parts can an application be divided such that the parts can be processed by different nodes at the same time. There are two general types of software parallelism, data and task parallelism. This section illustrates both types of parallelism with the help of an example application containing 4 tasks that each take 1 second to execute. The dependency graph of the example application is show in Figure 2.3.

Figure 2.3: Dependency graph of parallelism example application.

The dependency graph shows that task 2 and 3 are dependent on the output of the first task and that task 4 is dependent of the outputs of task 2 and 3. If this application were executed on a sequential system where only one task can be processed at a time, it would take 4 seconds to execute.

#### 2.3.1. Task parallelism

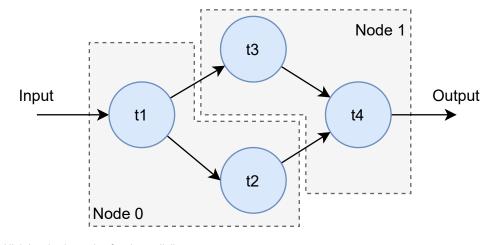

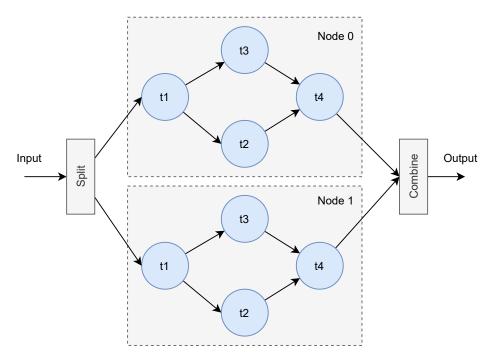

Task parallelism consists of dividing functional components of an application over multiple nodes such that they can be processed concurrently. The level of parallelism that can be achieved is strongly related to the inter-dependencies of the tasks. Task parallelism is applied on the example application and visualized in Figure 2.4.

Figure 2.4: High level schematic of task parallelism.

Although the example application consists of four tasks, it only makes sense to scale it on two nodes because of the dependencies. Executing each task on a separate node would result in tasks 2 and 3 waiting for task 1 to finish, and task 4 on its turn waiting for task 2 and 3 to finish. Essentially only reducing the performance due to the overhead of data transfer between the nodes and increasing the cost by using 3 extra nodes. From the dependency graph it can be read that task 2 and 3 are the only two tasks that can be processed in parallel. Amdahl's law, shown in Equation 2.1, can be used to show the theoretically attainable speedup when parallelizing parts of an application. In the equation, p is the proportion of the application that can be parallelized and is scaled, s represents the speedup of the parallelizable proportion.

$$Speedup = \frac{1}{(1-p) + \frac{p}{c}}$$

(2.1)

Equation 2.1: A formulation of Amdahl's law [22].

In the example application, two of the four tasks are concurrently executed on 2 nodes. When applying  $p = \frac{2}{4} = 0.5$  and s = 2 in Amdahl's law, shown in Equation 2.2, the total achieved speedup is 1.33 at the cost of one extra node resulting in an execution time of 3 seconds compared to the original 4 seconds.

$$Speedup = \frac{1}{(1-2) + \frac{0.5}{2}} \approx 1.33$$

(2.2)

Equation 2.2: Amdahl's law applied to task parallelism on the example application.

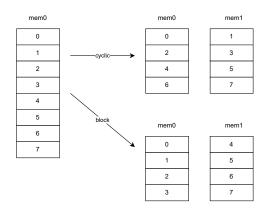

#### 2.3.2. Data parallelism

In data parallelism the same set of instructions or tasks are applied concurrently on different data. This is applied by splitting up the input data in several sets, processing each set concurrently and merging the results back together. Figure 2.5 demonstrates how this is applied to the example application.

Figure 2.5: High level schematic of data parallelism.

Assuming the nodes execute the application in a sequential manner, the execution of the entire application takes 4 seconds. The application of data parallelism in this case does not increase the performance of the application, but rather allows the throughput to increase when processing the application multiple times. Two nodes can now process double the input size in the same execution time. Amdahl's law is applied on this example in Equation 2.3. As the entire application is parallelized over two nodes, p = 1 and s = 2, resulting in a speedup of 2 for double the input size.

$$Speedup = \frac{1}{(1-1) + \frac{1}{2}} = 2$$

(2.3)

Equation 2.3: Amdahl's law applied to data parallelism on the example application.

By increasing the input size and adding more nodes, the speed up increases linearly as p remains the same and s increases i.e. 1000 nodes will process an input of 1000 times larger than the original in 4 seconds at the cost of 999 extra nodes.

Task and data parallelism are two constructs that can be used to scale an application. Task parallelism is often more complex to implement because it needs to manage task-dependencies as well as the data. Data parallelism is simpler concept to apply, but it requires an application for which the input can be split into different parts and processed independently. The example application demonstrates that data parallelism can theoretically be applied infinitely, being only bound by the input size and cost of nodes. Task parallelism can increase the performance of an application but its scalability is bound by the dependencies of the tasks. In practice, both types of parallelism can be used in combination on different levels to scale applications.

#### 2.4. Related work

With the introduction of standardized accelerators such as the Alveo family, FPGAs have greatly risen in popularity. Leading chip-makers and cloud computing companies are respectively developing and exploiting FPGAs at an increasing scale. In addition to the commercial introduction of FPGAs, large operational clusters such as HACC [20] are available to the public. The barrier of FPGA design is being circumvented by the introduction of open source ready-to-use hardware libraries and slowly being tore down with the help of HLS programming tools [1] [16].

Additionally, frameworks are being developed to help integrate FPGAs in widely-used programming ecosystems. One initiative in this direction is PYNQ (abbreviated from Python Productivity for ZYNQ), an open-source project from AMD that makes it easier to use their FPGAs [23]. The framework was originally designed for the low-end ZYNQ SoC FPGA family, but now also supports Alveo cards and AWS-F1 instances. The integration of FPGAs and high-level language frameworks is not naturally efficient. For instance, Peltenburg et al. identified that the serialization bandwidth of high-level frameworks is an order of magnitude lower than modern FPGA interface bandwidth and developed Fletcher, a framework to efficiently integrate FPGA accelerators with Apache Arrow [5].

Other initiatives developed to increase the adoption of FPGAs are in the area of virtualization, allowing the accelerators to be exploited by multiple users in a cloud environment [24] [25]. A concept already widely applied for CPUs and GPUs.

Where virtualization allows multiple users to share FPGAs, an orthogonal research direction is aimed at using multiple FPGAs for a single task. Fleet, a framework developed by Thomas et al. [26], enables users to apply massive parallelization by duplicating FPGA implementations on multiple independent data streams. A newly developed HLS resembling language based on Chisel forms the foundation of the framework. A less sophisticated but much more accessible concept of duplicating FPGA implementations is incorporated by AMD in the Vitis and Vivado tools [27].

Due to its high computational and memory demand, Full Waveform Inversion is only recently becoming a viable seismic imaging technology. Large corporations such as Shell are working together with research groups to accelerate and improve implementations of the algorithm [28] [29]. As a highly parallelizable algorithm, research efforts show that FPGAs and GPUs can offer significant performance improvements compared to traditional CPUs [30] [31].

3

# Application domains

This chapter introduces the applications used to answer the research question in this work, Full Waveform Inversion and Convolutional Neural Network. Sections 3.1.1 and 3.2.1 provide the reader with background information about the applications and the implementations used in this work. The sections conclude by characterizing the applications in terms of scalability in Sections 3.1.2 and 3.2.2.

# 3.1. Full Waveform Inversion

Full Waveform Inversion (FWI) is a data fitting method that aims to reconstruct velocity models of subsurface grids by iteratively solving a non-linear inversion problem. In this work, a linear approach is assumed to reduce complexity, the details of the linear approach are explained in Section 3.1.2. The non-destructive and high-resolution nature of FWI makes it suitable for applications such as seismic modeling and medical ultrasonic. Until recent years FWI was scarcely applied due to the heavy computational power required, the difficulty to estimate a good initial model, and the non-uniqueness of the solutions [31]. This section starts by providing background information about the algorithm and discusses some implementation specific aspects. Lastly, the application characteristics in terms of scalability are presented.

## 3.1.1. Background & implementation

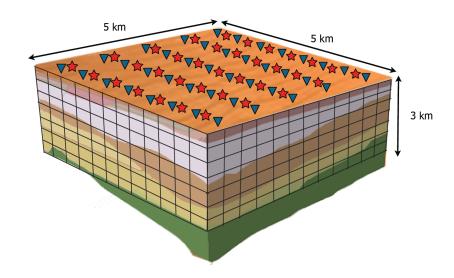

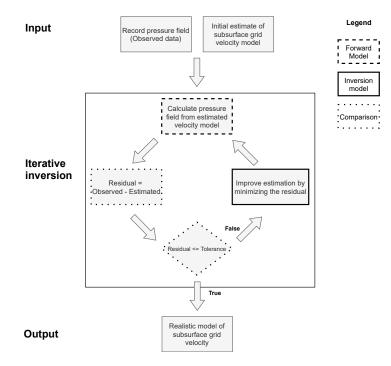

Over the years, many FWI approaches have been studied to improve image quality and reduce computational complexity. Approaches mostly differ in the number of physical dimensions taken into account, the type of waves measured and assumptions on the background of the grid. In this work an approach developed by Peter Haffinger in his Ph.D thesis is used [32]. The approach implements FWI using acoustic waves in a 2-D model where a homogeneous background of the measured subsurface grid is assumed. Figure 3.3 shows a simplified diagram of the approach. Three stages are specified, the input, the iterative inversion and the output. The input consists of gathering the recorded pressure field data and making an initial estimate of the subsurface grid velocity model. The pressure field data is in practice obtained by physically recording it in a subsurface grid. A common method to obtain this data is by using sources, such as small explosions, to generate acoustic waves in the subsurface grid. For a defined range of frequencies, the pressure field of the reflected waves is captured by receivers such as microphones and serves as the observed input data. In Figure 3.1 an ideal case of 3D inversion is shown.

Figure 3.1: A high-level overview of the FWI algorithm.

In the figure, the surface is covered in a matrix of sources and receivers, marked as stars and triangles. The subsurface is discretized into a grid, where each cell represents a grid point. The approach in this work is based on several assumptions. First, the input measured data from the sources and receivers, called the observed data, is synthetically generated. As mentioned previously, a homogeneous background with a constant acoustic velocity of  $c_0 = 2000m/s$  is assumed. The synthetic data represents layers of the subsurface structure with different, also homogeneous acoustics velocities. The contrast function of the acoustic velocities is in practice an unknown factor that is deduced from the seismic data. In this work, the contrast function, called chi ( $\chi$ ), is displayed in equation 3.1 where  $c_0(\vec{x})$  represents the homogeneous background velocity and  $c\vec{x}$  the subsurface layers' velocity.

$$\chi(\vec{x}) = 1 - \left[\frac{c_0(\vec{x})}{c(\vec{x})}\right]^2$$

(3.1)

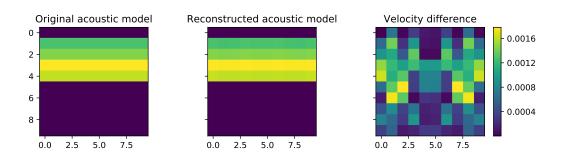

An example of a synthetic model is displayed in Figure 3.2, where on the left the original acoustic model is shown, the center represents the model reconstructed by applying FWI and the right shows the difference in chi between the original and reconstructed model. The horizontal and vertical axes represent the subsurface grid, a grid length of 1 in the figure represents 5 meters.

Figure 3.2: The synthetically generated acoustic model with a homogeneous background of  $c_0 = 2000m/s$ , embedded in the background are four layers with constant velocities from top to bottom of respectively 2200, 2233, 2300 and 2266 m/s. The differences are displayed by means of the contrast function and represent chi values. The grid is scaled where 1 grid length in the figure represents 5 meters.

The synthetic nature of this approach means the original acoustic model shown on the left of Figure 3.2 represents the true velocity model. To create the synthetic input data from this true model, the pressure field data that is normally measured is calculated by solving wave equations of the acoustic waves generated and received from, respectively, the sources and receivers over a defined set of frequencies. This process is used extensively during the iterative stage of FWI and is called the forward model. The resulting pressure field data is a synthetic equivalent to the data measured in the field in the case of a real implementation. Because the approach assumes a homogeneous background, the initial estimation of the subsurface velocity expressed through the contrast function consists of zeros. In other words, the initial estimation of the subsurface grid's velocity is that it is equal to the homogeneous background at 2000 m/s.

The second stage of FWI consists of an iterative approach to improve the estimated velocity model until an acceptable difference in chi is attained, measured by a tolerance variable. Figure 3.3 shows the main steps that occur in the iterative inversion phase. The first step is to apply the forward model to the estimated velocity model to retrieve pressure field data. This data is then compared with the synthetically generated pressure field data. The difference between the calculated and synthetic pressure field data, called the residual, determines the quality of the current estimated velocity model. If the residual is larger than a predefined tolerance, the quality of the estimation is deemed inadequate. A cost function as part of an optimization technique is used to minimize the residual and update the estimated velocity model, this process is referred to as the inversion model. These steps are iteratively repeated until the residual is smaller than the predefined tolerance, resulting in a realistic model of the subsurface grid velocity. The output of the model is a reconstructed velocity model of the subsurface grid expressed with the contrast function chi. An example is displayed in the center of Figure 3.2. The implementation of FWI in this research, uses a Finite Difference Forward model and an inversion model based on the Conjugate Gradient Descent cost function. These implementations were chosen because they are less computationally intensive and highly parallelizable. An alternative for the forward model is the integral model. Alternatives for the inversion model are random inversion, evolution inversion and gradient descent inversion. A more in depth overview of the implementation can be found in Appendix A.3

#### Full Waveform Inversion

Figure 3.3: A high-level overview of the FWI algorithm.

#### 3.1.2. Scalability characteristics

In real applications FWI needs to process incredible amounts of data. The inversion process is applied on a kernel further referred to as kappa. Kappa is built from a four dimensional function, the number of sources and receivers, the time measured and the number of unknown velocity values. For the sake of simplicity, in this work the time dimension is omitted. Before determining how kappa is built, an explanation is given of the linear and non-linear properties of FWI.

In FWI, each source produces a wave field that interacts with all the grid points in the subsurface grid. Every grid point that is not equal to the homogeneous background reflects a scattered wave field for every source originating field, effectively creating extra sources. The receivers measure not only wave fields from the original sources, but also from all the secondary sources. The interaction from the secondary sources causes a non-linear relationship between the actual velocities of the subsurface layers and the measured data. The kappa matrix represents the total field, where the pressure data for all the scattered and original wave fields for each measured frequency is mapped to the grid points. The dimensions of the matrix are *sources* \* *receivers* \* *frequencies* rows and the number of grid points as columns.

This non-linear property forces FWI to use the entire input space of measured data to perform a realistic inversion. In a real application this input space is extremely large, an example based on the 3D model in Figure 3.1 is shown in Table 3.1. The example is based on a  $5x5x3 = 75km^3$  domain where each cell is  $5x5x5 = 125m^3$ , this means there are  $6 * 10^8$  unknown velocity values in the domain. By assuming a sample size of 8 bits the kappa kernel is  $6.7 * 10^2$  Gb. These memory requirements become even larger if the time dimension is taken into account. The previously mentioned non-linearity results in the entire kappa matrix needed for the computations performed in the inversion model. Without quantum computers or much more powerful computing clusters, it is unfeasible to apply FWI for real 3D applications at this moment in time.

| х | 40000                   | # of sources      |

|---|-------------------------|-------------------|

| х | 40000                   | # of receivers    |

| х | 6 * 10 <sup>8</sup>     | # of unkowns      |

| = | $8.3 * 10^{10}$         | samples in kernel |

| х | 8 bits                  | per sample        |

| = | $6.7 * 10^2 \text{ Gb}$ | total kernel size |

Table 3.1: Memory requirements for kappa kernel in a real application with 40000 sources and receivers, measured over a  $5x5x3 = 75km^3$  grid with a cell size of  $5x5x5 = 125m^3$  assuming 8 bits per sample. Example adapted from [32].

The FWI used in this work based on Peter Haffinger's thesis consists of 2D model, drastically reducing the kernel size. Another solution he proposed to reduce the complexity is to apply localization of the grid. Essentially ignoring the non-linearity of the entire subsurface grid in the local inversions, and only applying it after all the local domains have been inverted. In this work, the same concept of domain decomposition is applied to show FWI can be scaled. For the sake of simplicity, the non-linear conversion after inverting the local domains is not applied. It should be noted that the non-linearity due to wave field scattering inside the local grids is taken into account.