# Fault Classification and Vulnerability Analysis of Microprocessors

# Pavan Talluri

# Fault Classification and Vulnerability Analysis of Microprocessors

by

# Pavan Talluri

to obtain the degree of Master of Science at the Delft University of Technology,

Student number: 4942256

Project duration: November 5, 2019 – November 4, 2020

Thesis committee: Dr. Ir. M. Taouil TU Delft, supervisor

Prof. Dr. Ir. S. Hamdioui TU Delft

Dr. Ir. R. van Leuken TU Delft

Ir. D. Vermoen Riscure B.V.

This thesis is confidential and cannot be made public until February 5, 2028.

An electronic version of this thesis is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

## **Abstract**

The adoption of Microprocessors is increasingly diversifying to several embedded and mobile devices. Growingly they can also be found in Smart Cards, RFID tags, SIM cards, Pay TVs, identity cards and passports. These devices store, processes and transact sensitive information like social security numbers and credit card numbers. Ensuring security of such systems is of paramount importance. Attackers use Fault injection as one of the techniques to induce faults into the processor in order to gain access to the sensitive information to abuse it. Vulnerability Analysis of the processors can help chip designers to counteract some of these risks. This analysis can be achieved by investigating the resulting fault space upon exhaustive simulation of fault injection attacks. Therefore, efficient tools and frameworks are needed to provide such security verification, where critical vulnerabilities can be discover and mitigated at design-time.

Multiple tools and frameworks for simulation based fault injection of hardware designs are available in literature, each with their own shortcomings. Two main strategies have been proposed in literature, one based on tool manipulation while other based on code modification. Applying tool manipulation, a designer can automate the process to inject faults in the system and obtain simulation results in a fast manner. However, this approach is limited by the features provided by the tool, which makes difficult to explore many different fault models. Additionally, in most cases, results require manual inspection to be interpreted. The latter approach, which is code modification, can inserts agents to cause the faults (i.e., saboteurs) or vary the existing design (i.e., mutants). It allows designers to achieve a high degree of control in terms of the type of fault and the injection method. However, current solutions are limited to a specific language, design or scenario. Hence, the literature presents many different strategies and tools to apply faults to investigate hardware behavior, but still the interpretation of vulnerabilities related to processors are not considered in such tools. Moreover, a complete automated framework capable to get a design and process it to report vulnerabilities and behavior issues related to security is still needed.

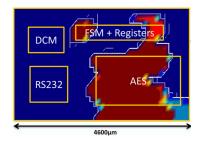

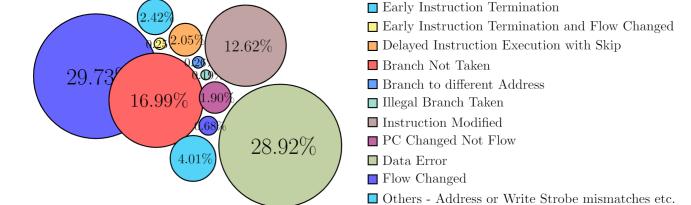

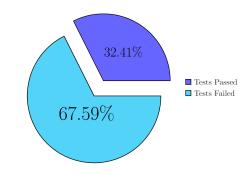

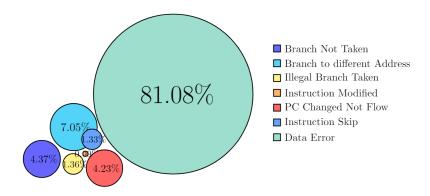

This thesis proposes a framework that provides a complete toolset able to evaluate vulnerabilities of processors in hardware description language. Its main steps comprises design instrumentation, simulation based fault injection and automatic fault classification. RISC-V is chosen as the target architecture due to its open source nature and its increasing adoption by academia and industry. Code profiling was carried out on the frameworks to identify bottlenecks to performance. The results were used to optimise execution time of simulations using the framework. Performing Fault injection campaigns requires running simulations in the order of 100k, which requires systems with high computing power to complete them in reasonable time. Therefore, multiprocessor support was implemented in simulation framework, which could be enabled or disabled during the injection campaign. The framework was used to perform fault injection campaigns on PicoRV32 and DarkRISCV processors. A comparison between the processors is made based on their major failure signatures. Analysis of finding design constructs in the processors which cause the major failure signatures was carried out. The results from this vulnerability analysis are used to propose software and hardware countermeasures to make the design more robust against fault injection.

# Acknowledgements

I would thank all the following people without whom this thesis would have been far from completion. In no apparent order:

- My daily supervisor Dr. Ir. Mottaqiallah Taouil from TU Delft (NL) for all the guidance and support during the project as well as writing the thesis. I would like to thank Prof. Dr. Ir. Said Hamdioui, my supervising professor for his intriguing lectures and introducing me to the field of hardware reliability and security.

- Dennis Vermoen and Stefan Droege, supervisors at Riscure BV. Their insights and feedback were critical for what I have achieved in my thesis. Despite being busy, they always found time to answer all my questions and have weekly meetings to help me progress throughout the length of my thesis.

- · Cezar Wedig Reinbrecht, for his suggestions and assistance in all the weekly meetings.

- My parents, Sankar and Kamala for their motivation and support, whom I owe everything to.

Pavan Talluri Delft, October 2020

# Contents

| Αb | strac | et e e e e e e e e e e e e e e e e e e         | ii  |

|----|-------|------------------------------------------------|-----|

| Αc | knov  | vledgements                                    | iii |

| 1  | Intro | oduction                                       | 1   |

| -  | 1.1   | Motivation                                     | 1   |

|    | 1.2   | State of the Art                               |     |

|    | 1.3   | Thesis Contributions                           |     |

|    | 1.4   | Report Outline                                 |     |

|    |       | ·                                              |     |

| 2  |       | Overview of Faults and Fault Injection Attacks | 5   |

|    | 2.1   | Faults                                         |     |

|    |       | 2.1.1 Sources of Faults                        |     |

|    |       | 2.1.2 Fault Categories                         | 11  |

|    |       | 2.1.3 ISA/Software Faults                      | 12  |

|    | 2.2   | Fault Injection Techniques                     | 14  |

|    | 2.3   | Fault Models                                   | 15  |

|    | 2.4   | Fault Injection Frameworks                     | 16  |

|    | 2.5   | Countermeasures                                |     |

|    |       | 2.5.1 Software Countermeasures                 | 18  |

|    |       | 2.5.2 Hardware Countermeasures                 |     |

| _  |       |                                                |     |

| 3  |       |                                                | 21  |

|    | 3.1   | RISC-V                                         |     |

|    |       | 3.1.1 Instruction Set Architecture             |     |

|    |       | 3.1.2 Control and Status registers             | 22  |

|    |       | 3.1.3 RISC-V Tool Chain                        | 23  |

|    | 3.2   | RISC-V OpenSource Cores                        | 24  |

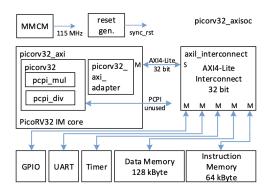

|    |       | 3.2.1 PicoRV32                                 | 24  |

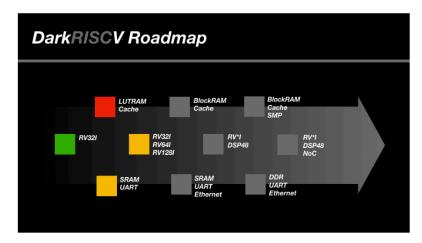

|    |       | 3.2.2 DarkRISCV                                | 25  |

|    | 84-41 | andalam.                                       | ~~  |

| 4  |       |                                                | 26  |

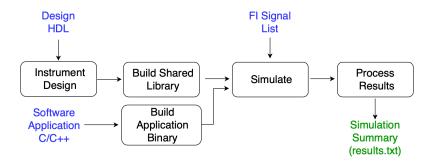

|    | 4.1   | Methodology Overview                           |     |

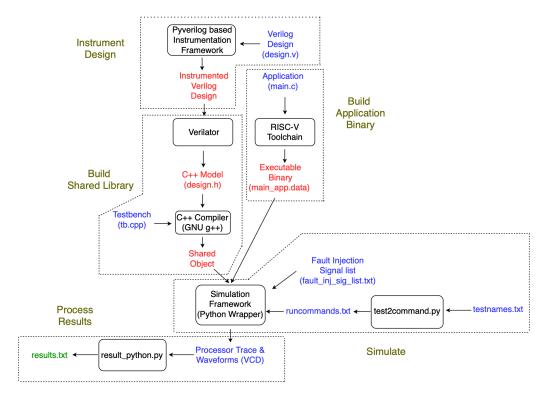

|    | 4.2   | Tool Flow Overview                             |     |

|    | 4.3   | Instrument Design                              |     |

|    | 4.4   | Build Shared Library and Application Binary    |     |

|    | 4.5   | Fault Simulation                               |     |

|    |       | 4.5.1 Fault models                             | -   |

|    |       | 4.5.2 Fault classification                     |     |

|    |       | 4.5.3 Simulation                               | 38  |

|    | 4.6   | Process Results                                |     |

|    | 4.7   | Code Profiling and Optimisations               | 13  |

|    | 4.8   | Multiprocessor Support                         | 15  |

| _  | C     | a study . El of BiopDV22 Dowl-DISCV            | 46  |

| 5  |       |                                                |     |

|    | 5.1   | PicoRV32                                       |     |

|    |       | 5.1.1 Fault Injection & Fault Bucketing        |     |

|    |       | 5.1.2 Results                                  |     |

|    | 5.2   | DarkRISCV                                      |     |

|    |       | 5.2.1 Fault Injection & Fault Bucketing        |     |

|    |       | 5.2.2 Results                                  | 19  |

Contents

|     | 5.3 Comparison of processors           | 52<br>52<br>53 |

|-----|----------------------------------------|----------------|

| 6   | Conclusion           6.1 Summary       |                |

| Α   | Platform setup                         | 58             |

| В   | RV32I ISA                              | 60             |

| С   | Watchdog Timer - Sample Verilog Design | 61             |

| Bil | bliography                             | 62             |

1

## Introduction

#### 1.1. Motivation

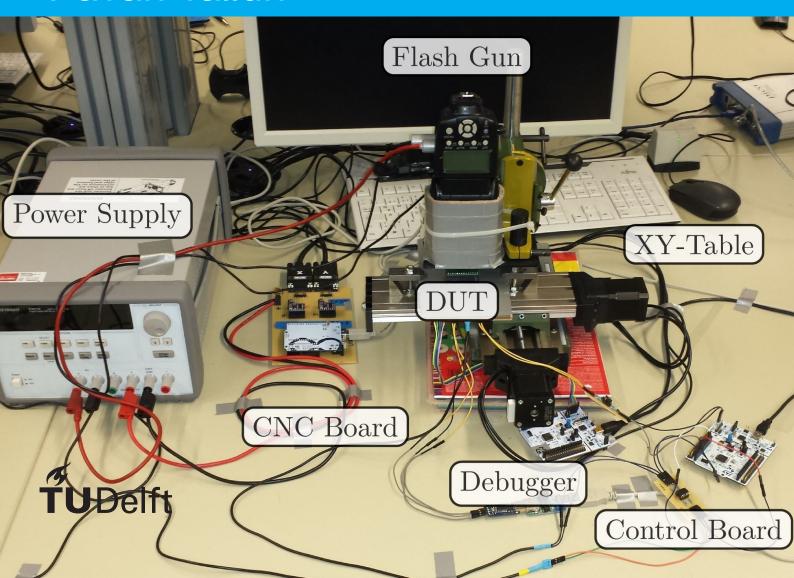

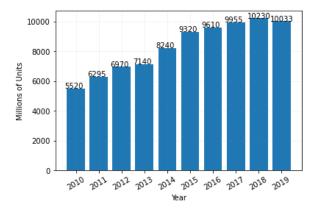

Since the invention of the transistor, silicon industry has made significant progress in improving the computational capacity, power and size of silicon devices by orders of magnitude. This complexity opened up several avenues for adversaries to develop new forms of hardware attacks [21]. One important target are the processors, which are increasingly seen in smart devices such as ID cards, SIM cards and smart cards [28]. This claim can be substantiated by the trend of increasing shipments of secure devices in Europe from 2010-2019 shown in Figure 1.1. These devices store sensitive information and are often targeted by attackers, who try to retrieve this information by compromising their security. One of the most dangerous threat are the fault injection attacks. The first article to discuss about fault attacks in literature is from 1997, by Boneh [16]. It lists the methodology followed in corrupting a computation by manipulating the circuit environment through fault injection. Since then, several new techniques have been designed to compromise or steal sensitive information causing great impact on silicon industry [35][62][15].

Figure 1.1: Secure Devices Shipments in Europe [4]

Fault injection can be achieved by various techniques such as variations in supply voltage, external clock, temperature, exposing to high intensity laser, electromagnetic radiation etc.[28]. Protecting systems against fault injection is quite challenging. Successful fault attacks were carried against DES implementation on a smart card [32], protected implementation of AES [72] as well as RSA authentication[10]. This is the reason why system designers require an abstraction of set of faults that could possibly be used by the attackers. Consequently, such knowledge allows engineers to build more effective software and hardware countermeasures [56]. This grouping of possible set of faults can be termed as a fault model. Most countermeasures are based on based on redundancy and this add considerable area to the design or increases execution time. This is due to the fact that, there

2 1. Introduction

exist no methodology to evaluate vulnerable parts of the design in the event of a fault. Therefore, to achieve an efficient methodology to explore the vulnerable parts of a design, a technique to stimulate the design under different fault models is needed.

Fault injection(FI) techniques can be classified into Hardware based, Software based, Simulation based, Emulation based and Hybrid [29]. Hardware based fault injection requires specialised equipment to inject faults. The focus of this thesis is to inject faults at HDL level and thus simulation based FI is adopted. Existing FI techniques focus on modifying the HDL code manually which is not desirable. This thesis overcomes this limitation by proposing an automated frameworks to instrument the design, inject faults and perform automatic fault classification. Vulnerability analysis of the processors as well as software and hardware countermeasures are discussed towards the end.

#### 1.2. State of the Art

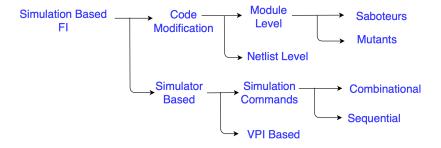

There exist multiple techniques of simulation based fault injection for any HDL like Verilog. Different classes of techniques are shown in the Figure 1.2. Saboteur is a special module added to the design, which if activated, alters the value or timing characteristics of a signal in the original design at the port level. It don't effect the design when inactive. A mutant is module that replaces the original design module, which when activated behaves like a module in presence of faults. Either behavioural descriptions of the design are modified or sub-modules are replaced with different modules. Simulator commands can also be used to modify values of either the signals or registers in a design. Unlike saboteurs and mutants, simulator commands doesn't require code modifications in the design. Simulation events to inject faults can also be invoked by using Verilog programming interface(VPI). VPIs are simulator independent and can be used to inject fault in any event region of a Verilog simulator.

Figure 1.2: HDL based fault injection techniques [37]

Code Modification - Saboteurs: A tool for automatic placement of saboteur was described in [43]. This tool, unlike the previous ones, was built considering FI for emulating external attacks and thus included different fault effects that could be implemented by a saboteur such as stuck at 0/1, indetermination, delayed input etc. Though placement of saboteur is automatic, a port selection for the placement is to be manually selected from a provided GUI. This approach becomes unmanageable for complex designs. The tool does not do signal extraction from design, making choosing critical signals hard.

Code Modification - Mutants: An automated framework for mutant based fault injection approach was discussed in [44]. Multiple mutations have been considered by perturbing the model at conditions such as if and case statements, assignments as well as operators. These translate into Stuck-Then, Stuck-Else, Micro-operation, global stuck data, local stuck data fault models. Using the configuration mechanism, multiple models are generated with a single fault in their component when compared to the reference model. A static mechanism would allow only permanent faults to be injected. A dynamic approach was developed by using guard signals along with configuration mechanism to allow for injection of transient faults. In this approach, initially a fault free model is simulated till the time of fault injection. Simulator commands are used to stop the simulation and save the state to fault. The saved state is loaded to a model with a mutant and simulation is resumed. The drawback of this approach is its simulation time and memory required by simulator to store all the models. The simulation time was

1.2. State of the Art

measured to be 100 times slower compared to the traditional simulation command based approach.

Code Modification - Netlist Level: The paper [12] discusses about a net list level fault injection tool for FPGAs. The framework uses a fault injection unit (FIU) hardware module in the FPGA to inject faults in RTL. The fault models modelled were stuck at 0/1, Random fault, Delay fault and SEU fault. The nets in the net list, which need to be injected with faults are opened and connected to FIUs. FIUs either drive the original value or a modified value to reflect one of the fault models mentioned earlier. Random faults are made possible due to the implementation of LFSRs. The timing and the type of fault model are controlled by a fault injection controller (FIC), which in-turn is programmed by the user. The user enter all the nets of the synthesized design to be subjected to fault injection. Random faults can also be controlled by the user by LFSR load value. A fault pattern file can also be used in-order to inject longer sequences of faults. The drawback of this solution are that, it requires a third party synthesis tool as well as signals present in HDL may not be present in netlist due to logic optimisation. The framework also doesn't provide a simulation script to generate a specific fault case in logical simulation.

**Simulator commands - Combinational:** Simulation based fault injection was earlier used to access the dependability of fault tolerance of systems towards radiation such as cosmic rays, known as single upset events[61]. This 1993 paper [50] proposes a VHDL based simulation tool, that can inject stuck at faults for simple designs. It fails to discuss about the scalability of the tool to more complex designs such as a processor and is language specific to VHDL.

**Simulator commands - Sequential:** A different approach entails fault injection into the model at the time of simulation by use of simulator commands. Here, the values of variables and signals of the model are varied by the simulator to model a fault. The paper [24] proposes a tool controlling the simulator to facilitate FI. Macros are used to prevent re-writing command code for every single fault. A precise control of fault duration, fault instant, fault value and fault signal/variable by the tool is possible. The drawbacks of this approach are, the fault simulation is very slow and cannot be used for fault space exploration; furthermore, the tool is simulator specific.

**VPI:** A Verilog VPI based approach was suggested in [18], which is independent of the simulator used unlike the simulator command based approach. Simulator command approach to inject faults into a non blocking statement is not possible as NBA(Non Blocking Assignment) is done in event region 3 of Verilog simulator as opposed to region 1. As modifying Verilog design code like in mutants and saboteurs is not required, recompilation for different fault injection simulations is not a necessity. Bit flip, stuck at 0/1, indetermination and high impedance were the fault models targeted. The developed framework reads inputs from user in an XML format, where the desired fault properties can be specified. ICORE processor was used to carry out the case study. The only shortcomings of the approach are its inability to scale to different type of faults as well as its performance for large scale fault exploration. This approach involves halting the simulator at the fault injection instant, injecting the fault, run simulation for specified fault injection period, halt the simulator, clear the fault and resuming the simulator again. The overhead of start-stop approach of the simulator as well as the need to manually add the required fault for the simulator hinder its use for a large scale fault space exploration.

4 1. Introduction

#### 1.3. Thesis Contributions

The main goal of this thesis is to design a framework to analyse how vulnerable is a processor to fault injection attacks. To achieve this objective, this thesis perform fault space exploration by injecting faults into the design, propose a classification for the faults and finally evaluate the methodology efficacy by embedding some countermeasures into a processor. The proposed framework is validated through two use cases; the RISC-V architectures namely PicoRV32 and DarkRISCV. As a result, we compare and contrast for vulnerabilities in their implementations. The primary contributions of the thesis have been the following.

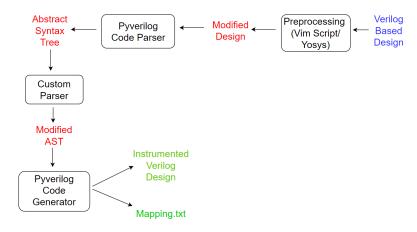

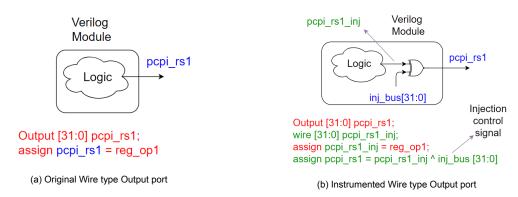

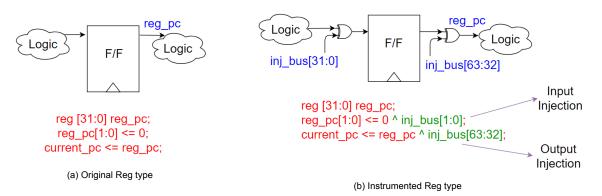

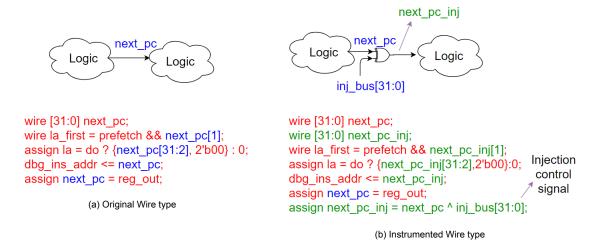

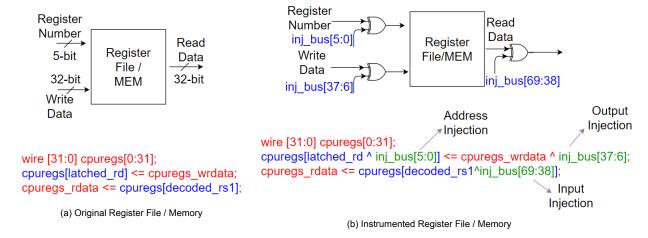

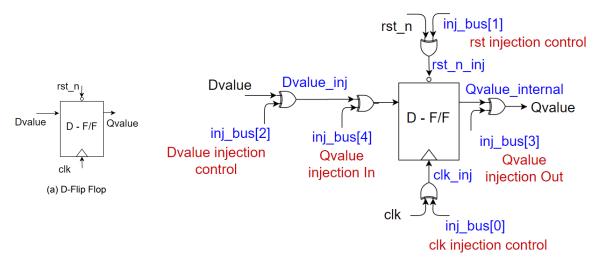

#### Creation of a framework for automatic instrumentation of Verilog-2001 based design to facilitate fault injection

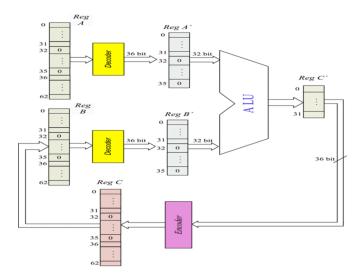

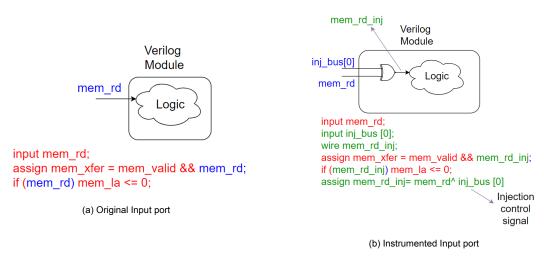

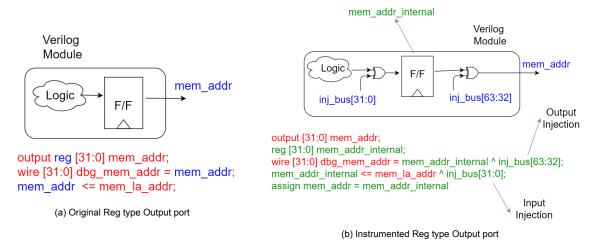

The framework employs, Pyverilog to convert the design described in Verilog-2001 to an abstract syntax tree (AST). This AST is read by a custom parser written in python, that instruments the code with fault injection signals. Finally, the framework utilises an AST code generator tool to convert the modified AST back to Verilog. All the registers and wires in the design can be injected with faults from the injection bus provided on the top level module of the design.

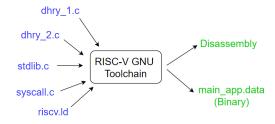

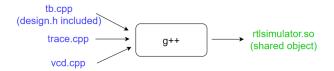

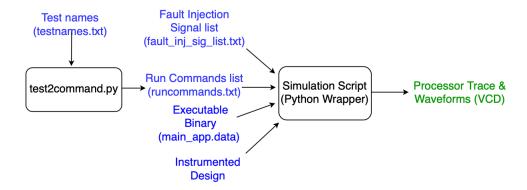

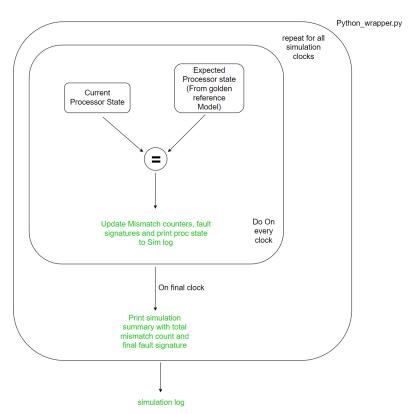

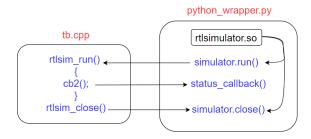

#### Development of a framework for simulation of designs which supports injection of fault in run time with automatic fault classification

The python framework converts the verilator based test bench to a C++ object, that is loaded as a run time library. The functions in the library are utilised by the framework to inject faults in the design when the simulation starts. The names of signals and registers where the fault are to be injected is provided as an input to the framework. Multiple simulations are run, each with a single fault in one of the bits of the aforementioned signals and registers. The framework also categorises the failed simulations to one of the fault categories. The framework has multiprocessor support, enabling it to be scaled to larger designs.

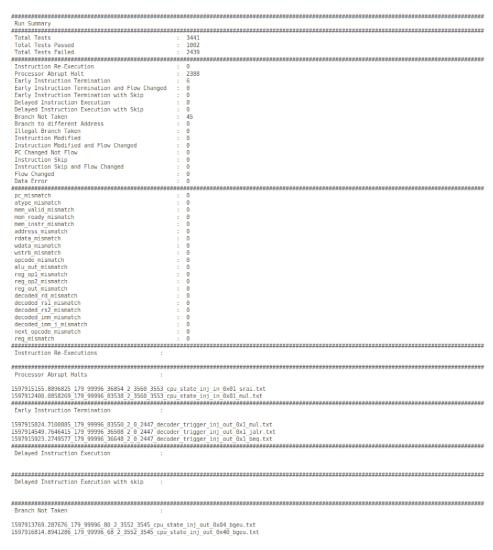

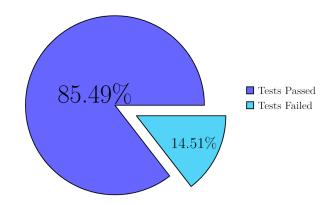

#### Exploration of the fault space on RISC-V based processors

An exhaustive search of fault space was performed with a single fault per simulation for RISC-V based processors. All the faults were grouped into multiple fault classes based on their resulting effect on the processor state.

#### Comparison of Fault space for different RISC-V based processors

A complete fault space exploration was performed for PicoRV32 and DarkRISCV, both of which implemented the RISC-V ISA. Analysis, comparing both the faults spaces illustrates the effect of different implementations of same ISA on resulting faults.

#### · Proposing countermeasures for faults in the resulting fault space

Countermeasures were proposed for faults with highest frequency as seen in the simulations for PicoRV32. A watchdog timer was implemented in the design as a hardware countermeasure for the class of abrupt halt faults. A software countermeasure was envisaged to protect against control flow errors like 'branch not taken' class of faults.

#### 1.4. Report Outline

The remainder of the thesis is divided into five chapters. Chapter 2 gives an introduction to different faults, fault models and fault injection attacks. These basics help to create a background to help dive into the later chapters. Chapter 3 discusses about the RISC-V architecture, ISA, available tool chains and open source cores. Fault injection corrupts the state of the processor and thus is checked on every clock cycle by the simulation framework. To understand what constitutes as a processor state, knowledge regarding the RISC-V architecture is of paramount importance. Chapter 4 presents the tool flow and framework that was used in this research, to instrument the design, inject faults and classify the faults automatically. Several tools like verilator, Pyverilog and Yosys that were integrated into the framework are also briefly discussed. Results of fault injection for PicoRV32 and DarkRISCV along with the implemented hardware and software countermeasures are examined in Chapter 5. Chapter 6 concludes the thesis as well as discusses about the future scope of this research direction.

# An Overview of Faults and Fault Injection Attacks

This chapter introduces the concept of faults and its sources, fault categories, fault models, fault injection techniques and finally some fault injection frameworks.

#### 2.1. Faults

A fault is an unpermitted deviation of atleast one characteristic property (feature) of the system from acceptable, usual, standard condition [36]. It is an abnormal condition that may cause reduction in, or loss of, the capability of a functional unit to perform a required function [31]. In the following subsections, we describe in details the sources of faults in a hardware system, how faults can be categorized and what are software/ISA faults.

#### 2.1.1. Sources of Faults

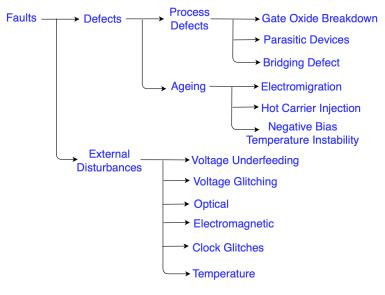

Different faults are possible based on the type of source. They are shown in the Figure 2.1 and are discussed in more detail in the following sections.

Figure 2.1: Types of faults

#### **Defects**

Manufacturing processes may induce imperfections in the intended CMOS structures, affecting their expected behaviour. These flaws are termed as process defects. In the course of their lifetime, ageing can also induce flaws in the CMOS based designs, termed as time dependent defects. Some defects are listed in the Figure 2.2. Environmental factors such as cosmic rays and radioactive particles can also induce faults into chips. Physical disturbances such as voltage underfeeding, lasers, EM pulses and clock glitching can be used by an attacker to induce faults in the chip in order to derive secret information or compromise its security. These are discussed in detail in the coming sections.

| Causes                                       | Targets                                           | Fault mechanisms                                                                   | Type of fault            |

|----------------------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------|--------------------------|

| Residues in cells                            | Memory and registers                              | Intermittent contacts                                                              | Manufacturing defect     |

| Solder joints                                | Buses                                             | Intermittent contacts                                                              | Manufacturing defect     |

| Electromigration                             | Buses                                             | Variation of metal resistance                                                      | Wearout-Timing           |

| Delamination                                 | I/O connections                                   | Voids                                                                              |                          |

| Crosstalk                                    | I/O connections<br>Buses                          | Electromagnetic interference                                                       | Internal noise<br>Timing |

| Gate oxide soft breakdown                    | NMOS transistors in SRAM cells                    | Leakage current fluctuation                                                        | Wearout-Timing           |

| Negative bias-temperature instability (NBTI) | PMOS transistors in combinational logic           | Increase of transistor threshold voltage $V_{TH}$<br>Reduction of carrier mobility | Wearout-Timing           |

| Negative bias-temperature instability (NBTI) | PMOS transistors in SRAM cells                    | Local mismatches among cell transistors, decrease of static noise margin           | Wearout                  |

| Hot-carrier injection (HCI)                  | NMOS transistors in combinational logic           | Increase of transistor threshold voltage $V_{TH}$                                  | Wearout-Timing           |

| Low-k dielectric breakdown                   | Buses<br>I/O connections                          | Leakage current fluctuation Temperature variations Capacity degradation            | Wearout-Timing           |

| Doping profile and gate length deviations    | MOS transistors in combinational logic and memory | Deviations in $V_{TH}$<br>Deviations in operation speed                            | Manufacturing variations |

Figure 2.2: Defects and their fault mechanisms [17]

#### **Process Defects**

#### Gate Oxide Breakdown

Gate is more vulnerable to breakdown if the manufactured gate oxide is thin. When the transistor operates and the current flows though the gate, manufactured traps get charged and start damaging the oxide. This causes thermal damage to the transistor, which increases conduction through the traps and thereby creating more traps. A conductive path between the substrate layer and metal layer of the transistor is established. If the resulting effect is only higher leakage current, this phenomenon is called soft gate oxide breakdown. A manifestation of a cross section in the gate connecting the metal and substrate layer is termed as a hard gate oxide breakdown [47].

#### Parasitic Devices

Unintended structures like PN junctions, Bipolar/ MOS transistors can manifest in integrated circuits (IC) due to fabrication process variations and Design/layout geometric constraints. These parasitic devices can sometimes benefit the parametric performance of design, but a conscious effort is made to keep their effect low to maintain the functional intent of the IC. A decrease in output current drive, timing constraint violations, increased I<sub>DDQ</sub> and I/O leakages can be attributed to parasitic devices in CMOS ICs. In a p-channel transistor, due to vertical and horizontal parasitic npn transistors in p-wells causes negative charge instability in undoped dielectric layer. For designs that should be radiation hardened, gate and field oxide transistors are particularly to be avoided. If design effort is not made to avoid these parasitic transistors, they would cause increased propagation delay, altering of logical functional intent of the IC and decreased maximum operatable clock frequency [70].

2.1. Faults 7

#### Bridging Defect

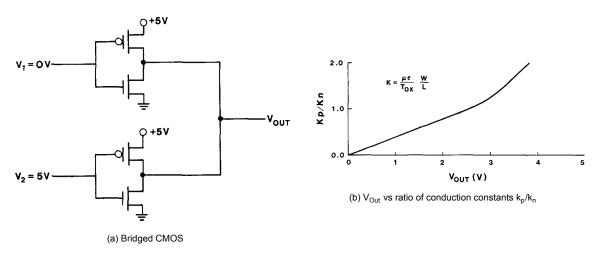

If a low resistance path occurs between logical nodes while wafer fabrication, it can introduce feedback or non-feedback configurations. A feedback can result in a latch or an oscillator, if the number of logical inversions are odd. A test set that guarantees 100% stuck at fault coverage doesn't guarantee absence of 2 bridges faults. A non-feedback bridging fault fuses outputs of two different gates. This defect can only be identified if both the gates are driven to opposite logic states. The relative transistor conduction constants of the pull-up and pull-down networks, which determine the current drive strength, determine the resultant voltage at the bridged node. The following Figure illustrates the ratio of transistor conductance constants of the two bridged CMOS inverters versus their output voltage at the bridged node [70].

Figure 2.3: Bridging Defect

#### **Time Dependent (Ageing)**

#### Electromigration

Due to the geometry of the metallic wires and the applied high electric field electrons migrate, causing voids and variations in the resistance. The voids can manifest as an open circuit and the accumulation can cause short circuits with adjacent wires. This completely alters the function of the circuit from intended behaviour. This is widely observed in Cu-Capping layer interface as it conducts the highest mass transport. Cu surface cladding can be deployed to minimize the effect. Scaling has further escalated the problem due to increase of Cu interface area in comparison to the volume. Degradation of wire due to EM depends on their geometry and current density. Unidirectional buses don't suffer from EM as they charge and discharge through the same end. Power, ground, clock and bidirectional data lines are all effected by EM [5].

#### Hot Carrier Injection

Scaling has reduced the channel length in the transistor, increasing its frequency of operation. This subsequently has led to higher electric field in the channel. Coupled along with higher voltages, this can give electrons or holes enough kinetic energy to move from substrate to gate oxide. The mechanism involved could either be impact ionisation or scattering that causes this interface state generation. The threshold of the transistor is in turn effected by this spurious injected current. Reduction of  $V_{DD}$  (operating voltage) along with LDD implants help to mitigate Hot carrier injection to an extent. Below the gate length of 50nm, the gate voltage was not reduced enough to compensate for scaling, to keep the HCI low. Emphasis on HCI will continue to increase as transistors are scaled further [39].

#### Negative Bias Temperature Instability

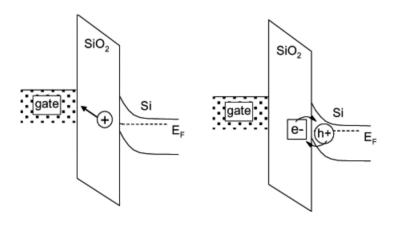

Operating voltages of devices has been reducing considerably over the decades. The electric field in the gate and operating temperature on the other hand have gone up due to higher power dissipation and lower voltage difference between  $V_T$  and  $V_{\text{Gate}}$ . These higher operating temperatures and low gate oxide thickness cause silicon hydrogen bonds in gate substrate interface to

break. These vacant silicon ions function as holes altering the threshold voltage of the transistor. Thus, transistors Inversion channel mobility decline, channel threshold voltage shift and subsequent slow down of the transistor causing timing faults over a period of time can be attributed on NBTI[52]. As a example, due to NBTI in a MOS capacitor, a positive flat band shift due to higher positive charges near Si-SiO<sub>2</sub> interface can be seen initially. Further, a negative flat band shift is obtained by exchange of charge with silicon substrate, increasing net positive charge in Si-SiO<sub>2</sub> interface [41]. These are shown in the Figure 2.4 illustrates this effect.

Figure 2.4: Effect of NBTI on MOS capacitors[41]

#### Physical/External disturbances

#### Voltage Underfeeding

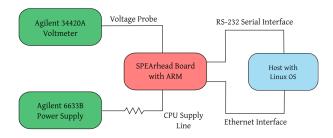

Constant voltage underfeeding causes the rise in setup time of the combinational logic to attain a stable state, which inturn effects the maximum operable clock frequency of the circuit. If the frequency is still maintained as per the normal operating conditions, while decreasing the supply voltage, proper setup of slower logic paths will fail[7]. A precision power supply such as agilent 34420A, can be used in a testbench to control the power supply of device under attack. A similar workbench was described in [8] and is shown in the Figure 2.5. This paper describes that only **LOAD** instructions are effected by this approach. This can be attributed to the fact that, **LOAD** instructions have long data paths compared to **STORE** or other arithmetic instructions. Write back buffers shorten critical paths of **STORES** and arithmetic instructions use functional units, registers that are highly optimised. All the failing loads cause bit flip down errors and no stuck at '1' errors. The result is an instruction swapping error if the **LOAD** corresponds to an instruction fetch and a data load error if its a data access. The spacial precision of the faults is limited in this approach as power is distributed all over the chip by the power distribution network. The temporal precision is also low as voltage underfeeding effect persists over multiple clock cycles [11].

Figure 2.5: Voltage Underfeeding Workbench [8]

2.1. Faults 9

#### Voltage Glitching

A temporary drop or spike in the supply voltage can cause timing violations, that can be used for an attack. Unlike voltage underfeeding, more control over the temporal location and intensity are possible in this approach. In the paper [27], voltage glitching was used to effect the bias of the generated output random numbers. Newer chips can have multiple power domains that can be effected by switching between multiple voltage levels. Faults can be injected into a particular power domain without effecting others. Attacks on controlling PC in an ARM 32 bit processor by this method was discussed in the paper [57]. A single or multiple bit corruption in the load instruction was induced to load an attacker desired value in the PC to allow execution for arbitrary code. If countermeasures are in place to prevent such attacks, the paper [45] describes a method to inject a transient timing fault by application of positive bias voltage on the substrate of MOS transistor. This application of few mV, changes the threshold voltage of transistor and introduces a local voltage pulse. This technique is referred to as Forward Body Biasing Injection (FBBI) and the platform used for this is described in the Figure 2.6.

Figure 2.6: Forward Body Bias Injection Platform [45]

#### Optical

This is the most precise and effective fault injection technique. The IC is first decapsulated from the packaging and is exposed to a light pulse. The source could be a low cost flash light or a laser beam. The latter achieves spatial precision in the order of micrometers and temporal precision in nanosecond range. Even a single transistor can be targeted by choosing the energy and duration of light pulse accordingly. On the flip side, the target chip could be permanently damaged. Shorter wavelengths are used to penetrate the metal layers if the front side of the chip is targeted. Infrared light is used to penetrate silicon substrate if backside is attacked. Multiglitching, where multiple faults are injected in a short period is also also possible. The state of the transistor, setting or clearing a single bit in memory can be manipulated, leading to faulty computations [21].

Figure 2.7: Laser Fault Injection [21]

#### Electromagnetic

By driving a high current through a coil, electromagnetic radiation as transient or harmonic pulses can be emitted, that can be used to inject faults in the target. Localised faults, that affect only a part of the chip are possible. Decapsulation of the chip as in optical faults is not required in EM attacks, though its spacial precision is comparatively lower. EM pulses induce eddy currents, which translate to faults. Injection probe's position and applied voltage determine the position and intensity of the generated EM pulse. Single bit faults in the memory can be induced by eddy currents on the surface of the chip. Errors in program flow and SRAM contents due to EM were discussed in the paper [68].

(2.8a) EM Fault Injection [68]

(2.8b) Clock Signal glitching [21]

#### (2.04) EW Facility of the

#### Clock Glitches

If an external source supplies clock to the circuit, it can be switched between a faster and slower clock. Temporarily the width of a clock pulse could be shortened by an attacker in clock glitching. This causes setup time violations and incorrect values are latched by the logic paths in the circuit. The temporal precision is very high as the clock cycle at which this glitch is introduce as well as how long the glitch is introduced can be controlled. This can translate to premature commit of the current instruction executing in a processor or capturing wrong data in registers or memories [21].

#### Temperature

Exposure to too high or too low temperatures outside the chips operating temperature range can induce faults. Overheating can induce timing violations in data path or cause bits to flip in memory cells. A focus on particular targeted portion of data is not possible. Some NVMs (Non volatile memories) have different temperature thresholds for read and write. By maintaining the temperature so that only write work and not the reads, different attack scenarios can be mounted. A laser can be used to heat a particular area of the chip, giving a high spacial precision. A high intensity light bulb or an alcoholic cooler on the other hand will offer a very low spacial precision [65][33].

The Figure 2.9 lists out the various fault injection techniques and their different characteristics.

| Fault injection technique | Characteristics of the applied physical stress |                    |      |                           |  |

|---------------------------|------------------------------------------------|--------------------|------|---------------------------|--|

|                           | Spatial precision                              | Temporal precision | Cost | Controlling the intensity |  |

| Overclocking              | Low (global)                                   | Low (global)       | Low  | Clock frequency           |  |

| Clock glitching           | Low (global)                                   | High (local)       | Low  | Glitch width              |  |

| Underfeeding              | Low (global)                                   | Low (global)       | Low  | Voltage level             |  |

| Voltage glitching         | Low (global)                                   | High (local)       | Low  | Glitch voltage            |  |

|                           |                                                |                    |      | Glitch width              |  |

| Overheating               | Low (global)                                   | Low (global)       | Low  | Ambient temperature       |  |

| Light pulse               | Medium (local)                                 | Medium (local)     | Low  | Pulse width               |  |

|                           |                                                |                    |      | Pulse energy              |  |

|                           |                                                |                    |      | Pulse offset              |  |

| Laser pulse               | High (local)                                   | High (local)       | High | Pulse width               |  |

| EM pulse                  | Medium (local)                                 |                    |      | Pulse energy              |  |

|                           |                                                |                    |      | Pulse offset              |  |

|                           |                                                |                    |      | Probe size                |  |

| DVFS interface            | Low (global)                                   | Medium (local)     | Zero | Supply voltage            |  |

|                           |                                                |                    |      | Clock frequency           |  |

| Memory disturbance        | High (local)                                   | Medium (local)     | Zero | Disturbance frequency     |  |

Figure 2.9: Fault Injection Techniques and their characteristics [11]

2.1. Faults 11

#### 2.1.2. Fault Categories

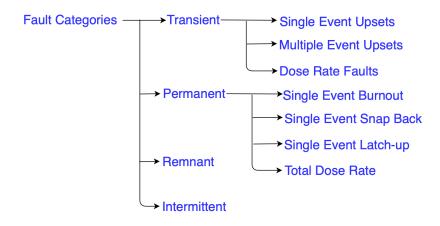

Multiple fault categories are possible based on their temporal characteristics. They are shown in the Figure 2.10. A detailed description of the faults is given in the remainder of the section.

Figure 2.10: Fault Categories

#### **Transient**

These faults can be generated by environmental conditions like cosmic rays or fault attacks like EM pulses. Their effect normally lasts only for few clock cycles and wears off as soon as the fault source ceases to exist. The effect though could propagate to software level in a processor. Original intended behaviour could be restored by a system reset [28].

#### Single Event Upsets

A single bit either in memory or registers could be flipped to a complementary state. SEUs can also manifest as variations in power supply voltage or system clock.

#### Multiple Event Upsets

If multiple SEUs occur simultaneously in the system, it is termed as MEUs. High packaging density predisposes devices to MEUs.

#### Dose Rate faults

Particles whose individual effect is negligible, but whose aggregate effect translates to a fault are categorised as dose rate faults.

#### Permanent/Destructive

Permanent faults are due to manufacturing defects, wear-out mechanisms and fault attacks, where the physical defect cannot be reversed. A fault injection technique like laser pulse can also damage a register or memory. The effect of these faults persist indefinitely. Permanent faults in a processor are more likely to effect the software, causing a system failure. They have a less likelihood of getting masked and so it should be diagnosed and the system must repaired or reconfigured to avoid the faulty unit.

#### Single event burnout

This is due to thermal runaway in MOS transistors as a result of parasitic thyristors. The entire circuit could be permanently damaged due to this [23].

#### Single event snap-back

This fault is mostly observed in devices with high supply voltage. Self sustaining currents are induced in N-channel of MOS transistors as a result of parasitic bipolar transistors.

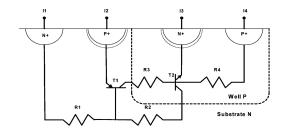

#### · Single event latch-up

A parasitic PNPN bipolar transistor can create a self sustaining current in MOS devices, that can potentially damage the device permanently. This is illustrated in the Figure 2.11.

Figure 2.11: SELs - parasitic transistors - T1 & T2

#### Total dose rate

Exposure to environment can also damage the device and induce faults. Radiation can cause effect gate potential and degrade current characteristics. As a solution, the radiation hardness of the device can be improved [60].

#### Remnant

If the configuration memory in a SRAM based FPGA is injected with a fault, the architecture of the design is altered. FPGA should be reprogrammed to get rid of the fault [20].

#### Intermittent

These faults recur at the same location non-deterministically and are present for finite number of clock cycles. The architecture vulnerability due to intermittent faults depends mostly on the fault length. Though underlying hardware defects such as device wearout and manufacturing defects are their main cause, they are not present indefinitely. They cause stuck-at and bridging faults [47].

#### 2.1.3. ISA/Software Faults

#### Instruction Replacement

When the instruction is in the pipeline of a processor and its binary encoding are corrupted during a bus transfer or when in pipeline registers, the instruction is transformed into an another instruction. This fault is called an instruction replacement fault [54]. If an assembly instruction can be skipped or if the instruction can be altered to not effect any useful register and as a result act as a **nop**, its is categorised as an instruction skip, special case of instruction replacement. These type of faults can be used by the attackers to bypass key checks in protocols like AES or RSA. Several other attack modes such as skipping a data load, backward jump, test inversion and changing a data load address are possible. The Figure 2.12 illustrates a C code and its corresponding assembly. It shows how if the jump instruction at line 9 can be replaced with a **nop**, the else condition check in the C program can be bypassed.

#### Device Reset

A complete reset of the device can be triggered by an attack like Forward Body biasing injection [45]. This completely corrupts the current state of the processor and the subroutines executed at reset or the boot loader can be exploited for an attack.

#### Data corruption

Multiple attack scenarios cause unique data corruption software faults. A clock glitch attack can cause the read of data bus even before the memory has the time to update the bus with the actual value, causing a data misread. This glitch attack particularly targets when the data is being transferred from memory to registers. When a laser is used to attack the data bus, it causes the read value to be always **255 (0xFF)** irrespective of the real read value. A voltage attack on **EEPROM** by increasing the supply voltage  $\mathbf{V}_{cc}$  to the maximum operable circuit voltage, makes

2.1. Faults 13

```

_example:

mov r2 dol // load the parameter in r2

mov a,#0x05 // put 5 into a

char example(char u)

add a,r2

// compute u + 5 in a

mov _c,a

clr c

// store c into RAM from a

char res, b;

// clear the carry

c = u + 5;

b = c < 10;

subb a,#0x0A // computes b i.e. c-10

jnc 00102$ // jumps to 102

// if carry not set (else)

if (b)

10

res = c + 1:

/* @ATTACK_ADDR1 */

// load c into a

12

mov a,_c

else {

// a++ i.e. c + 1

res = 0:

mov r2.a

// r2 stores a (res = c + 1)

14

15

sjmp 00103$ // jump over else

return res;

00102$:

mov r2,#0x00// r2 stores 0 (res = 0)

17

00103$:

18

mov dpl,r2 // push r2 on the stack

// returns

20

```

Figure 2.12: C code and its corresponding 8051 assembly [58]

the data to be read as **zero** always [28]. Attacks to alter the memory directly in register or volatile/ non-volatile memory cause a single bit or multiple bits to either flip or to be stuck at 0/1 [75].

#### · Computation error

When a Cryptographic chip, implementing AES is targeted by EM pulses, it can corrupt the computations and produce erroneous cipher texts. The circuit operation however is not halted. The paper [66] discusses this approach and cite an interesting effect of the type of the injector used. They point out that only crescent injector produces erroneous ciphers and not a flat head injector. The Figure 2.13 shows the areas on the chip that produce a computation error in cipher when attacked by EM pulses. A similar attack on smart cards can also impact the quality of the random numbers generated that are used internally[58].

Figure 2.13: EM attack on a Cryptographic chip [66]

#### 2.2. Fault Injection Techniques

Fault injection techniques were long used before fault attacks to affirm the dependability of a system. The device's behaviour is analysed when an unexpected event arises to ascertain if it is intended or not. To inject faults into a system prototype or model, various techniques have been designed and they fall into the following five categories [43]. The table 2.14 contrasts various techniques.

#### · Physical/Hardware

The fault is injected directly at the physical level by disturbing the hardware parameters like voltage, clock frequency, temperature etc. This requires detailed knowledge, physical access to the device and may require specialised equipment to inject faults [44].

#### Simulation

This is the most frequently used method. The advantages of this method include flexibility as well as not requiring the physical device. Faults are injected at high level models like a Verilog based HDL model. On the flip side, the simulation time required to simulate all the faults is impractical. Various approaches such as simulation command based, saboteurs and mutants[29].

#### Emulation

To reduce time spent in fault simulation campaigns or to avoid expensive physical testing, FPGA based fault injection techniques were proposed. This requires the initial HDL model to be synthesisable, so that it can be used to reconfigure the FPGA. Actual behaviour of the device in the application environment with respect to real time interactions can be studied[44].

#### Software

If the errors that would have been produced upon the fault occurring in the hardware are reproduced at the software level, it is termed as software based fault injection[29].

#### Hybrid

A mix of software implementation and Hardware monitoring. Software techniques mask their presence and have no effect on the system other than the fault. Hardware techniques leave a footprint while fault injection. These techniques try to balance both approaches while maximising the effectiveness of fault injection campaigns[43].

| Techniques           | Advantages                                                                                                                                                                                                                                                                                                                                                                                      | Disadvantages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware-<br>Based   | Can access locations that is hard to be accessed by other means. High time-resolution for hardware triggering and monitoring. Well suited for the low-level fault models. Not intrusive. Experiments are fast. No model development or validation required. Able to model permanent faults at the pin level.                                                                                    | Can introduce high risk of damage for the injected system. High level of device integration, multiple-chip hybrid circuit, and dense packaging technologies limit accessibility to injection. Low portability and observability. Limited set of injection points and limited set of injectable faults. Requires special-purpose hardware in order to perform the fault injection experiments.                                                                                                                                                                                                                               |

| Software-<br>Based   | Can be targeted to applications and operating systems. Experiments can be run in near real-time. Does not require any special-purpose hardware; low complexity, low development and low implementation cost. No model development or validation required. Can be expanded for new classes of faults.                                                                                            | Limited set of injection instants.     It cannot inject faults into locations that are inaccessible to software.     Does require a modification of the source code to support the fault injection.     Limited observability and controllability.     Very difficult to model permanent faults.                                                                                                                                                                                                                                                                                                                            |

| Simulation-<br>Based | Can support all system abstraction levels. Not intrusive. Full control of both fault models and injection mechanisms. Low cost computer automation; does not require any special-purpose hardware.  Maximum amount of observability and controllability. Allows performing reliability assessment at different stages in the design process. Able to model both transient and permanent faults. | Large development efforts. Time consuming (experiment length). Model is not readily available. Accuracy of the results depends on the goodness of the model used. No real time faults injection possible in a prototype. Model may not include any of the design faults that may be present in the real hardware.                                                                                                                                                                                                                                                                                                           |

| Emulation-<br>Based  | Injection time is more quickly compared with simulation-based techniques.     The experimentation time can be reduced by implementing partially or totally the input pattern generation in the FPGA. These patterns are already known when the circuit to analyze is synthesized.                                                                                                               | The initial VHDL description must be synthesizable and optimized to avoid requiring a too large and costly emulator and to reduce the total running time during the injection campaign. The cost of a general hardware emulation system and/or the implementation complexity of a dedicated FPGA based emulation board. The emulation is only used to analyze the functional consequences of a fault. When using a FPGA-based development board, the main limitation becomes the number of I/Os of the programmable hardware. Necessity of high speed communication link between the host computer and the emulation board. |

Figure 2.14: Comparison of FI techniques [29]

2.3. Fault Models

#### 2.3. Fault Models

To model the complex behaviour of a fault and its effect taking the abstraction level into consideration, a fault model is defined. If the faults are modelled at a signal level, the following fault models are conceivable [44][53].

- Stuck-at-0: The signal value is forced to be '0' due to the fault.

- Stuck-at-1: Fault forces the signal to be always 'high'.

- Stuck-open: After the retention time, the signal is forced to be 'low'.

- Bit-flip: The effect of the fault is reading the signal value and flipping it.

- Open-line: If the fault causes an open connection, the signal value can be modelled as 'high impedance' or 'Z'.

- Delay: Signal is updated to its expected value after a delay.

- Indetermination: The signal is written with a random value 'X'.

If the faults are modelled at the syntactical structure level of HDLs, they result in the following fault models[37].

- Stuck-then: An If condition is replaced by True.

- Stuck-else: An If condition is replaced by False.

- Assignment control: An assignment operation is disturbed.

- Dead process: A process is never made to execute by removing its sensitivity list.

- **Dead clause**: One of the clauses in a **Case** statement is removed.

- Micro-operation: An operator is disturbed by replacing it with an another operator.

- Local stuck-data: The value of either a signal or variable is forced to a value.

- **Global stuck-data**: All the updates to either a signal or variable are completely removed in the entire HDL description.

The following table summarizes various fault models based on different simulation based fault injection techniques.

| Injection technique | Transient           | Permanent                |

|---------------------|---------------------|--------------------------|

| Simulator           | Stuck-at (0, 1)     | Stuck-at (0, 1)          |

| Commands            | Bit-flip, Delay     | Indetermination          |

|                     | Indetermination     | Open-line, Delay         |

| Saboteurs           | Stuck-at (0, 1)     | Stuck-at (0, 1)          |

|                     | Bit-flip, Delay     | Indetermination          |

|                     | Indetermination     | Open-line, Delay, Short, |

|                     |                     | Bridging, Stuck-open     |

| Mutants             | Syntactical changes | Syntactical changes      |

Figure 2.15: Fault models for different simulation based Fault injection Techniques [37]

#### 2.4. Fault Injection Frameworks

Multiple frameworks have been proposed for different fault injection techniques, the following are widely used and thoroughly described in literature.

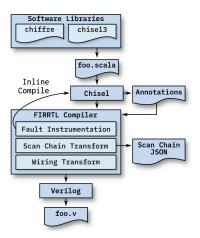

#### Chiffre

This framework can be used to instrument the design automatically while also facilitating run time injection of faults. Chisel hardware description language should be used to code the design for this framework to work. This hardware construction language(HCL) enables early stage design emulation and security verification. A circuit compiler like FIRRTL is used to read HCL based design and emit it's equivalent Verilog code after optimisation and transformations to add fault injections as well as scan chains. The fault injection is done at module level and thus the amount of user effort required for instrumentation is very low. Both registers and wires in the design can be instrumented at module and submodule level, offering high scalability for larger designs.

Figure 2.16: Chiffre: Chisel to Verilog generation and instrumentation [69]

#### · Modelsim with scripting

Modelsim is a simulation and verification tool for digital designs. This approach involves simulation based fault injection using Modelsim and script to control the simulation, which in-turn control the flow of the program. A random point in the processor such as in a register, cache memory or flip-flop are targeted at a random time with a single or multiple bit flips. Different faults such as SEU (Single event upsets), SET (Single Event Transients), MET (Multiple Event Transients) and MBU (Multiple Bit Upsets) can be propagated into the design. Of the total run time, 5% to 80% can be used for the activation of the fault and the remaining time is normally used by the processor for warm-up and to execute diagnostic routines. The paper [30] uses this methodology for fault injection in LEON3 processor and found out that integer and multiplier units are more susceptible to single and multiple faults respectively.

#### Coppelia

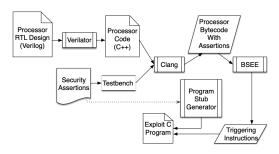

Coppelia is an end-to-end tool to find security threats of hardware vulnerabilities. The tool reads the processor design file, security critical constraint file and finds several assert statement violations. Using backward symbolic execution, a path from reset to assert failure is traced. Clock stitching is used to handle symbolic execution over multiple clock cycles. Cone of influence and search optimisations are used to generate exact sequence of instructions that trigger the assertion fail. Coppelia thus automatically generates replayable exploits with sequence of inputs to trigger a bug. Coppelia is built upon KLEE, a popular symbolic execution engine. It also uses verilator to convert the HDL based design to cycle accurate C++ code. Tool flow of Coppelia is shown in the Figure 2.17.

Figure 2.17: Workflow of Coppelia [64]

#### VerFI

A framework designed especially to inject faults into cryptographic hardware. VerFi is a simulation based fault injection tool that works on netlist of the design implementation. Fault injection can be acheived at Bit level granularity. The design could be inputted in the form of HDL or netlist, which is synthesised by either Synopsys or Yosys. The synthesizers are controlled by VerFI to not optimise redundancy, which is used as a fault countermeasure. The synthesizers also generate a configuration file, which the user could use for personalised fault injection. VerFI reads the fault configuration file along with input test vectors, simulates the design and produces coverage for the set of inputs as well as a report on the total number of generated faults. The faults are modelled in the circuit as gate level faults. Fault injection mechanism could be either hierarchical or component-wise. A event driven simulator is used, whose performance can be optimised by parallel fault simulation to use AVX2 on 256 bits, instead of bit-wise operations [75].

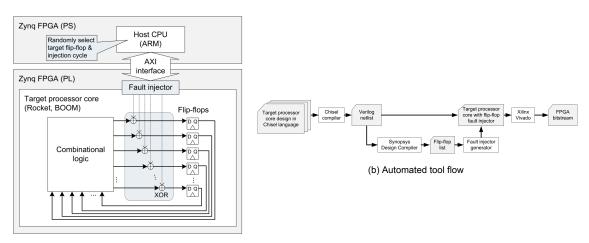

#### · Emulation based flip-flop fault injection

Designs that are created using Chisel are compiled to generate a Verilog netlist. This netlist is synthesised using Synopsys Design compiler to produce a list of flip-flops in the design. For every flip-flop in the list, a **XOR** gate is added at the data input. One of the inputs of the **XOR** gate is connected to a fault injection signal, which can be driven to flip the bit to inject the fault. This instrumented design is then ported to the programmable logic side of an FPGA. The FPGA has a host CPU on the processing system, which can be clocked as high as 50MHz. All the fault injection signals of the design are controlled by the host CPU through an AXI interface. During the fault campaign, to inject a fault, host CPU drives one of the fault injection lines that is selected randomly at a random clock cycle. After the design finishes the execution, results are collected by host CPU to classify fault effect. Silenced data corruption, unexpected termination, hang and vanished are the outcomes that are selected as they are mutually exclusive [14].

(a) Processor Emulation on Xilinx Zynq FPGA

Figure 2.18: FPGA emulation based Fault Injection Flow

#### 2.5. Countermeasures

To thwart fault injection attacks on processors and applications running on them, countermeasures implemented both in software and hardware were proposed [40]. In-order to best protect the device, a combination of both software and hardware countermeasures are used. Hardware implementations are limited by manufacturing costs and software by performance. The goal of countermeasures is to make fault injection expensive to perform, but not to prevent them completely due to aforementioned trade offs.

#### 2.5.1. Software Countermeasures

Software Countermeasures are a low cost approach as design changes in the processor are not required for their implementation, but rather a compromise in increase of execution time. They are also flexible as software can be changed to chose between various implementations. Following are some techniques and their brief description,

- Functional level temporal redundancy: Critical functions are called twice with same input data and their return data are compared for consistency [28]. This helps in fault detection, with a cost of doubling the execution time. If fault correction is desired, the function can instead be called thrice and their result be selected based on a voting logic [54]. In case of an encryption algorithm, running the decryption algorithm on the data produced and comparing the result with the input of encryption algorithm can detect faults.

- Instruction Duplication/ Triplication: The previous approach involves duplication at algorithmic level, where as this approach is at assembly instruction level. Same instruction is executed multiple times for error detection. The process can be automated by enhancing the compiler by adding compiler switches to implement the functionality [55]. Instruction duplication for a load to r4 is shown in Figure 2.19a and Instruction Triplication of xor between r1 and r2 with result stored to r4 is shown Figure 2.19b.

```

1. eor r12,r12,r12;

8. eoreq r12,r12,#2;

2. eor r10,r1,r2;

9. cmp r10,r0;

1. ldr r4,[r7];

eor r0,r1,r2;

10. eoreq r12,r12,#4;

2. ldr r12,[r7];

4. eor r4,r1,r2;

11. cmp r12,#0

3. cmp r12,r4;

5. cmp r4,r10;

12. beq <error>;

4. bne <error>;

eoreq r12,r12,#1;

13. cmp r12,#4;

7. cmp r4,r0;

14. moveq r4,r0;

(a) Instruction Duplication

```

(b) Instruction Triplication

Figure 2.19: Instruction Redundancy Techniques

- Parity Checking: Used for checking faults in data returned by load instructions. For data labelled as protected value, parity is pre-computed and stored in memory and a processor register is allocated to point to it. Later in program execution when a load instruction reads the protected value, its parity is computed and compared with pre-computed parity to determine its consistency. The drawback with this approach is that it can't be used for general purpose load and stores, it needs pre-computed parity. Storing parity is also an overhead in memory [6]. Parity check of value stored in r4 is shown in Figure 2.20a.

- Complementary Double check: Conditions that rely on protected data are often targets of attacks. A double check that's complementary should be implemented in this case, it requires the attacker to perform 2 different attacks in a short time, making a successful fault injection hard.

2.5. Countermeasures 19

```

; the push{} instruction is equivalent

7. lsr r0,r12,#1;

1. ldr r4,[r1];

2 ; to the stmdb sp!,{} instruction

2. mov r12,r4;

eor r12,r12,r0;

з stmdb sp, {r1, r2, r3, lr}

3. lsr r0,r4,#4;

9. and r12,r12,#1;

4 stmdb sp, {r1, r2, r3, lr}

4. eor r12.r12.r0:

10. ldr r6,[r7];

rx, sp, #16

5 sub

5. lsr r0.r12.#2:

11. cmp r12,r6;

6 sub

rx, sp, #16

6. eor r12,r12,r0;

12. bne <error>;

7 mov

sp, rx

8 mov

sp, rx

(a) Parity Checking

(b) Instruction Replacement Sequence

```

Figure 2.20: Algorithmic instruction level techniques

- Fault tolerant instruction sequences: To specifically protect against instruction skip attacks, which converts an instruction equivalently to a NOP. An instruction is replaced by a sequence of instructions, that are still functional if an instruction is skipped. The paper [54] implemented this for ARM thumb 2 instructions. Replacement sequences for different instruction classes were proposed. Instruction replacement sequence for push {r1,r2,r3,lr} is shown in Figure 2.20b.

- Iteration Check: Loops execute a piece of code multiple times based on a condition. They can be attacked to terminate halfway without completing the required iterations either in order to bypass checks at the end of the loop or to gain access of intermediate data. Adding a loop check code that verifies the number of iterations run by the loop once it terminates handles this fault.

- Random Code Delays: Fault injections target particular instructions in the code and assume their position in time is always fixed in any simulations. Encapsulating a sensitive function or data by calls to random delays, goes against the above assumption and is effective against temporal fault attacks [76].

- Execution flow counters: A common fault attack is to corrupt execution flow by causing a branch to a attack function and returning back. Maintaining counters that help to track which functions are taken how many times can avert this attack. Maintaining and incrementing counters to identify functions uniquely causes significant performance overhead and is not scalable to large applications.

#### **Modular exponentiation Algorithm**

The Modexp operation, mathematically represented as  $\mathbf{m^d}$  mod  $\mathbf{N}$  is used in many cryptographic algorithms such as RSA, DSA and Diffie-Hellman [26]. Algorithmically, the performance of Modexp operation determines the cryptographic systems performance. The exponent is decomposed into a base  $2^k$  number and Modexp operates on these bits from the most significant end (MSB). N-bit multiplications and reductions mod N form the critical operations in Modexp. Depending on the exponent bit, multiplications are either squarings, which are performed using faster squaring code or plain multiplications. The Modexp operations algorithm is as shown in Figure 2.21, the **if** condition can be injected with faults to corrupt the algorithm or timing difference can be used to perform a side channel attack.

```

\begin{array}{l} \text{MODEXP}(m,d,N) \\ \text{INPUT: } m,d=(d_{\ell-1}d_{\ell-2}\cdots d_1d_0),N \\ \text{OUTPUT: } m^d \bmod N \\ 1 \quad r\leftarrow 1 \\ 2 \quad \text{for } j\leftarrow \ell,\ldots,0 \\ 3 \quad r\leftarrow r^2 \bmod N \\ 4 \quad \text{if } d_j\neq 0 \\ 5 \quad r\leftarrow r\cdot m \bmod N \\ 6 \quad \text{return } r \end{array} \hspace{-0.5cm} \text{// exponent bit set?}

```

Figure 2.21: Modular exponentiation operation

#### 2.5.2. Hardware Countermeasures

Redundancy in hardware modules can be used for fault detection. Extra circuitry such as a voting logic or encoder and decoders in case of using error correcting codes can be used for fault correction. Choosing the suitable hardware countermeasure depends on the trade-off between allowable hardware overhead and level of fault/error correction required.

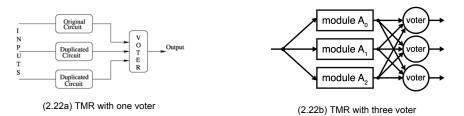

• **Triple Modular Redundancy**: This uses 2 extra ALUs and same instructions are computed on all the three ALU at the same time [49]. A majority voting logic is used to find the correct result. Fault in one processor is masked by results from other two. A configuration with single or triple voter for improved fault hardening can be used.

- Residue Code: For error detection of arithmetic operation, residue codes can be used. Since

they don't work for Boolean operations and as error correction is required, and extra ALU performing the same ALU operation on the residues, instead of data is used [74]. The original result,

modulo m and residue processor result are compared to catch a fault.

- **BCH Code**: A (63,36) BCH code can be used to encode and decode data from ALU and registers respectively to implement an ALU that can correct upto 5 faults injected at the same time [73]. Hardware overhead was experimentally shown to be **75%** of the original area, which is considerably less compared to TMR, which causes **200%** area overhead.

Figure 2.23: Fault tolerant ALU using BCH Code

• Watchdog: A watchdog processor can be used to ensure fault free data transmission between memory and the main processor [9]. The watchdog sits on the external memory bus and listens to all the transactions on the bus. Watchdog saves a shadow copy of all the writes to memory and on a read, compares its value with value returned by memory. On a mismatch a transaction is made to repeat. Control flow check is also discussed in the literature, which uses signature schemes to monitor code blocks. This can't be scaled to large real world applications. A new approach is proposed in Section 5.5.2.

# **RISC-V Processors**

#### 3.1. RISC-V

RISC-V is a reduced instruction set architecture based open ISA, which supports 32,64,128 bit data widths [13]. RISC-V is increasingly being adopted in industry and academia since it's introduction in 2010. The following factors make it more attractive compared to other ISAs:

- As it's open source and incurs no licensing costs when compared to other similar ISAs, widespread chip design and usage by various stakeholders is possible.

- Base ISA, which specifies concepts such as instruction encoding, address modes, integer arithmetic is frozen, allowing software developers to design tools such as compilers.

- Standard extensions which provide additional functionality along side with base ISAs, can be added and standardised. The new added extensions are designed to work with other existing extensions.

- High configurability of ISA allows it to be suited for various range of applications from low power to high performance with support for dedicated accelerators.

All memory accesses are byte level addressable and data is stored in little endian format in the memory. All the instructions must be aligned at 32-bit boundaries. Conditional codes for instructions other than branches are not supported as well as carry out bits to detect overflows. Three levels of privileged modes are defined, **machine**, **hypervisor and supervisor**, each with their own control & status registers.

#### 3.1.1. Instruction Set Architecture

RISC-V has a base ISA that should be present in any implementation and optional extensions can be added. The base ISA is designed to have minimum set instructions with an optional support to variable length instructions. An ISA is characterised by the width of the integer register. If the instructions are 32 bit, they should be aligned to 32 bit boundaries.

The base ISA has 32 registers and each of them have a standard function defined for them according to Application Binary Interface (ABI). ABI allows programs to access system hardware in order to ensure software interoperability. Development tool-chains refer ABI names for convenience as opposed to hard-coded register numbers. The instructions in RISC-V RV32I base ISA are shown in Appendix B.

An unusual condition at runtime due to an executing instruction is termed as an exception and is synchronously handled. The handler executes in a privileged environment. An interrupt on the other hand, is due to an external event and occurs asynchronously to the executing instruction. Four core instructional formats are possible, namely R/I/S/U, shown in Figure 3.1.

22 3. RISC-V Processors

| 31    | 25              | 24 20     | 19  | 15 14 | 12 11 | 7      | 6      | 0      |

|-------|-----------------|-----------|-----|-------|-------|--------|--------|--------|

| func  | t <b>7</b>      | rs2       | rs1 | funct | 3 1   | rd     | opcode | R-type |

|       |                 |           |     |       |       |        |        |        |

| :     | $_{ m imm}[11:$ | 0]        | rs1 | funct | 3 1   | rd     | opcode | I-type |

|       |                 |           |     |       | •     |        |        |        |

| imm[1 | 1:5]            | rs2       | rs1 | funct | 3 imn | n[4:0] | opcode | S-type |

|       |                 |           |     |       | •     |        |        |        |

|       |                 | imm[31:12 | ]   |       | 1     | rd     | opcode | U-type |

Figure 3.1: RISC-V Base Instruction Formats

The base ISA is integer instruction set with 32-bit(RV32I), 64-bit(RV64I), 128-bit(RV128I) data width specifications defined. Multiple extensions to base ISAs are possible and some frequently used ones are described below [42],

- · M Addition of a Multiply or Divide unit.

- F To include a Single point precision floating point unit.

- · D To add a Double precision floating point unit.

- · A Support for atomic operations.

- · C Compressed ISA.