**Delft University of Technology**

## **Risotto**

## A Dynamic Binary Translator for Weak Memory Model Architectures

Gouicem, Redha; Sprokholt, Dennis; Ruehl, Jasper; Rocha, Rodrigo C.O.; Spink, Tom; Chakraborty, Soham; Bhatotia, Pramod

DOI

10.1145/3567955.3567962

Publication date 2022

**Document Version** Final published version

## Published in

ASPLOS 2023 - Proceedings of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems

### Citation (APA)

Gouicem, R., Sprokholt, D., Ruehl, J., Rocha, R. C. O., Spink, T., Chakraborty, S., & Bhatotia, P. (2022). Risotto: A Dynamic Binary Translator for Weak Memory Model Architectures. In T. M. Aamodt, N. E. Jerger, & M. Swift (Eds.), *ASPLOS 2023 - Proceedings of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems* (pp. 107-122). (International Conference on Architectural Support for Programming Languages and Operating Systems - ASPLOS). ACM. https://doi.org/10.1145/3567955.3567962

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

#### Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

#### Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

## 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

Jasper Ruehl

TU Munich

Germany

jasper.ruehl@tum.de

Soham Chakraborty

TU Delft

Netherlands

s.s.chakraborty@tudelft.nl

# **Risotto: A Dynamic Binary Translator for Weak Memory Model Architectures**

Redha Gouicem\* TU Munich Germany gouicem@in.tum.de

Rodrigo C. O. Rocha University of Edinburgh UK rrocha@ed.ac.uk Dennis Sprokholt\* TU Delft Netherlands d.g.sprokholt@tudelft.nl

Tom Spink University of St Andrews UK tcs6@st-andrews.ac.uk

Pramod Bhatotia TU Munich Germany pramod.bhatotia@tum.de

#### ABSTRACT

Dynamic Binary Translation (DBT) is a powerful approach to support cross-architecture emulation of unmodified binaries. However, DBT systems face correctness and performance challenges, when emulating *concurrent binaries from strong to weak memory consistency architectures.* As a matter of fact, we report several translation errors in QEMU, when emulating x86 binaries on Arm hosts.

To address these challenges, we propose an end-to-end approach that provides correct and efficient emulation for weak memory model architectures. Our contributions are twofold: First, we formalize QEMU's intermediate representation's memory model, and use it to propose formally verified mapping schemes to bridge the *strong-on-weak memory consistency mismatch*. Second, we implement these verified mappings in Risotto, a QEMU-based DBT system that optimizes memory fence placement while ensuring correctness. Risotto further improves performance via cross-architecture dynamic linking of native shared libraries and faster yet correct translation of compare-and-swap operations.

We evaluate Risotto using multi-threaded benchmark suites and real-world applications, and show that Risotto improves the emulation performance by 6.7% on average over "erroneous" QEMU, while ensuring correctness.

\*The first two authors contributed equally to this work.

ASPLOS '23, March 25-29, 2023, Vancouver, BC, Canada

## **CCS CONCEPTS**

• Software and its engineering → Just-in-time compilers; Formal software verification; Simulator / interpreter; • Hardware → Simulation and emulation.

#### **KEYWORDS**

Binary translation, memory models, formal verification

#### **ACM Reference Format:**

Redha Gouicem, Dennis Sprokholt, Jasper Ruehl, Rodrigo C. O. Rocha, Tom Spink, Soham Chakraborty, and Pramod Bhatotia. 2023. Risotto: A Dynamic Binary Translator for Weak Memory Model Architectures. In *Proceedings* of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 1 (ASPLOS '23), March 25–29, 2023, Vancouver, BC, Canada. ACM, New York, NY, USA, 16 pages. https://doi.org/10.1145/3567955.3567962

#### **1** INTRODUCTION

With the emergence of new Instruction Set Architectures (ISAs) like Arm or RISC-V, the landscape of computing hardware is steadily shifting in the recent years [13, 38]. Major industry players are moving away from the currently dominating x86 to favor new features, performance, power efficiency, and license support [16, 32, 77]. However, this transition is not straightforward since existing applications are not compatible across different ISAs. To address this problem, DBT technology emulates the program's *guest* ISA on the *host* machine, by translating the code at run time [71, 80].

A major challenge for DBT systems is correct and performant emulation of concurrent binaries [28, 53]. The root cause of this issue is the mismatch in the memory model semantics between the guest and the host architectures, which is particularly problematic when translating from a strong memory model, *e.g.*, x86, to a weaker model, *e.g.*, Arm [6]. At a high-level, the DBTs must ensure that the behavior of the guest ISA is correctly reproduced on the host machine so that the application's original semantics are preserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

<sup>© 2023</sup> Copyright held by the owner/author(s). Publication rights licensed to ACM. ACM ISBN 978-1-4503-9915-9/23/03...\$15.00 https://doi.org/10.1145/3567955.3567962

In order to correctly support *strong-on-weak memory consistency* [90], DBTs must insert *memory fences* to preserve guest orderings, sacrificing performance [51]. For example, QEMU [71], a stateof-the-art DBT, tries to enforce a stronger ordering than x86's when emulating it on Arm, unnecessarily hurting performance. Despite its attempt at enforcing strong ordering, it fails to ensure correctness we discover and report several translation errors in QEMU due to incorrect fence usage that may lead to errors at run time. Further, while reasoning about mapping correctness, we discover and report that the Arm memory model [6] does not facilitate optimal mapping as it requires additional fences in x86 to Arm translation.

Moreover, the runtime performance is paramount for the adoption of DBT systems. Many user-mode DBT systems translate the entire application up to the system call interface, and fail to take advantage of pre-compiled host instructions where available. For instance, commonly used shared libraries are often present in the host system, however QEMU, instead of using the native and highly optimized version of the library, translates a guest version of the shared library function to the host ISA.

In this paper, we propose an end-to-end DBT approach based on QEMU that provides correct and efficient execution of concurrent x86 binaries on Arm architectures by combining: (a) formal verification of translation correctness for strong-on-weak architecture, and (b) a DBT system for run time binary translation based on these verified translation rules.

More specifically, on the formal verification aspect, we propose the *first formal concurrency memory model* of QEMU's intermediate representation (TCG IR). We use our formalization to offer verified mapping schemes, proving the correctness of (1) x86 to TCG IR and (2) TCG IR to Arm mapping schemes. We develop these correctness proofs using the Agda theorem prover [4].

Another aspect of QEMU's Tiny Code Generator (TCG) is the intermediate optimizations on the concurrency primitives, which may affect the translation correctness, as all transformation for sequential programs may be not be correct for concurrent programs [25, 59, 86]. Hence, only ensuring the memory model mismatches in architectures [28, 53] does not guarantee correct translation in QEMU. Therefore, we prove the correctness of a number of optimizations, including the ones performed by TCG. These verified optimizations, along with verified mappings, facilitate the development of an end-to-end DBT system based on QEMU.

On the system side, we build Risotto, a QEMU-based DBT system that implements these verified translation rules for mappings and optimizes fence placement. Risotto further enhances the emulation performance via a cross-architecture dynamic linker that uses native shared libraries whenever available, instead of translating their guest counterpart. In addition, Risotto leverages recent Arm atomic instructions to efficiently and correctly translate Compareand-Swap (CAS) operations.

We evaluate Risotto on the PARSEC [19] and Phoenix [72] benchmark suites, as well as various real-world applications such as OpenSSL and SQLite. Our evaluation shows that Risotto improves performance whilst still being correct with regards to memory ordering by up to 19.7%, and 6.7% on average compared to "erroneous" QEMU. We also show that our dynamic linker allows applications using shared libraries to match the speed of native applications using these libraries. Overall, our paper makes the following contributions:

- Concurrency analysis in QEMU and Arm memory model. We discover and report several translation errors in QEMU due to the incorrect usages of memory fences. We also report *undesired behavior* in the Arm memory model (herein referred to as Arm-Cats) for efficient x86-to-Arm translation [6], and propose revisions to the model for verified mappings. These revisions were accepted in the Arm-Cats model [39].

- TCG IR memory model: Formalization, verified mappings and optimizations. We formalize QEMU'S TCG IR. Based on this formal model, we propose mapping schemes from x86 to TCG IR and TCG IR to Arm, which we verify to be semantically correct. We also prove the correctness of various optimizations on TCG IR model which are performed by QEMU. These mapping schemes have been submitted to the QEMU mailing list and are under review at the time of writing.

- **Risotto DBT system.** We build Risotto, an end-to-end DBT system that is based on the formally verified translations on QEMU. In addition, we implement a dynamic host library linker, which allows to match the speed of native execution when using native shared libraries instead of translated libraries. Lastly, we implement a fast and correct translation of CAS operations.

#### 2 BACKGROUND

#### 2.1 Weak Memory Model Architectures

Concurrency is often interpreted as an interleaving of operations performed by multiple threads, with the operations in each thread executing in program order. This is known as Sequential Consistency (SC) [44]. However, concurrent systems may also behave in ways that cannot be explained by interleaving semantics. These non-SC behaviors result in weak memory models.

Weak memory models arise in some architectures due to various microarchitectural design decisions, *e.g.*, the memory hierarchy, or out-of-order execution. Therefore, memory models may vary among different ISAs, *e.g.*, x86 and Arm. The example below shows how the allowed behaviors for a program may vary depending on the memory model.

| V V O            |      | Shared variables <i>X</i> and <i>Y</i> are initialized |

|------------------|------|--------------------------------------------------------|

| X = Y = 0;       |      | to zero. The program has two concurrent                |

| X = 1;    a = Y; | (MP) | threads. Weak outcome $a = 1, b = 0$ is                |

| Y = 1;    b = X; |      | allowed in Arm but disallowed in x86.                  |

**Implication on binary translation.** If we translate the MP program's binary from x86 to Arm, without taking their memory models into account, the resulting Arm binary may exhibit undesirable behaviors. This incorrectness is due to the different memory consistency models between the source and destination ISAs. It can be fixed by explicitly enforcing the memory model of the source ISA when translating into the destination ISA via memory fences. However, the introduction of additional fences has a significant impact on performance [51].

#### 2.2 Dynamic Binary Translation

DBT systems typically operate as follows: (1) translate the instruction currently pointed at by the emulated Instruction Pointer (IP), and (2) execute the translated instruction, updating the IP to either the following instruction or the target of a jump. Most DBTs implement translation granularities of at least a *basic block*, and employ classic compiler optimizations to improve generated code quality (and hence run time performance). Basic blocks are often cached to avoid repeating translations.

QEMU is a state-of-the-art emulator capable of cross-ISA emulation that supports two operation modes: full system or user mode. Full system mode emulates the entire machine while user mode only emulates applications. In the latter, system calls are natively executed by the host machine and not emulated. In this paper, we focus on user-mode QEMU.

Shared libraries support. QEMU treats the application binary and any shared libraries as a unit, translating both guest application code and guest library code on-the-fly. This requires a guest version of the shared library to be available for the application to function correctly. However, since many shared libraries are common across platforms, some libraries used by guest applications will also be available on the host system in native form. A classic example is the GNU C Library (glibc), which is used by most applications. This means that QEMU translates functions from the guest glibc, while a native and optimized version is almost certainly available.

#### 2.3 TCG: QEMU's Dynamic Binary Translator

QEMU translates code through its TCG. Basic blocks are translated via an intermediate representation (IR) called the TCG IR. Architecture-independent optimizations are also applied on the basic blocks at the IR level.

**TCG IR.** The TCG IR is an assembly-like instruction set. It contains basic arithmetic, logic, and control flow instructions. However, floating-point arithmetic is emulated via integer-based computations.

**Memory fences.** The TCG IR provides fences for all types of pairs of accesses. For example, the Fww fence orders a store-store pair, while Frw orders a load-store pair. When generating fences in the IR, TCG takes the guest memory model into account to choose the fence accordingly. Section 3 provides a more detailed discussion.

Atomic read-modify-write (RMW). RMW accesses are currently translated into calls to helper functions in QEMU. Therefore, even if the host ISA has an equivalent atomic instruction, execution is still transferred from the emulated binary to QEMU. We discuss these primitives in Section 5.

**Optimizations.** TCG performs various optimizations on the translated basic blocks at the IR level. Some of the well-known optimizations are dead code elimination, constant propagation and folding, consecutive fence merging, etc.

#### 2.4 Concurrency Primitives in Architectures

We categorize the concurrency primitives as follows: (1) load accesses that read from shared memory, (2) store accesses that write to shared memory, (3) RMW accesses that atomically update shared memory, and (4) fence operations that order memory accesses. Figure 1 lists the concurrency primitives from x86, Arm and TCG IR used in the mapping schemes discussed in this paper.

**Load and store accesses.** Most instructions in x86 can perform a memory access, so we denote the underlying x86 load and store

| Access type            | x86    | TCG IR | Arm                                                   |

|------------------------|--------|--------|-------------------------------------------------------|

| Load                   | RMOV   | ld     | LDR                                                   |

| Store                  | WMOV   | st     | STR                                                   |

| Full-fence             | MFENCE | Fsc    | DMBFF                                                 |

| WW-fence               |        | Fww    | DMBST                                                 |

| RM-fence               |        | Frm    | DMBLD                                                 |

| MW fence               |        | Fmw    |                                                       |

| Atomic-update          | RMW    | RMW    | $\mathbb{R}M\mathbb{W}^1$ , $\mathbb{R}M\mathbb{W}^2$ |

| Rel.Acq. atomic-update |        |        | $\mathbb{RMW}_{AL}^1$ , $\mathbb{RMW}_{AL}^2$         |

$\mathbb{RMW}^2 \triangleq \ell$ : LX; cmp; bc  $\ell'$ ; SX; bc  $\ell$ ;  $\ell'$ :

$\mathbb{RMW}_{A}^{2} \triangleq \ell$ :  $LX_{A}$ ; cmp; bc  $\ell'$ ; SX; bc  $\ell$ ;  $\ell'$ :

$\mathbb{RMW}_{L}^{2} \triangleq \ell : LX; \text{ cmp; bc } \ell'; SX_{L}; \text{ bc } \ell; \ell':$

$\mathbb{RMW}_{\mathsf{A}\mathsf{I}}^2 \triangleq \ell : \ \mathsf{LX}_\mathsf{A}; \ \mathsf{cmp}; \ \mathsf{bc} \ \ell'; \ \mathsf{SX}_\mathsf{L}; \ \mathsf{bc} \ \ell; \ \ell':$

# Figure 1: Concurrency primitives in x86, TCG IR, and Arm which are used in the mapping schemes.

operations as RMOV and WMOV. In Arm, LDR and STR perform the load and store operations.

In x86, RMOV-RMOV, RMOV-WMOV, WMOV-WMOV access pairs are always executed in order. In Arm, independent LDR and STR accesses on different locations may execute out-of-order.

**Fence operations.** The full fences in x86 and Arm are MFENCE and DMBFF respectively, which order any memory access pair. Arm also has lightweight fences, *e.g.*, DMBLD orders a read operation with its successors and DMBST orders a pair of writes.

RMW **accesses.** Both x86 and Arm provide various types of RMW primitives. x86 has the LOCK CMPXCHG instruction. Arm provides two types of RMW primitives that we denote by RMW<sup>2</sup> and RMW<sup>1</sup>.

$\mathbb{RMW}^2$  is constructed from load-exclusive (LX) and store-exclusive (SX). Arm also provides acquire-load-exclusive (LX<sub>A</sub>) and releasestore-exclusive (SX<sub>L</sub>) instructions. A release access is ordered with its predecessors and an acquire is ordered with its successors. We can construct  $\mathbb{RMW}^2$ ,  $\mathbb{RMW}^2_A$ ,  $\mathbb{RMW}^2_L$ ,  $\mathbb{RMW}^2_{AL}$  primitives with these instructions as shown in Figure 1.  $\mathbb{RMW}^1$  denotes the single-instruction  $\mathbb{RMW}$  instructions [6, 12]. Similar to  $\mathbb{RMW}^2$ ,  $\mathbb{RMW}^1$  accesses can also have release/acquire combinations as shown in Figure 1.

In x86, a successful RMW acts as a full fence whereas in Arm, only a successful  $RMW_{A1}^1$  acts as a full fence.

#### **3 MOTIVATION**

In this section, we expose correctness and performance problems that arise when QEMU emulates concurrency. We also expose an error in an existing Arm mapping.

#### 3.1 Emulation of Concurrent Programs in QEMU

QEMU does not officially support the emulation of strongly ordered ISAs, *e.g.*, x86, on weakly ordered ones, *e.g.*, Arm. However, in user mode emulation, the program runs without triggering any warning or error message to users, who can therefore think that support is available.

**QEMU mapping schemes.** Figure 2 shows QEMU's mapping schemes for translating memory-related x86 instructions to Arm. An Fmr

| x86    |               | TCG IR   |               | Arm           |

|--------|---------------|----------|---------------|---------------|

| RMOV   | $\rightarrow$ | Fmr; ld  | $\rightarrow$ | DMBLD; LDR    |

| WMOV   | $\rightarrow$ | Fmw; st  | $\rightarrow$ | DMBFF; STR    |

| RMW    | $\rightarrow$ | call     | $\rightarrow$ | BLR; RMW; RET |

| MFENCE | $\rightarrow$ | $F_{sc}$ | $\rightarrow$ | DMBFF         |

Figure 2: QEMU mappings: x86 to Arm via TCG IR.

fence is inserted before loads (RMOV), ordering the load with its preceding memory access. Since store-load reordering is allowed in x86, TCG demotes this fence to Frr, only ordering the load with a preceding load. This is an attempt to match the x86 memory model. An Fmw fence is inserted before stores (WMOV), ordering the store with its preceding memory access. These fences are then lowered to Arm's DMBLD and DMBFF fences.

RMW **operations**. QEMU translates RMW operations as calls to helper functions. These helper functions rely on GCC built-ins for the atomic accesses. As a result, depending on the GCC version, the instructions differ. For example, the helper function emulating the x86 CMPXCHG instruction uses an ldaxr-stlxr pair ( $\text{RMW}_{AL}^2$ ) with GCC 9, but a casal instruction ( $\text{RMW}_{AL}^1$ ) with GCC 10. Both are correct from GCC's standpoint since they both comply with the C/C++ memory model. However, this leads to inconsistencies for the x86 model.

#### 3.2 Correctness: Errors in QEMU

We found several errors in QEMU'S x86 to Arm translation, more specifically in handling RMW access (both RMW<sup>1</sup> and RMW<sup>2</sup>). We demonstrate these errors by the translations of the MPQ and SBQ programs where RMW<sup>1</sup> and RMW<sup>2</sup> accesses are generated respectively.

We also show that the usage of  $F_{\rm MR}$  fence in TCG IR may also result in an erroneous RAW transformation as demonstrated by the translation of the FMR program.

**Error in mapping scheme with**  $\mathbb{RM}^1_{AL}$ . Consider the x86 to Arm mapping by QEMU for the following program.

$$\begin{array}{ll} X = Y = 0; & X = Y = 0; \\ X = 1; \\ Y = 1; \\ \end{bmatrix} \begin{array}{ll} a = Y; & & X = 1; \\ \mathbf{if} (a = = 1) & & X = 1; \\ \mathbf{RMW}(X, 1, 2); & & Y = 1; \\ \end{array} \begin{array}{ll} \mathsf{DMBFF}; \\ \mathsf{DMBFF}; \\ \mathsf{if} (a = = 1) \\ \mathsf{RMW}_{\mathsf{AL}}^1(X, 1, 2); \end{array} \right. \tag{MPQ}$$

In x86, a = 1 implies that all writes in the first thread are completed. Since reads are not reordered, the RMW always reads the X = 1 and successfully updates X = 2. As a result a = 1, X = 1 is never possible. In Arm, however, a read and a read-acquire pair can be reordered. This means that even though the first thread's writes are ordered by fences, the read of  $\text{RMW}_{AL}^1$  can be speculatively executed before the a = Y instruction as they are unordered. In that case, the  $\text{RMW}_{AL}^1$ will not observe X = 1 and fail, but the result will still be committed after a = Y sets a to 1. It results in the outcome a = 1, X = 1, which is disallowed in x86, hence an incorrect translation. R. Gouicem, D. Sprokholt, J. Ruehl, R. Rocha, T. Spink, S. Chakraborty, and P. Bhatotia

| x86    |               | Arm                       |

|--------|---------------|---------------------------|

| RMOV   | $\rightarrow$ | LDRQ                      |

| WMOV   | $\rightarrow$ | STRL                      |

| RMW    | $\rightarrow$ | $RMW_{AL}^{\overline{1}}$ |

| MFENCE | $\rightarrow$ | DMBFF                     |

Figure 3: Intended Arm mappings of Arm-Cats [6].

**Error in mapping scheme with**  $\text{RMW}_{AL}^2$ . Consider the following x86 to Arm translation.

$$\begin{split} X &= Y = Z = U = 0; \\ X &= Y = Z = U = 0; \\ X &= 1; \\ \text{RMW}(Z, 0, 1); \\ a &= Y; \end{split} \begin{vmatrix} Y &= 1; \\ \text{RMW}(U, 0, 1); \\ b &= X; \\ a &= Y; \end{vmatrix} \begin{vmatrix} \text{DMBFF}; \\ X &= 1; \\ \text{RMW}^2_{AL}(Z, 0, 1); \\ \text{DMBLD}; \\ a &= Y; \end{vmatrix} \begin{vmatrix} \text{DMBFF}; \\ Y &= 1; \\ \text{RMW}^2_{AL}(U, 0, 1); \\ \text{DMBLD}; \\ b &= X; \end{vmatrix}$$

The behavior in question is Z = U = 1, a = b = 0. In x86, successful RMW accesses order store-load access pairs in the executions. On the other hand, neither successful  $\text{RMW}_{AL}^2$  accesses nor DMBLD fences can order the store-load access pairs. Thus, the mapping results in a new outcome in the generated Arm program and, therefore, the overall translation is incorrect.

Error in RAW transformation in TCG IR. QEMU performs various constant propagation optimizations on TCG IR such as read-after write (RAW), e.g., Y = 2; a = Y;  $\rightarrow Y = 2$ ; a = 2;. We note that in the presence of Fmr, the RAW transformation is incorrect as it introduces a new outcome. Consider the following example.

$$\begin{array}{ll} X = Y = Z = 0; & X = Y = Z = 0; \\ X = 3; \\ Fmr; \\ Y = 2; \\ a = Y; \\ Frw; \\ Z = 2; \end{array} \middle| \begin{array}{ll} \text{if} (Z == 2) \left\{ & Fmr; \\ Frw; \\ X = 4; \\ c = X; \\ Frw; \\ Z = 2; \end{array} \middle| \begin{array}{ll} \text{if} (Z == 2) \left\{ & Fmr; \\ Fmr; \\ X = 4; \\ c = X; \\ Frw; \\ Z = 2; \end{array} \right| \begin{array}{ll} \text{if} (Z == 2) \left\{ & Fmr; \\ Fmr; \\ X = 4; \\ c = X; \\ Frw; \\ Z = 2; \end{array} \right|$$

Consider the outcome a = 2, c = 3. In the source TCG program, the Fmr and Frw fences in the first thread establish dependency-based ordering from X = 3 to Z = 2 via a = Y. In the second thread, Frw orders the read of Z with the successor accesses on X. As a result, the outcome a = 2, c = 3 is disallowed. The RAW transformation in the first thread remove the read of Y and hence X = 3 and Z = 2 are not ordered anymore. As a result, the a = 2, c = 3 outcome is allowed in target program, making the RAW transformation incorrect.

## 3.3 Correctness: Error in "Desired" Arm Mapping

We consider the x86 to Arm-Cats mapping [6]. While the authors do *not* explicitly give a mapping, we infer:

- LDAPR (LDR<sub>Q</sub>) and STLR (STR<sub>L</sub>) enable efficient emulation of x86-TSO on Arm-Cats [6, p.6]

- amo in Arm-Cats exclusively models RMW<sup>1</sup><sub>AL</sub>, e.g., casal, which should act as a full barrier [6, p.18].

- In x86, a successful RMW also behaves like a full barrier [6, 64].

We interpret their intended mapping as given in Figure 3.

ASPLOS '23, March 25-29, 2023, Vancouver, BC, Canada

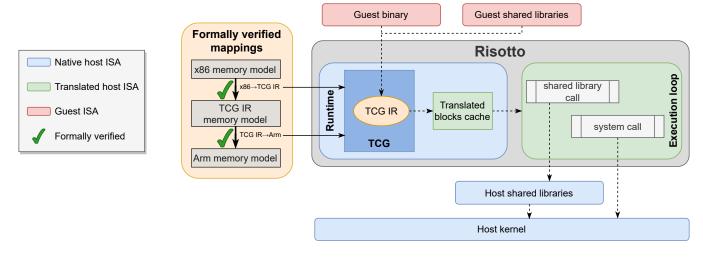

Figure 4: Overall architecture of Risotto.

While examining that mapping, we discover that it is incorrect following the memory models [6]. Consider the following example:

$$\begin{array}{l} X = Y = 0; & X = Y = 0; \\ \mathbb{RMW}(X, 0, 1); & \left\| \begin{array}{l} \mathbb{RMW}(Y, 0, 1); \\ a = Y; \end{array} \right\| \begin{array}{l} \mathbb{RMW}(Y, 0, 1); \\ b = X; \\ \end{array} \xrightarrow{} \left\| \begin{array}{l} \mathbb{RMW}_{AL}^{1}(X, 0, 1); \\ b = X_{Q}; \\ \end{array} \right\| \begin{array}{l} \mathbb{RMW}_{AL}^{1}(Y, 0, 1); \\ b = X_{Q}; \\ \end{array} \right\| \begin{array}{l} \mathbb{RMW}_{AL}^{1}(Y, 0, 1); \\ \end{array} \right\| \left\| \begin{array}{l} \mathbb{RMW}_{AL}^{1}(Y, 0, 1); \\ \mathbb{RMW}_{AL}^{1}(Y, 0, 1); \\ \end{array} \right\| \left\| \begin{array}{l} \mathbb{RMW}_{AL}^{1}(Y, 0, 1); \\ \mathbb{RMW}_{AL}^{1}(Y, 0, 1); \\ \mathbb{RMW}_{AL}^{1}(Y, 0, 1); \\ \mathbb{RMW}_{AL}^{1}(Y, 0, 1); \\ \mathbb{RW}_{AL}^{1}(Y, 0, 1); \\ \mathbb{RW}_{A$$

The source x86 program *disallows* X = Y = 1, a = b = 0 as outcome, while the Arm program *allows* it. Therefore the mapping is erroneous.

**Fixing this error.** There are two options to fix this error in the model:

- Keep the current formal model and accept casal is insufficient to model x86 RMW.

- Strengthen the formal model slightly, so casal behaves like x86 RMW.

We choose the second option that we detail in Section 5. We hypothesize that hardware may already be consistent with our model. We contacted the authors of Armed Cats, but they could not confirm hardware behavior with regards to our SBAL example in the new model. However, they still decided to strengthen the memory model like we proposed [39].

## 3.4 Performance: Fence and Shared Library Issues

**Fence placement.** QEMU's mapping schemes in Figure 2 prevent any reordering of memory accesses, even though the guest ISA (x86) allows some reorderings to happen. However, the CPU performs these reorderings to maximize its utilization. Not taking advantage of the CPU's instruction scheduling hurts performance. Additionally, having fences *before* every access makes it impossible to merge them.

**Shared library.** QEMU translates shared library functions from guest to host ISA, even when these same functions already exist on the host system in a native shared library. In general, translated code

is less performant than natively compiled code, because the translation engine is unable to achieve the same level of optimization as the native compiler, when compiling from source code. Therefore, using pre-compiled native code when available, *i.e.*, the native version of a shared library, will lead to significant performance gains for guest programs that rely heavily on shared libraries.

#### **4 OVERVIEW**

We propose an end-to-end approach to improve the performance of strong-on-weak architecture DBT while maintaining semantic correctness.

## 4.1 Verified Mapping Schemes and Optimizations

We reason about the end-to-end translation steps: (1) x86 to TCG IR mapping (2) TCG IR to TCG IR optimization (3) TCG IR to Arm mapping.

**TCG IR formalization.** To reason about these steps formally, we use existing formal models of x86 and Arm [6], and propose a formalization of TCG IR. Based on this formalization, we ensure the correctness of the translations in all three steps.

**Mappings in steps (1) & (3).** We map the load, store, RMW, and fence accesses from the source to the corresponding accesses in the target models. The orderings between the accesses vary based on the consistency models. To ensure orderings between weaker accesses, we introduce additional leading or trailing fences along with the memory accesses. As fences are costly, our goal is to introduce only the minimal fences that are required to ensure correctness.

Moreover, we note that some TCG optimizations may perform read-after-write (RAW) transformations, which can introduce errors in the presence of Fmr or Fwr fences (see FMR example). Hence, we avoid generating any Fmr or Fwr fence in the x86 to TCG IR mapping scheme so that RAW transformations remain correct on the generated TCG IR programs.

R. Gouicem, D. Sprokholt, J. Ruehl, R. Rocha, T. Spink, S. Chakraborty, and P. Bhatotia

Using all three formal models, we formally prove the correctness of the mapping schemes. These new schemes use minimal fences to preserve correctness.

**IR transformations in step (2).** Risotto performs several optimizations on the TCG IR before generating the Arm code. To ensure their correctness, we analyze the common transformations performed on the concurrency primitives. We show that the proposed TCG IR formalization allows the transformations performed by Risotto's optimizations.

More specifically, we reason about elimination of redundant shared memory accesses and reordering of shared memory accesses. We also reason about fence merging optimizations which can be performed when there are adjacent fences. Our x86 to TCG IR mapping scheme creates such adjacent fences which can be merged to improve performance as shown in Section 7.

## 4.2 Risotto: A Dynamic Binary Translator for Strong-on-Weak Architectures

We build Risotto upon the widely used emulator QEMU. We improve over the existing work through three contributions: (*i*) the implementation of formally verified memory mappings, (*ii*) a dynamic linker that uses host shared libraries instead of guest libraries, and (*iii*) a fast and correct translation of CAS instructions. Figure 4 shows the overall architecture of Risotto.

**Memory mappings.** We first replace the memory mapping schemes used by QEMU with our schemes presented in Section 5, which are formally verified to enforce the x86 memory model [6, 64, 65]. We implement this in the TCG shown in Figure 4, where the TCG IR code is generated. We also implement fence merging optimizations at the TCG IR level to minimize the cost of inserted fences.

**Dynamic host linker.** QEMU uses guest shared libraries that are translated to the host ISA. Since translated code is less efficient than native host code, maximizing the amount of native code used is a good way to improve performance. In Risotto, we target shared libraries to expand the amount of native code used because of their unique properties.

First, similar to system calls, they provide a clearly defined API to programs, which makes it possible to correctly marshal arguments and return values between guest and host ISAs. Second, even if a binary is only available for the guest ISA, the shared libraries that it uses may be available on the host ISA.

In Risotto, we implement a dynamic linker that connects invocations of shared library functions to native host shared libraries, instead of translating guest shared libraries (§ 6.2).

**Fast and correct CAS.** As previously stated, RMW primitives are emulated through a call to a helper function in QEMU and not translated. In addition to the performance hit, this can also trigger erroneous behaviors.

In Risotto, we aim at preserving correctness while maximizing performance. For atomic operations, we propose to translate the x86 atomic instructions, *e.g.*, CMPXCHG, directly into Arm assembly, *e.g.*, using the new casal instructions. This allows us to fix the errors in QEMU's current scheme as well as improve performance. We also implement this in the TCG (§ 6.3).

#### 5 TCG IR CONCURRENCY MEMORY MODEL

In this section, we propose an axiomatic concurrency model for the TCG IR. Based on this model, we propose formally verified mapping schemes from x86 to Arm via the TCG IR.

#### 5.1 Axiomatic Model for Concurrency

In axiomatic semantics, a program is represented by a set of finite executions where an execution constitutes of a set of events and relations. An event is generated from the execution of a shared memory access or a fence and the events are related by various relations. We can represent an execution as a graph where the nodes represent events and edges represent relations [6, 10, 18, 43].

The set of read, write, and fence events are R, W, and F respectively. The events are connected by various relations.

**Notations.** To define the formal models we use relation and set notations (similar to 'cat' notations [8]). Given a binary relation *S* on events, dom(*S*) and codom(*S*) are domain and range of *S*. We compose binary relations  $S_1$  and  $S_2$  by  $S_1$ ;  $S_2$ . [*A*] is an identity relation on a set *A*. Finally, on an execution graph, relation *S* is acyclic if  $S^+$  (transitive closure of *S*) is irreflexive.

**Relations.** The events are primarily connected by program-order (po), reads-from (rf), coherence-order (co) relations. Relation po is a strict partial order that captures the syntactic order among the events, rf relates a pair of write and read events on same-location having same values, and co is a strict total order on same-location write events. We compose these relations to derive new ones.

- Relation from-read (fr  $\triangleq$  rf<sup>-1</sup>; co) relates a read and write events r and w on same-location (rf<sup>-1</sup> is inverse of rf). In this case, w is co-after the write u where rf(u, r) holds.

- A relation is external when it is not between po-related events, *e.g.*, external rf, co, fr relations are:

$$\mathsf{rfe} \triangleq \mathsf{rf} \setminus \mathsf{po} \qquad \qquad \mathsf{coe} \triangleq \mathsf{co} \setminus \mathsf{po} \qquad \qquad \mathsf{fre} \triangleq \mathsf{fr} \setminus \mathsf{po}$$

• Relation rmw connects a pair of read and write events accessing same memory location. These two events are same-location-porelated (po<sub>loc</sub>) as well as immediate-po-related (po<sub>im</sub>), *i.e.*, there is no intermediate event (po<sub>im</sub>  $x y \triangleq po x y \land \nexists z$ . [po  $x z \land po z y$ ]).

**Execution.** Given an execution  $X = \langle E, po, rf, co \rangle$ , X.E is the set of events, and X.po, X.rf, X.co are the set of po, rf, and co relations between the events in X.E. In an execution, all the memory locations are initialized.

**From programs to executions.** A program consists of the initialization of all shared memory locations followed by a parallel composition of threads. In a program, the concurrency primitives generate the events and relations during an execution. In an execution, we do not capture thread-local operations and accesses explicitly. However, we can always augment a program with additional shared variables to observe the values of thread-local variables.

**Behavior.** Given an execution, the final values of all memory locations define its behavior, *i.e.*, the values written by the writes which have no **co**-successors.

$\mathsf{Behav}(\mathsf{X}) \triangleq \{ \langle e.\mathsf{loc}, e.\mathsf{val} \rangle \mid e \in \mathsf{X}.\mathsf{W} \land [\{e\}]; \mathsf{X}.\mathsf{co} = \emptyset \}$

**Consistency axioms.** Based on these relations and events, we define the consistency axioms for a model. The consistency axioms capture certain architectural properties which are satisfied in an

| (external) axiom<br>ob is irreflexive where                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ob \triangleq (rfe \cup coe \cup fre \cup lob)^+$                                                                                                                |

| $lob \triangleq (lws \cup dob \cup aob \cup bob)^+$                                                                                                               |

| bob ≜ po; [F]; po ∪ [R]; po; [F <sub>LD</sub> ]; po<br>∪ [W]; po; [F <sub>ST</sub> ]; po; [W]<br>∪ po; [dom([A]; amo; [L])] ∪ [codom([A]; amo; [L])]; po<br>∪ ··· |

Figure 5: Arm-Cats Arm model (corrected)

execution. If an execution satisfies all the axioms of the model, then it is consistent in that model. The set of consistent executions of program  $\mathbb{P}$  in memory model M is denoted by  $[[\mathbb{P}]]_M$ . The set of behaviors exhibited by the consistent executions constitute the program behavior.

#### 5.2 x86 and Arm Concurrency Models: A Preview

We briefly discuss the axiomatic models of x86 and Arm [6, 8, 10].

- An x86 RMOV or Arm LDR generates a read (R) event and an x86 WMOV or Arm STR generates a write (W) event.

- In both x86 and Arm, a *successful* RMW generates a pair of rmwrelated events. In x86, these events are [R]; rmw; [W] related. In Arm, we categorize the rmw relations as amo and lxsx relations which result from RMW<sup>1</sup> and RMW<sup>2</sup> primitives. So, in Arm, rmw = lxsx ∪ amo holds. If an RMW fails in x86 or Arm, it generates an R event only.

- An x86 MFENCE or Arm DMBFF generates an F event.

Arm also generates events and relations for lightweight fences and synchronizing memory accesses.

- $\bullet\,$  DMBLD and DMBST fences generate  $F_{\text{LD}}$  and  $F_{\text{ST}}$  events.

- Release store (e.g., STR<sub>L</sub>), acquire load (e.g., LDR<sub>A</sub>), acquirePC-load (e.g., LDR<sub>Q</sub>) generate L, A, Q events respectively. L is ordered with its predecessors, A and Q are ordered with its successors, and a L is ordered with its successor A event. Finally, L ⊆ W, A ⊆ R, and Q ⊆ R hold.

**Common features.** Both x86 and Arm ensure coherence and atomicity which are captured by these axioms.

<u>Coherence</u>: The property enforces *SC-per-location* in an execution: the memory accesses per memory locations are totally ordered. The property is captured by (sc-per-loc) axiom:  $(po|_{loc} \cup rf \cup co \cup fr)^+$  is irreflexive.

<u>Atomicity</u>: The read and write pair generated from a successful RMW access is atomic. Suppose *r* and *w* are **rmw** related read and write events. If there exists a write event *w'* between *r* and *w*, and X.fre(*r*, *w'*) and X.coe(*w'*, *w*) hold, then the execution violates atomicity. Both x86 and Arm restrict atomicity violation by (atomicity) axiom: **rmw**  $\cap$  (fre; coe) =  $\emptyset$ .

**Distinguishing x86 and Arm concurrency.** Now, we discuss the relations and axioms that differentiate the x86 and Arm formal models.

<u>x86</u>: The read-read, read-write, write-write event pairs are ordered by preserved-program-order (ppo) relation. In addition, access pairs ASPLOS '23, March 25-29, 2023, Vancouver, BC, Canada

| (G | Ord | ) axion |

|----|-----|---------|

| (U | Olu | ј алтоп |

| ghb is irreflexive where                              |                                                              |

|-------------------------------------------------------|--------------------------------------------------------------|

| $ghb \triangleq (ord \cup rfe \cup coe \cup fre)^+$   |                                                              |

| ord $\triangleq$ [R]; po; [F <sub>RR</sub> ]; po; [R] | $\cup \ [R]; po; [F_{RW}]; po; [W]$                          |

| $\cup \ [R]; po; [F_{RM}]; po; [R \cup W]$            | $\cup \ [W]; po; [F_{WR}]; po; [R]$                          |

| $\cup \ [W]; po; [F_{ww}]; po; [W]$                   | $\cup ~[W]; po; [F_{\scriptscriptstyle WM}]; po; [R \cup W]$ |

| $\cup \ [R \cup W]; po; [F_{_{M\!R}}]; po; [R]$       | $\cup ~[R \cup W]; po; [F_{\scriptscriptstyle MW}]; po; [W]$ |

| $\cup [R \cup W]; po; [F_{MM}]; po; [R \cup$          | [W U                                                         |

| $\cup$ po; [W <sub>sc</sub> $\cup$ dom(rmw)]          | $\cup \; [R_{sc} \; \cup \; codom(rmw)]; po$                 |

| ∪ po; [F <sub>sc</sub> ]                              | ∪ [F <sub>sc</sub> ]; po                                     |

|                                                       |                                                              |

Figure 6: Proposed TCG IR model. TCG also satisfies the (scper-loc) and (atomicity) axioms, similarly to x86 and Arm.

are ordered by intermediate rmw or F accesses which is captured by implied relation. Using these relations, x86 defines (GHB) axiom which enforces a global order.

(GHB) (implied  $\cup$  ppo  $\cup$  rfe  $\cup$  fr  $\cup$  co)<sup>+</sup> is irreflexive where ppo  $\triangleq$  ((W × W)  $\cup$  (R × W)  $\cup$  (R × R))  $\cap$  po implied  $\triangleq$  po; [At  $\cup$  F]  $\cup$  [At  $\cup$  F]; po where At  $\triangleq$  dom(rmw)  $\cup$  codom(rmw)

<u>Arm</u>: In Figure 5, we show the (external) axiom from the official Arm model, with some revisions detailed later. Arm defines a transitive relation locally-ordered-before (lob) to order events in a thread. Relation lob has the following components:

- Relation local-write-successor (lws) orders a memory event to a same-location po-successor write event.

- Relation atomic-ordered-by (aob) is based on rmw.

- Relation dependency-ordered-before (dob) is derived from data, address, and control dependencies from a read to another write, memory accesses, and all events respectively.

- Relation barrier-ordered-by (bob) is based on fences and synchronizing memory accesses.

We discovered an undesirable scenario in the existing model, as elaborated in subsection 3.3. To ensure the casal instruction *acts as a full barrier*, we propose a fix to the model, where we replace po; [A]; amo; [L]; po in bob, which we marked green in Figure 5.

#### 5.3 Formalizing TCG IR Concurrency

We begin with the TCG primitives along with generated events and relations in an execution.

**Load and store accesses.** TCG provides load (Id) and store (st) operations that respectively read and write shared memory locations. Id and st accesses generate R and W events.

**Fence accesses.** TCG provides different types of fences: Frr, Frw, Fww, Fwr, Facq, Frel, and Fsc. These fences generate  $F_{RR}$ ,  $F_{RW}$ ,  $F_{WW}$ ,  $F_{WR}$ ,  $F_{ACQ}$ ,  $F_{REL}$ , and  $F_{SC}$  events respectively. They can be combined to define stronger fences, *e.g.*, we combine Frr and Frw to define Frm, that generates an  $F_{RM}$  event for the proposed mapping schemes. All these fences order certain memory accesses which we capture in *order* (ord) relations. For instance, a pair of po-related events (*a*, *b*) are in ord relation if *a* and *b* are W events with an intermediate  $F_{WW}$  event following the [W]; po; [F<sub>WW</sub>]; po; [W] rule.

| x86                | TCG IR  |  |  |

|--------------------|---------|--|--|

| RMOV               | ld; Frm |  |  |

| WMOV               | Fww; st |  |  |

| RMW                | RMW     |  |  |

| MFENCE             | Fsc     |  |  |

| (a) x86 to TCG IR. |         |  |  |

| TCG IR                   | Arm                                    |  |

|--------------------------|----------------------------------------|--|

| ld                       | LDR                                    |  |

| st                       | STR                                    |  |

| RMW                      | DMBFF; $RMW^2$ ; DMBFF or $RMW^1_{A1}$ |  |

| Frr/Frw/Frm              | DMBLD                                  |  |

| Fww                      | DMBST                                  |  |

| Fwr/Fmm/Fsc              | DMBFF                                  |  |

| Fwr/Fmm/Fsc<br>Facq/Frel | -                                      |  |

| (b) TCG IR to Arm.       |                                        |  |

| x86                        |               | TCG IR            |               | Arm                                                               |

|----------------------------|---------------|-------------------|---------------|-------------------------------------------------------------------|

| RMOV                       | $\rightarrow$ | ld; Frm           | $\rightarrow$ | LDR; DMBLD                                                        |

| WMOV                       | $\rightarrow$ | Fww; st           | $\rightarrow$ | DMBST; STR                                                        |

| RMW                        | $\rightarrow$ | RMW               | $\rightarrow$ | DMBFF; RMW <sup>2</sup> ; DMBFF or RMW <sup>1</sup> <sub>A1</sub> |

| MFENCE                     | $\rightarrow$ | $F_{\mathrm{sc}}$ | $\rightarrow$ | DMBFF                                                             |

| (c) x86 to Arm via TCG IR. |               |                   |               |                                                                   |

Figure 7: Verified mapping schemes for x86 to Arm via TCG IR.

RMW accesses. TCG also provides a number of atomic read-modifywrite (RMW) operations. These atomic RMW accesses follow SC semantics and do not allow reordering with other accesses. A successful RMW generates a rmw-related  $R_{sc}$  and  $W_{sc}$  event pair, *i.e.*,  $[R_{sc}]$ ; rmw;  $[W_{sc}]$ . A failed RMW generates a  $R_{sc}$  event. Finally,  $R_{sc} \subseteq R$  and  $W_{sc} \subseteq W$  hold in the model. Events generated from RMW accesses also enforce ord relation as shown in the ord definition.

Finally, we define global-happen-before (ghb) relation to order events across different threads. On an execution graph, ghb(a, b) implies that there is a path from *a* to *b* by ord and external relations rfe, coe, fre.

**Axioms.** Based on these relations, we define the consistency constraints. Similar to x86 and Arm, the TCG IR model also includes the (sc-per-loc) and (atomicity). axioms. The (GOrd) axiom in Figure 6 ensures a global order between events.

#### 5.4 Verified Mappings and Transformations

Based on the proposed IR model, we verify the correctness of the transformation (mappings and transformations) steps.

THEOREM 1 (TRANSFORMATION CORRECTNESS). Suppose a given source program  $\mathbb{P}_s$  in model  $M_s$  is transformed to the target program  $\mathbb{P}_t$  in model  $M_t$ . The transformation is correct if for each consistent target execution  $X_t \in [[\mathbb{P}_t]]_{M_t}$  there exists a consistent source execution  $X_s \in [[\mathbb{P}_s]]_{M_s}$  such that  $Behav(X_t) = Behav(X_s)$ .

For mapping schemes,  $M_s$  and  $M_t$  differ. For transformations,  $M_s$  and  $M_t$  are the same.

R. Gouicem, D. Sprokholt, J. Ruehl, R. Rocha, T. Spink, S. Chakraborty, and P. Bhatotia

$$X = Y = 0;$$

$$X = Y = 0;$$

$$a = X; || b = Y; \rightarrow Frw;$$

$$Y = 1; || X = 1;$$

$$Y = 1; || X = 1;$$

(LB-IR)

$$X = Y = 0;$$

$$Frw;$$

$$Y = 1; || X = 1;$$

$$X = Y = 0;$$

$$Frw;$$

$$Y = 1; || X = 1;$$

$$X = Y = 0;$$

$$Frw;$$

$$Y = 1; || X = 1;$$

$$Y = 1; || X = 1;$$

Disallowed outcome a = b = 1.

$$X = Y = 0;$$

$$X = Y = 0;$$

$$X = 1; || a = Y; \rightarrow X = 1; || a = Y;$$

$$Y = 1; || b = X; \qquad Fww;$$

$$Y = 1; || b = X; \qquad Y = 1; || :$$

(MP-IR)

Disallowed outcome a = 1, b = 0.

Figure 8: LB-IR and MP-IR disallow a = b = 1 and a = 1, b = 0by enforcing ld-st and ld-ld orders using at least Frw and Frr fences. We combine these fences and insert a trailing Frm with a load in the x86 to IR mapping. The leading Fww fence orders st-st in MP-IR. Hence we introduce a leading Fww with a store access in the x86 to IR mapping.

**Correct mapping schemes.** We translate concurrency primitives from x86 to Arm in two steps: (1) x86 to TCG IR and (2) TCG IR to Arm. We formally prove Theorem 1 to ensure correctness of these mapping schemes. These mapping schemes are *precise*: each placed fence is necessary in some program. Yet, it is sufficient to preserve the required ordering in every program.

*x86 to IR mapping scheme.* The mapping scheme is in Figure 7a. It introduces additional fences along with the load and store accesses to enforce the same restrictions as x86. In order to ensure correctness, we prove Theorem 1.

The x86 to IR mapping scheme is minimal. In x86 load-load and load-store accesses are ordered (formally by ppo) unlike that of IR. To enforce these orderings (formally ord) in the generated programs we require the trailing and leading fences with load and store respectively as shown in Figure 8.

*IR to Arm mapping scheme.* The mapping scheme is in Figure 7b. We prove the correctness theorem to ensure that the mapping scheme preserves correctness.

The IR to Arm mapping scheme is minimal. We analyze the fences in this mapping. If a TCG RMW generates RMW<sup>2</sup> access then it introduces leading and trailing DMBFF fences. These fences are required to preserve the mapping correctness as shown in Figure 9. The mapping scheme generates a DMBLD from a Frr/Frw/Frm fence in the IR to preserve the order of a load with its successor memory accesses. A Fwr/Fmm/Fsc fence in the IR generates a DMBFF fence to preserve the order between store-load pair on different locations. The Facq and Frel fences do not generate any instruction in Arm.

The examples in Figure 9 show that the DMBFF fences with RMW<sup>2</sup> accesses are required to preserve the mappings.

*x86 to IR to Arm mapping.* In Figure 7c, we combine the translations from x86 TCG and from TCG to Arm to obtain x86 to Arm translation.

$$\begin{split} X &= Y = 0; \\ X &= Y = 0; \\ X &= 2; \\ \text{RMW}(Y,0,1); \quad & \text{PMW}(X,0,1); \\ \text{RMW}(X,0,1); \\ \text{DMBFF;} \end{split} \quad \begin{array}{l} Y &= 2; \\ \text{DMBFF;} \\ \text{RMW}^2(Y,0,1); \\ \text{DMBFF;} \\ \text{DMBFF;} \\ \end{array} \quad \begin{array}{l} Y &= 2; \\ \text{DMBFF;} \\ \text{RMW}^2(X,0,1); \\ \text{DMBFF;} \\ \text{RMW}^2(X,0,1); \\ \text{DMBFF;} \\ \end{array} \end{split}$$

Disallowed outcome X = Y = 1.

$\begin{array}{ccc} X = Y = 0; \\ X = Y = 0; \\ \text{RMW}(X,0,1); & \text{RMW}(Y,0,1); & \rightarrow & \text{RMW}^2(X,0,1); \\ a = Y; & b = X; \\ & a = Y; \end{array} \begin{vmatrix} \text{DMBFF}; \\ \text{DMBFF}; \\ b = X; \\ b = X; \end{vmatrix} \begin{array}{c} \text{DMBFF}; \\ \text{DMBFF}; \\ b = X; \\ \end{array}$

Disallowed outcome a = b = 0.

Figure 9: The DMBFF fences preserve correctness in IR to Arm mapping. The outcomes are disallowed in the IR model. Arm would allow these outcomes without the intermediate DMBFF fences and the translations would be incorrect.

**Optimizing transformations.** We formally prove Theorem 1 for various transformations on the concurrency primitives in the TCG IR. The verified transformations ensure the correctness of the translations in Risotto.

<u>Memory access eliminations</u>: TCG performs constant propagation and folding on the IR. These transformations may also be performed on shared memory accesses. Hence, we prove the correctness of the following transformations on executions, where  $a \cdot b$  denotes po<sub>im</sub>related events with the labels *a* and *b*. The memory access pairs are on the same-location and may have any type of intermediate fences denoted by F<sub>0</sub> where  $o \in \{\text{RM}, \text{ww}\}$ , or F<sub> $\tau$ </sub> where  $\tau \in \{\text{sc}, \text{ww}\}$ .

*Fence merging:* It is correct to merge a fence to a same or stronger fence. We can also strengthen a fence to a stronger fence. We can combine these transformations as follows:

$$F_{RM} \cdot F_{WW} \xrightarrow{strengthen} F_{SC} \cdot F_{SC} \xrightarrow{merge} F_{SC}$$

<u>Reordering</u>: The plain memory accesses are unordered in TCG IR unlike in x86, and hence can be reordered freely. The proposed TCG IR model allows the reorderings of independent memory access pairs on different locations. Moreover, dependencies do not enforce any ordering in TCG IR unlike that of Arm, and hence TCG can remove false dependencies. These transformations are formally correct as the TCG IR model do not order accesses based on dependencies.

We prove that reordering  $a \cdot b \rightsquigarrow b \cdot a$  is correct where a and b are the labels of non-RMW memory events which are independent and access different memory locations.

<u>Mechanized Proofs</u>: We prove the correctness of our transformations – from some source program  $\mathbb{P}_{src}$  to a target program  $\mathbb{P}_{tgt}$  – in three steps. First, given a  $M_t$ -consistent execution  $X_t$  of  $\mathbb{P}_{tgt}$ , we define a source execution  $X_s$  from  $\mathbb{P}_{src}$ . Secondly, we relate the relations in  $M_s$  and  $M_t$  to show that  $X_s$  satisfies the axioms in  $M_s$ , because  $X_t$  satisfies those of  $M_t$ . Finally, we show that the  $X_t$ .co and  $X_s$ .co relations match, which means  $X_t$  and  $X_s$  have identical behaviors.

We mechanize all proofs in 14,000 lines of Agda [4].

ASPLOS '23, March 25-29, 2023, Vancouver, BC, Canada

| $R(X, v) \cdot R(X, v')$               | $\rightsquigarrow R(X, v)$                | (RAR)   |

|----------------------------------------|-------------------------------------------|---------|

| $W(X, v) \cdot R(X, v)$                | $\rightsquigarrow W(X, v)$                | (RAW)   |

| $W(X, v) \cdot W(X, v')$               | $\rightsquigarrow W(X, v')$               | (WAW)   |

| $R(X, v) \cdot F_o \cdot R(X, v')$     | $\rightsquigarrow R(X, v) \cdot F_o$      | (F-RAR) |

| $W(X, v) \cdot F_{\tau} \cdot R(X, v)$ | $\rightsquigarrow W(X, v) \cdot F_{\tau}$ | (F-RAW) |

| $W(X, v) \cdot F_o \cdot W(X, v')$     | $\rightsquigarrow F_o \cdot W(X, v')$     | (F-WAW) |

**Figure 10: Elimination Transformations**

#### **6 RISOTTO SYSTEM ARCHITECTURE**

Risotto is based on QEMU 6.1.0 [71]. In Risotto, we implement our verified mapping schemes, a dynamic linker to use host shared libraries and a fast and correct translation of the x86 CAS instructions.

#### 6.1 Formally Verified Memory Mappings

We implement the formally verified memory mappings described in Section 5.3 in Risotto. More precisely, we implement the mapping schemes from Figure 7. We obtain the following performance benefits compared to the existing QEMU implementation.

**Lightweight fences.** Compared to QEMU that generates Fmr and Fmw fences before load and store operations, we generate Frm and Fww fences in the TCG IR. While QEMU's fences end up as a DMBLD or DMBFF fence, our scheme produces either a DMBLD or a DMBST fence. These fences are less costly in terms of performance than full fences [51].

**Newly allowed reorderings.** Enforcing the proper x86 model also allows for reorderings of memory operations that were not possible with QEMU. Indeed, in our mapping scheme, there is no fence between a store and a load access. This allows store-load access pairs to be freely reordered by the processor if there is no dependency between them.

**Fence merging optimizations.** We implement an optimization pass over the TCG IR to merge fences that have no intermediate memory access. We merge the fences as a stronger one that suffices, and place it where the earliest fence was. As an example, we show the translation of a program from x86 to Arm: (1) x86 to TCG IR following Figure 7a, (2) fence merging, and (3) TCG IR to (4) Arm following Figure 7b.

$$\begin{array}{cccc} a=X; & a=X; & a=X; & a=X; \\ Y=1; & & Frm; & & Fsc; & & DMBFF; \\ & & Y=1; & & Y=1; & Y=1; \end{array}$$

**False dependency elimination.** We perform false dependency elimination (*e.g.,*  $X = a * 0 \rightarrow X = 0$ ) on the TCG IR. It is trivially correct as the TCG IR model does not use dependency relations for any ordering, unlike in Arm.

#### 6.2 Dynamic Host Library Linker

In order to use host shared library functions, Risotto must detect when the emulated program calls a shared library function, and link to the host library instead of emulating the guest linker and guest library function.

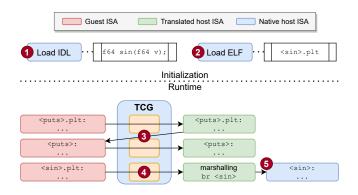

Figure 11: Risotto's dynamic linker workflow.

**Supporting host shared libraries.** To support native shared library execution, the shared library functions in use must be described to the DBT runtime, so that translated guest code can correctly transition to and from native library execution. The transition process translates function arguments from the guest representation to the host, and return values back from the host representation to the guest.

Function signature descriptions are necessary because parameters types, and their semantics are not specified in the raw application binary, and this information is necessary to perform parameter values translation. The runtime effectively needs to map the guest calling convention to the host's, which requires the parameter types must be known, so that appropriate value marshaling can take place. This would be unnecessary if both the host and guest Application Binary Interfaces (ABIs) were fully compatible. In our setup, we have no control over the OS, which means we cannot change the ABI to make it compatible across ISAs.

To describe function signatures to the runtime, we introduce an *Interface Definition Language* (IDL) that provides this information at run time to the translation system. Our IDL describes function signatures in a form similar to C function prototypes.

**Capturing shared library calls.** The key idea is to detect calls to shared library functions in the guest program, and, instead of performing binary translation as usual, emit code that directly calls the host shared library function. To do this, we exploit the dynamic linking mechanism of the ELF binary format. ELF files use a Procedure Linkage Table (PLT) that contains short code sequences that transfer control to the dynamic linker when a shared library function is invoked. Each imported shared library function has a PLT entry.

All shared library calls are made via the corresponding PLT entries – application code makes a call to the PLT entry when it wants to invoke such a function. When Risotto encounters a PLT entry, instead of translating the routine, it generates a code sequence that directly calls the host version of the shared library function.

**Sequence of events.** Figure 11 show the workflow of our linking mechanism. First, we read the IDL file, which identifies the shared library functions that are to be executed natively, and store the function signature information (1). Then, as Risotto loads the guest ELF binary, it parses the .dynsym section to determine the shared

R. Gouicem, D. Sprokholt, J. Ruehl, R. Rocha, T. Spink, S. Chakraborty, and P. Bhatotia

library functions that the program imports. For each detected function, the signature is looked up, and if present, *i.e.*, it has been described in the IDL, the corresponding PLT entry is located in the binary. The address of the PLT entry, along with a pointer to the function signature description, is stored in a lookup table (2).

When Risotto is about to translate a basic block, the address of the block is checked in the lookup table. If it was not specified in the IDL, the PLT entry as well as the guest library function are translated, as shown with the puts function (3). If it was, we generate code to marshal the function arguments from guest to host representation (4), and ultimately call the host function directly, as shown with the sin function (5). In practice, for Arm and x86, guest register values are copied into host register values, and viceversa for the function return value.

**Discussion on correctness.** Using native libraries may cause inconsistencies due to the mismatch in memory models. If it is stronger than the guest model, then there is no problem. If it is weaker, incorrect behaviors only happen if the shared library function and emulated code interact with the same data location concurrently, which we have not observed in our applications.

#### 6.3 Fast and Correct CAS Instructions

As previously detailed, QEMU translates CAS operations as calls to helper functions that in turn rely on GCC built-ins. In order to avoid the correctness problems this creates, as well as the performance degradation due to unnecessary jumps, we design a direct translation of CAS instructions. In particular, we target the translation of the x86 CMPXCHG instruction to Arm.

Risotto directly translates the x86 CMPXCHG instruction to the Arm casal instruction, without using a helper function. We do this by adding a new instruction to the TCG IR, CAS. Instructions implementing a CAS semantic in the guest ISA are translated to this new TCG IR instruction if the host supports native CAS. Otherwise, the usual call to the helper function is generated. When translating back from TCG IR to the host ISA, the CAS instruction is translated to the corresponding host CAS instruction. More specifically, in Arm, we translate it to a casal instruction.

**Correctness.** We follow the mapping schemes from Figure 7 for the RMW translation. x86 RMW acts as a full fence, and only a successful  $\text{RMW}_{AL}^1$  in Arm does the same (see Section 2.4). Since CMPXCHG is an x86 RMW and Arm's casal is an RMW<sub>AL</sub><sup>1</sup>, both have the same semantics in terms of ordering, making our translation correct.

## 7 EVALUATION

We evaluate Risotto's overall performance (§ 7.2), dynamic library linker (§ 7.3) and CAS translation (§ 7.4).

## 7.1 Experimental Setup

**Testbed.** We perform our evaluation on a server equipped with two Marvell ThunderX2 CN9975 processors (ARMv8.1, 28 cores per chip, 4-way SMT, 2.0 GHz), 256 GB of DDR4 memory ( $4 \times 64$  GB, 3200 MHz, ECC) and a 960 GB SSD (SATA 6Gb/s).

**Benchmark suites and applications.** We perform our evaluation on a set of applications from two benchmark suites: PARSEC 3.0 [19] and Phoenix [72]. For PARSEC, we omit the raytrace and x264

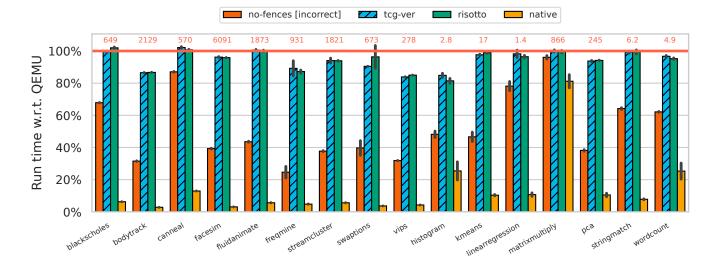

Figure 12: Run time of PARSEC and Phoenix benchmarks, running with QEMU with no fence generation (no-fences), QEMU with our verified mappings (tcg-ver) and Risotto, relative to QEMU. Native execution is also shown (native). Lower is better, raw values in seconds.

benchmarks because they respectively fail to build and run natively on Arm.

**Setups.** We run our experiments on QEMU v6.1.0, as well as multiple variants: one that does not enforce any ordering, *i.e.*, no fences generated, noted no-fences; one that enforces our verified mappings, noted tcg-ver, and finally Risotto, with all features described previously. Note that no-fences is incorrect, but still serves as an oracle of the maximal performance improvement possible when optimizing ordering fences. We also run binaries natively, *i.e.*, Arm binaries without emulation, to show the performance gap. In every plot, the red line shows the average performance of QEMU, with the raw values in red.

**Methodology.** We run every experiment five times and compute the speedups compared to our baseline, QEMU. For better reproducibility, we disable turbo boost and use the performance scaling governor of Linux which uses a fixed frequency of 2.0 GHz on our CPU. We also pin our experiments on a single socket to avoid NUMA effects, therefore using 112 hardware threads. We compile all variants of QEMU and Risotto with GCC 10.3.0.

#### 7.2 Overall Performance

First, we evaluate the raw performance of Risotto on PARSEC and Phoenix benchmarks. Figure 12 shows the performance results relative to the baseline, QEMU (red horizontal line), lower is better.

**Cost of memory ordering enforcement.** In order to better understand Risotto's performance, we first analyze the cost of QEMU's fence mapping. By observing the performance of no-fences, we see that fences account for a large portion of the execution time of our benchmarks, up to 75% (for freqmine), 48% on average. These results highlight the importance of reducing overhead associated with fences while still preserving its correctness.

**Risotto's verified mappings.** tcg-ver achieves significant performance gains without compromising the program's correctness. Compared to QEMU, we achieve improvements of up to 19.7% (6.7% on average), thanks to fence merging and weaker fence usage (Section 6.1).

#### 7.3 Dynamic Host Library Linker

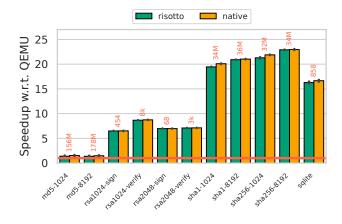

We evaluate Risotto's dynamic linker on well-known libraries that are extensively used in real-world applications. We evaluate the OpenSSL cryptography library [63] (*libssl, libcrypto*), the sqlite3 database engine [81] (*libsqlite*) and a stress microbenchmark on the standard math library (*libm*).

**OpenSSL and sqlite.** We run popular digests and ciphers with OpenSSL 1.1.1, such as RSA, MD5, SHA-1, and SHA-256, with different input sizes, as well as the speedtest benchmark of sqlite. We measure their throughput, *i.e.*, sign/s, verify/s or ops/s. We also run the sqlite speedtest1 benchmark and report its throughput.

Figure 13 shows the speedup of both Risotto and the native version over QEMU. Speedups vary from 1.4× (md5-1024) to 23× (sha256-8192), on a par with the native execution. Overall, we match the speed of native execution of shared libraries when using our dynamic host linker.

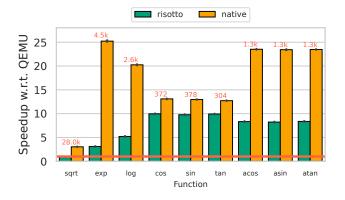

**Math library.** We evaluate the performance gains on functions from the standard math library. We run these functions 100M times and compute their throughput. Results are shown in Figure 14, with Risotto and native compared to QEMU. We observe speedups ranging from  $1 \times (\text{sqrt})$  to  $10 \times (\cos)$  with Risotto. Even though we significantly improve performance, we do not match the native version, that achieves up to  $25 \times$  speedups. This difference is explained by the short duration of the library calls, preventing the overhead of argument marshaling to be amortized.

Figure 13: Speed-up of openssl and sqlite benchmarks against QEMU. Higher is better, raw values in ops/s.

Figure 14: Speed-up of math library functions with Risotto compared to QEMU. Higher is better, raw values in ops/ms.

**Floating point emulation.** Using host libraries for functions with floating point (FP) computation offers another benefit. Correctly emulating FP instructions across the variety of implementations is hard, and so QEMU implements a software floating-point implementation, drastically impacting performance. By using host shared libraries, we can take advantage of native FP instructions, adding to the performance improvement, as exposed by the math library benchmark.

**Overhead of host library calls.** Calling a host library function instead of a guest one requires to perform argument marshaling (§6.2). The OpenSSL and sqlite results show that there is no overhead in performing host shared library calls. However, the math library results show a clear difference between Risotto and native execution (Figure 14). This stems from the duration of the linked functions. Math functions are very short, meaning that argument marshaling dominates the execution time. This is not the case with the other benchmarks, where functions have a longer duration. Still, even in the worst-case scenario, using host libraries is clearly beneficial.

**Overhead of our dynamic linker.** We evaluate the overhead of our dynamic linker when unused. Indeed, programs that make no

R. Gouicem, D. Sprokholt, J. Ruehl, R. Rocha, T. Spink, S. Chakraborty, and P. Bhatotia

Figure 15: Throughput of the CAS instruction with various levels of contention. Higher is better.

use of shared libraries should not be slowed down by this feature. Conveniently, PARSEC and Phoenix do not make extensive use of shared libraries, except libc for thread management. Figure 12 shows no difference between Risotto (with the linker) and tcg-ver (without the linker). Thus, our linker has no impact on performance if no host function is linked.

## 7.4 Fast Compare-and-Swap

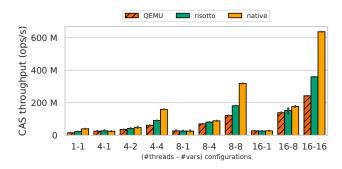

To evaluate our CAS translation, we implement a micro-benchmark that stresses this component in a multi-threaded setup. We vary the number of threads and variables accessed by CAS instructions to show various levels of contention. Figure 15 shows the throughput of QEMU, Risotto, and a native Arm binary. Note that QEMU's helper functions also use the casal instruction.

We observe that Risotto outperforms QEMU only when there is no contention (#threads = #variables) by up to 48% (14.5% on average). However, under contention, they perform similarly. Indeed, the casal instruction then dominates the execution time, reducing the relative impact of the additional jumps performed by QEMU.

#### 8 RELATED WORK

**Concurrency and memory models.** Mappings of concurrency primitives from programming languages to different architecture have been studied widely in the literature [17, 18, 41, 43, 66, 67, 73] where correctness is established based on formal semantics. The correctness of program transformations under relaxed memory models is also well explored [25–27, 41, 42, 47, 75, 76, 86]. Similar to these approaches, we use formal semantics of the architectures to define correct and precise mapping schemes as well as correct translations on TCG IR.

Prior works have formalized informal concurrency specifications such as C/C++ [18, 21], LLVM IR [26], Power and ARMv7 [10, 55, 74]. The earlier formalization of ARMv8 by Pulte *et al.* [70] is updated by Alglave *et al.* [6] with the semantics of casal accesses. To our knowledge, we are the first to formalize the TCG IR concurrency model to obtain formally verified cross-architecture translations.

There are several results on identifying the differences between weak memory models [2, 3, 5, 9, 35, 36, 54, 82, 89]. To address these differences, a number of optimized fence placement approaches

have been proposed [31, 45, 58, 78, 83, 87]. However, optimal fence placement is an undecidable problem in the general case [14].

Recently, VSync [61] proposed using model checking to identify efficient fence insertion in Arm and RISC-V programs. Others have developed analyses to check if a program is SC-robust/stable against weaker models, inserting fences where necessary [1, 7, 23, 46, 48–50, 78]. Tao *et al.* [85] implement a KVM-based hypervisor that satisfies *weak data race free conditions* on an SC model which also holds on the Arm model. However, using model checking to insert fences is computationally expensive, and rarely scales beyond small programs.

**Binary translation.** While many QEMU-based DBTs support multithreaded programs, most fail to address mismatches among memory consistency models [29, 37, 88]. Similarly, modern static binary translators target the LLVM IR, allowing for better whole program optimization [15, 20, 24, 79, 91]. However, they do not support concurrency either.

Apple's Rosetta 2 [11] is an emulator developed for their x86 to Arm transition. It uses both static and dynamic binary translation. It handles the memory model mismatch by implementing both x86 and Arm models in hardware [40]. Microsoft also enables emulation of x86 binaries on Arm machines through the WOW64 layer [56]. They use a caching system that optimizes the generated code after a first execution. Unfortunately, both Microsoft's and Apple's solutions rely on their control over the hardware and software ecosystems, and are closed source, with scarcely available technical details.

**ArMOR.** ArMOR [53] proposes a specification format that defines the ordering of memory accesses in architectures, and other properties such as *multicopy-atomicity* (MCA), allowing it to identify the required fences during a program execution. However, it has several limitations:

- No DBT ArMOR generates DFSMs to insert fences, which they applied inside the Pin [52] instruction instrumentation tool. Pin, however, is not a DBT system. Pico [28] leverages ArMOR to obtain mapping rules for load and store accesses. As ArMOR cannot handle RMWs, Pico defines their own mapping rules for RMWs, without any formal guarantees of correctness. Additionally, Pico translates PowerPC to x86, which differs from translating from x86 to Armv8 through TCG.

- No RMWs ArMOR considers RMWs a straightforward extension, as long as ordering behavior is correctly specified. Through our formal proofs, we discover that RMWs may display intricate behavior, which differs subtly between architectures. Moreover, Arm's LX/SX RMWs suffer from spurious failures unlike x86 RMWs, which goes beyond ordering rules. Hence, we believe that ArMOR cannot *easily* handle RMWs without major extensions.

- **Dependency tracking** We carefully analyze dependencies in Arm and discover their behavior to be quite intricate. We thus elect to *eliminate them with our mappings*. If dependencies were included in ArMOR, we foresee some challenges: (1) it is *computationally expensive* to track dependencies for an *arbitrary number* of memory location, and (2) dependency rules may be exceedingly complex. For instance, Arm's dob can order an event *a* with another *write* event *b*, if there is another instruction inbetween that is address-dependent on *a*.

• **QEMU** – QEMU translates programs at basic block granularity, across which no information propagates. In ArMOR, this corresponds to a *stream interruption*, which may cause inserting unnecessarily strong fences. Additionally, QEMU performs intermediate optimizations on concurrency primitives, for which it is not clear how it interacts with ArMOR's approach.

Host shared libraries. Tan *et al.* [84] use QEMU's helper functions to support calls to native shared library functions, adding a level of indirection, and requiring hard-coding the helper functions. QEMU has to be recompiled when adding support for a function. box86/64 [68, 69] implement native shared libraries in their instruction set simulator with "wrapped libraries". This approach also requires hard-coding a glue layer that supports native shared library invocation.

Microsoft's Windows-on-Arm supports this feature by changing the ABI of Windows, easing the translation from x86 to Arm [57]. Rosetta 2 also uses a common ABI for x86 and Arm and performs lazy binding of shared library functions [60].

## 9 CONCLUSION

We present an end-to-end approach to provide correct and efficient execution of legacy x86 software on the weak memory Arm architecture. To achieve this, we formalize QEMU'S TCG IR memory model, and use it to propose formally verified mapping schemes. We leverage these schemes in Risotto, a QEMU-based DBT system that optimizes fence placement while ensuring correctness. Risotto further optimizes performance by cross-architecture dynamic linking of native shared libraries and a fast and correct CAS translation. We evaluate Risotto using multi-threaded benchmark suites and real-world applications, and show that Risotto improves the emulation performance, while ensuring correctness.

**Open source contributions.** We contacted the Arm-Cats authors to propose a strengthening of the Arm model that was accepted [39]. We also submitted our new mapping schemes to the QEMU mailing list. The patch is currently under review with a positive feedback.

#### DATA-AVAILABILITY STATEMENT

Risotto, the proofs and the instructions to reproduce the results are available on Github [33] and Zenodo [34]. appendix A details how to use the artifact.

## ACKNOWLEDGMENTS

We would like to thank the reviewers from the technical program committee for their detailed feedback on the paper, as well as the reviewers from the artifact evaluation committee for testing our artifact and helping us fix it.

#### A ARTIFACT APPENDIX