# OSCILLATOR BASED ANALOG-TO-DIGITAL CONVERTER FOR ACTION POTENTIAL READOUT IN MICROELECTRODE ARRAYS NIKHITA BALADARI

UDelft

# Oscillator based ADC for Action Potential Readout in Microelectrode Arrays

by

### Nikhita Baladari

at the Bio Engineering Lab, ETH Zürich under the supervision of Dr. Fernando Cardes and Prof. Andreas Hierlemann,

to obtain the degree of Master of Science in Biomedical Engineering at the Delft University of Technology, to be defended publicly on August 28, 2020.

| Student number:   | 4815882                        |                      |

|-------------------|--------------------------------|----------------------|

| Project duration: | August 1, 2019 – January 31, 2 | 020                  |

| Thesis committee: | Dr. Virgilio Valente,          | TU Delft, supervisor |

|                   | Prof. Dr. Ir. Wouter Serdijn,  | TU Delft             |

|                   | Prof. Dr. Ir. Ronald Dekker,   | TU Delft             |

This thesis is confidential and cannot be made public until December 31, 2022.

An electronic version of this thesis is available at http://repository.tudelft.nl/.

### Acknowledgments

This thesis would not have been possible without the invaluable guidance of Dr. Fernando Cardes, my thesis supervisor, who has been my constant pillar of confidence throughout the project. His brilliance in this field never ceases to inspire me. Thanks for acknowledging and building my passion for bioelectronic design. I want to express my sincere gratitude to Prof. Andreas Hierlemann for providing me this opportunity to work at Bio Engineering Laboratory, ETH Zürich. He is the coolest professor I have met so far. I enjoyed working in this multi-disciplinary environment and have had the opportunity to learn something new every day from my teammates.

I want to thank Dr. Virgilio Valente, my advisor at TU Delft, whose constant feedback has always helped me and pushed me towards betterment. Thanks for the valuable suggestions and for helping me shape my thesis. I would like to thank Prof. Wouter Serdijn, who has always been supportive and encouraging during the decisions I had to take during my Masters.

As it goes without saying, my family has always been there for me throughout this journey. I should thank my mom, who never knew how to not believe in me, my dad, who always supported me in turning my dreams to reality, and my brother, who still thinks he has the coolest sister in the world (which he should). Thanks for always being there for me and never giving up on me.

I don't know if I should continue in the previous paragraph as I mention Srikanth Nallanthighal and Suryateja Sharma, who are more like family to me. My heartfelt thanks to Srikanth, who has constantly been babysitting me throughout my Masters. The Netherlands is home to me because of him. I want to thank Suryateja, who was the first person that inspired me to pursue a career in biomedical engineering. It is the greatest decision I have made, and he deserves all the credit for that. I want to thank all my friends who have been a part of this journey with me. Thanks to Akhil and Ganesh, who stuck by my side, despite my tantrums. Thanks to my 'Master gang' at ETH, Giulia, Ashlyn, Bram, Patricia, Philip, and Jeanne, who made my exchange semester smooth and memorable.

### Abstract

The functioning of the brain depends on the interplay between a large number of neurons. To understand the information processing in neuronal networks, we need tools to record the electrical activity of cells at high resolution. Microelectrode arrays (MEAs) are predominantly used to measure neuronal activity at high spatial and temporal resolution. With the advent of complementary metal-oxide-semiconductor (CMOS) based MEAs, it has been possible to design high-density MEAs with electrode sizes comparable to that of the individual neurons, allowing sub-cellular resolution. CMOS technology has also facilitated the on-chip signal conditioning needed to record the low-amplitude bio-signals with superior signal quality. In this thesis, a readout architecture for in-vitro MEAs has been proposed for a low-noise extracellular action potential (AP) readout.

One of the challenges in MEA implementation is the design of thousands of low-noise readout channels for simultaneously recording the signals. There is a need to design low-noise ADCs with optimal power and area consumption. In this thesis, a unique low-noise oscillator based sigma-delta ( $\Sigma\Delta$ ) ADC has been designed for MEA applications. With the advantages of oversampling and time-encoding techniques, the in-band noise has been optimized, without increased hardware complexity. The simple implementation of this proposed ADC makes it efficient in terms of area and power consumption.

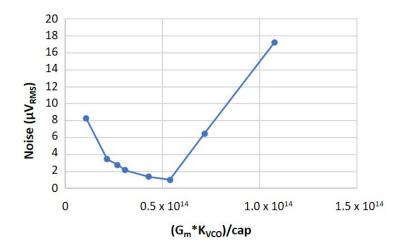

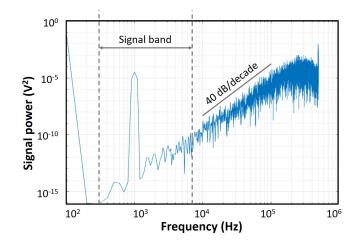

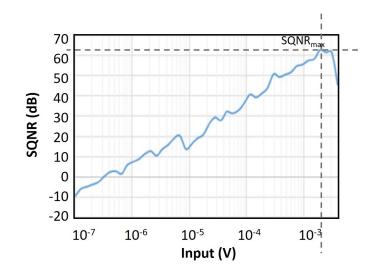

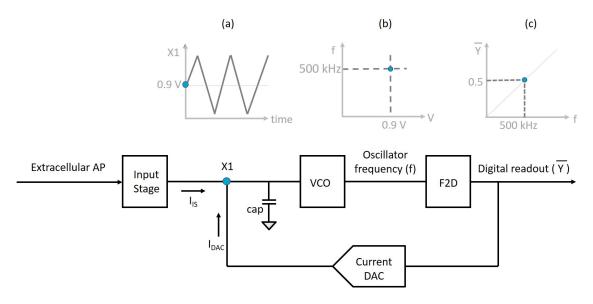

The integrated circuit for this oscillator based  $\Sigma\Delta$  ADC has been implemented in 0.18  $\mu$ m CMOS technology to demonstrate the feasibility of high-order oscillator-based ADCs for low-noise extracellular AP readout. It was possible to obtain a noise below 5  $\mu$ V<sub>RMS</sub> (simulations) and power consumption under 3  $\mu$ W using this ADC, which approximately occupies an area of 0.002 mm<sup>2</sup>. The action potential readout system implemented with this ADC has been taped-out for further analysis through measurements.

### Contents

| Ab | ostra             | ct v                                             |  |

|----|-------------------|--------------------------------------------------|--|

| Li | st of             | Figures xi                                       |  |

| Li | List of Tables xv |                                                  |  |

| Li | st of             | Abbreviations xvii                               |  |

|    |                   |                                                  |  |

| 1  | Intr              | oduction 1                                       |  |

|    | 1.1               | CMOS based in-vitro MEAs 3                       |  |

|    | 1.2               | In-vitro MEA applications                        |  |

|    | 1.3               | Challenges in MEA readout design                 |  |

|    | 1.4               | Time encoding based ADCs                         |  |

|    | 1.5               | Thesis objectives                                |  |

|    | 1.6               | Structure of the thesis                          |  |

|    |                   |                                                  |  |

| 2  | In-v              | itro Microelectrode arrays 9                     |  |

|    | 2.1               | Signal flow in MEA system                        |  |

|    | 2.2               | MEA readout architectures                        |  |

|    |                   | 2.2.1 Switch matrix architecture                 |  |

|    |                   | 2.2.2 Active pixel architecture                  |  |

|    |                   | 2.2.3 Switch Matrix vs Active Pixel Sensor       |  |

|    | 2.3               | Improvement of readout architecture for APS MEAs |  |

|    |                   | 2.3.1 Target MEA specifications                  |  |

|    |                   | 2.3.2 $\Sigma\Delta$ ADCs for MEAs               |  |

|    | 2.4               | Conclusion                                       |  |

|    |                   |                                                  |  |

| 3  | Tim               | e encoding $\Sigma \Delta$ ADCs 21               |  |

|    | 3.1               | Introduction                                     |  |

|    |                   | 3.1.1 Sampling                                   |  |

|    |                   | 3.1.1.1 Nyquist-Shannon sampling theorem         |  |

|    |                   | 3.1.2 Quantization                               |  |

|    | 3.2               | Oversampling data converters                     |  |

|    |                   | 3.2.1 Sigma-delta data converters                |  |

|    |                   | 3.2.1.1 First order $\Sigma\Delta$ modulator     |  |

|    |                   | 3.2.1.2 Second order $\Sigma\Delta$ modulator    |  |

|    | 3.3               | Time encoding ADCs                               |  |

67

|   | 3.4  | Conclusion                                          | 2  |

|---|------|-----------------------------------------------------|----|

| 4 | Syst | tem-level design of VCO based $\Sigma \Delta$ ADC 3 | 3  |

|   | 4.1  | Introduction                                        | 3  |

|   | 4.2  | Implementation of ADC                               | 4  |

|   |      | 4.2.1 First order ΣΔ ADC                            |    |

|   |      | 4.2.2 Oscillator based $\Sigma\Delta$ ADC           |    |

|   | 4.3  | VCO based $\Sigma\Delta$ ADC for MEA                | 8  |

|   | 4.4  | Circuit impairments                                 | 9  |

|   |      | 4.4.1 Transconductor                                | 0  |

|   |      | 4.4.2 Current DAC                                   | 0  |

|   |      | 4.4.3 Capacitor                                     | 0  |

|   |      | 4.4.4 VCO based quantizer                           | 1  |

|   |      | 4.4.5 Clock jitter and metastability                | 1  |

|   | 4.5  | Conclusion                                          | 1  |

|   |      |                                                     |    |

| 5 | Imp  | elementation of VCO based $\Sigma \Delta$ ADC 4     | 3  |

|   | 5.1  | Circuit design of VCO based $\Sigma\Delta$ ADC      | 3  |

|   |      | 5.1.1 Input stage                                   | 3  |

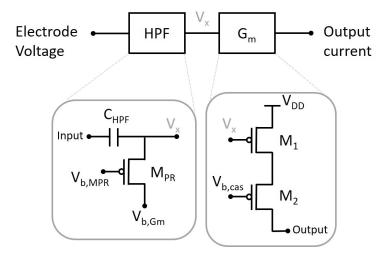

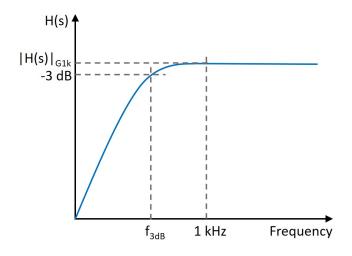

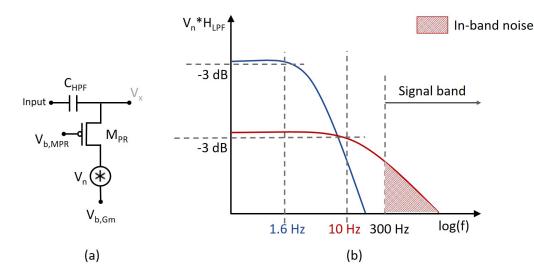

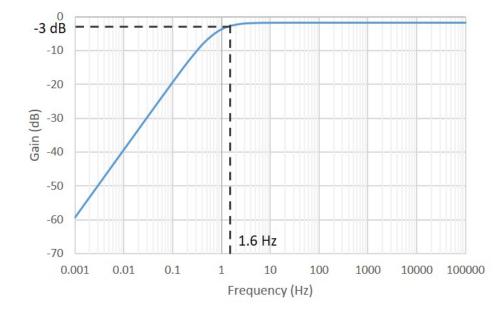

|   |      | 5.1.1.1 Architecture                                | 3  |

|   |      | 5.1.1.2 Corners and Monte Carlo analysis            | 8  |

|   |      | 5.1.2 Feedback DAC                                  | .9 |

|   |      | 5.1.2.1 Architecture                                | .9 |

|   |      | 5.1.2.2 Corners and Monte Carlo analysis            | 1  |

|   |      | 5.1.3 Integrator                                    | 2  |

|   |      | 5.1.4 Voltage controlled oscillator                 | 3  |

|   |      | 5.1.4.1 Architecture                                | 3  |

|   |      | 5.1.5 Frequency to digital converter                | 5  |

|   |      | 5.1.5.1 Architecture                                | 5  |

|   |      | 5.1.6 Schematic simulations                         | 9  |

|   | 5.2  | Integration in the test chip                        | 0  |

|   |      | 5.2.1 Complete ADC system                           | 0  |

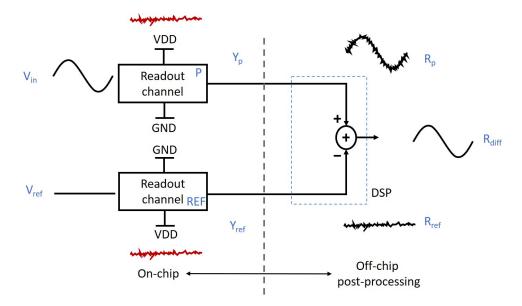

|   |      | 5.2.2 Pseudo-differential system                    | 1  |

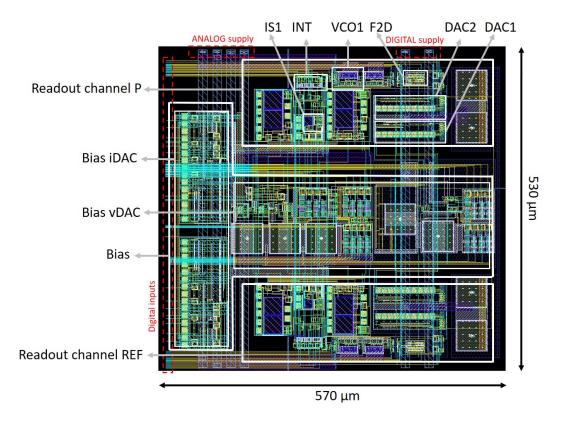

|   | 5.3  | Layout                                              | 2  |

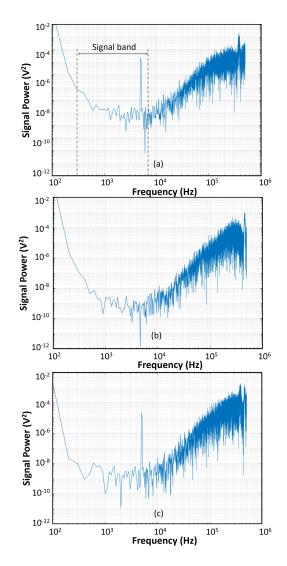

|   |      | 5.3.1 Post-layout simulations                       | 4  |

|   | 5.4  | Conclusion                                          | 5  |

|   |      |                                                     |    |

#### 6 Discussion

| 7 | Conclusion and future work | 71   |

|---|----------------------------|------|

|   | 7.1 Conclusion             | . 71 |

|   | 7.2 Future work            | . 71 |

| A | SQNR of ADCs                              | 73   |

|---|-------------------------------------------|------|

|   | A.1 Nyquist converters                    | 73   |

|   | A.2 Oversampled converters                | 74   |

|   | A.3 First order $\Sigma\Delta$ modulator  | 76   |

|   | A.4 Second order $\Sigma\Delta$ modulator | 77   |

| в | Noise                                     | 79   |

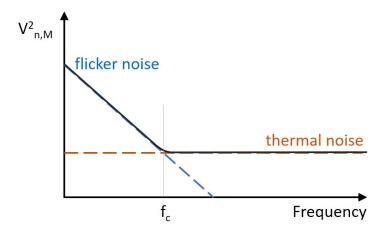

|   | B.1 Flicker and thermal noise             | . 79 |

|   | B.2 kT/C noise                            | 80   |

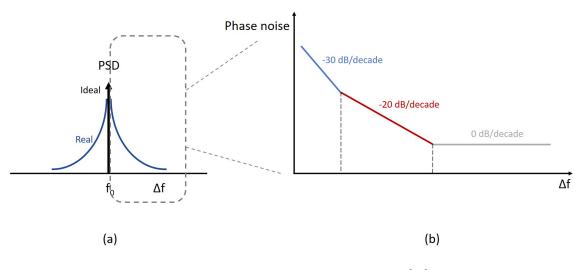

|   | B.3 Phase noise                           | 81   |

|   |                                           |      |

#### Bibliography

# List of Figures

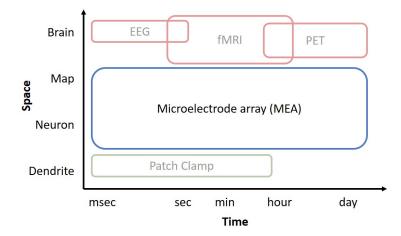

| 1.1 | Spatial and temporal resolution of neuronal sensing techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

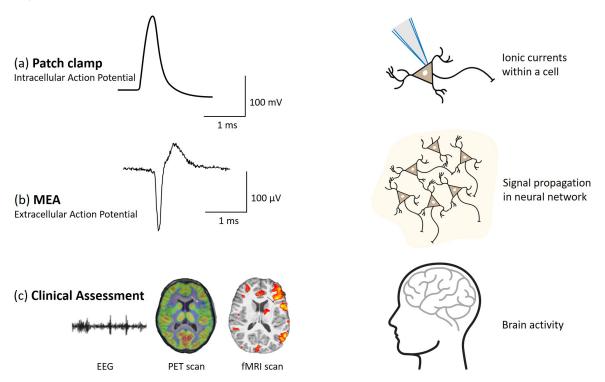

| 1.2 | Neuronal sensing techniques and their application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2  |

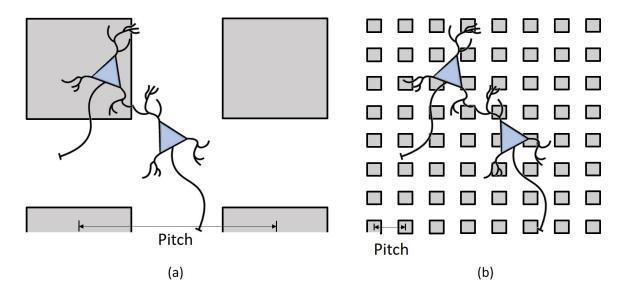

| 1.3 | Illustration of neurons on top of MEAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3  |

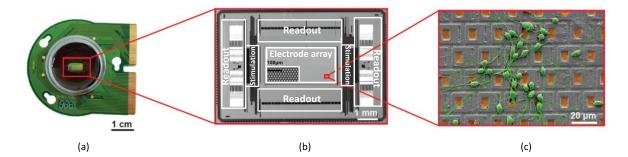

| 1.4 | Typical CMOS MEA sytem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5  |

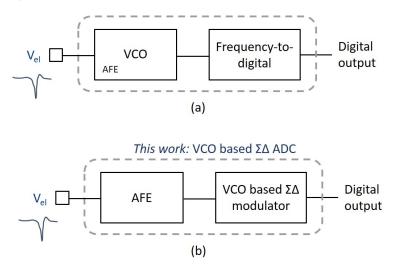

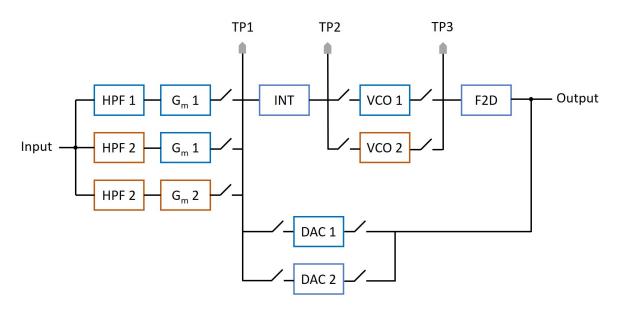

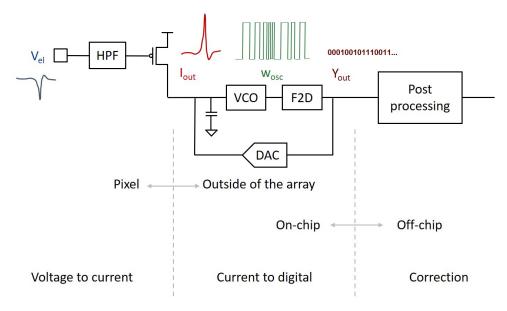

| 1.5 | Possible VCO based readout architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6  |

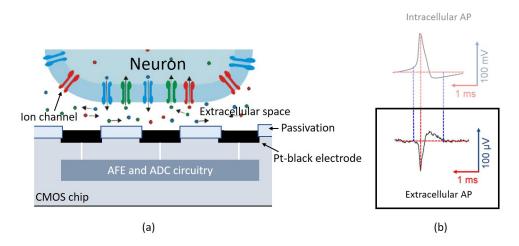

| 2.1 | Illustration of cell-MEA interface and extracellular AP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10 |

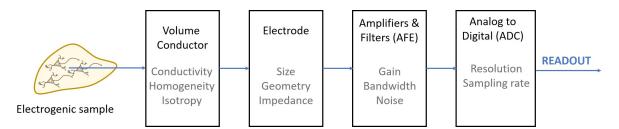

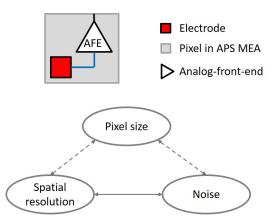

| 2.2 | Parameters effecting the readout process in MEA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10 |

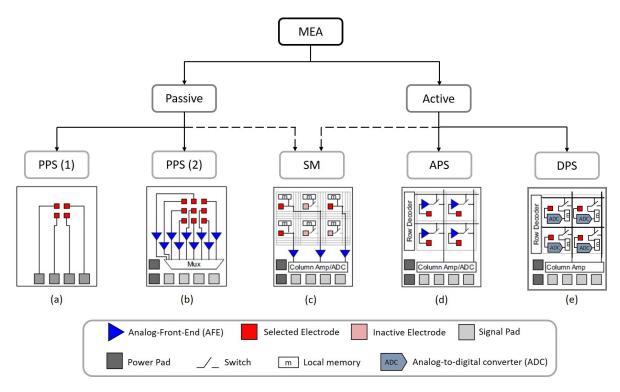

| 2.3 | Classification of MEAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12 |

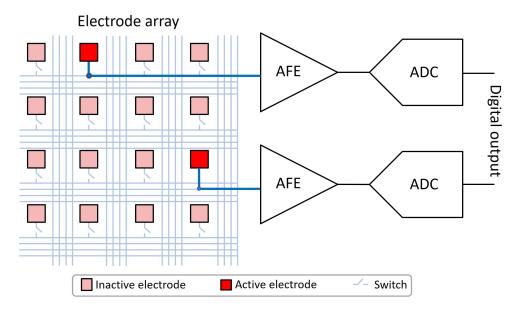

| 2.4 | Block diagram of switch matrix MEA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14 |

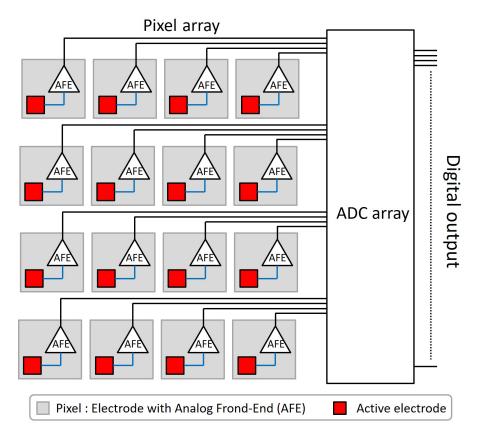

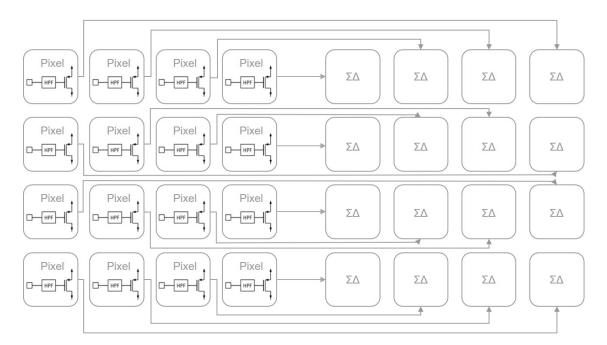

| 2.5 | Block diagram of APS MEA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 |

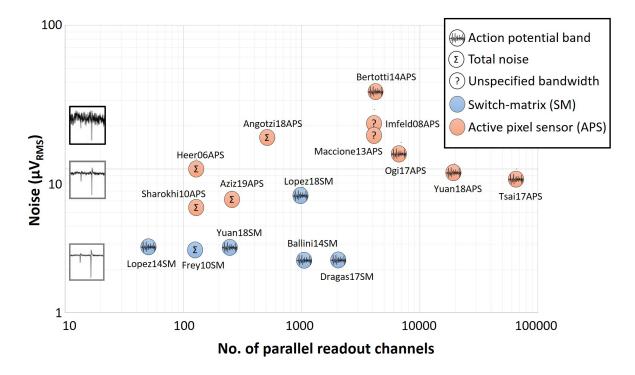

| 2.6 | Comparison of noise vs. the number of readout channels of different MEAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17 |

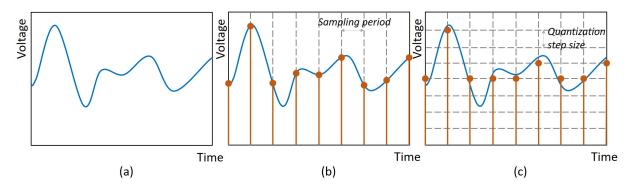

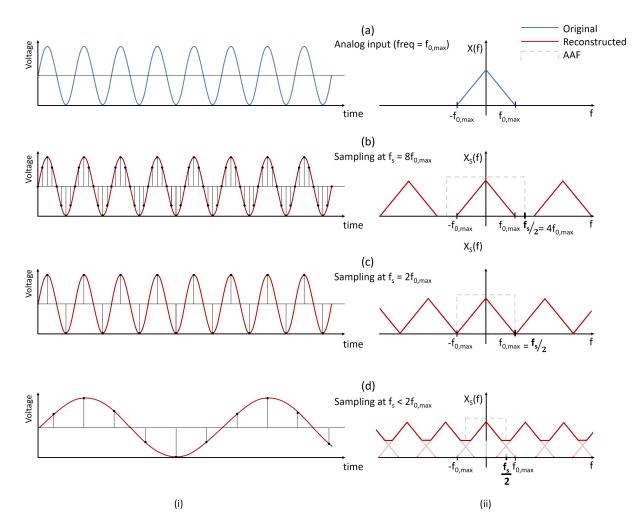

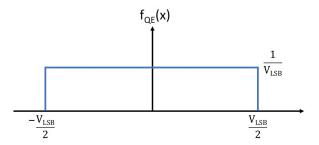

| 3.1 | Sampling and quantization in ADCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21 |

| 3.2 | Example for Nyquist theorem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22 |

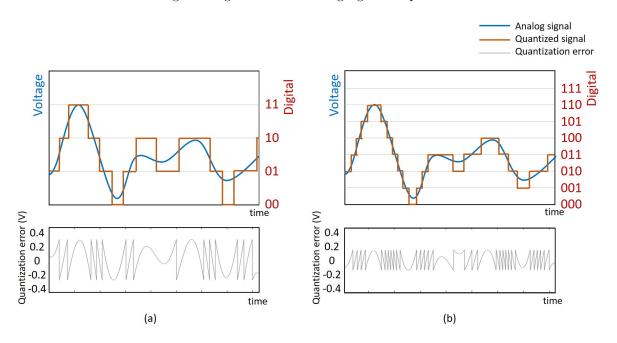

| 3.3 | Resolution in a 2-bit and 3-bit ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23 |

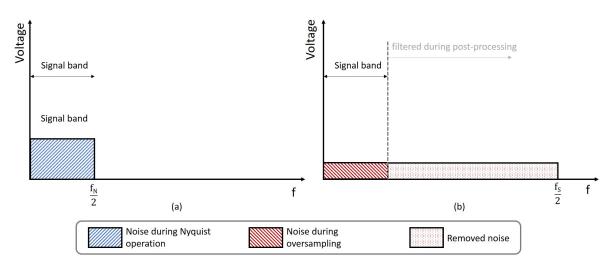

| 3.4 | Quantization noise: nyquist vs oversampled ADCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24 |

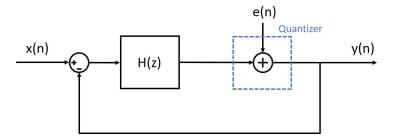

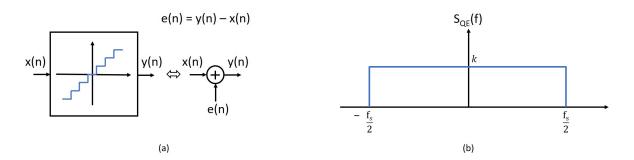

| 3.5 | Linear model of $\Sigma\Delta$ data converter $\hfill \hfill \hfill$ | 25 |

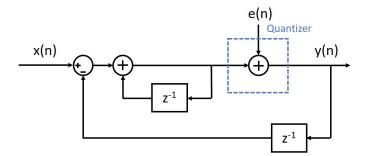

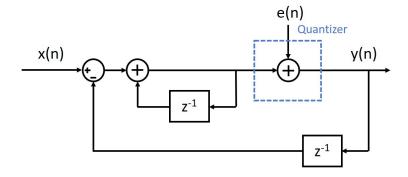

| 3.6 | Linear model of a first order $\Sigma\Delta$ data converter $\hdots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26 |

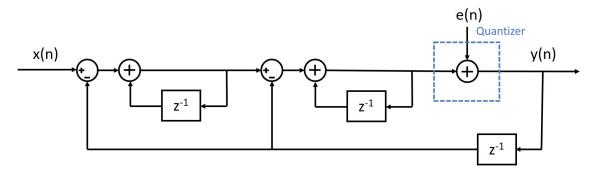

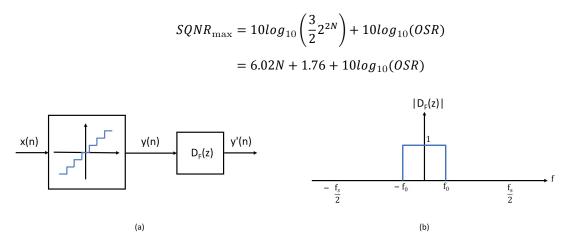

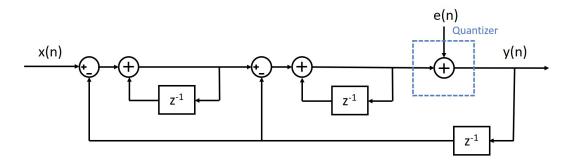

| 3.7 | Linear model of a second order $\Sigma\Delta$ data converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27 |

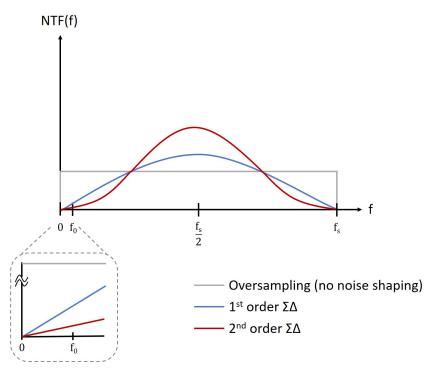

| 3.8 | Noise shaping in oversampled ADCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28 |

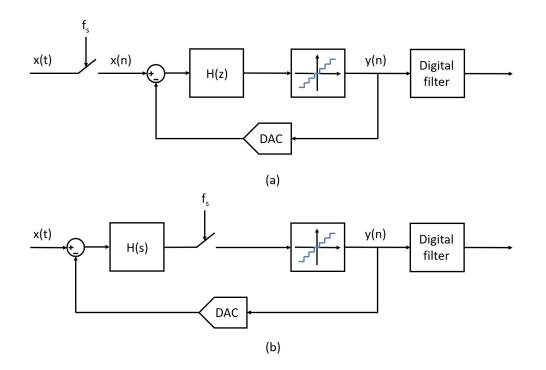

| 3.9                                                                                                                | Discrete- and continuous-time $\Sigma\Delta$ ADCs $\hfill \ldots \hfill \hfill \ldots \hfill \ldots \hfill \ldots \hfill \ldots$ | 29                                                                                             |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

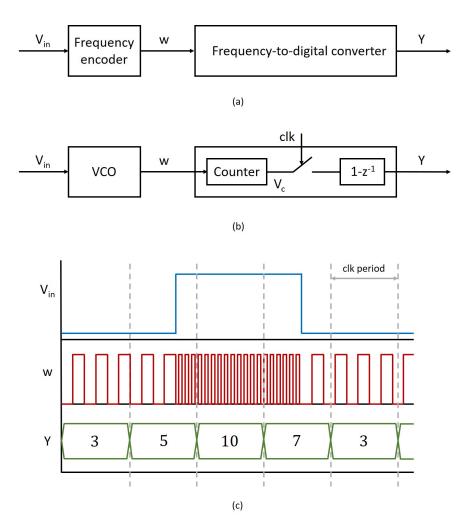

| 3.10                                                                                                               | Frequency encoding based ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30                                                                                             |

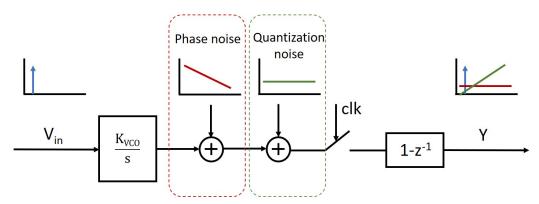

| 3.11                                                                                                               | Linear model of VCO based ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31                                                                                             |

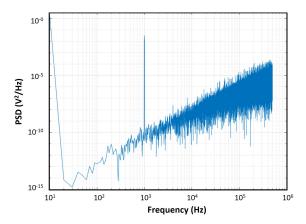

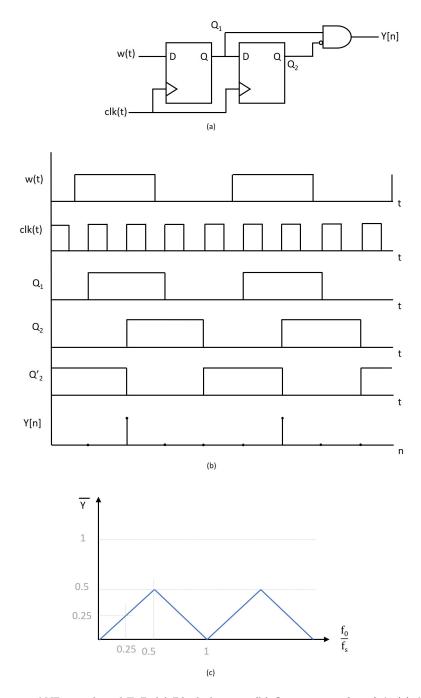

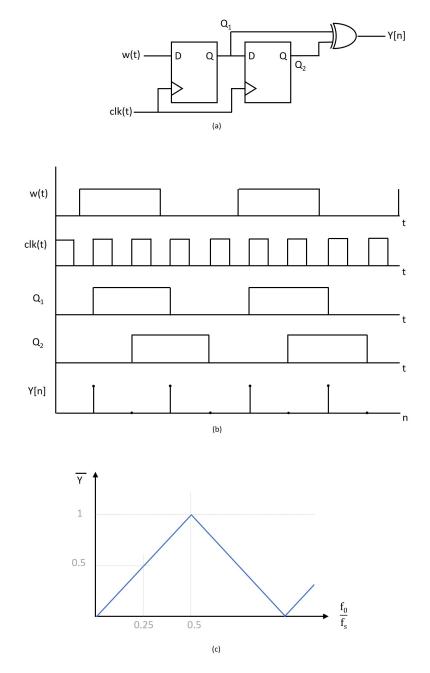

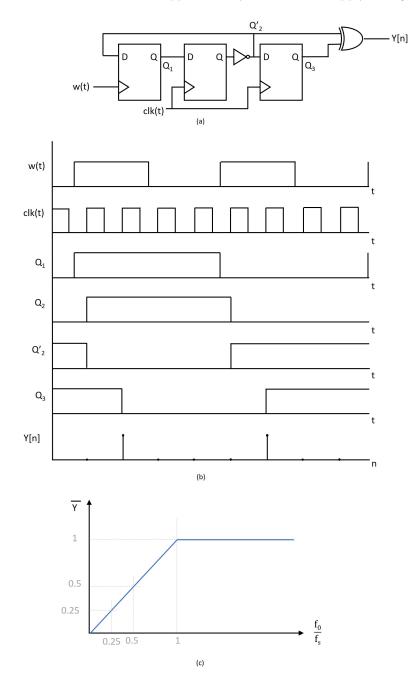

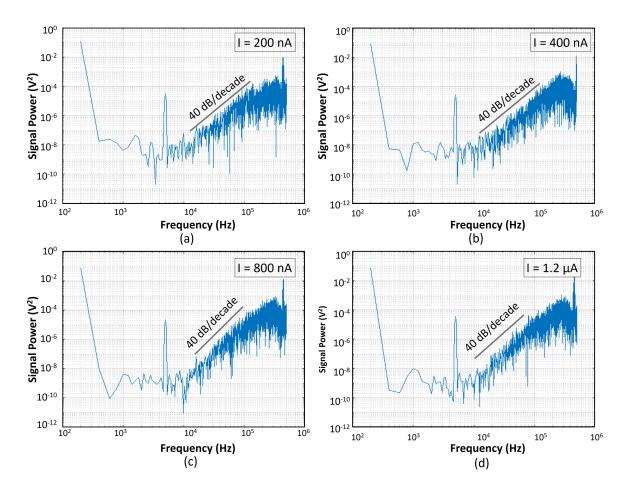

| 3.12                                                                                                               | PSD obtained from the VCO quantizer model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31                                                                                             |

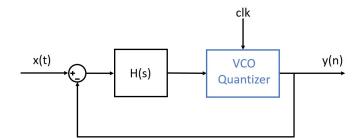

| 3.13                                                                                                               | Block diagram of VCO based $\Sigma\Delta$ ADC $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32                                                                                             |

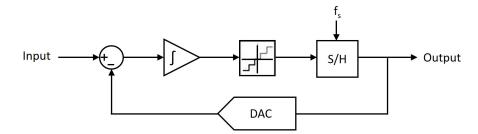

| 4.1                                                                                                                | Block diagram of first order $\Sigma\Delta$ modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                                                                                             |

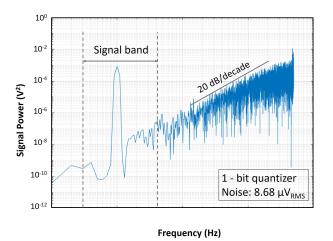

| 4.2                                                                                                                | PSD of first order $\Sigma\Delta$ ADC $\hfill \hfill $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34                                                                                             |

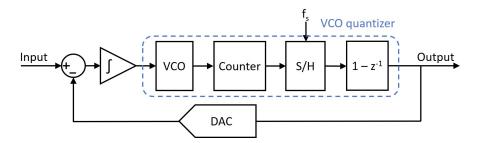

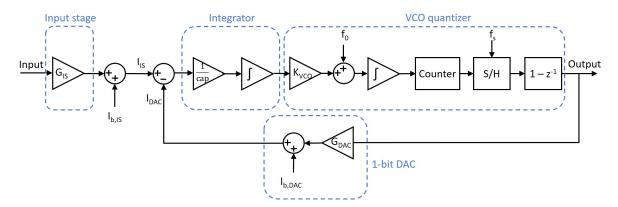

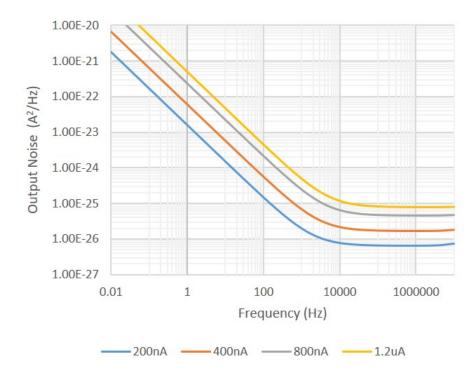

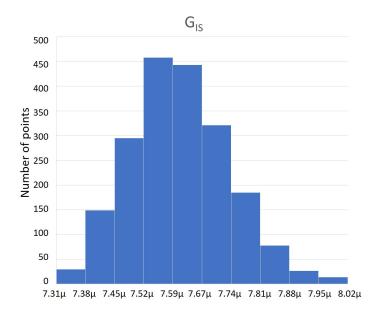

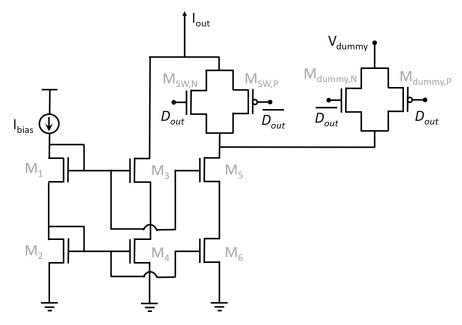

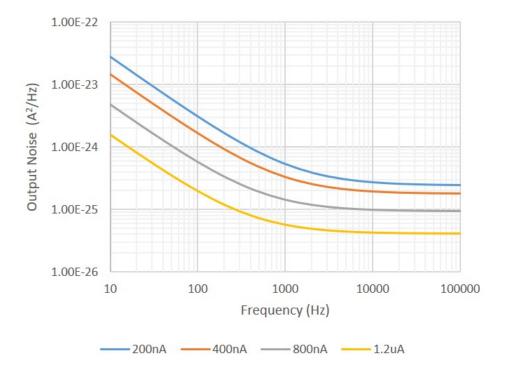

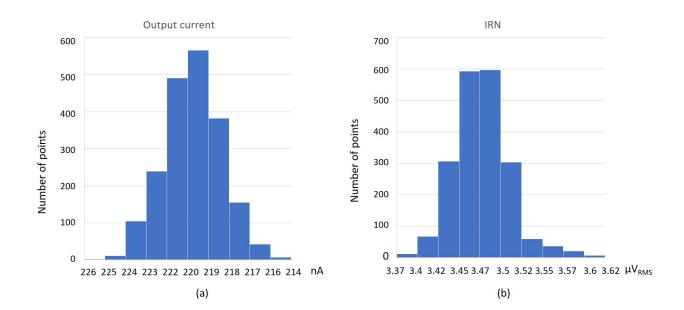

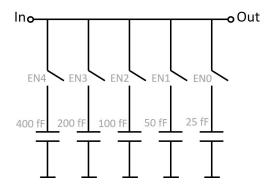

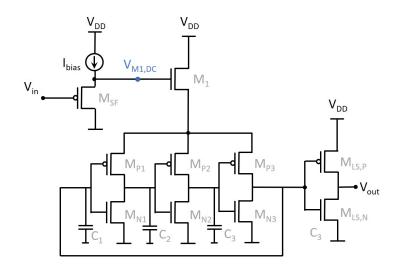

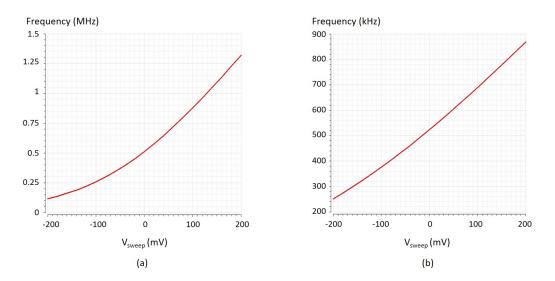

| 4.3                                                                                                                | Block diagram of VCO based $\Sigma\Delta$ modulator $\hdots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35                                                                                             |