# Quantum Computer Microarchitecture for color centers in diamond

Q. van Wingerden

by

Q. van Wingerden

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Thursday, August 26 2021 at 14:00.

Student number:4476913Project duration:Nov 1, 2020 – July 1, 2021Thesis committee:Prof. dr. ir. J.S.S.M Wong,<br/>Dr. F. Sebastiano,<br/>Dr. S. Feld,TU Delft, supervisor<br/>TU Delft

This thesis is confidential and cannot be made public until August 26, 2021.

An electronic version of this thesis is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

# Abstract

Nowadays, the need for better and faster computing searches for solutions in the field of quantum computing. It is believed that quantum computing can and will surpass conventional, classical computing. When quantum computing surpasses classical computing, it is called quantum supremacy. There are many different projects that use different quantum technologies aim to achieve quantum supremacy, such as projects from Google and Intel. In this thesis, the reader is introduced to a new project: the Fujitsu Project. The project is a collaboration between TU Delft and Fujitsu and has the goal of fabricating a new distributed quantum quantum computer based on color centers in diamond. The focus of the thesis is the definition of the microarchitecture.

The quantum computer stack is explained in detail. Precise and robust definitions for each of the seven layers of the quantum computer stack are given, where the definition of the microarchitecure is most important. A microarchitecture is defined as the list of instructions of the lowest level before entering control electronics. To define the diamond microarchitecture, a set of goals have to be completed. Other architectures such as QuTech's QuMA and QuTech's Central Controller were identified and analyzed. Combined with the requirements of the overall diamond system architecture as defined by the project, a list of requirements for the microarchitecture is created. Using these requirements, a Quantum Instruction Set Architecture (QISA) and a microarchitecture are defined.

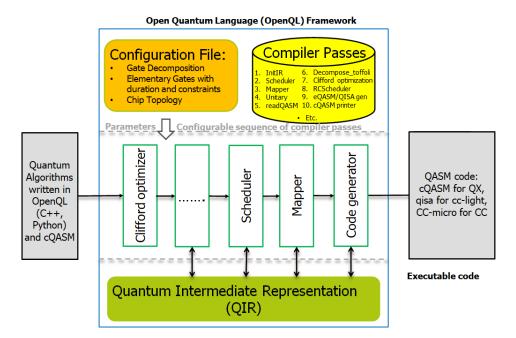

Based on the defined QISA and microarchitecture, a compiler is designed. The compiler is made in OpenQL. OpenQL is a framework for high-level quantum programming that targets different quantum computing platforms. The main task of the compiler is to translate high-level quantum algorithms, expressed in a high-level quantum programming language (C++/Python APIs), to quantum microcode. The quantum microcode consists of instructions that are defined in the microarchitecture.

The QISA, microarchitecture and compiler are verified against the requirements that are set at the beginning of their respective definition phases. The microarchitecture supports for all gates that are part of cQASM 1.0. In addition, it supports all diamond color center specific protocols and rules. The compiler supports all instructions from cQASM as well. Moreover, the compiler supports all standard (gate) instructions and diamond specific instructions through OpenQL's Python API.

The work is intended to be a solid baseline, where the future of the project can rely and improve upon. Possible improvements could be the adaption of the microarchitecture to the growth of the number of controlled qubits per controller, the parallelization of the microarchitecture instructions to improve instruction throughput, and alignment with the quantum network group. The compiler can also be improved with for example enhanced scheduling, differentiation between qubit types and an entanglement library. The next step in the design of the microarchitecture will be the design of a microarchitecture simulator, which takes the microcode as input and simulates the hardware architecture.

# Preface

Starting my studies at TU Delft I always had affinity with computer. I always wanted to know how electronics worked and how computers worked from the inside. Because of this, I started my bachelor Electrical Engineering at the TU Delft. After completing the BSc, I pursued a master's degree in Computer Engineering to learn more about how computers work. Nearing the end of the first year of this enjoyable master it was time to search for a thesis project. I had gathered interest for quantum computing and, *Stephan Wong* answered my email with an interesting project about quantum computer microarchitectures. After an online meeting we decided that I would take the project.

Now, a year later, the thesis project has come to an end. I have learned many things, not only about quantum computing and microarchitectures, but also how to write, present, and have meaningful discussions with other people in (online) meetings. I am proud to have completed the thesis, but not without the help of the following people:

First, I would like to thank my supervisor *Stephan Wong* for always being critical and getting the most out of me. He challenged me in multiple ways - by having me give presentations to large crowds in online meetings or by reviewing my thesis time after time until it met the requirements.

Second, I would like to thank *my parents* for supporting me and always being there to talk to. They taught me valuable skills when I was growing up and that helped me complete the thesis.

Third, I would like to thank *Jeroen van Straten* for assiting me with all the work I have done with the OpenQL compiler. Jeroen was one of the maintainers of OpenQL and helped me understand the program and guided me through adding my own code to the framework. I could not have built the compiler as is without Jeroen. I would also like to thank *Luc Enthoven* for the valuable discussions about the workflow of the quantum computer and about the requirements of the microarchitecture. I also would like to thank *Erwin van Zwet* and *Jaco Morits* from TNO that helped form the blueprint for the overall system architecture and thus a blueprint for the microarchitecture.

Fourth, I would like to thank my friends for always being there when I had something to complain about or when I had good results that I could share with them. I want to thank two people in special that helped me do so, namely *Thijs Timmer* and *Suzanne Brand*. I could not have done this project without you.

I hope you enjoy reading this thesis as much as I had fun reading, learning from, thinking, programming, reviewing and submitting it.

> Q. van Wingerden Ridderkerk August 26, 2021

# Contents

| 1 | Intro       | oductio | n                                        | 1    |

|---|-------------|---------|------------------------------------------|------|

| - | 1.1         |         | jitsu Project                            | . 1  |

|   | 1.2         |         | n Statement.                             |      |

|   | 1.3         |         | lology                                   |      |

|   | 1.4         |         | Overview                                 |      |

| _ |             |         |                                          |      |

| 2 |             | kgroun  |                                          | 4    |

|   | 2.1         |         |                                          |      |

|   |             | 2.1.1   | Qubits                                   |      |

|   |             | 2.1.2   | Gates                                    |      |

|   |             |         | Quantum Circuits and Algorithms          |      |

|   | 2.2         |         | Tech Quantum Computer Stack              |      |

|   |             | 2.2.1   | Quantum Algorithm.                       |      |

|   |             | 2.2.2   | Programming Paradigm & Languages         |      |

|   |             | 2.2.3   | Quantum Arithmetic, Runtime and Compiler |      |

|   |             | 2.2.4   | Quantum Instruction Set Architecture     |      |

|   |             | 2.2.5   | Microarchitecture                        |      |

|   |             | 2.2.6   | Quantum to Classical.                    |      |

|   |             | 2.2.7   | Quantum Chip                             |      |

|   | 2.3         |         | Iters in Diamond.                        |      |

|   |             | 2.3.1   | Other types of Qubit                     | . 9  |

|   | 2.4         | Quant   | Im Computer Microarchitectures           | . 10 |

|   |             | 2.4.1   | QuMA                                     | . 10 |

|   |             | 2.4.2   | QuTech Central Controller                | . 14 |

|   |             | 2.4.3   | Central Controller.                      | . 15 |

|   |             | 2.4.4   | CC-Spin                                  | . 18 |

|   | 2.5         | Quant   | Im Networking.                           | . 19 |

|   |             | 2.5.1   | Quantum Communication                    | . 19 |

|   |             | 2.5.2   | Entanglement and Teleportation           | . 20 |

|   |             | 2.5.3   | Quantum Tools for Networking.            |      |

|   | 2.6         |         | L                                        |      |

|   | 2.7         |         | sion                                     |      |

| _ |             |         |                                          |      |

| 3 |             |         | licroarchitecture                        | 23   |

|   | 3.1         |         | nd Microarchitecture Requirements        |      |

|   | 3.2         |         |                                          |      |

|   | 3.3         |         | Im Instruction Set Architecture (QISA).  |      |

|   |             |         | Refining of the QISA                     |      |

|   | 3.4         |         | ed QISA and microachitecture             |      |

|   |             | 3.4.1   | Supported High-Level Instructions.       |      |

|   |             |         | Example of decomposition                 |      |

|   | 3.5         | Conclu  | sion                                     | . 31 |

| 4 | Tool        |         |                                          | 33   |

| - | 4.1         |         | L                                        |      |

|   |             |         | er Design                                |      |

|   | <b>7.</b> ∠ |         | Compiler Requirements                    |      |

|   |             |         | Diamond backend in OpenQL                |      |

|   |             |         | Microcode Translator Pass.               |      |

|   |             | 4.∠.J   |                                          | . 34 |

|   |                          |                                                                                                                                        | the Compiler                                                                                                                                                                                                                                                                                                                                                |                                       |       |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |                                       |          |   |                                                                                                                            |

|---|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------|----------|---|----------------------------------------------------------------------------------------------------------------------------|

| 5 |                          | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5                                                                                              | and microarchitecture .<br>Deterministic and precise control of the control electronics<br>Classical instructions for flow control .<br>Basic quantum gate instructions (X, Y, Z, S and T)<br>cQASM Gateset                                                                                                                                                 |                                       | · · · | <br><br><br>                                                                                             | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 | · · ·                                 | <br><br> |   | . 40<br>. 40<br>. 41<br>. 41<br>. 41                                                                                       |

|   | 5.3                      | Conclu                                                                                                                                 | ision                                                                                                                                                                                                                                                                                                                                                       | •                                     |       |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                               | • •                                   |          | • | . 45                                                                                                                       |

| 6 | Con<br>6.1<br>6.2<br>6.3 | Main C                                                                                                                                 | ary                                                                                                                                                                                                                                                                                                                                                         |                                       | · ·   | <br><br><br>                                                                                             | <br><br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                 | <br><br>                              | <br><br> |   | . 48<br>. 49<br>. 49<br>. 49<br>. 50                                                                                       |

| Α |                          |                                                                                                                                        | tecture Documentation                                                                                                                                                                                                                                                                                                                                       |                                       |       |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |                                       |          |   | 52                                                                                                                         |

|   |                          | A.1.1<br>A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6<br>A.1.7<br>A.1.8<br>A.1.9<br>A.1.10<br>A.1.11<br>microa<br>A.2.1<br>A.2.2<br>A.2.3 | structions.<br>Qubit Gate<br>Qubit Rotation<br>Qubit Readout<br>Qubit Readout<br>Qubit Initialize.<br>nop<br>Entanglement.<br>Nuclear Spin Operations.<br>Biasing and Checks<br>Calibration<br>Timing.<br>Standard (Classical) Instructions<br>Timing.<br>Additional Instructions<br>Standard (Classical) Instructions<br>Standard (Classical) Instructions |                                       |       | · · ·<br>· · · | <ul> <li>.</li> <li>.&lt;</li></ul> | ·<br>·<br>·<br>·<br>·<br>·<br>· | · · · · · · · · · · · · · · · · · · · |          |   | . 55<br>. 55<br>. 55<br>. 55<br>. 56<br>. 56<br>. 56<br>. 56                                                               |

| В |                          |                                                                                                                                        | ition Microcode                                                                                                                                                                                                                                                                                                                                             |                                       |       |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |                                       |          |   | 62                                                                                                                         |

|   | B.10                     | Initializ<br>qentar<br>NVent<br>sweep<br>decou<br>calcula<br>calcula                                                                   | irrement.                                                                                                                                                                                                                                                                                                                                                   | · · · · · · · · · · · · · · · · · · · | · · · | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·                                                                | · · ·<br>· · ·<br>· · ·<br>· · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                 | · · · · · · · · · · · · · · · · · · · | · · ·    |   | <ul> <li>. 62</li> <li>. 62</li> <li>. 63</li> <li>. 63</li> <li>. 63</li> <li>. 64</li> <li>. 64</li> <li>. 64</li> </ul> |

|   |                          |                                                                                                                                        | lfpi                                                                                                                                                                                                                                                                                                                                                        |                                       |       |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |                                       |          |   |                                                                                                                            |

| С   | List  | of Sup                                | ported Functions and Gates of the Compiler | 67 |

|-----|-------|---------------------------------------|--------------------------------------------|----|

|     | C.1   | Initiali                              | zation                                     | 67 |

|     |       | C.1.1                                 | prep_z                                     | 67 |

|     |       | C.1.2                                 | prep_x                                     | 67 |

|     |       | C.1.3                                 | prep_y                                     | 67 |

|     |       | C.1.4                                 | initialize                                 | 67 |

|     | C.2   | Measu                                 | urement                                    | 68 |

|     |       | C.2.1                                 | measure                                    | 68 |

|     |       | C.2.2                                 | measure_z                                  | 68 |

|     |       | C.2.3                                 | measure_x                                  | 68 |

|     |       | C.2.4                                 | measure_y                                  | 68 |

|     | C.3   | Single                                | Qubit Gates                                | 68 |

|     | C.4   | Two C                                 | Qubit Gates                                | 68 |

|     | C.5   | Three                                 | Qubit Gate                                 | 68 |

|     | C.6   | Diamo                                 | ond Calibration                            | 69 |

|     |       | C.6.1                                 | cal_measure                                | 69 |

|     |       | C.6.2                                 | cal_pi                                     | 69 |

|     |       | C.6.3                                 | cal_halfpi                                 | 69 |

|     |       | C.6.4                                 | decouple                                   | 69 |

|     |       | C.6.5                                 | Custom Rotations                           | 69 |

|     |       | C.6.6                                 | rz                                         | 69 |

|     |       | C.6.7                                 | rx                                         | 69 |

|     |       | C.6.8                                 | ry                                         | 69 |

|     |       | C.6.9                                 | cr                                         | 69 |

|     |       | C.6.10                                | )                                          | 70 |

|     | C.7   | Diamo                                 | ond Protocols and Sequences                | 70 |

|     |       | C.7.1                                 | •••••••••••••••••••••••••••••••••••••••    |    |

|     |       | C.7.2                                 | rabi_check                                 |    |

|     |       | C.7.3                                 | excite_mw                                  |    |

|     |       | C.7.4                                 |                                            |    |

|     |       | C.7.5                                 | nventangle                                 |    |

|     |       | C.7.6                                 | memswap                                    |    |

|     |       | C.7.7                                 | sweep_bias                                 | 71 |

|     | C.8   | · · · · · · · · · · · · · · · · · · · | ]                                          | 71 |

|     |       |                                       |                                            |    |

|     |       |                                       | qnop                                       |    |

|     | C.9   |                                       | cal Support Functions                      |    |

|     |       |                                       | calculate_current                          |    |

|     |       | C.9.2                                 | calculate_voltage                          | 71 |

| Bil | bliog | raphy                                 |                                            | 72 |

# Bibliography

# Introduction

Nowadays, in the search for better and faster computing, there is a very large interest in quantum computing. It is believed that quantum computing can solve some problems exponentially quicker using its quantum technology than with its classical counterpart [1]. When quantum computing surpasses classical computing, it is called quantum supremacy. To achieve quantum supremacy, quantum algorithms are needed. An example of such an algorithm is Shor's algorithm [2], which is designed to factor a number N into its prime factors p and q using the power of the Quantum Fourier Transform (QFT). Shor's algorithm can be used to break RSA-encryption because RSA assumes that it is a hard problem to factor a large number N into its prime integers p and q. Another well-known example is Grover's Search Algorithm [3], which provides a quadratic speedup in the unstructured search. Unstructured search is that out of *N* options the correct option  $\omega$  has to be picked. Classically, at best one try is needed and at worst *N* tries. On average,  $\frac{N}{2}$  tries are needed. With Grover's algorithm,  $\sqrt{N}$  tries are needed, thus providing quadratic speedup.

The field of quantum computing is rapidly evolving. Several quantum computers have been made already, such as the systems by D-Wave [4], which uses quantum annealing, or Sycamore, the 54-qubit quantum processor from Google that claims it showed quantum supremacy [5]. Within QuTech and through the Quantum Inspire platform [6], two quantum accelerators (Spin-2 and Starmon-5) are made publicly available. More examples are the Quantum Processing Units (QPUs) from Intel, Microsoft and IBM, but there are many more QPUs in existence.

Each of these QPUs work with different types of quantum bits (qubits), which are the physical entities that are used to perform calculations on. The qubits are fundamental particles where quantum computers are based on. There are many different technologies available for the creation of different types of qubits. Examples of these types of qubits are transmon, majorana fermion, quantum dots and color centers in diamond (such as NV-centers) [7].

This thesis documents the (beginning of) the development of a microarchitecture for quantum computing using color centers in diamond. This Chapter will introduce the project. The thesis is part of the Fujitsu Project, that is introduced in Section 1.1. After that, the problem statement is introduced in Section 1.2 and the project methodology is discussed in Section 1.3. The Chapter ends with a overview of the thesis in Section 1.4.

# 1.1. The Fujitsu Project

The Fujitsu Project is a collaboration between TU Delft and Fujitsu Limited. The project has a duration of five years, and the goal of is to develop a distributed quantum computer based on color centers in diamond. Color centers contain a particle, typically an electron, that has a spin and thus can be used as a qubit. The goal is to develop and fabricate a *scalable* quantum computer using these qubits. Because of the modular nature of the architecture, retaining scalability should be expected. In addition to that, the color center qubits have special characteristics compared to other types of qubit<sup>1</sup>. In contrast to other qubits, color center qubits can function at room temperature. This means less cooling and thus

<sup>&</sup>lt;sup>1</sup>This also depends on the type of color center qubit. At Fujitsu, NV-centers as well as SnV-centers are used.

less energy consumption. In addition, the qubits have long coherence times. This means that the qubit can hold its state longer, which is beneficial for quantum computing. Color center qubits are *ODMR*, which stands for Optically Detected Magnetic Resonance. This means that the qubits can be read out with lasers and photondetectors, and can be controlled by magnetic fields. Using these qubits, there are two important goals that the project aims to achieve:

- 1. Demonstration of scalable fabrication of the integrated circuits that contain the qubit, the control electronics and other parts needed to function.

- 2. Demonstration of a unit with a 20 qubits operating with a high fidelity.

# **1.2. Problem Statement**

For the Fujitsu Project, a microarchitecure needs to be developed that will work with the diamond spin qubits. It should interface with the control electronics that are directly connected to the qubits. The following research question arises:

How is a microarchitecture for a quantum computer based on color centers in diamond defined?

To answer this research question, three goals have been set:

- 1. Define the overarching Quantum Instruction Set Architecture (QISA) that interfaces with the higher layers of the quantum computer stack.

- 2. Define the microarchitecture.

- 3. Build a compiler that is able to translate a quantum algorithm to quantum microcode, defined by the microarchitecture, using the higher layer and interfaced with an existing compiler framework.

# 1.3. Methodology

To complete these goals and answer the research question, a number of tasks are performed:

- 1. Identify how other quantum microarchitectures are defined.

- 2. Determine the requirements of the diamond microarchitecture.

- 3. Define the microarchitecture.

- 4. Fabricate a simple compiler that compiles an algorithm to diamond-specific assembly code.

- 5. Verify the results by comparing them to their requirements.

## **1.4. Thesis Overview**

In Chapter 2, the background material needed to understand the rest of the thesis is provided. First, it covers basics, such as quantum information theory. Second, it covers the quantum computer stack that is defined within QuTech. Third, NV-centers, a type of color center in diamond, are discussed. Fourth, the reader is introduced to quantum computer microarchitectures. An overview of developments in quantum networking is given in the following section. Finally, an overview about OpenQL, the framework for high-level quantum programming in C++/Python, is given.

In Chapter 3, the design of the microarchitecture is discussed. It will cover what the microarchitecture needs to be able to do. After that, an overview of the system where the microarchitecture is being designed for is given. The design process of the QISA as well as the microarchitecture is discussed. The finalized version of both the QISA and the microarchitecture is presented. At the end of the chapter, decompositions from the QISA to the microarchitecture are presented.

In Chapter 4, we discuss the compiler tool that translates high-level quantum algorithms to lowlevel assembly code (microcode). OpenQL is briefly refreshed upon. After that, the requirements of the design and the design itself are presented. At the end of the chapter it is explained how to use the compiler tool.

In Chapter 5, we present the verification of the designed microarchitecture. It is split in two parts. The first part discusses the completeness of the microarchitecture. It compares its functions with the

requirements that are stated in Chapter 3. In the second part of the Chapter, the compiler is verified against the requirements introduced in Chapter 4.

In Chapter 6, we conclude the thesis by taking a look at at the work that is done. A summary is given and the research question is answered using the goals and tasks defined in this introduction. Furthermore, the main contributions are listed as well as ideas and suggestions for future work.

Appendix A documents the documentation for reading and using the defined microarchitecture. Appendix B presents details about decompositions that are explained in Chapter 3.

Appendix C contains the documentation for the compiler tool.

# $\sum$

# Background

This chapter will present all the information that is needed to understand the thesis work. In Section 2.1, the theory behind quantum computing, also called quantum information theory, is briefly touched upon. Here, qubits are explained, just as basic quantum operations, gates and how to build circuits and algorithms. Then in Section 2.2, the QuTech quantum computer stack is explained. The stack is an important reference for the design of quantum computers. In this section, the definition of a microarchitecture is given. After the stack has been presented, NV-centers in diamond will be explained in Section 2.3. Section 2.4 will discuss quantum computer microarchitectures. After that, a short introduction to quantum networking is presented in Section 2.5. Finally, in Section 2.6, OpenQL, a framework for high-level quantum programming, is introduced.

# 2.1. Quantum Information Theory

This section will give a short summary of quantum information theory. It will cover quantum bits (qubits) by explaining what they are and how they differ from classical bits. The section will also cover quantum gates (operations on the qubits) and quantum algorithms (quantum programs).

### 2.1.1. Qubits

A qubit is different from a classical bit. Where a classical bit can be either in state '0' or '1', a qubit can be in a linear superposition of these states. The notation of qubits is called the *Dirac* notation [8]. This can be illustrated by the following formula:

$$|\Psi\rangle = \alpha |0\rangle + \beta |1\rangle$$

Here, it can be seen that the qubit consists of state  $|0\rangle$  by part  $\alpha$  and state  $|1\rangle$  by part  $\beta$ . However, since a qubit must be 'complete', the chance of the qubit existing must be 1. Therefore, it must hold that  $|\alpha|^2 + |\beta|^2 = 1$ .

There are a other rules that the qubits must follow. One of the most important ones is that when you measure a qubit, the outcome is not deterministic. Measuring a qubit is a probabilistic process. For example, if  $\alpha$  and  $\beta$  have the same value (which is valid for a value of  $\frac{1}{\sqrt{2}}$ ), the chance of measuring  $|0\rangle$  and  $|1\rangle$  is the same, as  $|\frac{1}{\sqrt{2}}|^2 = 0.5$ . If measuring that specific qubit and the outcome is  $|0\rangle$ , then the full state becomes  $|\Psi\rangle = |0\rangle$ . This means that the qubit state collapses to either  $|0\rangle$  or  $|1\rangle$ , depending on the measurement result. In the case of the example, the state has been collapsed to the zero-state.

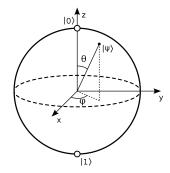

A good way to visualize the state of a qubit is by using the Bloch-sphere, depicted in Figure 2.1. Note that the Bloch-sphere visualization only works for a single qubit. The qubit will be anywhere on the edge of the sphere. It can help to understand what the state of the qubit is when applying the quantum gates in algorithms. It also means that the formula from earlier can be rewritten as:

$$\left|\Psi\right\rangle = cos(\frac{\theta}{2})\left|0\right\rangle + e^{i\phi}sin(\frac{\theta}{2})\left|1\right\rangle$$

In addition to the previous notations, there is also a notation that is particularly helpful when doing (hand) calculations on qubits when they are in the so-called Clifford states, which are found on the Bloch-sphere as +z, -z, +x, -x, +y and -y axis.

Figure 2.1: The Bloch-sphere [9].

The Clifford states are:

$1. |0\rangle \equiv \begin{bmatrix} 1\\0 \end{bmatrix} \qquad 4. \frac{1}{\sqrt{2}}(|0\rangle - |1\rangle \equiv |-\rangle) \equiv \begin{bmatrix} \frac{1}{\sqrt{2}}\\ -\frac{1}{\sqrt{2}} \end{bmatrix}$  $2. |1\rangle \equiv \begin{bmatrix} 0\\1 \end{bmatrix} \qquad 5. \frac{1}{\sqrt{2}}(|0\rangle + i|1\rangle \equiv |+i\rangle) \equiv \begin{bmatrix} \frac{1}{\sqrt{2}}\\ \frac{i}{\sqrt{2}} \end{bmatrix}$  $3. \frac{1}{\sqrt{2}}(|0\rangle + |1\rangle) \equiv |+\rangle \equiv \begin{bmatrix} \frac{1}{\sqrt{2}}\\ \frac{1}{\sqrt{2}} \end{bmatrix} \qquad 6. \frac{1}{\sqrt{2}}(|0\rangle - i|1\rangle \equiv |-i\rangle) \equiv \begin{bmatrix} \frac{1}{\sqrt{2}}\\ -\frac{i}{\sqrt{2}} \end{bmatrix}$

By representing the states in their vector notations, they can be transformed into new states by using linear algebra.

Until now, only single qubit states are presented. However, multiple qubits can share a state together. For example, when two qubits share a state together, it can be represented like the following:

$$|\Psi\rangle = \alpha_{00} |00\rangle + \alpha_{01} |01\rangle + \alpha_{10} |10\rangle + \alpha_{11} |11\rangle$$

The rules that apply to a single qubit state still hold. Multiple qubit states are very useful because they allow for the use of quantum entanglement. Entanglement can be seen as the quantummechanical connection between two qubits. It can be seen as a *resource* [8] that plays a key role in quantum algorithms.

#### 2.1.2. Gates

Gates can also be represented by their vector notation. This makes that if the X-gate (quantum equivalent of the NOT-gate) is applied, the calculation becomes:

$$X |0\rangle = \begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix} \begin{bmatrix} 1 \\ 0 \end{bmatrix} = \begin{bmatrix} 0 \\ 1 \end{bmatrix} = |1\rangle$$

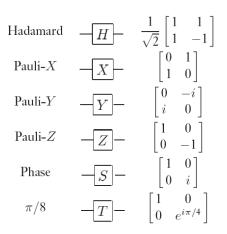

The X-gate is given by the first (2x2) matrix. The qubit itself is represented by the second (2x1) matrix. An overview of the most frequently used gates are given in Figure 2.2, together with their circuit representation. The Hadamard gate, H, maps a qubit into equal chances of measurement of  $|0\rangle$  or  $|1\rangle$ , creating superposition. The X, Y and Z gates rotate the qubit around the specified axis (x, y or z) with  $\pi$  radians. The S and T gate both shift the phase of the qubit over the Z-axis, with  $\frac{\pi}{2}$  and  $\frac{\pi}{4}$  respectively. Gates are the building blocks of quantum algorithms, as illustrated in the next section. It is worth noting that some gates, such as the Pauli-X gate, can be written as a HZH gate. Other examples are Pauli-Y, which equals iXZ and Pauli-Z that equals HXH.

Figure 2.2: Overview of qubit gates [8, Fig. 4.2]

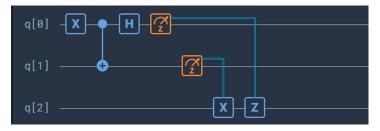

#### 2.1.3. Quantum Circuits and Algorithms

Quantum algorithms are described using discrete time-based schematics. An example can be found in Figure 2.3 where the state of the top qubit is teleported to the bottom qubit. As can be seen, multiple gates from Figure 2.2 are present in the circuit together with two measurements. The majority of quantum circuits and algorithms are visualized like this. In the Figure, there is an X-gate on qubit 0, followed by CNOT with qubit 0 as control and qubit 1 as target. Then, a Hadamard gate is performed on qubit 0 followed by a measurement on qubits 0 and 1. Depending on the outcome of the measurements, an X gate and a Z gate are performed on qubit 2. The example is explained in more detail in [8, Section 1.3.7].

Figure 2.3: Teleportation Circuit. Made with Quantum Inspire [6].

# 2.2. The QuTech Quantum Computer Stack

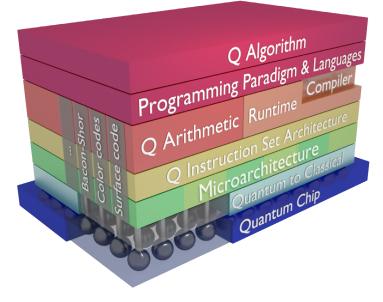

As this thesis focuses on the definition of a microarchitecture for a quantum computer based on diamonds, it is important to get the definitions of said microarchitecture correct. A clear definition of what the microarchitecture is already exists for classical computing systems and so the same must be done for quantum computing systems. A clear definition will add clarity for all who are involved in the development of quantum computers, as different research facilities and different quantum computing companies might have different definitions right now. Based on work that has been done before, an abstract quantum computer stack can be created, as depicted in Figure 2.4. The quantum computer stack presents an overview of the different layers of a quantum computer. It can be observed that there are a total of seven layers. In this section, the definition of each layer is given, starting with the top layer and working to the bottom layer.

#### 2.2.1. Quantum Algorithm

This layer contains the definition of the quantum algorithm. Contrary to classical algorithms, where the data input and data output set are defined, as well as the operations that transform the input data to the output data, a quantum algorithm consists of a set of discrete-time gates operating on qubits as depicted in Figure 2.3. Examples for use cases are data encryption, finding a new molecule or synthesizing a

Figure 2.4: The QuTech system stack. Q stands for Quantum.

new vaccine for COVID-19 (caused by the SARS-CoV-2 virus). The quantum algorithms have the goal of speeding up a use case using quantum computation characteristics, such as superposition or entanglement. Examples of well-known quantum algorithms are Shor's Algorithm [2] or Grover's Search Algorithm [3], as explained in the introduction of the thesis.

## 2.2.2. Programming Paradigm & Languages

In this layer, the quantum algorithm defined in the Q Algorithm layer (for example: Shor's Algorithm) gets transformed into a specification using a high-level quantum programming language. There are different high-level quantum programming languages available today, such as Scaffold, Q, Q#, Quipper, LIQUI) and Project Q, see Figure 2.5. For some of these languages, compilers have been written. For example, to compile Scaffold, the ScaffCC compiler and analysis framework is used. Here at QuTech, we use the OpenQL framework, which uses a Python API or a C++ API as algorithm input. OpenQL is currently used for the QuTech Central Controller and for the hardware backends that can be programmed through Quantum Inspire as well [6]. More information about OpenQL can be found in Section 2.6 or at openql.readthedocs.org.

Figure 2.5: Different programming languages for quantum computing.

### 2.2.3. Quantum Arithmetic, Runtime and Compiler

At this layer, the initial translation from a quantum algorithm towards the signals used to control the electronics controlling the qubits is performed. For this purpose, a set of quantum arithmetic operations is assumed and the target outcome of the compiler is a program that is composed of instructions defined in the QISA. Similar to traditional compilers, the runtime refers to a high-level scheduler that is needed for a larger multi-qubit or multi-node (with multiple qubits per node) system. The runtime is envisioned to be programmed using instructions from the QISA.

#### 2.2.4. Quantum Instruction Set Architecture

The QISA can be seen as the bridge between (high-level) quantum algorithms, expressed using quantum programming languages or quantum arithmetic operations, and the microarchitecure level below. The layer defines the functionality of the quantum computer expressed as a list of quantum instructions similar to the ISA of a traditional computer. This includes instructions for the functionality of a qubit as well as instructions for the necessary control logic, including classical instructions. These classical instructions are also used by the runtime to perform scheduling between qubits. The definition of the QISA is important, as a well defined QISA allows for adaptability and flexibility of the functions of the quantum computer.

#### 2.2.5. Microarchitecture

The goal of the microarchitecture is to execute QISA instructions generated by the higher layers in a deterministic manner with ample run-time support. It should, just like the QISA, support both quantum operations as classical operations. The microarchitecure is defined as a collection of simple(r) micro-instructions of the lowest level that implements the functionalities of the QISA by controlling the complex electronics that control qubits.

#### 2.2.6. Quantum to Classical

The Quantum to Classical layer, also called the control electronics layer, is responsible for driving the physical qubits. It is located very close to the qubits. The layer is controlled by the microarchitecure layer. Some examples of control electronics are Digital-Analog Converters (DACs), Analog-Digital Converters (ADCs), Arbitrary Waveform Generators (AWGs) and Ultra-High Frequency Quantum Analyzers (UHF-QAs) as well as relays, optical switches and current sources. These *all* need to be properly controlled to ensure correct and full functionality of the quantum computer.

#### 2.2.7. Quantum Chip

The bottom layer of the stack would be the quantum chip layer, or the qubits themselves. There are different types of qubit available (superconducting, spin, NV-centers and more) and each type demands different requirements from the higher layers.

# 2.3. NV-centers in Diamond

There are many ways to implement a qubit available today. Each type of qubit has its own advantages and disadvantages. The most known types of qubit are superconducting qubits, spin qubits, majorana-fermion qubits and diamond color center qubits [7]. In this thesis, the focus lies on the fourth qubit type: color center qubits. Within these color center qubits, the focus lies on NV-centers.

A NV-center is an open space in diamond caused by the replacement of a carbon atom with a nitrogen atom in the structure of the diamond. The open space, or vacancy, is occupied by a particle that can act as a qubit. These vacancies can form naturally or be formed by humans in artificial diamonds [10]. The needed structure can be made using different approaches. One of these approaches could be to try to "grow chemical vapor-deposited diamond onto etchable substrates" [11].

As said previously, an NV-center is a type of color center, A color center is an impurity or defect that gives emeralds and rubies their color [11]. Diamond is the optimal environment for an artificial atom because of the thermal and mechanical properties of the material. Also, there are very few nuclear-spins present in diamond. The nuclear spins that are present can even be used as an advantage.

As the particle inside the vacancy can be used as a qubit, is must be able to have superposition of quantum states. It is also important that the particle has a long coherence time and this is usually achieved by isolating the particle from uncontrolled perturbations in the form of noise [10].

In [10], it is stated that all of the previously mentioned properties are in fact satisfied by the NVcenter. Today, it is widely known that NV-centers can be used to generate, measure and control qubits, but at the time of [10] this was not trivial.

These particles in the vacancy, from now on qubits, can be controlled with both magnetic as optical interactions [10]. Readout of the qubit is can be done optically. This is supported by the fact that the ground state of the NV-center shines brighter than the excited state [11]. This is one of the properties of color centers: they react strongly with microwaves and optical fields. Because of these properties, the qubit can be classified as *Optically Detected Magnetic Resonance*, or ODMR.

The created diamond and corresponding NV-center are made purer and purer, enhancing the lifetime of the qubit. In 2013, [10] shows that this can be extended to the millisecond range by removing spins, both nuclear and electronic. These spins normally act as sources of decoherence. Thus, by minimizing these sources the coherence time of the qubit increases. However, not all material spins are necessarily bad. It is possible to create Quantum Memory by using the nuclear spin of the carbon atoms to store data without losing the state because of entanglement generation [12]. In particular, natural material contains spins with weak hyperfine couplings, a magnetic coupling between atoms/electrons, between 20-50KHz. If these coupling strengths are weak enough (<10KHz), the spins can survive up to hundreds of entanglement attempts [12]. The Fujitsu Project aims to use the nuclear spins surrounding the qubit as additional qubits.

These nearby nuclear carbon-atom spins can also be used to implement Quantum Error Correction (QEC) [13]. The authors use the electron found in the NV-center to initialize, control and read out the carbon-13 spins found close to the center. They have implemented 1- and 2-qubit gates with high fidelity, as well as a three-qubit QEC [13]. This supports the statement that nuclear spins around the qubit do not necessarily influence the NV-center qubit system badly.

It is important to stress that not every NV-center is the same. Thus, not every trapped particle is the same. There are differences in brightness of emitted light and in decay rate [14]. Therefore, a metric has to be introduced which will indicate the efficiency of a NV-center. This is done in [14]. Quantum Efficiency, or QE, is quantified experimentally. They measured between 30 and 40 NV-centers and mapped their brightness. A broad distribution was found in accordance with previous reports. They found that the decay rate is influenced by two parts: Radiative and Nonradiative decay rates. NV-centers have a QE of between 10 and 90 percent [14].

Comparing the NV qubit with other types of qubits, we see that the NV electron spin lifetimes are much longer, about a couple of milliseconds even at room temperature. Other types of qubit are usually cooled down to less than 4K to be useful.

However, the biggest challenge that comes with NV-center based qubits is its scalability. The scalability of the qubits is very hard to develop well. This is mostly because the quality of the devices and materials is nowhere near it should be right now. On top of that, optical coupling between qubits is also needed. Optical coupling between qubits would mean they can also be coupled (and subsequently entangled) over long distances [11], resulting in a quantum network.

There are also ideas to combine multiple types of qubits into one system. [10] names the combination of superconducting qubits (which are fast and high-controllable) and NV-qubits (to act as quantum memory and transducers).

Other types of color centers are also present in diamond. Research has been done to other types as NV-centers have a "large static and dynamic inhomogeneous linewidth", [15]. Another type of color center, the negatively charged SiV-center has good optical behavior and a narrow inhomogeneous linewidth, making it a good candidate for quantum communication. However, the SiV-center has a much smaller coherence time. This can be elongated to one minute at a temperature of 4K [15]. As mentioned before, the Fujitsu Project also does research about SnV-centers.

A simulator has been proposed by [16] to learn the Hamiltonian that describes the behavior of the NV-center qubit. It consists of three parts: 1) a Silicon Quantum Photonic Simulator, 2) a Diamond NV electron spin system and 3) a classical computer. The system proves that the verification and validation of quantum systems and quantum devices can be done with a hybrid-system, which is part classical and part quantum [16].

#### 2.3.1. Other types of Qubit

NV-centers can be used as qubits, and can be controlled using lasers, magnetic fields en electric fields (ODMR). This is quite different from other types of qubit and also what makes the technology special.

For example, the decoherence time of NV-centers is longer than superconducting qubits.

Superconducting is perhaps the most popular and therefore most explored type of qubits. Sycamore, the quantum computer from Google, uses 53 of these type of qubits [5]. The qubits, as the name suggests, consist of superconducting electrodes that are interconnected with Josephson-Junction. Within the superconducting qubits, there are different types. Examples are: charge, flux, phase and fluxonium. At QuTech, the transmon qubit is used. There are two islands, interconnected with a junction. This junction is comparable with an LC-oscillator. Surface code is an example of an application of transmon qubits. It uses bus-resonators, readout-resonators and microwave-inputs to control the qubits [7].

Spin qubits are more comparable to NV-centers than superconducting qubits. Spin qubits also utilize the spin of an isolated electron to do calculations. Charge sensing can be used to detect if an electron spin is present. The space wherein a spin qubit is present is called a quantum dot. Two quantum dots can be cross coupled, but that has as a disadvantage that the voltage applied to dot #1 also influences the potential of dot #2. Instead of control with lasers, the control is now done with alternating magnetic fields. When this alternating field is introduced, the spin starts to rotate as a function of time. The oscillations are called Rabi-oscillations. These are important as they form the basis of single qubit rotations. The oscillations decay because of nuclear spins present in the environment, and so the frequency of the qubit changes over time. Silicon-28 has 0 nuclear spin, thus there is no decay of oscillations. Together with sequences and other materials an increase of the coherence-time of a qubit is possible [7].

## 2.4. Quantum Computer Microarchitectures

Because there are different types of qubits, there must also be different ways to control them, either because the underlying qubit requires that or because the design philosophy is different. In this section, a few quantum computer microarchitectures will be highlighted. Note that, because there is a discrepancy between the definitions of microarchitecture used in between these examples, the definition might not add up completely to the definition set in Section 2.2.

#### 2.4.1. QuMA

QuMA, or **Qu**antum **M**icro **A**rchitecture [17], is a heterogeneous microarchitecture aimed at the control of superconducting qubits. There is a host classical CPU, with a quantum co-processor. There are, essentially, three versions of QuMA. The first version, called QuMA, is based on four concepts at the core: codeword-based event control, Queue-based event timing control, multilevel instruction decoding and QuMIS, the **Qu**antum **M**icro Instruction **S**et. The other versions of QuMa, QuMa\_v2 (featuring eQASM microarchitecture) and QuMa\_FT are discussed later.

#### Codeword-based event control

In QuMa, every event is indexed with a codeword. The events are then triggered by the codewords, improving control flexibility. Additionally, there is less memory usage. For the *AllXY*-experiment that serves as a benchmark for QuMA, there is an 83% reduction in used memory.

#### Queue-based event timing control

Events are buffered in a group of queues. Then, the events can be triggered at the expected timing resulting in deterministic and precise execution under non-deterministic timing.

The concept is quite simple. Each operation has a time label. A timeline can be created, going from left to right, where different operations have their own time label. Once the system clock  $T_d$  has reached the correct time on which the operation with time label (x) has to be executed, it executes the operation and resets the system clock for the next event.

#### Multilevel instruction decoding

Because the preceding two concepts already handle a lot of things, other parts of QuMA can focus on flexibly decoding instructions. In addition, this part also focuses on filling the queue as fast as possible.

Quantum instructions are defined in the Quantum Instruction Set (QIS). It contains classical and quantum instructions, where the classical instructions are used for basic arithmetic and logic operations and program flow control. The quantum instructions determine when and what operation is applied on which qubit.

Multilevel instruction decoding supports technology-independent QIS definitions. At the core, quantum instructions are decoded into quantum micro-instructions, micro-operations and eventually codeword triggers.

#### **Quantum Micro Instruction Set**

QuMIS is the microinstruction set that is used within QuMA. it has four different instructions:

- 1. Wait: wait between consecutive time points.

- 2. Pulse: apply quantum gates on qubits.

- 3. MPG: generate the measurement pulse.

- 4. MD: trigger the measurement discrimination process.

The first version of QuMA is no longer used, because there are a flaws in the architecture that prohibit the architecture from functioning optimally. There is no feedback based on qubits measurement results, there is limited scalability because of a low instruction information density and it is limited in flexibility because of the tight bound to the hardware. Because of these flaws, QuMIS can **not** be defined as a QISA [17].

This is why Fu proposed a new version featuring eQASM, the executable quantum assembly [17, 18]. Under the definitions set up in Section 2.2, eQASM is an example of a microarchitecture. eQASM has support for the following:

- Runtime Feedback: Two kinds of feedback are supported within eQASM: fast conditional execution and comprehensive feedback control (CFC).

- Operational Implementation: the definition of eQASM lies on the assembly level and basic rules of mapping assembly to binary.

- Increased Quantum Operation Issue Rate (QOIR): By adapting a VLIW architecture in addition to Single-Operation-Muliple-Qubit (SOMQ) execution, alleviating the Quantum Operation Issue Rate (QOIR).

- Configurable QISA at compile time: eQASM allows the user to configure quantum operations at compile time instead of at the ISA design stage.

#### Overview

Quantum computing can be compared with computing in for example OpenCL. OpenCL is a open industry standard for programming for GPUs. Following this heterogeneous computing mode, we can also do do the same for a quantum computer, or quantum accelerator. A host program, typically written in Python or C++ is used with kernels written in OpenQL, a quantum compiler, for the quantum part of the program. The kernels are compiled to eQASM instructions, which are then loaded into the QPC by the host CPU and executed. eQASM is defined by five principles, [17, p. 77]:

- 1. "eQASM should include classical instructions to support quantum program flow control including runtime feedback;

- 2. eQASM should contain well-defined methods to specify the timing of quantum operations;

- 3. Low-level hardware information should be abstracted away from the eQASM assembly as much as possible to avoid eQASM being stuck to a particular hardware implementation;

- The quantum operation issue rate is a potential bottleneck of the quantum microarchitecture, and should be addressed, e.g., by densely encoding the instructions such as done with SIMD and VLIW for classical architectures;

- 5. Different experiments and radical compiler-based optimization techniques such as quantum optimal control [144, 145] may use a different set of quantum operations, which can be uncalibrated or uncommon. eQASM should be flexible to allow different quantum operations via configuration."

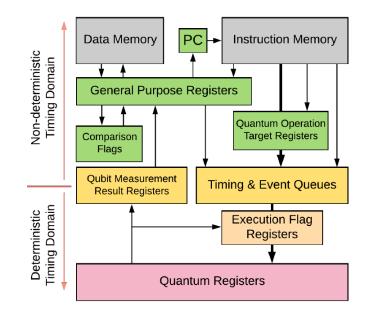

The architectural state of the QPU (Quantum Processing Unit) is shown in Figure 2.6. The **Data Memory** buffers intermediate compute results and acts as the communication channels between CPU and QPU. Instructions are obviously stored in the **Instruction Memory** while the **Program Counter** (**PC**) keeps track of the instruction addresses. **General Purpose Registers (GPRs)** are 32-bit registers, starting with r1. The comparison result from comparison and branch instructions are stored in the **Comparison Flags**. There are two types of **Quantum Operation Target Registers**: single qubit registers for single-qubit operations and two-qubit registers for two-qubit operations. The physical address of a set of qubits is stored in a target register. Same as with QuMA, eQASM features a queue-based timing control scheme, splitting the process into two domains: deterministic and non-deterministic timing. This is done in the **Timing and Event Queues**. For storing the measurement results of the qubit, a set of **Qubit Measurement Result Registers** are available. There is an **Execution Flag Register** for quick conditional execution. The **Quantum Registers** which serve as a collection of all physical qubits. A unique index is assigned to each qubit called the physical address.

**Figure 4.2:** Architectural state of eQASM. Arrows indicates the possible information flow. The thick arrows represent quantum operations, which reads information from the modules passed through.

Figure 2.6: Architectural state of eQASM [17, Figure 4.2]

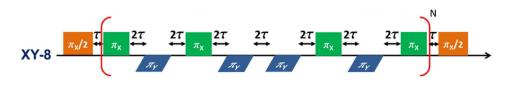

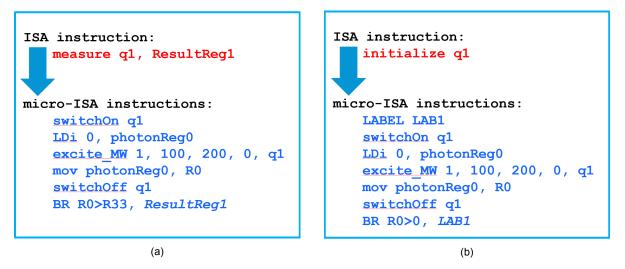

An important part of eQASM is that one of the goals is that it is technology independent. This means that eQASM is directed at the assembly level with rules of mapping the assembly code to binary. eQASM enables freedom for the design of the microarchitecture to enhance performance or usability.