# Backside contacting of individual signals in multilayer ICs for chip forensics

Msc Thesis in Microelectronics Tibbe van der Biezen

## Backside contacting of individual signals in multilayer ICs for chip forensics

by

## Tibbe van der Biezen

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Thurday July 18, 2024 at 1:00 PM.

Student number: 4686608 Supervisors: Dr. ir. S. V

4686608 Dr. ir. S. Vollebregt, Dr. ir. J. Romijn M. Roeloffs MSc ir. K. Schot

TU Delft SiTime Netherlands Forensic Institute (NFI) Netherlands Forensic Institute (NFI)

## Abstract

Chip forensics has become an important aspect of law enforcement for retrieving data from data carriers. Improving data encryption techniques, smaller technology nodes and increasing chip design complexity instigate the constant need for new software and hardware hacking methods. The work presented in this thesis investigates the potential of a new hardware hacking method named backside contacting. This method aims to connect a probe to one of the bottom interconnects through the backside to listen to the signals sent over that interconnect.

For this purpose, a recipe has been developed. This recipe is a workflow of numerous processes and steps. Several methods like delayering, cross-sectioning and infra-red (IR) imaging were developed to obtain information about the layout and technology of the chip. Atomic layer deposition (ALD), induction coupled plasma enhanced chemical vapour deposition (ICPECVD) and a focussed ion beam (FIB) were used to create structures on the die, in order to realize a backside interconnect. Finally, various setups were built to test the chip throughout the recipe.

The study shows that each step is possible without losing the data on the chip. The yield of surviving chips after each step, however, should be increased to establish a complete backside contact while keeping the chip alive. The study also indicates that there remains considerable potential for improvement within each step. The results are promising and justify further research into the method of backside contacting.

## Acknowledgements

This thesis started as an exciting adventure into the world of secrecy and bureaucracy. A world where the knowledge and skill of reverse engineering were something that I had not encountered before in the courses that I followed during my bachelor's and master's. I had to quickly learn about numerous new techniques and tools, understanding their standard use cases as well as unconventional applications for which they were not originally intended. I thoroughly enjoyed the way of thinking, the practical way of problem-solving and the discussions that were had during the course of this project.

In large part, this was made possible by the amazing group of supervisors who helped me navigate through the many obstacles. First, I would like to thank Sten, who was a never-ending source of information, help and new ideas. His patience and knowledge of the possibilities at the TU Delft labs made this project possible.

Secondly, I would like to thank my supervisors at the NFI. They welcomed me from the start and their immediate trust was inspiring. I am grateful for the level of flexibility they offered and the extensive use of their lab and tools. I would like to especially thank Joost, Mark and Kees; Joost for the warm introduction at the NFI, his critical feedback and enlightening explanations; Mark for his help with the tiniest problems, his enthusiasm and of course his background music; and Kees for his advice, shared knowledge and intriguing stories.

I would also like to thank Folkert, who trained me on most of the tools at the NFI and helped me understand all their intricate parts and functions. Additionally, I would like to thank Bas and Marinus who gave me access to the Kavli Nanolab and trained me on the deposition tools.

Last but certainly not least, I would like to thank my friends and family who have supported me during my whole education. I would like to especially thank my brothers who kept me motivated by always asking intriguing questions and having a listening ear for problems they were not supposed to solve. Special thanks also go out to my parents, who always supported me, whatever decision I made, good or bad and always trusting in a good outcome.

Tibbe van der Biezen Delft, July 2024

## Contents

| Ab            | strac                      | ct                                                                                                                                                                                                                                                                                                       | i                                      |

|---------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Ac            | knov                       | wledgements                                                                                                                                                                                                                                                                                              | ii                                     |

| Ac            | rony                       | yms                                                                                                                                                                                                                                                                                                      | viii                                   |

| 1             | Intro<br>1.1<br>1.2<br>1.3 | oduction Motivation and problem statement Thesis objectives Thesis outline                                                                                                                                                                                                                               | <b>1</b><br>1<br>2<br>2                |

| 2             | 2.1                        | kground informationBasics of hardware hacking2.1.1Device physics2.1.2Technological advancements2.1.3Acquiring data                                                                                                                                                                                       | <b>3</b><br>4<br>12<br>16              |

|               | 2.2<br>2.3                 | Imaging       2.2.1 Acquiring initial chip layout         2.2.2 Finding points of interest       2.2.3 Aligning chip         2.2.3 Aligning chip       2.2.3 Contamination         2.3.1 Risk analysis       2.3.2 Prevention                                                                            | 18<br>18<br>20<br>21<br>22<br>22<br>23 |

| 3             | Reci                       | ipe design                                                                                                                                                                                                                                                                                               | 23<br>24                               |

| J             | 3.1                        |                                                                                                                                                                                                                                                                                                          | 24<br>24<br>24<br>25                   |

|               | 3.2                        | Acquisition of chip layout and technology3.2.1Non-destructive observation3.2.2Cross-section fabrication3.2.3Die extraction3.2.4Exposing backside                                                                                                                                                         | 26<br>26<br>26<br>26<br>27             |

|               | 3.3                        | 3.2.5 Determine areas of interest       Invasive processing         Invasive processing       Invasive processing         3.3.1 Create holes in the Si bulk       Invasive processing         3.3.2 Create pillars       Invasive processing         3.3.3 Deposite insulation       Invasive processing | 28<br>29<br>29<br>31<br>31             |

|               | 3.4<br>3.5                 | Establish external connection                                                                                                                                                                                                                                                                            | 31<br>31<br>32<br>32                   |

| 4 Experiments |                            |                                                                                                                                                                                                                                                                                                          | 34                                     |

| -             | 4.1                        | Recipe processes       4.1.1 Cross-section fabrication         4.1.2 Die extraction       4.1.3 Acquire layout         4.1.3 Acquire layout       4.1.4 Exposing backside         4.1.5 Removing the die-attach       4.1.6 Removing Si bulk                                                             | 34<br>34<br>35<br>35<br>37<br>37<br>38 |

|               |                            | 4.1.7 Determine areas of interest                                                                                                                                                                                                                                                                        | 40                                     |

|    |       | 4.1.8 Creation of holes in the Si bulk                                                 | 1 |

|----|-------|----------------------------------------------------------------------------------------|---|

|    |       | 4.1.9 Create pillars                                                                   | 2 |

|    |       | 4.1.10 Deposit insulation                                                              |   |

|    |       | 4.1.11 Create pads and traces                                                          |   |

|    | 4.0   | 4.1.12 Wirebonding                                                                     |   |

|    | 4.2   | Testing                                                                                |   |

|    |       | 4.2.1 BeeProg2                                                                         |   |

|    |       | 4.2.3 Resistance measurements                                                          |   |

|    |       | 4.2.4 X-vision                                                                         |   |

|    |       | 4.2.5 IR heat camera                                                                   |   |

| 5  | Baa   | Its and evaluation 55                                                                  | - |

| 5  |       | Its and evaluation       55         Acquisition of chip layout and technology       55 |   |

|    | 5.1   | 5.1.1 Outside observation                                                              |   |

|    |       | 5.1.2 Obtaining cross-section                                                          |   |

|    |       | 5.1.3 Extracting the die                                                               |   |

|    |       | 5.1.4 Exposing backside                                                                |   |

|    |       | 5.1.5 Determine areas of interest                                                      | 3 |

|    | 5.2   | Invasive processing                                                                    | 3 |

|    |       | 5.2.1 Create holes                                                                     | 3 |

|    |       | 5.2.2 Create pillars and deposit TEOS                                                  | 7 |

|    |       | 5.2.3 Deposite insulation                                                              | 3 |

|    | 5.3   | Establish external connection                                                          | - |

|    |       | 5.3.1 Create pads and traces                                                           | - |

|    |       | 5.3.2 Wire bonding                                                                     | 3 |

| 6  | Con   | lusion and future work 74                                                              | ŧ |

|    | 6.1   | Recipe review                                                                          | ŧ |

|    |       | 6.1.1 Acquisistion of chip layout and technology                                       | - |

|    |       | 6.1.2 Invasive processing                                                              |   |

|    | ~ ~   | 6.1.3 Establish external connection                                                    |   |

|    | 6.2   | Recommendations                                                                        | ) |

| Re | ferer | ces 77                                                                                 | 7 |

| Α  | Extr  | cting die using nitric acid 81                                                         | ı |

|    |       | Preperation                                                                            | 1 |

|    |       | A.1.1 Equipment                                                                        | I |

|    |       | A.1.2 Materials                                                                        | I |

|    |       | A.1.3 Safety                                                                           | l |

|    | A.2   | Procedure                                                                              | l |

|    |       | A.2.1 Start etching                                                                    |   |

|    |       | A.2.2 Cleaning                                                                         |   |

|    |       | A.2.3 Place the chip in the fuming acid                                                |   |

|    |       | A.2.4 Etch stop                                                                        |   |

|    |       | A.2.5 Cleaning                                                                         | - |

| В  | Sum   | nary processed samples 83                                                              | 3 |

## List of Figures

| 2.1  | Spectrum from software to hardware hacking                                              | 4   |

|------|-----------------------------------------------------------------------------------------|-----|

| 2.2  | Packaging of the chip                                                                   | 4   |

| 2.3  | Wirebonded cross-section                                                                | 5   |

| 2.4  | Cross-sections of a chip in package                                                     | 5   |

| 2.5  | Cut-outs of the top of a chip                                                           | 6   |

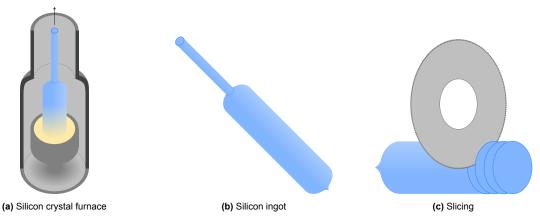

| 2.6  | First steps of creating a wafer                                                         | 6   |

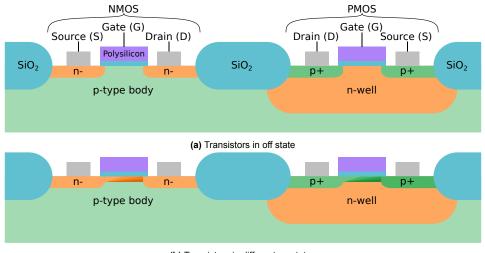

| 2.7  | Two basic CMOS transitors                                                               | 9   |

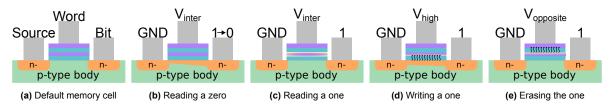

| 2.8  | Different operating states of a memory cell                                             | 10  |

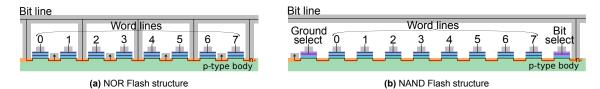

|      | Different Flash architectures                                                           | 11  |

|      | Transistor roadmap presented by IMEC [21]                                               | 12  |

|      | Schematic representations of FinFETs                                                    | 13  |

|      | Schematic representation from FinFET to gate all-around nanosheet field-effect transis- | 15  |

| 2.12 | tor (GAA-NSFET).                                                                        | 13  |

| 0 10 | Schematic representation from GAA-NSFET to gate all-around forksheet field-effect tran- | 13  |

| 2.13 |                                                                                         | 4.4 |

| 044  | sistor (GAA-FSFET)                                                                      | 14  |

|      | Cross-section of a complementary field-effect transistor (CFET)                         | 14  |

|      | Chip stacking                                                                           | 15  |

| 2.16 | Overview materials used inside package                                                  | 22  |

| 04   | Lienensky en englied to project design                                                  | ~ 4 |

| 3.1  | Hierarchy as applied to recipe design                                                   | 24  |

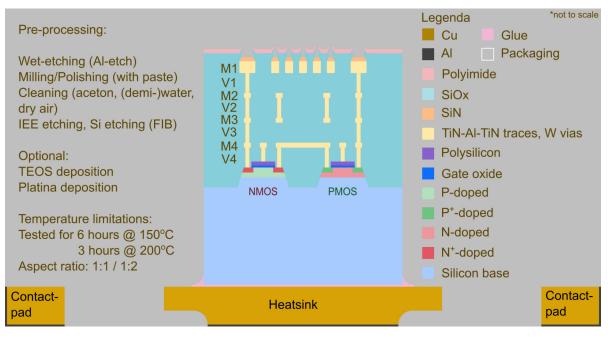

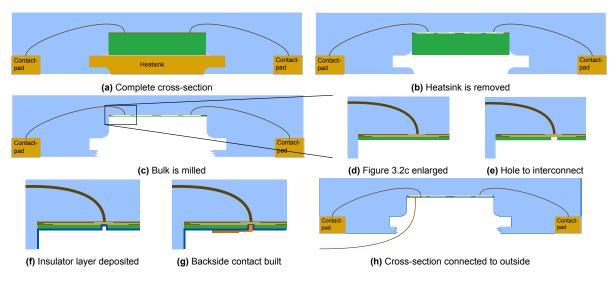

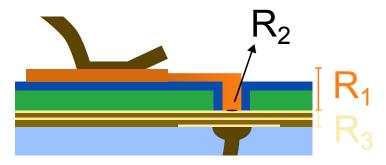

| 3.2  | Cross-sections of the main concept                                                      | 25  |

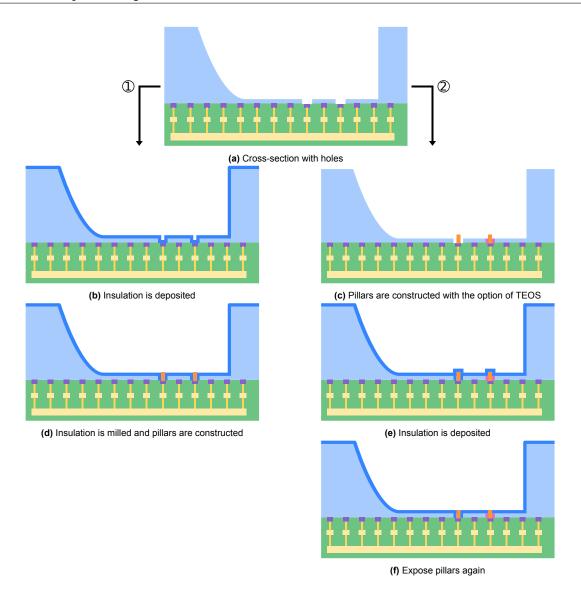

| 3.3  | Example crosssections of the different paths                                            | 30  |

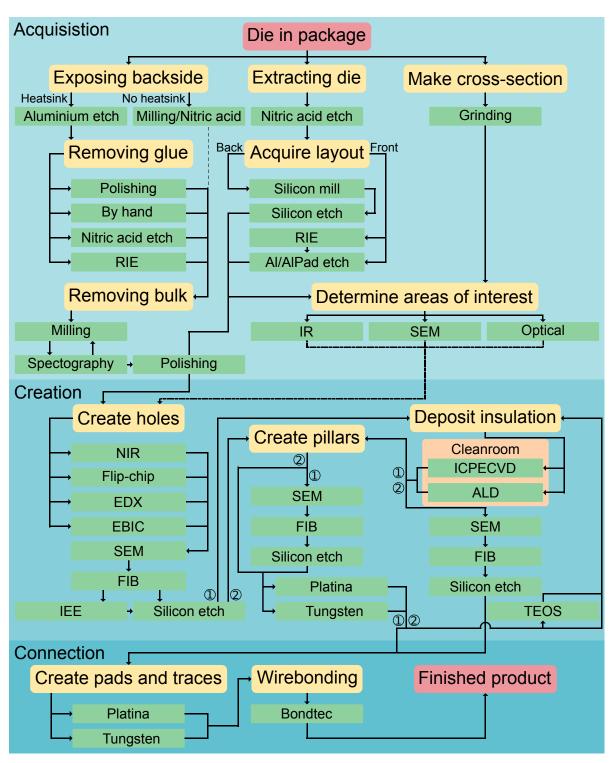

| 3.4  | Recipe flowchart                                                                        | 33  |

| 4.1  | Multiprep                                                                               | 34  |

|      |                                                                                         |     |

| 4.2  | Fume hood with equipment used                                                           | 35  |

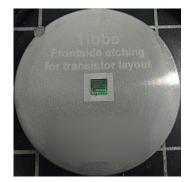

| 4.3  | Die mounted for frontside layout analysis                                               | 35  |

| 4.4  | Lext 3D surface-analysis tool                                                           | 35  |

| 4.5  | X-prep                                                                                  | 36  |

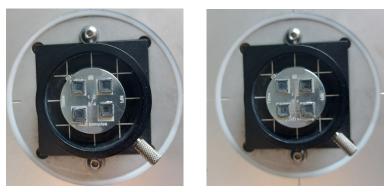

| 4.6  | Sample setup for backside layout analysis                                               | 36  |

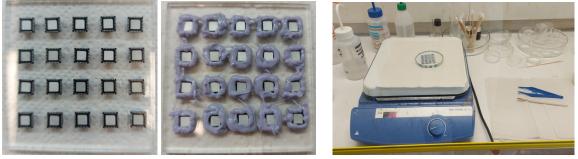

| 4.7  | Setup steps for heatsink etching                                                        | 37  |

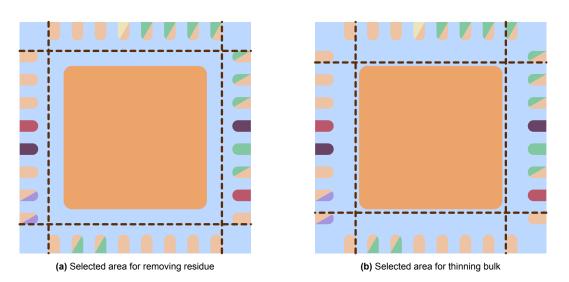

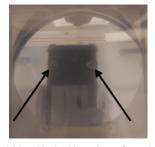

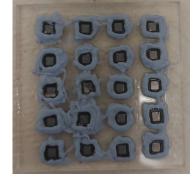

| 4.8  | Selected areas for milling                                                              | 39  |

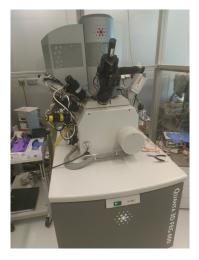

| 4.9  | Scanning electron microscope (SEM)-FIB tool                                             | 40  |

|      | IR microscopes                                                                          | 41  |

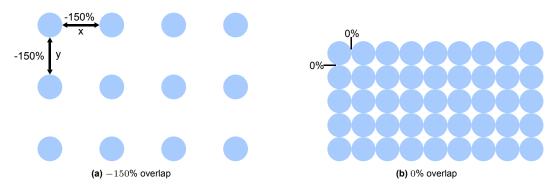

|      | Overlap percentage explained                                                            | 43  |

|      | ALD tool setup                                                                          | 43  |

|      | ICPECVD tool setup                                                                      | 44  |

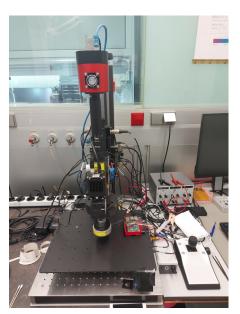

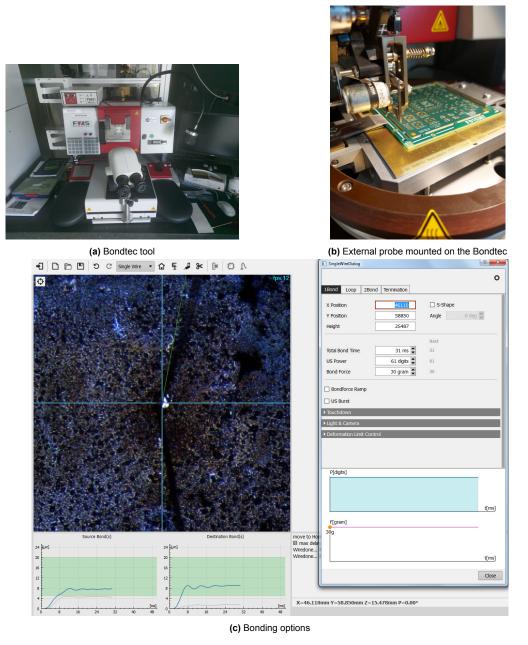

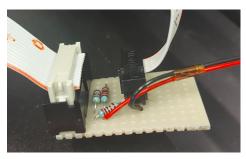

| 4.14 | Wirebonding setup                                                                       | 47  |

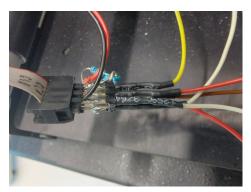

| 4.15 | BeeProg2 with DIL32/MLF32-1 adapter                                                     | 48  |

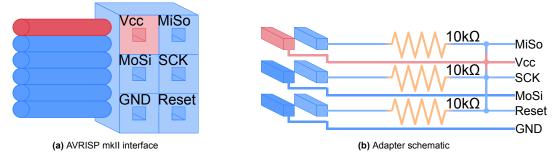

| 4.16 | AVRISP mkll                                                                             | 48  |

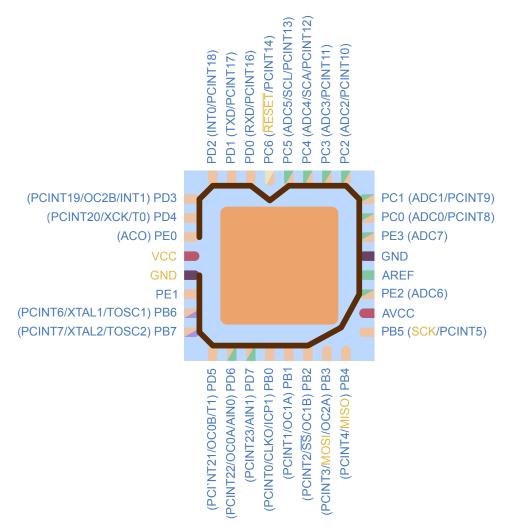

| 4.17 | Chip layout including ground wire                                                       | 49  |

|      | AVRISP mkll general setup                                                               | 49  |

|      | Probe station setup                                                                     | 50  |

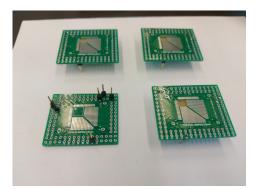

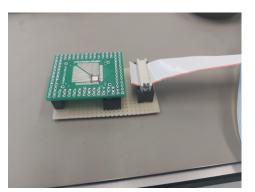

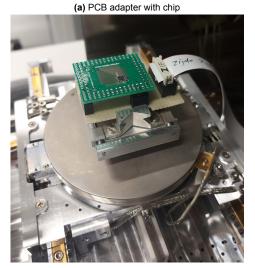

|      | SEM adapters                                                                            | 51  |

|      | Fluke 189 multimeter                                                                    | 51  |

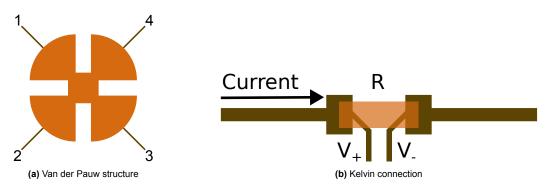

|      | Resistances in signal path                                                              | 52  |

|      | Resistance measurement structures                                                       | 52  |

|      |                                                                                         | 53  |

|      |                                                                                         | 54  |

| 4.26 | IR thermal imaging setup                               | 54 |

|------|--------------------------------------------------------|----|

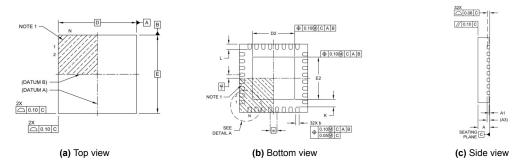

| 5.1  | Sizing and package from datasheet                      | 55 |

| 5.2  | X-ray scans with additional SEM images                 | 56 |

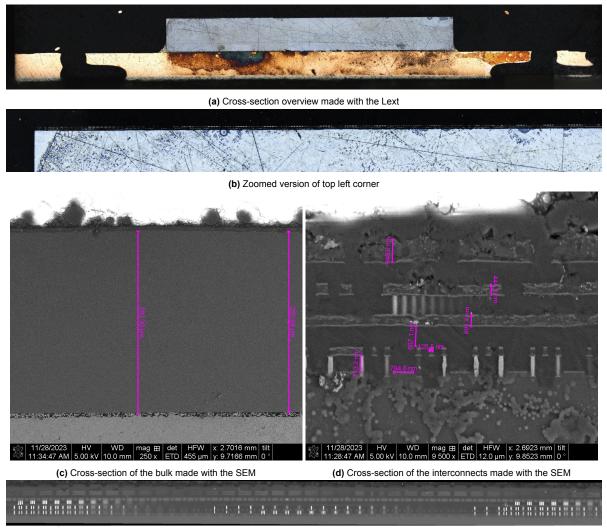

| 5.3  | Crosssections made with the Lext and SEM               | 58 |

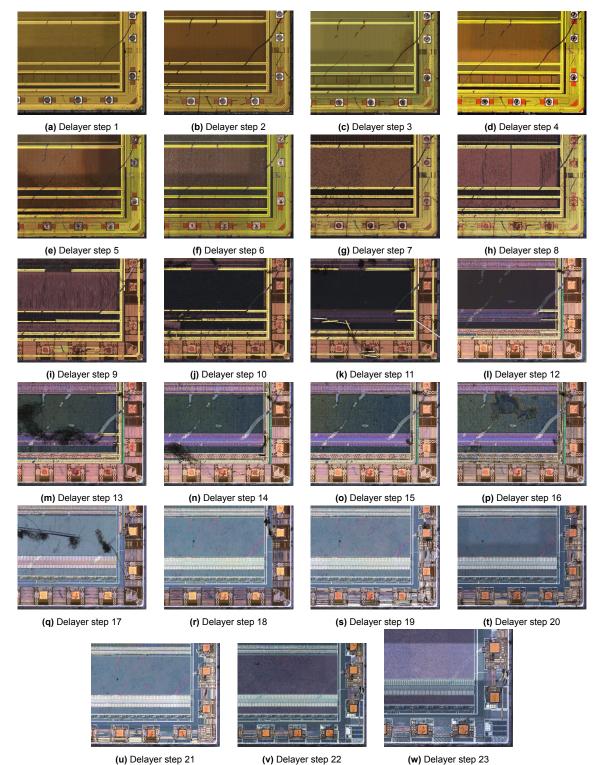

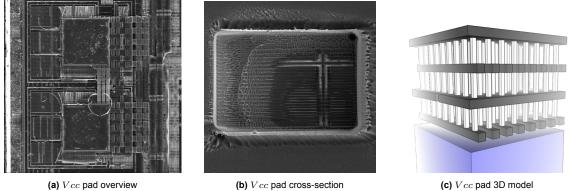

| 5.4  | Delayering results of the frontside lower right corner | 59 |

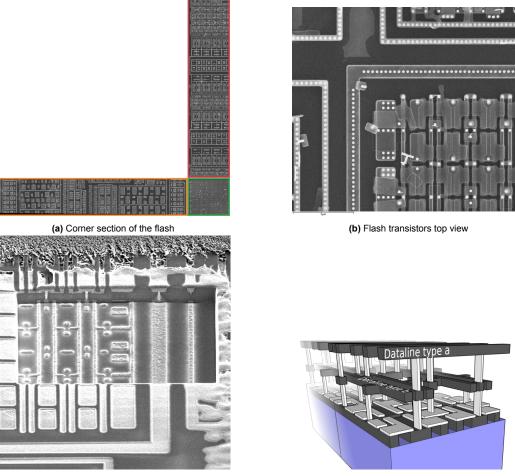

| 5.5  | Flash analysis using the SEM                           | 60 |

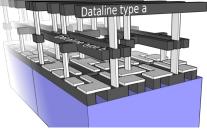

| 5.6  | Vcc pad analysis using the SEM                         | 61 |

| 5.7  | Results of the heatsink removal process                | 62 |

| 5.8  | Stubs ready for bulk thinning                          | 63 |

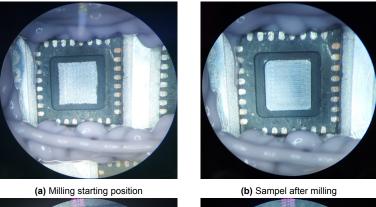

| 5.9  | Milling steps results                                  | 63 |

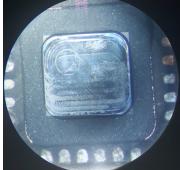

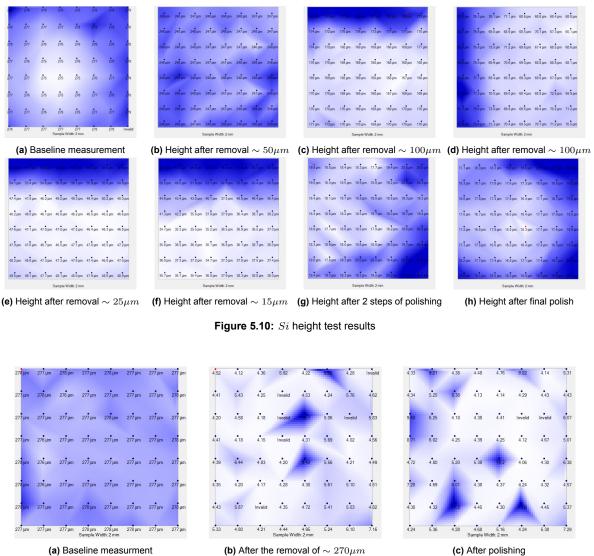

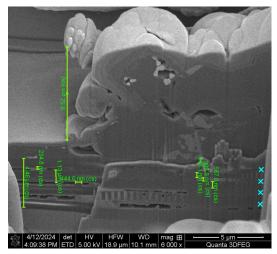

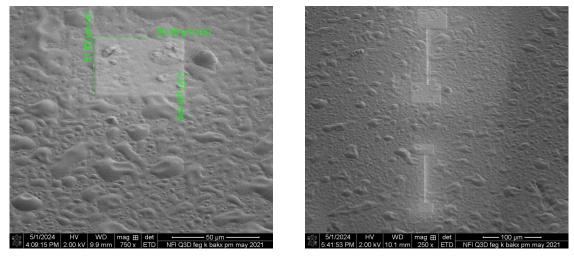

| 5.10 | Si height test results                                 | 64 |

|      | Si height test results of the improved process         | 64 |

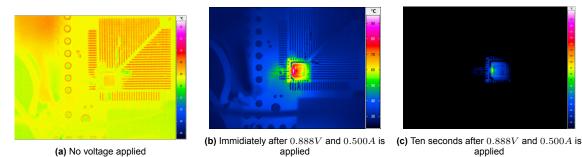

| 5.12 | IR heat camera results                                 | 65 |

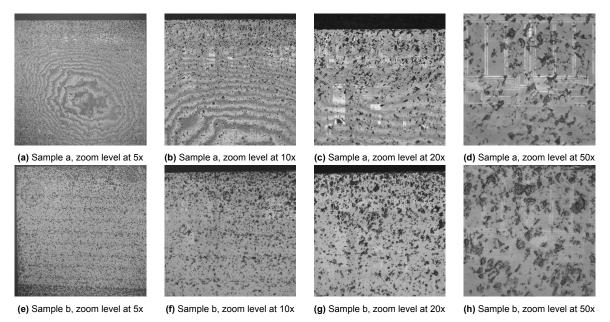

| 5.13 | Near infra-red (NIR) images                            | 66 |

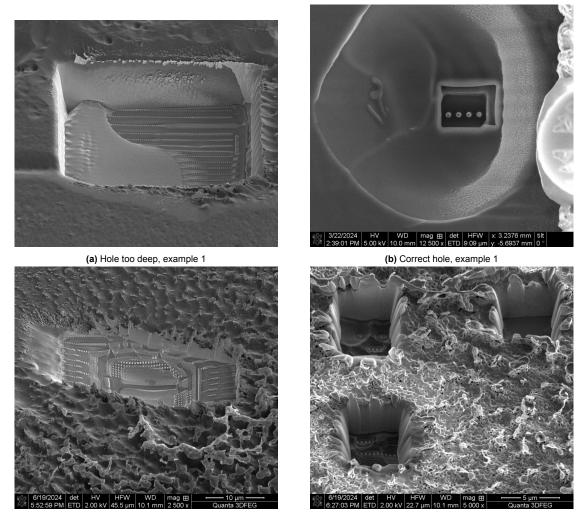

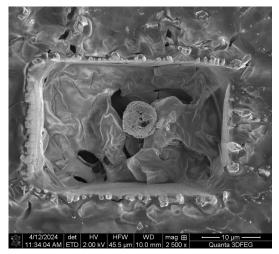

| 5.14 | Holes to the <i>Vcc</i> connection pad                 | 67 |

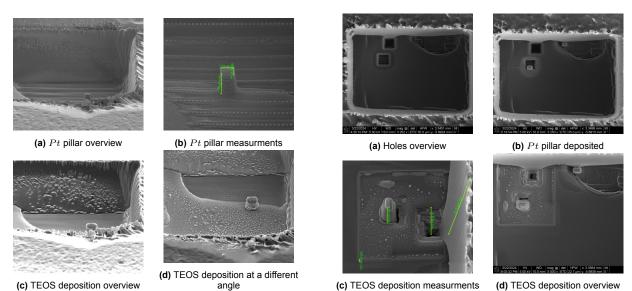

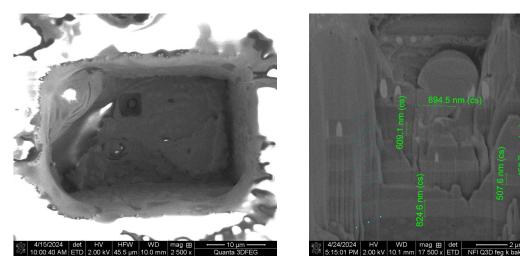

| 5.15 | Pillar and TEOS of sample a                            | 68 |

| 5.16 | Pillar and TEOS of sample b                            | 68 |

| 5.17 | AlOx ALD results                                       | 68 |

| 5.18 | SiO <sub>2</sub> ICPECVD results                       | 69 |

| 5.19 | Improved ALD results                                   | 70 |

| 5.20 | Alternative ICPECVD results                            | 71 |

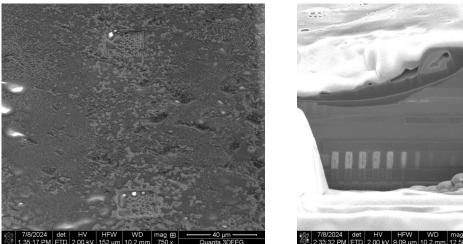

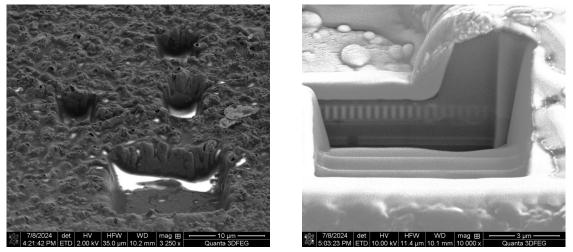

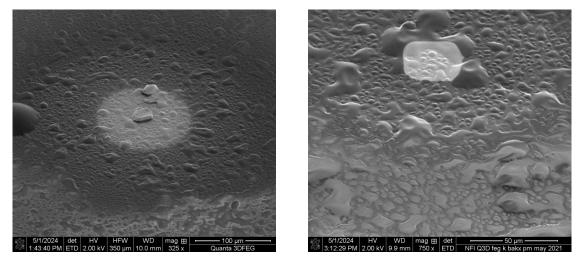

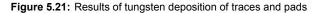

| 5.21 | Results of tungsten deposition of traces and pads      | 72 |

| 5.22 | Results of platina deposition of traces and pads       | 72 |

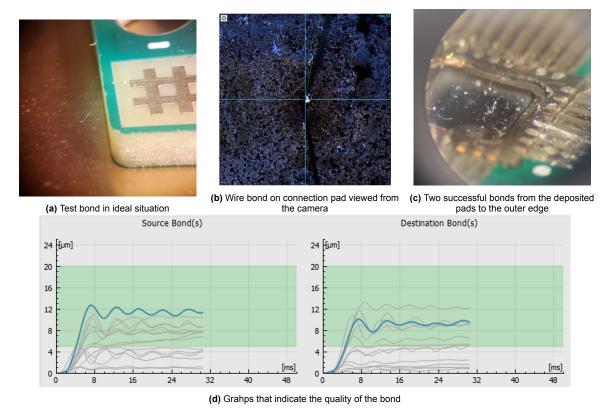

| 5.23 | Results of the bond wirering                           | 73 |

## List of Tables

| 4.1 | Recipe for $14.5nm \ AlOx \ ALD$ at $105^{\circ}C$                                             | 44 |

|-----|------------------------------------------------------------------------------------------------|----|

| 4.2 | Recipies for $HfOx$ and $AlOx$ ALD at $105^{\circ}C$                                           | 44 |

| 4.3 | Recipe for ICPECVD with $SiO_2$ at $150^{\circ}C$                                              | 45 |

| 4.4 | Recipe for ICPECVD with $SiN$ at $100^{\circ}C$                                                | 45 |

| 4.5 | Pads and traces deposition                                                                     | 46 |

| 5.1 | Packaging dimensions from datasheet                                                            | 56 |

| 5.2 | Temperature test results                                                                       | 57 |

| 5.3 | Bulk thinning resistance and verification results                                              | 65 |

| 5.4 | <i>Vcc</i> to <i>Gnd</i> resistance and functionality test results after insulation deposition | 71 |

| B.1 | All samples used in testing with short description                                             | 83 |

### Acronyms

AES advanced encryption standard 17 Al artificial intelligence 14, 18 ALD atomic layer deposition i, v-vii, 8, 31, 43, 44, GUI graphic user interface 48 63, 68-71, 74, 75 **BPDN** backside power distribution network 14, 15, 74 **CCPECVD** capacitivily coupled plasma enhanced chemical vapour deposition 8 **CFET** complementary field-effect transistor v, 12, 14 CG control gate 10 CHE channel hot electrons 10 **CPA** correlation power analysis 16 CPU central processing unit 11 CR cleanroom 23, 43 CVD chemical vapour deposition 8, 9 **DES** data encryption standard 17 DFA differential fault analysis 16 DRIE deep reactive-ion-etching 7, 8 EBIC electron beam induced current 22 ECC elyptic curve cyphers 17, 18 ECDLP elyptic curve discrete logarithmic problem 18 EDX energy dispersive X-ray 19, 20, 26 **EEPROM** electronically erasable programmable read-only memory 10 **EKL** Else Kooi Laboratory 40 ELM electrical linewidth measurement 52, 53 EPROM erasable programmable read-only memory 9, 10 ESD electrostatic discharge 65, 75 ETD Everhart–Thornley detector 41 FG floating gate 10 **FIB** focussed ion beam i, v, 17, 29–31, 40–42, 45, 48.60.66 **FN** Fowler-Nordheim tunnelling 10 FSM finite state machine 17 **GAA-FSFET** gate all-around forksheet field-effect transistor v, 12–14

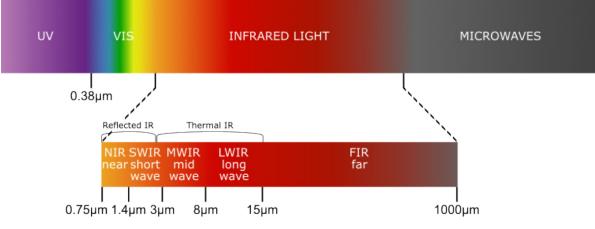

GAA-NSFET gate all-around nanosheet field- VCI voltage contrast imaging 50, 75 effect transistor v, 12-14

GIS gas injection system 41 **GPT** generative pre-trained transformer 18 HVQFN heat sink very-thin quad flat no lead 4, 48 IC integrated circuit 6, 15 **ICPECVD** induction coupled plasma enhanced chemical vapour deposition i, v-vii, 8, 31, 43-45, 63, 68-71, 75 IEE insulator enhanced etch 29, 41, 67 IP intellectual property 2 **IR** infra-red i, iv–vi, 20, 21, 28, 29, 40, 41, 47, 53, 54, 65, 66, 74, 75, 84 LOCOS localized oxidation of silicon 8 MSDS material safety datasheet 23 NFI Netherlands Forensic Institute 1, 25, 35, 45 NIR near infra-red vi, 20, 21, 29, 40, 53, 66 NMOS N-channel metal oxide semiconductor 9, 10, 14 PCB printed circuit board 46, 50, 51 PMOS P-channel metal oxide semiconductor 9, 14 PoP Package-on-Package 5, 15 PVD physical vapour deposition 8, 9 RIE reactive-ion etching 7, 27, 28, 37, 74, 76, 85 RMG replacement metal gate 13 **SEM** scanning electron microscope v, vi, 28–31, 34, 40, 41, 45, 47–51, 55–58, 60, 61, 66, 74, 75 SIT sidewall image transfer 13 SoC system on a chip 16 SOI silicon on isolator 19 SPA simple power analysis 16 STI shallow trench isolation 8, 19, 57 **TSV** through-silicon-vias 15 TVT rhin-film transistor 9

VR virtual reality 14

## Introduction

Trias politica, or separation of powers is a commonly known model to describe the division of power within a government. These branches, often divided into a legislature, an executive, and a judiciary, hold significant power and responsibility. This thesis takes place in the context of the executive and judiciary. These branches strive to execute and interpret the law. In case of a major crime, numerous investigations have to take place to correctly apply this law. This is where the Netherlands Forensic Institute (NFI) plays its part.

When a crime of a certain degree has taken place, evidence is gathered by the police and associated parties. This is then brought to the NFI where it is analysed and prepared for the public prosecutor. To guarantee the maximum amount of information is extracted from a piece of evidence, research is done by multiple disciplines. One of these disciplines is device forensics which consists of both hardware and software analysis. Their goal is to extract data from data carriers, like computers, laptops or phones.

The gathered information may be presented in court and impact the verdict. Therefore, it must be collected using scientifically rigorous methods. These methods, however, need constant updating as technology advances and society finds more secure ways to communicate or store data. This phenomenon occurs not only from a consumer perspective but is also driven by the ongoing cat-and-mouse game between criminals and forensic researchers. One example that illustrates both the necessity for this research as well as its impact was the breakthrough in intercepting crypto communication [1].

#### 1.1. Motivation and problem statement

With the increase in digital devices for both communication and data storage, more and more evidence can be gathered from those devices. Evidence that can point towards a possible perpetrator or clear someone's name. One of the more interesting devices is the mobile phone. It stores important information like communication history, GPS coordinates and photos. However, these devices are developed continuously, implementing better data encryption and more safety features in the hardware. Furthermore, the transistor sizes become smaller and the amount of metal layers keeps increasing. This means new methods need to be developed to access the important information which helps the judiciary.

The first step in accessing the data is using software hacking. Chapter 2 will go into more detail about these methods. It shows that these methods are limited to the external connection pads. Furthermore, the signals and memory data that can be recovered are often encrypted if they can be recovered at all. That is where hardware hacking might be the solution. By being able to access these intermediate signals and possibly the memory directly, new software attacks are possible and encryption can be circumvented.

This thesis will analyse a proposed method called *backside contacting*. The main idea behind this method is that instead of editing the front side of the chip, which is done nowadays, a hole is created through the backside to read the information travelling over the bottom interconnects. This should bring two major advantages. First, by going from the backside it should be easier to keep the chip alive by not breaking the higher interconnects. Secondly, the lower interconnects generally contain more raw data since they are directly on top of the transistors. The encryption of this data is therefore limited,

increasing the possibility to decrypt and use this information.

Keeping the chip alive is important in forensic research because the data on the chip should still be intact and accessible. This means that the main functionalities of the chip should still be performed like power-up and flash reads. This requirement does not apply to most reverse engineering techniques and processes which are mainly used for intellectual property (IP) protection and analyzing state-of-the-art chip manufacturing technology. That means, either these processes have to be adapted or new processes need to be designed.

#### 1.2. Thesis objectives

The main objective of this thesis is to validate the proof of principle of being able to connect to the bottom metal interconnects while keeping the chip alive. This was divided into three practical objectives; getting to know the available techniques and technology for chip forensics; getting to know the chip fabrication technology and layout; and finally, defining process steps and exploring the best options per step. As a result, a recipe should be designed containing the whole process of creating a backside contact.

#### 1.3. Thesis outline

The thesis consists of six chapters:

- 2. Background information: a chapter that provides background knowledge, concepts, and the latest research outcomes, regarding chip manufacturing, reverse engineering and contamination risks;

- 3. Recipe design: a chapter that explains the processes that were used and the considerations that were taken into account while designing the recipe. It concludes with the recipe concept;

- Experiments: a chapter that describes all the tools, processes and steps that are used in the recipe. Additionally, it describes the various test setups that were designed.

- 5. Results and evaluation: a chapter that summarizes all the results. Ranging from the chip layout analysis to fault analysis, fabrication results and many intermediate test results. Additionally, it evaluates these results and offers explanations where possible.

- 6. Conclusion and future work: a chapter that reflects on the thesis objectives, describes some concluding arguments and provides ideas for further research.

# $\sum$

## Background information

As was briefly mentioned in the introduction, the transistor sizes become smaller as are the lower interconnect layers. To accommodate the smaller transistors and increase the computational capacity, the amount of interconnect layers steadily increases. On top of that, the encryption of our data becomes more and more complex and robust[2]. In some areas of research, these layers and data need to be accessed, for example in reverse engineering, testing of chip functionality or when it comes to forensic research. Ample of research is already been done when it comes to reverse engineering and testing of chips[3]. Most if not all of the proposed methods have one thing in common, they damage the chip core functionalities meaning the chip partially or completely stops working. However, in the case of forensic research, it is vital that the chip stays alive in order to be able to get information out of it.

This chapter will be the foundation to determine if it is possible to access the bottom interconnects using existing processes and machines while keeping the chip alive. First of all, background knowledge on packaging, die manufacturing and transistors should be established. This will help to understand better where the interconnects are situated, what they are used for and why it is useful to gain access to them. Next, an overview of the different methods and technologies for the fabrication of chips can be put together. This overview is used to design a recipe while taking into account what is available and which processes are compatible with each other. In chapter 3 a closer look is taken at how to keep the chip alive. It is not only important to carefully select and tune the fabrication process but to also look at contamination and potential future developments.

This chapter is structured in the following way. Section 2.1 will discuss the environment within and the fundamentals on which chips are built. This will include the way the sample chips are provided, different technologies and where this project lies with respect to other fields of research. Section 2.2 will go into detail about analysing the chip and where to find potential areas for holes. Finally, section 2.3 will be about the contamination risk when using different machines and moving samples within and between labs.

#### 2.1. Basics of hardware hacking

To understand why hardware hacking is becoming more important nowadays a brief introduction to hacking in general is needed. First, the definition of hacking varies from field to field but generally involves identifying and exploiting weaknesses of a device or network to gain unauthorized access to its data. As an illustration, a spectrum can be constructed where hardware hacking sits on the right-hand side of hacking techniques, see figure 2.1. Hardware hacking is very destructive and always involves physically altering the device. Examples of hardware hacking are the implementation of counterfeit elements or Trojan horses. The latter means that either during the design or fabrication of the chip extra connections or transistors are made or connections are altered in order to change the functionality of the chip[4]. The left side of the spectrum would then be software hacking, in which the device has no physical or destructive alteration. Examples of these techniques are computer viruses, DDoS attacks or zero-day exploits. In between are techniques which combine both extremes. For example, physically changing a bit in memory can cause some security features to malfunction, letting you access data without a password. Other techniques involve side-channel or fault injection attacks[5].

| Software         | Hardware              |                 |                        |

|------------------|-----------------------|-----------------|------------------------|

| Zero-day exploit | Fault injection       | Counterfit elem | ents                   |

| DDoS attack      | Side channel analysis | Trojan horses   | Additional connections |

Figure 2.1: Spectrum from software to hardware hacking

This project focuses purely on hardware hacking, where the proposed hardware hacking technique is backside contacting. This is done after the chip is fabricated to extract digital information stored on the chip or to combine it with fault injection or side-channel attacks. Most importantly, this means that during all processing steps, the chip must stay alive and the most important modules must remain functional. To better understand how hardware hacks are designed, an overview of the fundamental processes and physics regarding packaging and fabrication processes is given in the next section. Furthermore, this section aims to indicate the possibilities of tuning these processes in favour of this project. After the basics are covered, a short discussion about the history and future of transistors will be given to get more insight into the future limitations of this attack. The final section is about getting information out of the chip and how this project can help achieve higher yields in successful hacking.

#### 2.1.1. Device physics

#### Packaging

Because this project is about breaking into a chip, it is only logical to explain the chip fabrication process in reverse. The last step of the fabrication process is the packaging. This step is about encapsulating the die to protect it against the environment.

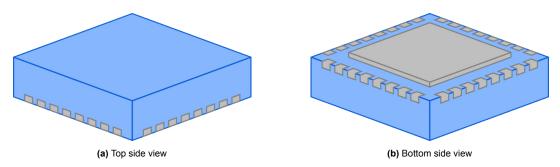

**Outside** First, figure 2.2 shows how the chip looks like once it comes out of the factory. Here, the package is shown from the top and bottom side with in blue the package material and in grey the in and output pads. Most of the time these pads are made of aluminium but other materials like gold and nickel are also used. The packaging material can be made of many types of materials like metal or ceramic but is generally a form of plastic. The most common plastics used are epoxies, silicones, polyurethanes or phenolics [6]. A package needs to fulfil many constraints regarding mechanical stresses, heat transfer, thermal expansion, electrical properties and production cost. Additives are used to tailor the plastic to its specific needs.

On the edge of the package, the in- and output pins are clearly visible. The big square in the centre is a heat sink. A setup like this is called a heat sink very-thin quad flat no lead (HVQFN)[7], which is one of many ways to package a chip.

Figure 2.2: Packaging of the chip

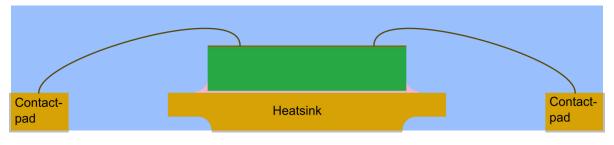

**Cross-section** Figure 2.3 shows the cross-section of the chip in the package. Now, the actual die is visible as shown in green. During packaging, the chip is mounted on the heat sink using a thermal conductive glue. In the chips used for this project, the heat sink is made of copper with an aluminium coating. This combination gives good thermal conductivity because of the copper centre, while the aluminium protects the copper against corrosion and makes it easier to connect to. Other combinations are also possible like silver or copper and aluminium alloys. More optimal shapes with fins have also been proposed. Additionally, the wire bonds are visible. These ensure that the die is connected to the pads on the outside. Wire bonds can be categorized into two aspects; the wire material and bonding

technique. Popular materials for wires are gold and copper but other materials like silver or aluminium are also used.

Regarding bonding techniques, there are three main techniques. The first and most common is ball bonding which makes use of a needle that at both points welds the wire to the bond pads. The first weld starts by heating the tip of the wire with an induced current. This forms a ball which is placed and welded onto a bond pad by applying heat, pressure and ultrasonic vibrations. The other end of the wire is welded using the second technique which is called wedge bonding. It uses the same principles as ball bonding except the creation of a ball is skipped over.

The third technique is compliant bonding. This technique, also referred to as solid-state bonding, mostly makes use of applying pressure with a small amount of heat. To prevent the sample and wire from too much pressure a compliant medium is used in between the bonding probe and the lower surface. This medium deforms slightly, thereby distributing the forces as required. After the wire bonding, a fluid packaging material is placed which hardens over time resulting in a well-protected chip.

Figure 2.3: Wirebonded cross-section

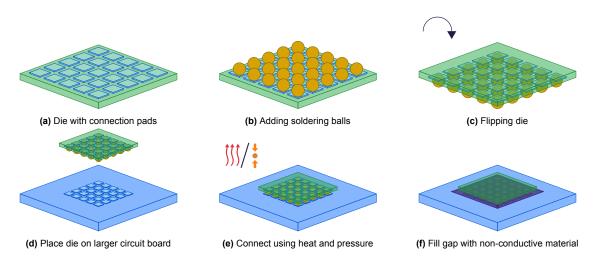

There exists a second method besides wire bonding which is called flip-chip. The flip-chip technique is used to create shorter wires, flatter packaging and is also useful in case of many contacts. This technique is technologically more difficult because of the constraints on stress and the flatness of both surfaces is much higher. That being said, the principle concept is quite straightforward to explain.

Figure 2.4 shows the basic steps. To start, the die is manufactured in the same way with the connection pads on top. Some steps are undertaken to improve the soldering and adhesion capabilities after which the soldering balls are applied. Then the chip is flipped over, aligned and placed on the larger circuit board. Using pressure and heat the balls are then soldered in place. Finally underfill is applied to help with heat conduction and distributing potential stress differences between the die and circuit board. This technique can also be used to stack multiple packages on top of each other which leads to Package-on-Package (PoP) chips, see section 2.1.2.

Figure 2.4: Cross-sections of a chip in package

#### Die

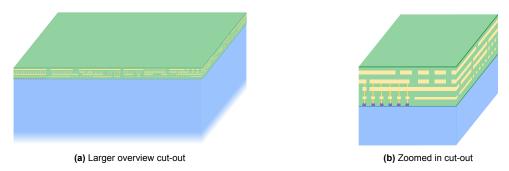

The die is by far the most complex structure inside the whole package and can be described as a small city with roads connecting all the houses. In this case, the roads would be the interconnects and the houses the transistors. Figure 2.5a shows a cut-out version of what a chip could look like with in yellow the interconnects and a little bit darker the vias (vertical interconnects). The chip from the figure shows four metal layers. However, modern chips can have more than 12 layers[8]. The purple blocks indicate a connection to the bulk (in blue) meaning those metal lines would either connect to ground or to any structure present in the silicon. The transistor would be located in the bulk touching the green area. To build this small city there is an almost standardized method consisting of a few general steps which will be discussed briefly below.

Figure 2.5: Cut-outs of the top of a chip

**Wafer** A die is a rectangular but mostly square integrated circuit (IC) and starts off as being part of a wafer. Figure 2.6 shows the first few steps. Wafers are made from a silicon ingot. The ingots are grown from a silicon seed also known as the Czochralski method[9]. This is a precise and controlled process which results in a large column of monocrystalline, very pure silicon. The process ensures that the silicon crystal structure is aligned and connected perfectly everywhere. Wafers have to be made so carefully to guarantee uniform electrical properties. In figure 2.6b such a column is shown. This column is then sliced into very thin disks called wafers as depicted in figure 2.6c. The wafers are still very rough after the slicing step which is not preferable. To get the smooth shining wafers many polishing and sometimes even etching steps are done. With newer technologies wafers have been increasing in diameter and thickness. Large diameters mean that there fit more dies on a single wafer or that the dies themselves can be larger. This means that the next processing steps will be more efficient. However, larger sizes will increase the risk of impurities and contamination and since the wafer also acts as a structural basis it should also be made thicker to prevent it from breaking. On the wafer, multiple dies are made in parallel in a grid pattern and are eventually cut out.

Figure 2.6: First steps of creating a wafer

**Doping** The die itself is built up in layers. The bottom layer will be the wafer, which because of the silicon structure will be great to build on and gives a mechanical strong foundation. The next step

is called doping where parts of the wafer are altered to create an excess (n-type) or a lack (p-type) of electrons. These doped parts are called negatively and positively doped wells because they exist at the surface and only reach a certain depth. They are made with processes like diffusion or ion implantation. With ion implantation, ions are shot into the silicon, altering the structure. Depending on the ion type, the acceleration given to the ion and the duration of the process the concentration and depth of the well can be controlled quite accurately. The most common ions for CMOS technology are Boron for p-type and Phosphorus and Arsenic for n-type wells. To make sure only certain parts are doped a protective layer shields the other areas. This layer is applied using lithography which will be discussed in the next section. Nowadays, often the silicon wafer itself is already doped during the growth of the silicon to reduce the time spent on p-type doping and guarantee a uniformly doped bulk, meaning the underside of the chip. After the doping, the surface is still flat but now the silicon is prepared for the transistors to be built.

**Lithography** Lithography itself consists of three steps. First, a thin film of photoresist is put on the mask using spin coating. The photoresist is a liquid containing three components; a resin which is the base, a sensitizer which reacts to light and a solvent to keep it a liquid. During spin coating, the photoresist is applied while the wafer is spinning. This results in an evenly spread thin layer without any bumps. Finally, the wafer is baked making the photoresist solid. The second step is to expose designated areas to light. For this step, a photomask is needed. This is a thin piece of glass made of nearly pure silicon dioxide therefore ensuring well-known, uniform optics. On top of this glass plate, a pattern is made out of a thin film of chromium. This mask is placed in between the light source and the wafer thereby blocking the light according to the pattern. The parts which are exposed to the light will be chemically changed. Finally, a developer is applied. At this point, it depends on whether a positive or negative photoresist is used. Positive photoresist which has been exposed will dissolve into the developer. With negative photoresist, the areas which were not exposed will dissolve. Now a pattern of protected and exposed areas is created on the wafer which can be used by for example etching or depositing. After these processes are done the remaining photoresist can easily be removed using, for example, a resist stripper which removes the adhesion effect of the photoresist.

**Etching and depositing** In an iterative process where lithography is combined with etching and depositing, removing and adding materials, the transistors are built up. Build on top of those transistors are the metal layers also called interconnects, with higher layers containing stronger signals and being therefore also physically larger. Once a layer is complete it is almost impossible to change anything below this layer. Therefore it is very important to consider all the materials and for example their melting point during the making of the fabrication process. For this project, a lot of these techniques will be considered and tested. Therefore the next paragraphs will briefly summarize the most common methods.

**Etching** is the removal of material from the waver or device. This can be done in two ways, namely wet or dry etching.

Wet etching or chemical etching is a method that mostly relies on the chemical reaction between the material that needs to be etched and the etchant, a liquid chemical. For wet etching, the sample is partially or fully submerged in an etchant. This etchant will then chemically and most of the time selectively react to one or more materials on the sample. This etching process is mainly determined by firstly the material that needs to be etched, secondly the etchant, thirdly the temperature and finally the time. Interesting structures and shapes can be made by careful selection of these variables like caves or wells with certain gradients for the walls.

Dry etching makes use of a plasma which releases neutrals and ions. Depending on the pressure in the chamber and the voltages of the magnetic fields applied to the plasma roughly three techniques can be described. At lower pressures, ion milling or sputter etching is done where ionized atoms are shot towards the surface to knock off atoms. In the middle sits reactive-ion etching (RIE) which makes use of large positive ions released by a plasma. These ions are attracted by a negatively charged wafer which results in the surface atoms getting knocked off because of momentum transfer or a chemical reaction. This process is much more selective than the previous technique. Finally, there is deep reactive-ion-etching (DRIE), a more refined implementation of RIE. DRIE exists of multiple short RIE etches with between each etch a deposition of a passivation layer to reduce the amount of sideways etching. All dry etching techniques are well suited for high aspect ratio etching where DRIE can give the most vertical walls.

There are also less precise ways to remove material. For example, milling or polishing where the chip is ground down or flattened using high-quality sandpaper and felt. This is often done with reverse engineering when a complete layer or large part of a chip needs to be removed.

**Depositing** is the addition of material onto the wafer or device. In this field of study, this mostly means adding a thin film of only a few atoms till a few micrometres thick onto the entire wafer. This film needs to be as uniform as possible and is made from a large range of materials. To fulfil all the needs of the industry there are roughly four techniques in use.

Thermal oxidation makes use of the very fundamental principle of oxidation. This technique is used to create a thin layer of oxide by exposing the layer to an oxidising agent under very high temperatures. Very pure steam is commonly used as an oxidising agent with a temperature ranging from 800 to  $1200^{\circ}C$  [10], [11]. Under these circumstances, for example, the silicon bonds with the oxygen in the water, creating a thin layer of silicon dioxide. It could be argued that this is not a deposition method as it consumes part of the silicon in the process however since this method is often part of constructing CMOS transistors it is placed in this section. In the CMOS transistor, the gate is insulated from the silicon with a thin silicon dioxide layer, hence this technique's potential use. To reduce cross-talk between the transistors more localized oxidation of silicon (LOCOS) can be done. Finally, nowadays trenches are made beforehand which then also get filled with the dielectric silicon dioxide called shallow trench isolation (STI) [12].

chemical vapour deposition (CVD) is a widely used method to deposit material on a wafer. The basic principle is a vacuum chamber in which the sample is placed together with one or more volatile precursors. The precursors are turned into vapours which in turn react with the surface of the wafer or decompose altogether to create a thin layer on the wafer. Mainly, four variables can change the process. First of all, adaptations can be made to accommodate solid or liquid precursor materials. Next, the pressure inside the chamber can be changed, resulting in better uniformity or higher aspect ratios [13]. Then there is the option to heat the chamber which is not only required for most recipes but is also a useful parameter to tune the growth rates. Last but not least a plasma can be created to increase the reactivity of the precursor. This will result in much lower operating temperatures. Depending on the plasma this can even be down to room temperature. Apart from these four options, there are plenty of other alterations which use different energy sources like UV light, combustion or lasers to let the chemicals react to the wafer.

As a result of the high demand for CVD, many varieties and adaptations were developed to fit all use cases. Three adaptations are worth mentioning in the context of this project, namely ALD, ICPECVD and capacitivily coupled plasma enhanced chemical vapour deposition (CCPECVD). ALD is a specialised form of CVD where the focus is to create one atom thick, uniform layers. To create a thin film, multiple ALD-cycles are done, each cycle consisting of multiple steps. Each step is carried out sequentially, contrary to CVD. The purpose of a step can vary from deposition, a chemical reaction or etching. The precursor used in each step is self-limiting which results in one atom thick layers. To ensure the steps happen sequentially, careful purging, cleaning and evacuation steps are performed in between.

ICPECVD and CCPECVD are two types of CVD where plasma is used to enhance the process. The addition of using a plasma means that processes which would otherwise require high chamber temperatures can now be done at very low temperatures like room temperature or around  $100 - 300^{\circ}C$ . Both induction and capacitive coupled plasmas have their benefits like low contamination risk for induction or lower deposition rates for capacitive coupled plasmas.

physical vapour deposition (PVD) most common implementations are sputtering or evaporation. Both make use of a vacuum chamber with a source which provides the material for the thin film. Often the source is charged negatively and the wafer positively to guide the source atoms. With sputtering the vacuum chamber is filled with an energized inert gas whose atoms are similar in mass to the source atoms. When the gas atoms collide with the source, source atoms are knocked off and momentum is kept due to similar mass. When the source atoms reach the wafer they stick to the surface thereby creating a thin layer. The source atoms can also stick to the walls of the chamber however they can be reused by bombarding them with ions or atoms. Like other techniques, this process is highly dependent on pressure, temperature and materials used. Evaporation, as the name already indicates, starts by heating the source till the point where it starts evaporating. The high vacuum causes the evaporated atoms to fly almost directly towards the wafer, without interacting with anything else. Once they collide with the wafer, due to the colder temperature of the wafer they immediately turn back to a solid state. These thin uniform layers are used in a wide variety of applications like rhin-film transistors (TVTs) [14].

Epitaxy is another form of deposition and relies on the fact that crystals can grow. Epitaxy is a refined process where the growth of the crystal is very well defined. It is a similar process with which wafers are made, see section 2.1.1. A crystal structure can have different orientations and the process can be tailored to make use of these characteristics. If tuned correctly, features can be grown on specific orientations while not being able to grow on other orientations. This is called grain-to-grain epitaxy. Epitaxy does not only grow the already present crystal but with the right choice of materials is also able to grow new materials on top. This is respectively called homo and hetero epitaxy. Finally, the growth can be limited to only one direction or in all directions. The latter is then called opotaxy. The method for actually growing the crystal can differ a lot. Under the right circumstances CVD or PVD can be used but also dipping the seed in a melt or covering it with a solid and heating it is being used [15].

#### Transistor

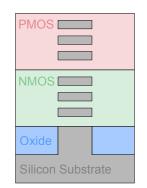

For the final step, a look at the transistor level is needed. This project aims to make a hole between the transistors to access one of the lower metal interconnects. The most standard representation of a CMOS transistor is given in figure 2.7a. In CMOS technology there are two types of transistors depending on the doping beneath the gate. N-channel metal oxide semiconductor (NMOS) and Pchannel metal oxide semiconductor (PMOS) behave the same but inversely. Because of a difference in the mobility of electrons compared to holes (the lack of an electron), careful sizing needs to be applied to ensure equal driving strength. By applying a voltage onto the gate, negative for NMOS and positive for PMOS, a channel is created in which respectively electrons or holes can travel from one side (source) to the other side (drain). The channel can take on different forms as indicated in figure 2.7b. The relation between gate-voltage and conductance is non-linear which is utilized to satisfy many different applications. There are no moving parts, meaning this is an electrically controlled solid state switch. These switches are connected to create an intricate circuit. With enough transistors, these circuits can perform the most complex functions. The connections between the transistors are called the interconnect and exist in multiple layers. Now it becomes clear why the bottom interconnects are of most interest. Because these interconnects are directly on top of the transistors, all the information will need to pass through them first before being processed.

(b) Transistors in different on states

Figure 2.7: Two basic CMOS transitors

One point of interest for device forensics is the memory inside a chip. More specifically the nonvolatile memory, meaning that the data will be kept intact when there is no external power supply. Within this category of memory are generally three options. Erasable programmable read-only memory (EPROM) is programmable using an external tool. Once programmed it retains its data until it is removed using for example UV-light. Since at this point the chip is already integrated into a PCB it is very hard to connect an external tool again to reprogram the EPROM. To solve this the electronically erasable programmable read-only memory (EEPROM) was invented. This device can be reprogrammed on chip. Although this device has great flexibility in being able to program individual bits it is not very information dense. Every bit needs two transistors which with increasing demand for data storage is not efficient enough. Over the years this amount of transistors per bit has decreased resulting in Flash memory. Nowadays, Flash memory is able to store multiple bits in one transistor. One drawback of Flash is that instead of being able to program single bits it is only possible to program in blocks of for example kilobytes. As of now, all non-volatile memory is built up using either floating gate transistors or charge traps. To get a better understanding of where the interesting data traces lie, let's have a closer look at how these transistors look and function.

First of all, they are based on the NMOS transistor as shown in figure 2.7. To lock the transistor into a state, thereby saving it as a zero or one, an extra gate is built on top of the previous one. Only this top gate, called the control gate (CG), is connected to the outside and the gate in the middle is insulated. This insulated gate is called the floating gate (FG) and acts as a charge storage. Using different physical phenomena like channel hot electrons (CHE) and Fowler-Nordheim tunnelling (FN) [16], [17] the floating gate can be charged or discharged. When the FG is charged it dampens the electric field from the CG which means that the threshold voltage of the transistor will be higher. To determine whether charge is stored on the FG a voltage in between the low and high threshold voltage is applied to the CG. If the transistor turns on, it means no charge was present which is interpreted as a zero (or one). Besides reading there are two more functionalities required from a memory cell. Namely writing the bit to a one and the possibility to erase a one. Figures 2.8 indicate how these functionalities take place. Very briefly, figure 2.8a shows the default of a memory cell. The two states in which the cell can be read are indicated in figures 2.8b and 2.8c. Figure 2.8d shows a high voltage, typically over 5V, being applied on the CG. These high voltages are not immediately available on the chip as they are higher than the supply voltage. Therefore charge pumps are created near Flash memory. By accumulating charge on capacitors they are able to provide the high voltages. The high voltage on the CG creates a large channel which in turn forms channel hot electrons. These electrons charge the FG and write an one into the memory cell. To remove the one, an opposite polarity voltage is applied to the CG thereby creating the FN effect and pulling out the trapped charges. This is indicated in figure 2.8e.

Figure 2.8: Different operating states of a memory cell

Charge traps work very similar to floating gate transistors with the exception that an insulator is used in the floating gate instead of a conductor. The charge is still injected using CHE however to remove the charge the FN tunnelling needs to be adapted. By changing the current to an induced field, holes are injected into the trap thereby removing the charge. Using charge traps has many benefits for the industry mainly in reduced cost, smaller feature sizes and higher reliability.

A memory block consists of many transistors and over the years many layouts of this principle have been developed but the most popular are the common ground NOR and the NAND configurations [18]. The schematics of these configurations can be found in figure 2.9. It immediately shows that there is a big difference in the way they are wired. Let's first focus on the NOR type Flash. This structure easily follows from putting many single memory cells in parallel. Expanding this topology with many bit lines in parallel will result in words, blocks and pages. By setting one of the word lines to high, this word can be read out on the bit lines. Because all transistors can be controlled directly, it has faster reading speeds compared to a NAND topology. As a result, it is often used to store execution code.

The NAND topology makes use of two extra transistors, one for ground select and one for bit select. Furthermore, the memory cells are placed in series. To read a word not only needs that specific line to be set at the intermediate voltage but the other word lines will need a voltage above the second threshold to make sure they conduct. Although this limits the reading speed it is well worth it. Because the transistors are in series it is now possible to add two extra transistors, one at each end. They can disconnect or connect a single bit line to the rest of the circuit. Thereby making it possible to address single bits. Furthermore, these transistors reduce a lot of wiring in the ground and bit line circuitry. In practice, this saves up so much space that a higher transistor density can be achieved using a NAND topology. NAND type Flash is mostly used for file storage.

To conclude, a memory block contains a lot of information that is always available to read. Getting information directly out of the Flash without using the controlling logic behind it won't be useful since there is no indication of what kind of information is acquired. Ideally, eavesdropping a bit line, word line or both will yield the most useful information. Combining this data with the code that is being executed could result in important data about its security like where certain encryption keys or bits are stored or what they are.

Figure 2.9: Different Flash architectures

Memory is a very important topic for new research. Together with a central processing unit (CPU), it is a fundamental part of a computer and memory performance is still lacking compared to the processing units. To improve the capabilities of memory without developing entire new processing techniques a new method was invented called package-on-package. It removes the memory from the main die and combines multiple memory dies to create one large memory chip. How technology moves forward is discussed in the next section with more details about package-on-package in section 2.1.2.

#### 2.1.2. Technological advancements

Although there might be earlier versions made, it is generally accepted that the first working transistor was demonstrated by Walter Brattain and John Bardeen to their colleagues at Bell Labs[19]. This was in the afternoon of 23 December 1947 and since then the developments regarding this device have taken off. What started as a point contact transistor, became a BJT, was slowly replaced by MOSFET and is nowadays more and more finFET. Only reducing the transistor size will not be enough as the industry still strives to uphold Moore's law[20] by trying to double the density every two years. More fundamental changes regarding chip design and fabrication will have to be made. The next sections will discuss what these new-generation transistors and chips will look like. The final section is a short discussion on how these advancements might impact the feasibility of backside contacting in the future.

#### Roadmap

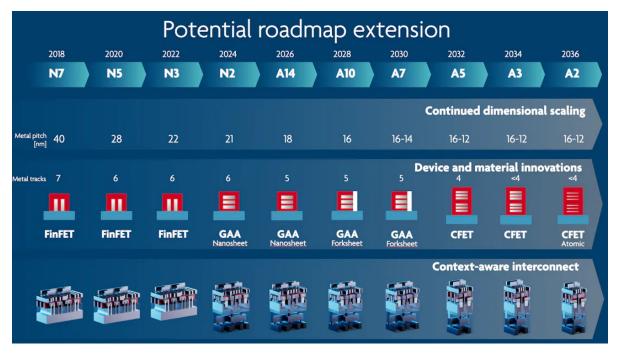

A great source to get an idea of the future of transistors is IMEC, the Interuniversity Microelectronics Centre. This institute provides a basis for all leading micro-electronics companies to work together towards new and improved technologies and their roadmap is therefore a good representation of what is currently in development. Their latest roadmap shows a GAA-NSFET, GAA-FSFET and CFET [21]. The roadmap depicted in figure 2.10 also shows that they expect that in the coming years, the technology will advance to below 10 Ångström ( $10\mathring{A} = 1nm$ ). These numbers are used to refer to the gate length of a transistor plus a few other features like the metal pitch. However, since the 45nm node the gate length reached its minimum without introducing many second-order effects[22]. From then on, the naming was used more symbolically to indicate the transistor density. The next paragraphs will discuss the new transistors in more detail.

Figure 2.10: Transistor roadmap presented by IMEC [21]

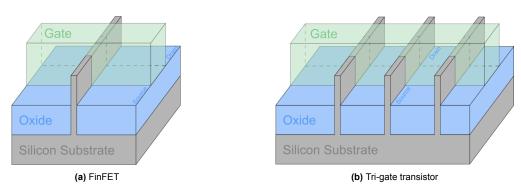

**FinFET** Since the beginning of the 2010s, FinFET transistors started being used in mass production [23], [24]. What sets FinFETs apart from previously used transistors is the three-dimensional structure. Figure 2.11a shows how the gate now wraps around the channel. This means that the same drain current can now be created with lower voltages, thereby reducing the power. Furthermore, this layout ensures faster switching speeds and a smaller footprint. In practice, CMOS transistors are often put in parallel to increase their driving capability. The same can be done with FinFET as figure 2.11b shows.

Figure 2.11: Schematic representations of FinFETs

**GAA-FET** In this section, the two variations of Gate-All-Around field-effect transistors will be discussed. These transistors are predicted to be the next breakthrough in transistor technology and are the industry's hope to keep scaling according to Moore's law. The new design comes with many benefits, as is indicated in the next few paragraphs, but also comes with significant challenges mainly in the form of higher fabrication complexity. New technologies like sidewall image transfer (SIT) for better resolution below 10nm, replacement metal gate (RMG) for better temperature budgets and internal spacers for more mechanical strength and reduced parasitic capacitance's [12], [25] are making the step to mass production of GAA-FET's more and more feasible. The development of these transistors is an ongoing field of research to achieve a fabrication technique which ensures high reliability and low impact of process variations.

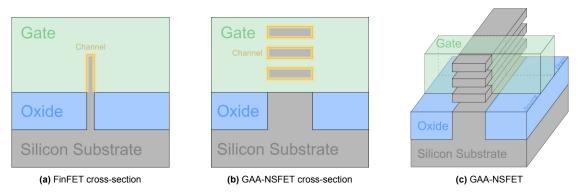

**Nanosheet** The next iteration of transistors that is currently being worked on are the GAA-NSFETs. In this design, the gate consists of a very thin layer of for example silicon, called a nano-sheet [26]. Figure 2.12b shows how the GAA-NSFET is an improvement on the FinFET. The gate now wraps around thereby creating more channel area which in turn reduces the short channel effects and results in better gate control. Instead of having multiple gates in parallel to improve driving performance, gates can now be stacked on top of each other. This saves valuable area and potentially allows for higher transistor density. Although IMEC suggests this layout because of better design control over the width and height of the sheets, other options with vertical sheets or nano-wires have also been proposed [27].

Figure 2.12: Schematic representation from FinFET to GAA-NSFET

**Forksheet** A logical improvement after the GAA-NSFET would be the implementation of GAA-FSFET. These structures are very similar with the exception that between the N-type and P-type doped regions a dielectric is placed. This means that the channels can be closer together, saving on precious surface area[28]. Furthermore, this layer shields not only the channels from each other but also the substrate from the doped regions, in turn saving a complex doping step during fabrication[29]. Figure 2.13 shows how this looks as a cross-section and how it relates to the previous nano-sheet design.

Figure 2.13: Schematic representation from GAA-NSFET to GAA-FSFET

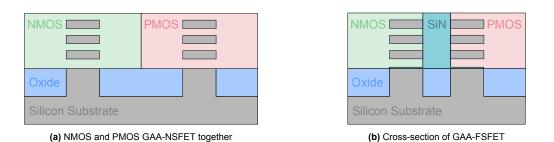

**CFET** Finally, as of now, all roadmaps end at the CFET technology. The main innovation compared to its predecessor GAA-FSFET is the fact that the negative and positive doped regions are now stacked. The stacked N-type and P-type regions look a lot like the layout of the complementary circuits that are designed today in CMOS, hence the name CFET. Figure 2.14 shows this structure from which it is visible that this technology has again a lower footprint. Compared to its predecessors, the high aspect ratio that comes from stacking structures on top of each other is an even bigger challenge. Time will tell what the limitations on for example the amount of stacked channels or the channel thickness are. In any case, these developments have the potential to start off the Ångström age.

Figure 2.14: Cross-section of a CFET

#### Additional advancements

Apart from optimizing the transistor density, speed and power consumption it is also necessary to develop the circuitry and interconnects around the transistors. Two of the most well-known obstacles are the memory wall and the power wall. Both limit the performance that can be extracted from the processor and chip. With increasing transistor density these problems get even more important and need a rigorous solution. Finally, there is a great demand from the industry to keep developing within the multi-purpose characteristic of CMOS. For example, high computing power chips for artificial intelligence (AI) or highly efficient chips for virtual reality (VR) headsets. As of now, there are three proposed and partially implemented solutions; backside power distribution network (BPDN), the use of chiplets and chip stacking.

**BPDN** BPDN has the potential to solve a lot of problems at once. Nowadays, the interconnect is situated on top of the transistors and consists of both the signal network and the power distribution network. By moving the power distribution to the backside of the chip, and burying it inside the silicon bulk, a lot of area is freed to improve the signal network. Its density can be improved, the lines can be shorter and the parasitic capacitance's will be lower meaning that the operating frequency can be higher. The power distribution network also benefits because there is again more space to place the network and it suffers less from leakage and the heat transfer will be easier. To connect the power to the transistors so-called through silicon vias will have to be implemented.

The major foundries have already agreed to research and implement the above-mentioned ideas to be able to connect and extract the maximum performance out of the new smaller and faster transistors discussed in the previous section 2.1.2 and avoid hitting a wall [30].

**Chiplets** Although the power and memory walls are partially solved by the BPDN there is another solution which can improve the performance of the chip even more. This is the use of chiplets. Chiplets are smaller chips that only contain part of an integrated circuit. By combining multiple different chiplets for example a larger processing unit can be built up. This way the chiplets can be designed independently meaning different technology nodes can be used. Furthermore, the design can become more optimized and better tested before implementation. This means a lower failure rate and because the chip itself is also smaller, fewer defects. On top of that, because the chiplets will contain mostly basic functionality they can be used in multiple systems. Additionally, when a larger integrated circuit breaks down, only the chiplet has to be replaced. Finally, by using chiplets it is possible to create larger chips and systems than would be possible on only one monolithic integrated circuit.

**Chip stacking** Advancements are also being made on a higher level. Another way to increase memory capacity and processing capabilities is to use more dies. These dies however need to communicate at high speeds meaning they need to be placed together as close as possible. This led to the implementation of 3D ICs. In 3D ICs, two or more dies are stacked on top of each other in one single package. The moment the dies are stacked in the process varies from wafer-to-wafer to die-to-die. It is even possible to have monolithic dies which grow a Si layer on top of which the second 'die' can be built. The stacked dies are connected using through-silicon-vias (TSV) and are mainly used for memory applications. This offers many benefits in decreased cost, area and power consumption and increased bandwidth, security and design options. There are however also some drawbacks like testing individual modules, design complexity and, because the TSVs are relatively big compared to transistors and other components, the overhead of the TSVs.

To tackle those disadvantages a new concept was brought to life, namely package-on-package. With PoP like the name suggests multiple packages are stacked on top of each other. In practice due to limitations in heat dissipation mostly 2 dies are stacked. The stacking happens using the flip chip technology discussed in section 2.1.1. Figure 2.15 shows the cross-section of how such a stack could look like. In this case, both 3D ICs and PoP are combined to create a complete chip. For example, the top package might be two memory dies while the bottom chip could contain the computational logic. There are many advantages to using this technique, two of which stand out. Firstly, the packages can be tested separately. This means that faulty chips can be taken out of assembly earlier on, thereby increasing the yield. The second one is the flexibility of stacking different packages. If designed correctly, combinations can be made and the customer can select which chip combination suits their demands best.

#### Figure 2.15: Chip stacking

#### Limitations

Comparing these technological advancements against the goal of this project shows very clearly that accessing the lower interconnects will become more and more difficult. With higher transistor density the free space to create a hole will become smaller and less frequent. Higher aspect ratios in for example FinFETs and stacked transistors show that the the holes also need to be deeper. That is if the backside stays available. With the introduction of the BPDN, thinning the backside will no longer be possible and maybe the frontside will become more attractive again. The same can be said with stacked dies where maybe holes need to be made from the side or chips need to be reconstructed after package removal and drilling.

In short, preferably a scalable technique needs to be found which has to be able to adapt to the challenges of the future. By already striving to create holes and access the bottom and smallest interconnects it can be proven that this new concept will be useful in the future. Luckily, some of these new techniques like internal spacers could also be very helpful to achieve the resolution and aspect ratio that is required.

Probably one of the biggest challenges will not only be to get a signal from one of the interconnects out of the chip but also to be able to detect it. Since these signal strengths become lower and lower to reduce power consumption it will be harder to read and interpret them. This however is out of the scope of this project and will require further research.

#### 2.1.3. Acquiring data

Important data that is stored on a system on a chip (SoC) is most of the time encrypted. Because of the high throughput of data that is required in modern devices, this encryption is done by designated cryptographic modules. These encryptions are designed to be mathematically very hard to crack so it is easier to extract the encryption key in some other way. As of now, there are mainly two well-known concepts to hack into single chips; side channel analysis and fault injection. After the chip has been processed using the methods developed within this project it will most likely be subject to either one of these methods to get data out of the chip. A little bit of background information about these techniques will therefore be helpful to determine what possible requirements are. Furthermore finding out their limitations could point in a new direction in which this concept can contribute the most.

#### Side channel analysis

Side channel analysis or SCA for short makes use of the information that is leaked on the side channels like computation time, power consumption, optical observations or electromagnetic radiation. The relation between this information and the activity of the encryption module can help predict encryption keys[31]. Techniques evolved from simple power analysis (SPA) to differential power analysis (DPA) which includes more signals that are analysed and finally correlation power analysis (CPA) which not only uses a modelled power consumption but also takes into account the real power consumption. On top of that electromagnetic sensors are added to detect the EM radiation from the device to get a more complete model.