## Power RF-DAC

## The Design of a LDMOS Class-E SMPA DRAC with a CMOS Driver

by

R.J. Bootsman

to obtain the degree of

Master of Science in Electrical Engineering

at the Delft University of Technology, to be defended publicly on Tuesday January 30, 2018 at 15:00

Student number: 4093844

Project duration: September 8, 2016 – November 1, 2017

Thesis committee: Prof. dr. ing. L.C.M. de Vreede, TU Delft, Chair ELCA, supervisor

Dr. ir. S.M. Alavi, TU Delft, ELCA

Prof. dr. J.E.J. Schmitz, TU Delft, Dean EEMCS

Dr. F. van Rijs, Ampleon, Innovation Manager and RF Architect

Ir. R.M. Heeres, Ampleon, Principal RF Engineer

This thesis is confidential and cannot be made public until December 31, 2021.

An electronic version of this thesis is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

Cover Photo Information: Radio Mast and Faculty by Sunrise

Camera NIKON D7200

Sigma 105 mm f/2.8 EX DG OS HSM Lens

Date Time Original 2018:01:07 09:02:08

Focal length 105 mm Aperture f/5.6Exposure time 1/200s

ISO 200

Flash off, did not fire

Copyright ©2018 Robert Bootsman

Shown in foreground is a radio mast for telecommunications owned by T-Mobile, put into operation on the 24th of November 2017. It provides 4 types of communication: a microwave (μW) transmission link, GSM1800, UMTS and LTE. The microwave transmission link is directed at 199,1° from north, operates at 32,771 GHz with an output power of 3,6 dBW. The main lobes of the antennae for the remaining types are directed at 10°, 120° and 240° from north.

| Туре         | Direction          | Frequency  | Power    |

|--------------|--------------------|------------|----------|

|              | 10°                | 1848,8 MHz | 32,1 dBW |

| GSM1800      | 120°               | 1872,2 MHz | 32 dBW   |

|              | 240°               | 1874,4 MHz | 32 dBW   |

|              | 10°, 120° and 240° | 950 MHz    | 32,2 dBW |

| UMTS and LTE | 10°, 120° and 240° | 1860 MHz   | 32,1 dBW |

|              | 10°, 120° and 240° | 2144,7 MHz | 32,6 dBW |

Shown in the background is high rise building of the faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS) of the Delft University of Technology (TU Delft), where the research for this thesis was conducted. This building is more commonly known as 'het EWI-gebouw', or simply EWI, and is situated along the Mekelpark. The high rise building is in use since 1969. With 23 floors it stands 90 m tall making it the second highest building of Delft, right after the Nieuwe Kerk. The building is designated as a municipal monument. As the radio mast is placed on a flat building lot it allows for a nice clear view to the faculty of EEMCS.

## **Summary**

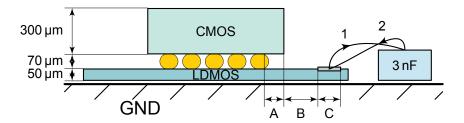

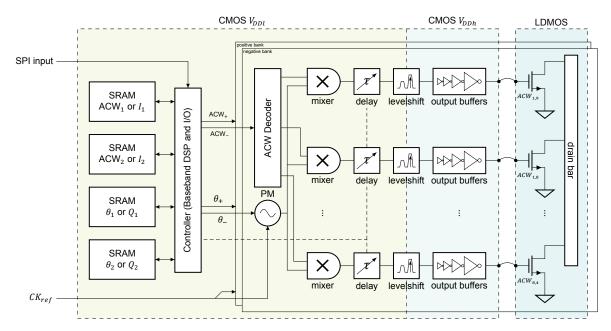

This document explains the design of a power RF-DAC, with as main focus to seek improvement in power efficiency for mobile Radio Frequency (RF) communication applications. For this reason a polar RF-DAC topology is selected. Due to limitations in current technology the power RF-DAC can not be integrated on one chip, therefore a combination of two chips is proposed to overcome these limitations. For the first chip a linear, high power analog LDMOS technology by Ampleon is proposed to implement a power Digital-to-RF-Amplitude Converter (DRAC) in and its design is the main focus of this thesis. The second chip will function as its driver and will be made in high integration, high speed digital 40 nm CMOS by TSMC, which has a maximum supply voltage for thick oxide devices of 2,5 V. The two chips will be connected using flip-chip bonding, allowing a maximum operation frequency of 3 GHz.

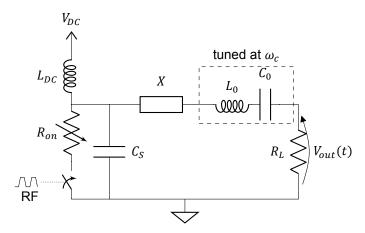

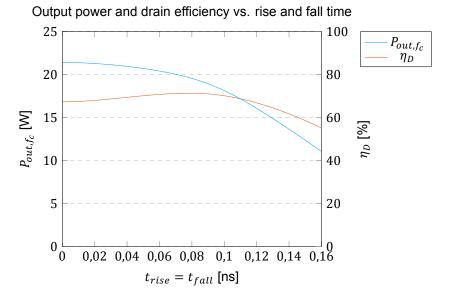

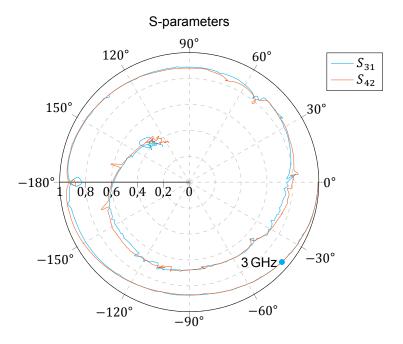

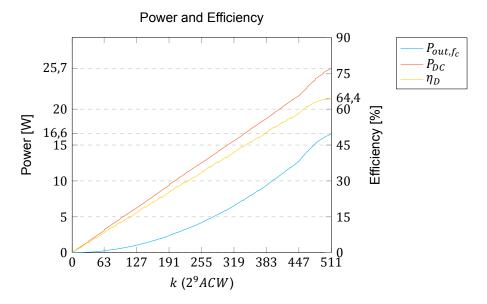

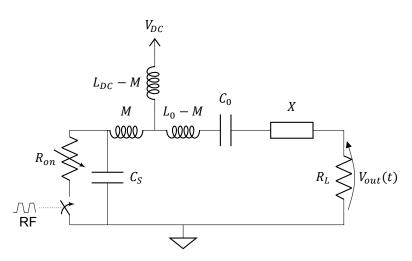

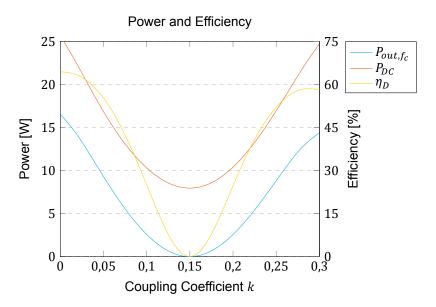

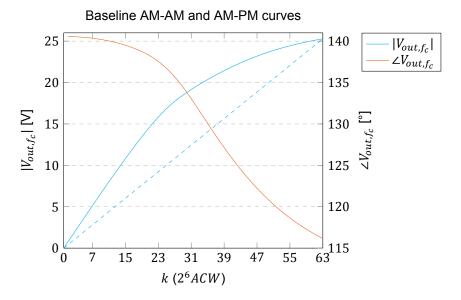

The LDMOS DRAC is designed to operate as non-linear Switch-Mode Power Amplifier (SMPA), allowing for high drain efficiencies. A Class-E matching network is used for the SMPA DRAC as it can incorporate the LDMOS output capacitance. The output voltage can be varied by modulating the Class-E transistor on-resistance, done by switching differently sized transistors. A LDMOS Total Gate Width (TGW) of 51 mm is used. When driven by a 2,0 V peak-to-peak square wave, post-layout simulations show a peak fundamental output power of  $P_{out,f_c} = 16,6$  W with a drain efficiency of  $\eta_D = 64,4$ % at the maximum operation frequency of 3 GHz.

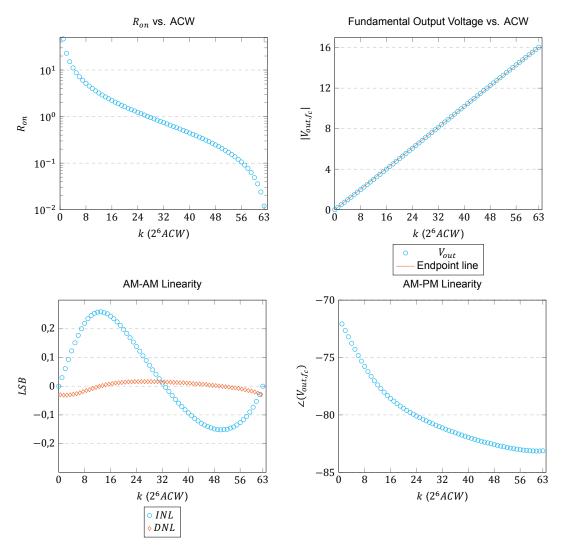

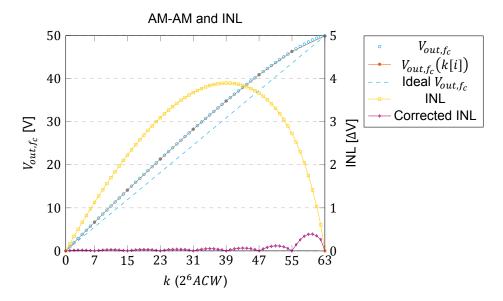

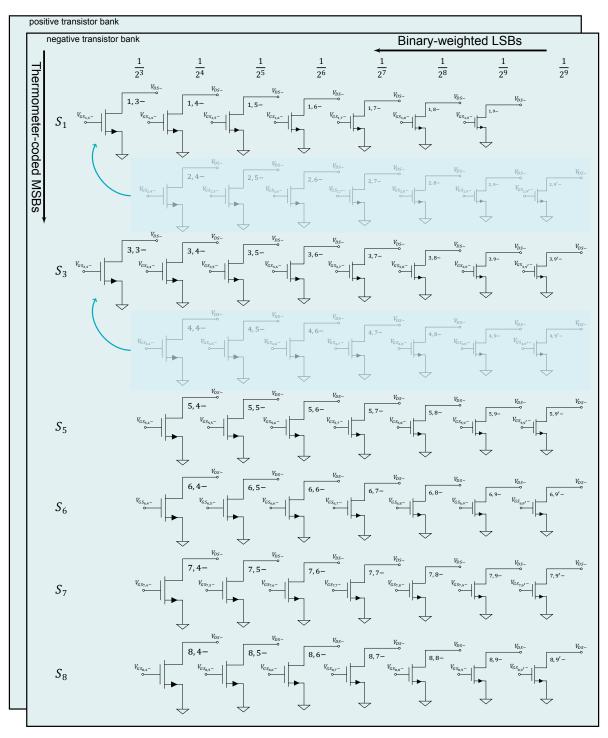

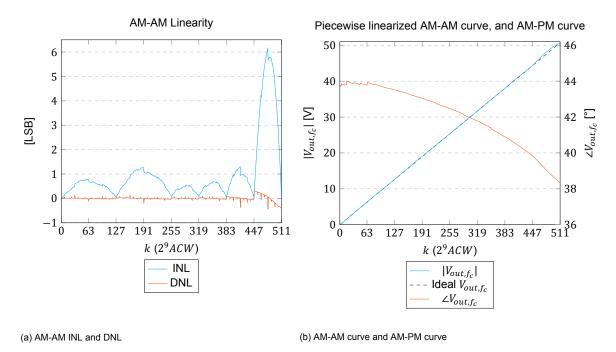

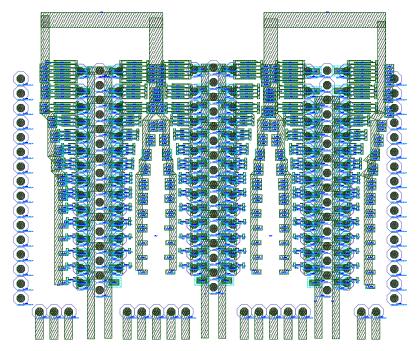

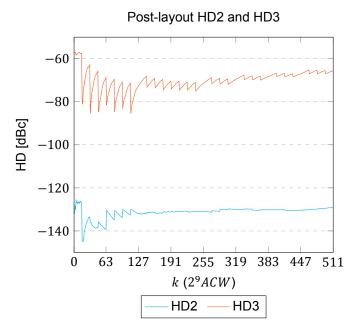

The DRAC has a dual line-up topology, primarily intended for push-pull operation to mitigate even orders of harmonic distortion. The TGW is divided over these two transistor banks. Within those banks the TGW is spread over 6 thermometer-coded segments and within these segments into a 6 bit binary-weighted fashion, creating an internal resolution of  $N_b=9$  bit which should allow for ACPR levels better than 50 dBc. Piecewise AM-AM linearization is applied on transistor level by applying a scaling factor to each of the segments. This results in a total of 2×43 individually sized LDMOS transistors. Static post-layout simulations show a peak Integral Nonlinearity (INL) error of  $INL_{pk,LSB}=10.7$  LSB. This error can be compensated for using Digital Pre-Distortion (DPD).

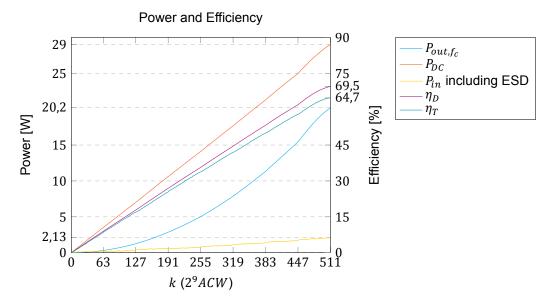

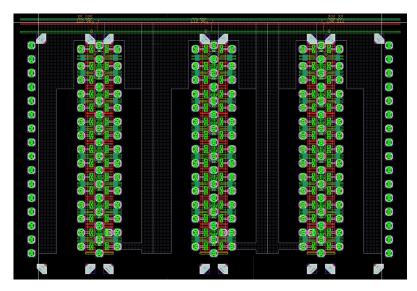

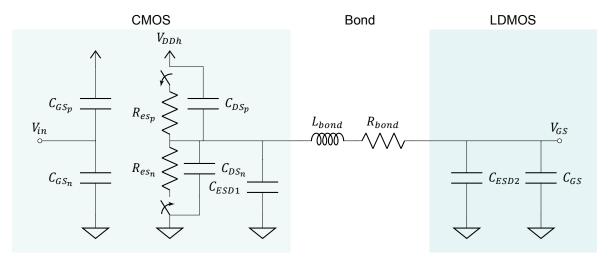

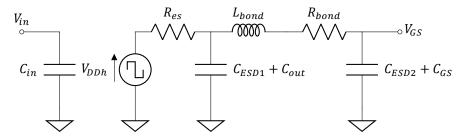

The CMOS driver operates in Class-D, which means the required drive power for the DRAC is proportional to  $fCV^2$ . The peak input power for the LDMOS gate capacitances is  $P_{in}=0.91\,\mathrm{W}$  for maximum operation frequency and DRAC output power. However, as there are two physically separate chip dies, both chips need to be provided with Electro-Static Discharge (ESD) protection which raises the required peak input power to  $P_{in}=2.13\,\mathrm{W}$ , resulting in a peak total DRAC efficiency of  $\eta_T=59.5\,\%$ . This required input power scales linearly with DRAC fundamental output voltage, or with the square root of the fundamental output power.

The CMOS driver output buffers consist of a chain of inverters increasing in size, which have an estimated DC power consumption 4,63 times the output power, resulting in a peak power consumption of 9,45 W. This factor remains constant for all possible values of output power (implying constant 'driver efficiency'), making it that driver power consumption scales linearly with required DRAC input power. This results in a lower average driver power consumption compared to an analog system where a Class-A or Class-AB predriver would be used. This also means that the RF-DAC system is frequency agile, implying that the operational frequency is only dependent on external output matching network components of the DRAC.

Including all other power consumptions of the CMOS driver, including two phase modulators and DSP, its expected peak total power consumption lands at 9,78 W. Using this an estimate for peak system efficiency can be made, giving  $\eta_{T,system}=46,7\%$  at 3 GHz and peak DRAC output power. Using statistical data for a modulated signal with  $PAPR=8,0\,\mathrm{dB}$  the average system efficiency is calculated to be  $\overline{\eta_{T,system}}=21,8\%$  without the use of any energy efficiency enhancement techniques. As the DRAC design features a dual line-up topology, the push-pull operation could be switched out for e.g. Doherty operation to improve the average system efficiency, but this will something for future research.

## Acknowledgments

This thesis is written in assignment of the Electronics Research Laboratory (ELCA) department at the faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS) of the Delft University of Technology (TU Delft). It is the final assessment for the completion of the master Electrical Engineering, track Micro Electronics.

Upon starting my master in the direction of Micro Electronics I did not yet know what specialization to pursue. At first I aimed for pure digital design, but at some point I wanted to do 'something' on the border between analog and digital. The course on digital RF was recommended to me with that idea in mind, which caused me to take the RF specialization courses in the subsequent semester. This resulted in me wanting to do a thesis project related to RF-DACs.

During the time working on this thesis project I have learned a lot, which I could not have done on my own. I take this opportunity to express my gratitude first towards my supervising professor, Leo de Vreede, for the time he was willing to make available for me, his support, enthusiasm and knowledge on this topic, the useful discussions and the feedback which all enabled me to get to this result.

Secondly I thank everyone in the ELCA group that shared their knowledge with me. It accelerated the design process for me as I could build upon previous research. In that sense it is truly a team effort. By name, I thank Earl McCune for interesting discussions and his ability to break complex matter down to extremely simple, yet surprisingly accurate, examples (of which the 'variable resistor' implementation of a DAC is a prime example), Morteza Alavi for his deep theoretical knowledge on RF-DACs, Mohsen Hashemi for providing me with good pointers for implementing the DRAC topology and transistor level AM-AM linearization, Atef Akhnoukh for his experience on the CMOS ESD protection and making the proposed CMOS layout possible and Yiyu Shen for his knowledge on CMOS design and according power consumptions which allowed me to make an estimation of system performance.

The research was done at the TU Delft, but with support from Ampleon. I thank Ampleon for their support during my thesis work and specifically Rob Heeres for his time on helping to creating the layout for the LDMOS DRAC and Fred van Rijs for supplying information on the LDMOS devices and the 'customization' options, such as the  $V_T$ -shift.

This thesis is the crown on a wonderful period as student at the TU Delft, for which I owe many thanks to my parents and friends. I hereby also thank my study association, the Electrotechnische Vereeniging (ETV), that facilitated connecting with a lot of people in Electrical Engineering and allowed me to quickly find new friends in Delft. Where the TU Delft taught me the essential academic and soft skills, the ETV and the committee work I have done there allowed me to further develop my soft skills and myself.

Lastly, I would like to thank the LaTeX community for the upkeep of the software and related packages, such as (Circui)TikZ and PGFPLOTS, that I could use to typeset this thesis and create most of the illustrations, and Stack Exchange for solving the many headaches related to LaTeX encountered during the writing process of this thesis.

R.J. Bootsman Delft, January 2018

## Contents

|   | <b>5</b> u      | ımma  | ary                                                             | V   |  |  |  |

|---|-----------------|-------|-----------------------------------------------------------------|-----|--|--|--|

|   | Ac              | knov  | wledgments                                                      | vii |  |  |  |

|   | List of Figures |       |                                                                 |     |  |  |  |

|   | Lis             | st of | Tables                                                          | χv  |  |  |  |

|   | 1               | Intro | oduction                                                        | 1   |  |  |  |

|   |                 | 1.1   | Growing Required Wireless Data Capacity                         |     |  |  |  |

|   |                 |       | 1.1.1 Energy consumption                                        |     |  |  |  |

|   |                 | 1.2   | RF Transmitter Architectures                                    |     |  |  |  |

|   |                 |       | <ul><li>1.2.1 Analog RF TX Architectures</li></ul>              |     |  |  |  |

|   |                 | 1.3   | Thesis Goals                                                    |     |  |  |  |

|   |                 | 1.4   | Thesis Organization                                             |     |  |  |  |

|   | <b>.</b>        |       |                                                                 | _   |  |  |  |

| ı |                 | eory  |                                                                 | 9   |  |  |  |

|   | 2               | PA I  | Basics  Definitions                                             | 11  |  |  |  |

|   |                 | Z. I  | 2.1.1 PA Power                                                  |     |  |  |  |

|   |                 |       | 2.1.2 Gain                                                      |     |  |  |  |

|   |                 |       | 2.1.3 Efficiency                                                |     |  |  |  |

|   |                 |       | 2.1.4 Linearity                                                 | 13  |  |  |  |

|   |                 |       | 2.1.5 Peak-to-Average Power Ratio                               |     |  |  |  |

|   |                 | 2.2   | Amplifier Power Relations                                       |     |  |  |  |

|   |                 | 2.3   | Amplifier Classes                                               |     |  |  |  |

|   |                 |       | <ul><li>2.3.1 Device Model</li></ul>                            |     |  |  |  |

|   |                 |       | 2.3.3 Saturated Transconductance Amplifiers and Harmonic Tuning |     |  |  |  |

|   |                 |       | 2.3.4 Switching Amplifiers                                      |     |  |  |  |

|   |                 | 2.4   | Conclusion                                                      |     |  |  |  |

|   | 3               | RF-   | DAC Basics                                                      | 33  |  |  |  |

|   |                 | 3.1   | DAC structures                                                  |     |  |  |  |

|   |                 |       | 3.1.1 Oversampled DACs                                          |     |  |  |  |

|   |                 |       | 3.1.2 Nyquist rate DACs                                         |     |  |  |  |

|   |                 | 3.2   | 3.1.3 DAC Performance Metrics                                   |     |  |  |  |

|   |                 | 3.2   | 3.2.1 Frequency Domain Analysis                                 |     |  |  |  |

|   |                 |       | 3.2.2 DRAC Performance Metrics                                  |     |  |  |  |

|   |                 | 3.3   | Towards a Power DRAC Implementation                             |     |  |  |  |

|   |                 | 3.4   | Conclusion                                                      | 46  |  |  |  |

| Ш | lm              | plen  | nentation                                                       | 47  |  |  |  |

|   | 4               | •     |                                                                 | 49  |  |  |  |

|   | •               |       | Technology                                                      |     |  |  |  |

|   |                 |       | 4.1.1 Fraunhofer IAF GaN25                                      |     |  |  |  |

|   |                 |       | 4.1.2 Ampleon LDMOS LM8                                         |     |  |  |  |

|   |                 |       | 4.1.3 Technology Evaluation                                     | 56  |  |  |  |

x Contents

|     | 4.4        | Resolution and Dynamic Range  Driver  4.3.1 Driver Model  4.3.2 Inter-Chip Connection Methods  4.3.3 Driver Evaluation  Circuit Topology.  4.4.1 DRAC Structure  4.4.2 Single-Ended or Push-Pull Topology  Conclusions. | 58<br>59<br>61<br>64<br>65<br>65<br>67 |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 5   | LDM        | MOS DRAC Implementation                                                                                                                                                                                                 | 71                                     |

|     |            | Technology Characterization                                                                                                                                                                                             | 71                                     |

|     |            | 5.1.1 Finding a Design Set                                                                                                                                                                                              |                                        |

|     | F 0        | 5.1.2 The AM-AM Curve                                                                                                                                                                                                   |                                        |

|     | 5.2        | Implementing the DRAC                                                                                                                                                                                                   |                                        |

|     |            | 5.2.2 Simulation Setup with Driver Model                                                                                                                                                                                |                                        |

|     | 5.3        | Layout                                                                                                                                                                                                                  |                                        |

|     | 0.0        | 5.3.1 Layout Version 1                                                                                                                                                                                                  |                                        |

|     |            | 5.3.2 Layout Version 2                                                                                                                                                                                                  |                                        |

|     | 5.4        | Conclusion                                                                                                                                                                                                              | 98                                     |

| 6   | CMC        | OS Driver                                                                                                                                                                                                               | 101                                    |

| Ü   | 6.1        | Driver Requirements                                                                                                                                                                                                     |                                        |

|     | 6.2        | ·                                                                                                                                                                                                                       |                                        |

|     |            | 6.2.1 Driver Model Revisited: Inverter Delays                                                                                                                                                                           |                                        |

|     |            | 6.2.2 Designing the Inverter Chain                                                                                                                                                                                      |                                        |

|     |            | 6.2.3 Levelshifter                                                                                                                                                                                                      |                                        |

|     |            | 6.2.4 Complete Output Chain                                                                                                                                                                                             |                                        |

|     | 6.3        | Supply Decoupling                                                                                                                                                                                                       |                                        |

|     | 6.4<br>6.5 | CMOS Driver Implementation Ideas                                                                                                                                                                                        |                                        |

|     | 0.5        | 6.5.1 Estimation of Future System Performance                                                                                                                                                                           |                                        |

|     | 6.6        | Conclusion                                                                                                                                                                                                              |                                        |

| _   |            |                                                                                                                                                                                                                         |                                        |

| 7   |            |                                                                                                                                                                                                                         | 117                                    |

|     |            | Recommendations for Further Work                                                                                                                                                                                        |                                        |

|     | 1 .2       | 7.2.1 Short-Term Future Work                                                                                                                                                                                            |                                        |

| _   |            |                                                                                                                                                                                                                         |                                        |

| Α   |            |                                                                                                                                                                                                                         | 123                                    |

|     |            | Design Set Example Class-E                                                                                                                                                                                              |                                        |

|     |            | Harmonic Distortion of Designed DRAC.                                                                                                                                                                                   |                                        |

|     |            | Mutual Inductance                                                                                                                                                                                                       |                                        |

|     |            | OTA Transistor Widths                                                                                                                                                                                                   |                                        |

| В   | LDM        | MOS Case Study: A Higher Drive Voltage                                                                                                                                                                                  | 129                                    |

|     |            |                                                                                                                                                                                                                         | 133                                    |

|     |            |                                                                                                                                                                                                                         | 137                                    |

|     | ossai      |                                                                                                                                                                                                                         | 13 <i>1</i><br>141                     |

|     | rony       |                                                                                                                                                                                                                         | 141<br>143                             |

|     | mbol       |                                                                                                                                                                                                                         | 143<br>147                             |

| U y | וטטווו     |                                                                                                                                                                                                                         | . +/                                   |

## List of Figures

| 1.1  | Illustrating today's need for connectivity                                                           | 2        |

|------|------------------------------------------------------------------------------------------------------|----------|

| 1.2  | Representation of $g(t)$ in the complex plane                                                        | 3        |

| 1.3  | Examples of analog modulation architectures                                                          | 4        |

|      |                                                                                                      |          |

| 1.4  | Digital polar TX architecture                                                                        | 5        |

| 1.5  | Digital I/Q TX architecture                                                                          | 6        |

| 1.6  | Combined RF-DAC and PA TX architecture                                                               | 6        |

| 2.1  | Power flows in a general PA                                                                          | 11       |

| 2.2  | Different power gain measures                                                                        | 13       |

| 2.3  | Generalized PA                                                                                       | 15       |

| 2.4  |                                                                                                      | 17       |

|      | Simple FET model                                                                                     |          |

| 2.5  | Switched FET model                                                                                   | 19       |

| 2.6  | FET <i>I-V</i> curves                                                                                | 19       |

| 2.7  | FET <i>I-V</i> curves and example resistive load-line                                                | 20       |

| 2.8  | Circuit topology of a transconductance PA                                                            | 21       |

| 2.9  | Class-A drain waveforms and load-line                                                                | 21       |

|      | Class-AB, B and C drain waveforms and load-lines                                                     | 22       |

|      |                                                                                                      |          |

|      | Performance of the different ideal transconductance amplifier classes                                | 24       |

|      | Saturated Class-A drain waveforms and load-line                                                      | 24       |

| 2.13 | Saturated Class-B drain waveforms and load-line                                                      | 24       |

| 2.14 | Circuit topology of a Class-F PA                                                                     | 25       |

|      | Circuit topology of a Class-F PA with a transmission line                                            | 25       |

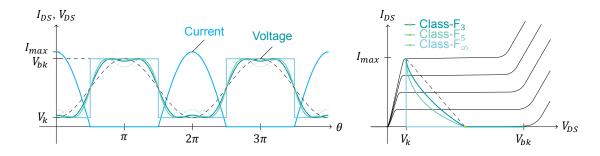

|      | Class- $F_3$ , $F_5$ and $F_\infty$ drain waveforms and load-line and Class-B dashed for reference . | 26       |

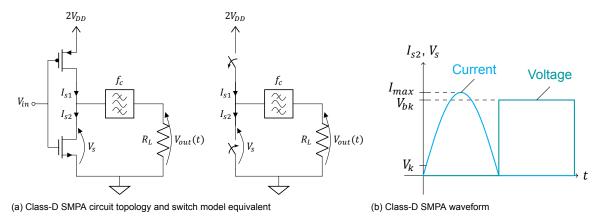

|      | Class-D SMPA circuit topology and waveforms                                                          | 27       |

|      |                                                                                                      |          |

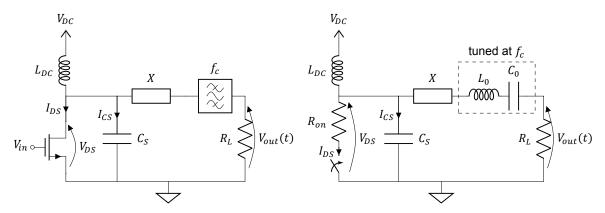

|      | Class-E SMPA circuit topology and switch model equivalent                                            | 27       |

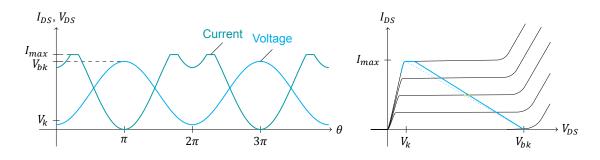

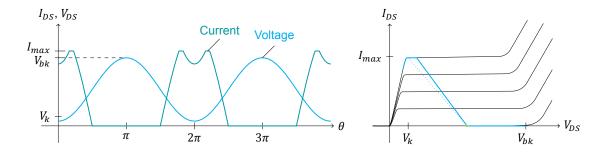

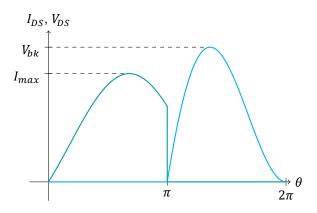

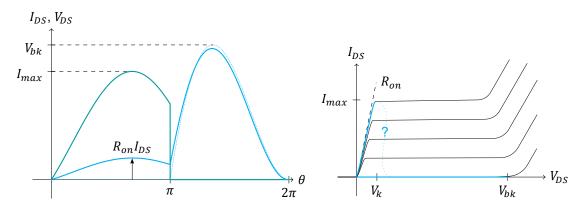

|      | Class-E SMPA waveform                                                                                | 29       |

| 2.20 | Class-E SMPA waveform for non-zero $m$ and corresponding load-line $\ldots \ldots \ldots$            | 30       |

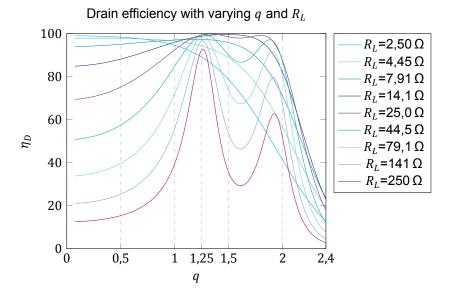

| 2.21 | Drain efficiencies for varying $q$ and $R_L$                                                         | 31       |

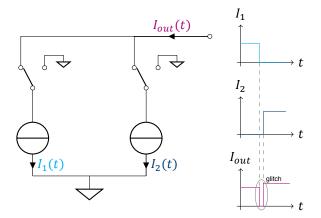

| 3.1  | Simplified DAC circuit diagram                                                                       | 34       |

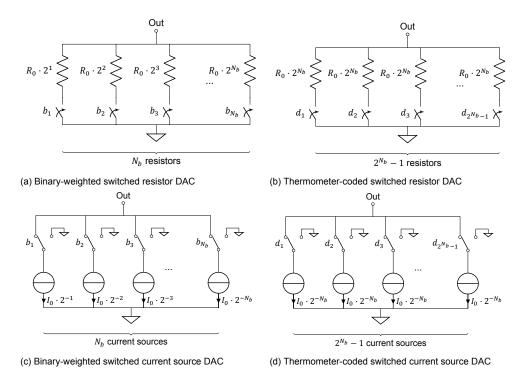

| 3.2  | Switched circuit quantity DAC implementations                                                        | 35       |

| 3.3  | Origin of glitches                                                                                   | 35       |

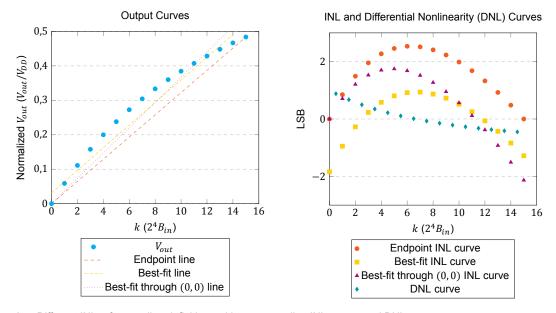

| 3.4  | Different INL reference line definitions with corresponding INL curves and DNL curve                 | 37       |

|      |                                                                                                      |          |

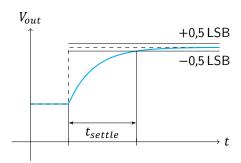

| 3.5  | DAC settling time                                                                                    | 38       |

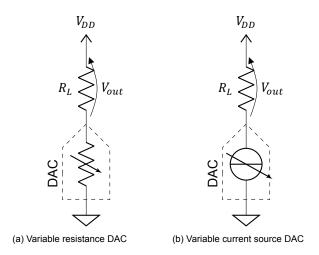

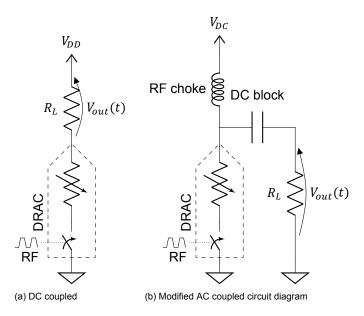

| 3.6  | Simplified variable switched resistance DRAC circuit diagrams                                        | 40       |

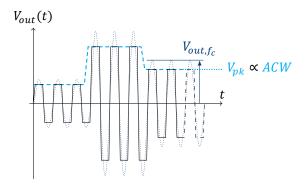

| 3.7  | DRAC time domain waveform                                                                            | 40       |

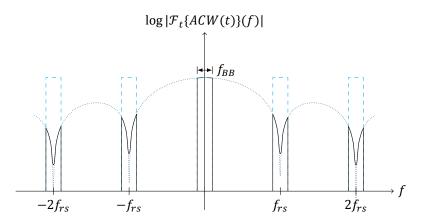

| 3.8  | Baseband ACW frequency spectrum with ZOH-effect                                                      | 42       |

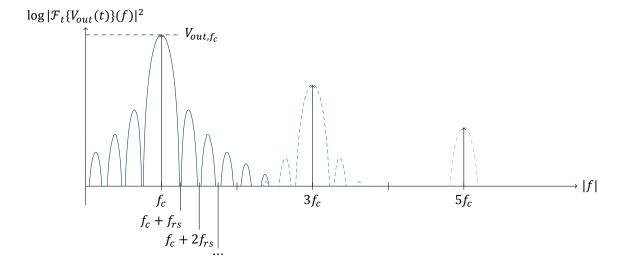

| 3.9  | Upconverted bandpass RF absolute frequency power spectrum with ZOH-effect and har-                   |          |

|      | monic replicas                                                                                       | 42       |

| 2 10 |                                                                                                      | 43       |

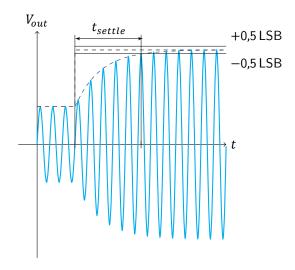

|      | DRAC settling time                                                                                   |          |

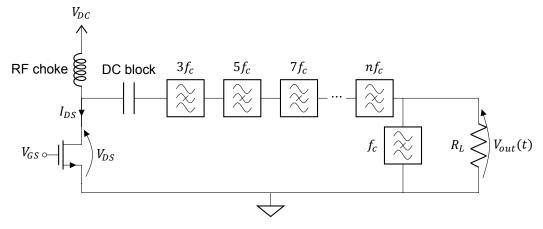

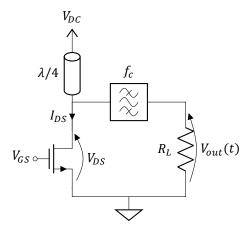

|      | Class-E SMPA DRAC                                                                                    | 44       |

| 3.12 | Ideal switch Class-E DRAC output curves                                                              | 45       |

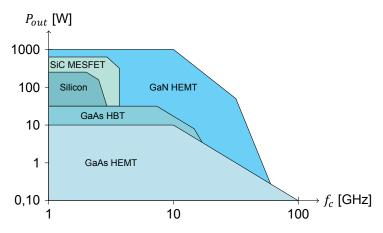

| 4.1  | Technology comparison in terms of output power and speed [35]                                        | 49       |

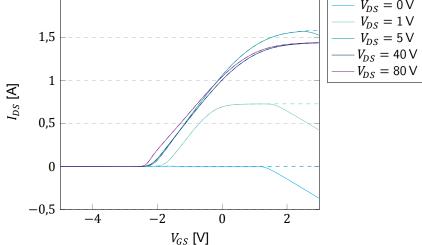

| 4.2  | GaN25: DC $I_{DS}$ - $V_{GS}$ curves                                                                 | 51       |

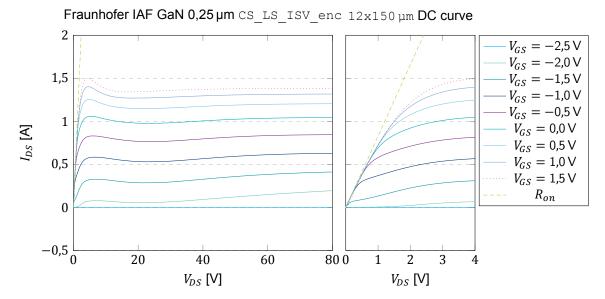

| 4.3  | GaN25: DC $I_{DS}$ - $V_{DS}$ curves                                                                 | 52       |

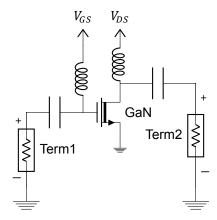

| 4.4  | S-parameter simulation circuit                                                                       | 52       |

|      | GaN25: Drain to source resistance as function of $V_{GS}$ to determine $R_{on}$                      | 53       |

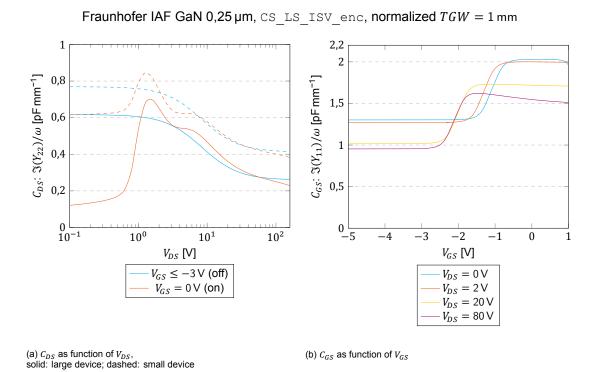

|      | GaN25: Non-linear canacitance characterization                                                       | 53<br>54 |

| /I D | Ganzo Mon-inear canacilance characterization                                                         | 2/1      |

xii List of Figures

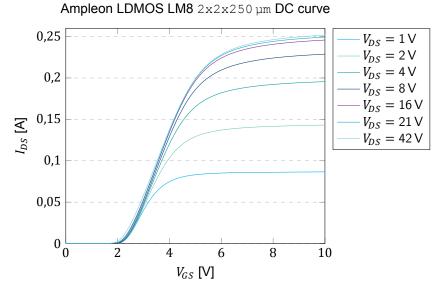

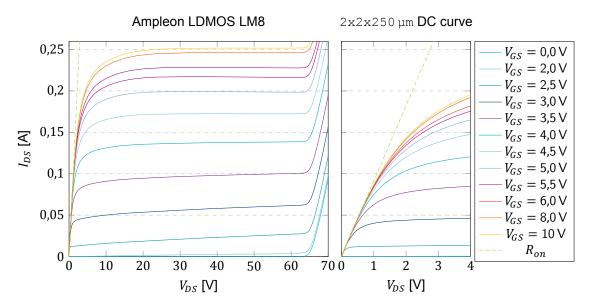

| 4.7  | LDMOS LM8: DC $I_{DS}$ - $V_{GS}$ curves                                                       | 55  |

|------|------------------------------------------------------------------------------------------------|-----|

|      | LDMOS LM8: DC $I_{DS}$ - $V_{DS}$ curves                                                       | 56  |

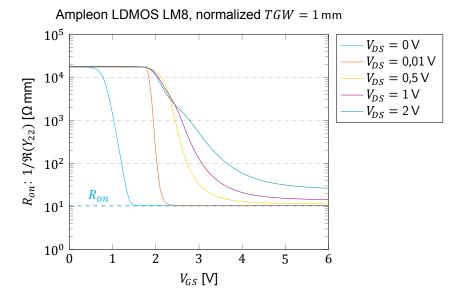

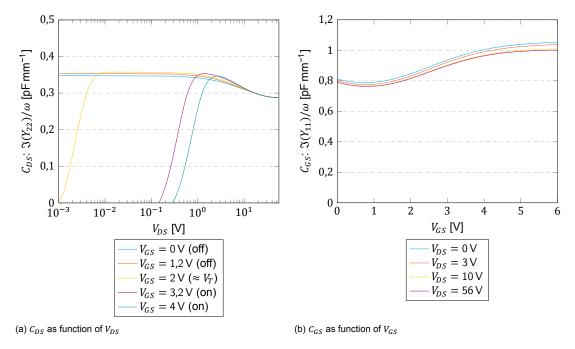

| 4.9  | LDMOS LM8: Drain to source resistance as function of $V_{GS}$ to determine $R_{on}$            | 57  |

| 4.10 | LDMOS LM8: Non-linear capacitance characterization                                             | 58  |

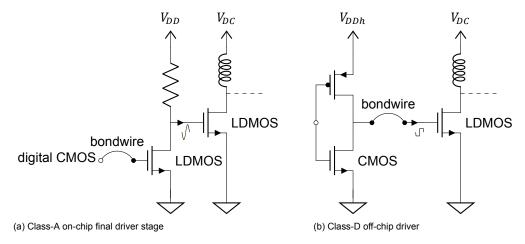

| 4.11 | Options for the DRAC driver                                                                    | 59  |

|      | Class-D off-chip driver model                                                                  | 60  |

| 4.13 | Simplified Class-D off-chip driver model                                                       | 60  |

|      | Inter-chip connection by bondwires                                                             | 62  |

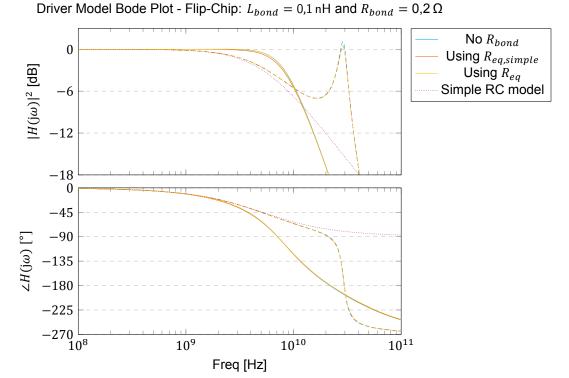

|      | Bode plots for bondwire and flip-chip based driver models                                      | 63  |

|      | Inter-chip connection using flip-chip bonding                                                  | 64  |

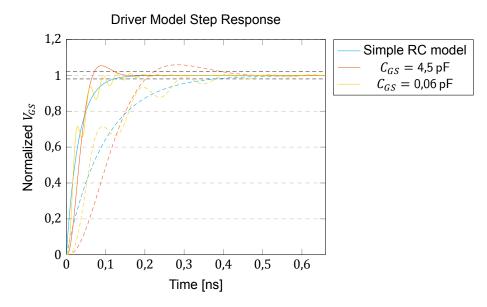

|      | Step responses of the driver model                                                             | 64  |

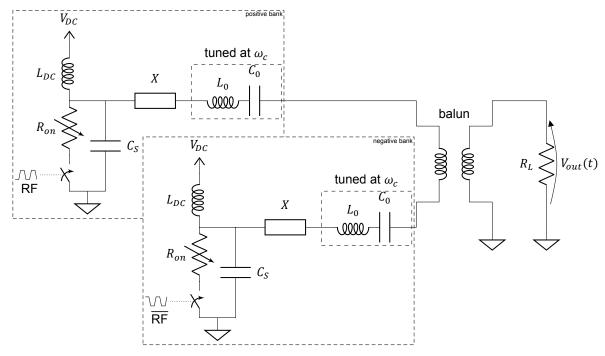

|      | Push-pull Class-E SMPA DRAC                                                                    | 68  |

|      |                                                                                                |     |

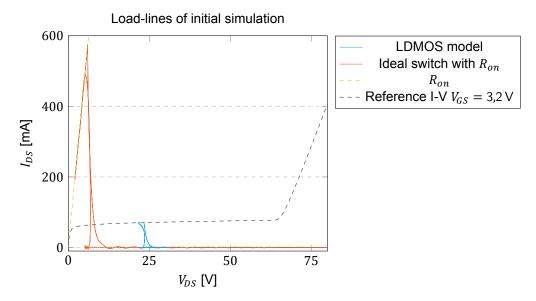

| 5.1  | Initial simulated time domain waveforms                                                        | 72  |

| 5.2  | Initial simulated load-line                                                                    | 73  |

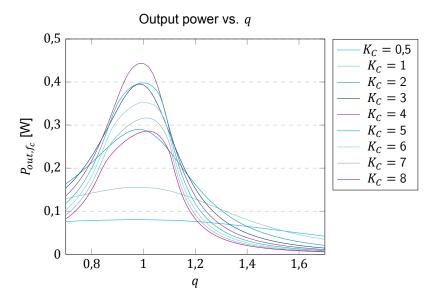

| 5.3  | Output power as function of $q$ and $K_C$                                                      | 74  |

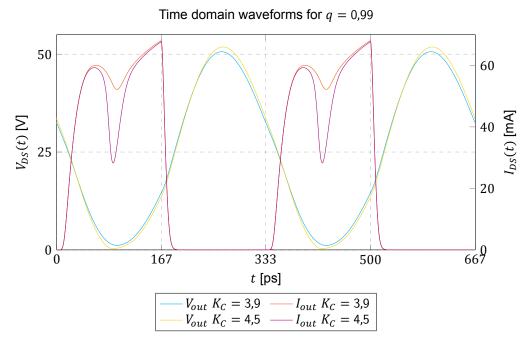

| 5.4  | Time domain waveforms for $q=0.99$ and $K_X=0$                                                 | 74  |

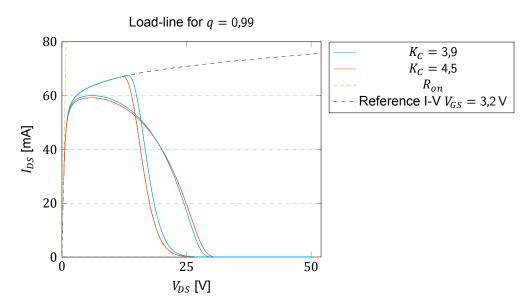

| 5.5  | Load-lines for $q=0.99$ and $K_X=0$                                                            | 75  |

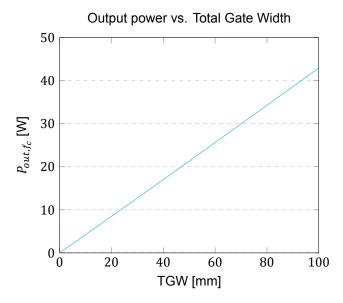

| 5.6  | Output power as function of TGW                                                                | 75  |

| 5.7  | LDMOS output power and efficiency as function of rise and fall time                            | 77  |

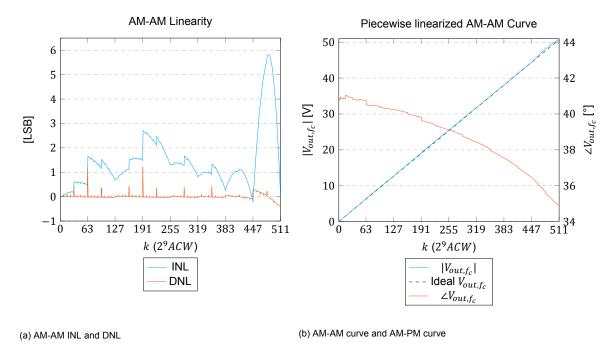

| 5.8  | LDMOS baseline AM-AM curve and INL                                                             | 78  |

| 5.9  | Illustrating the individual transistor sizes                                                   | 80  |

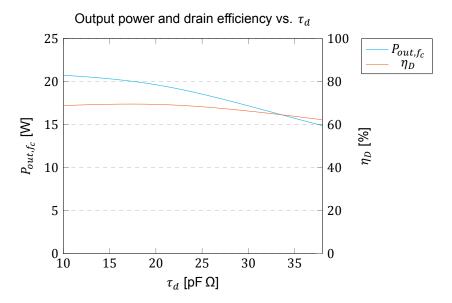

|      | LDMOS output power and efficiency as function of $	au_d$                                       | 81  |

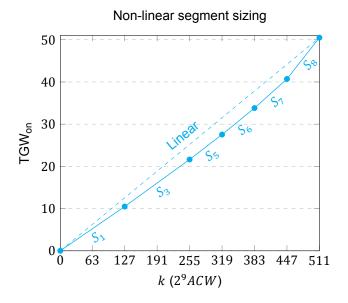

|      | Activated TGW versus ACW illustrating non-linear segment sizing                                | 82  |

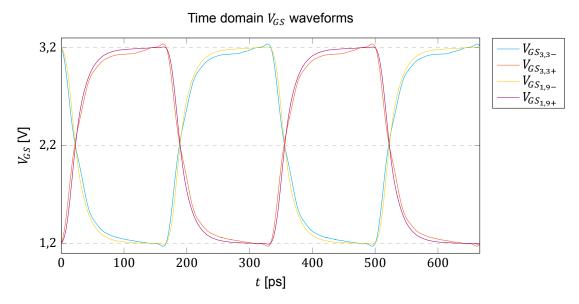

|      | Time domain $V_{GS}$ waveforms for $\tau_d$ =17 pF $\Omega$                                    | 82  |

| 5.13 | AM-AM linearity of implemented DRAC with $N_b = 9  \mathrm{bit}$ , using a simple driver model |     |

|      | without series inductance                                                                      | 83  |

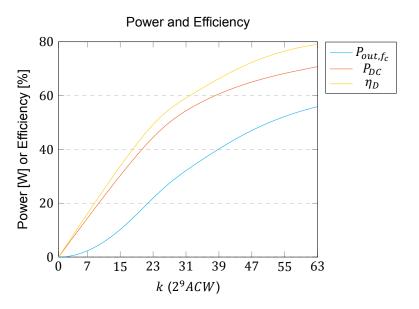

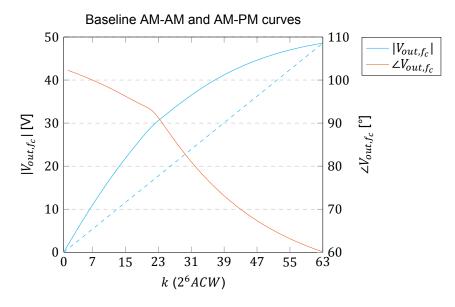

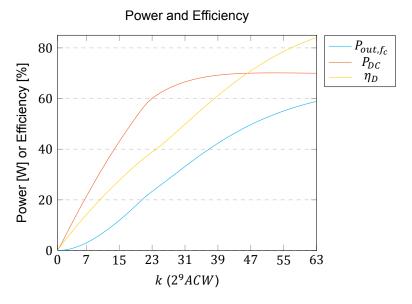

|      | Power and efficiency of implemented DRAC with $N_b=9$ bit at $f_c=3$ GHz                       | 84  |

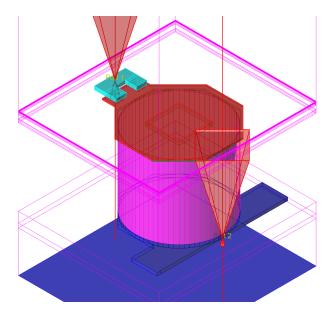

|      | EM model of flip-chip bond                                                                     | 85  |

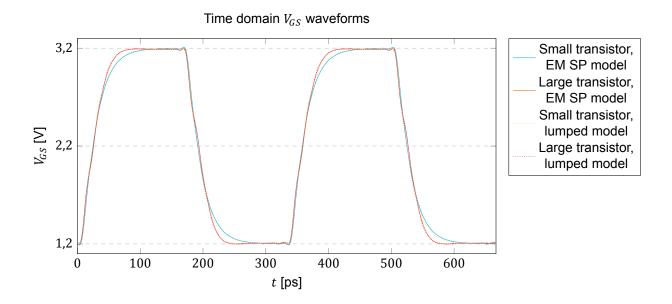

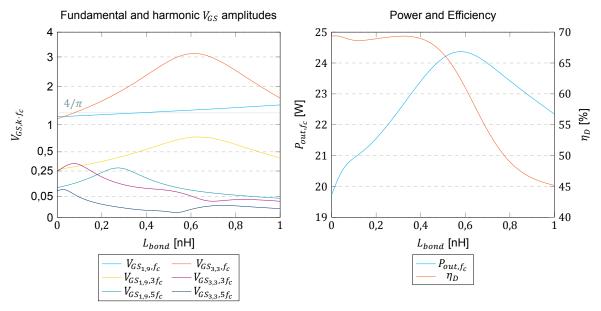

|      | Time domain $V_{GS}$ waveforms using EM bond models                                            | 85  |

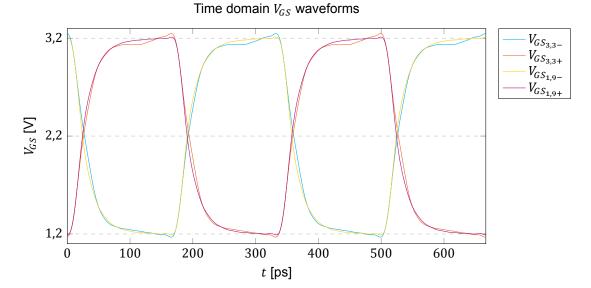

|      | Time domain $V_{GS}$ waveforms for $\tau_d$ =20 pF $\Omega$ and $L_{bond}$ =24,8 pH            | 86  |

|      | AM-AM linearity of implemented DRAC with $N_b=9$ bit, using $L_{bond}=24.8\mathrm{pH}$         | 87  |

|      | Effect of $L_{bond}$ on $V_{GS}$ , power and efficiency                                        | 87  |

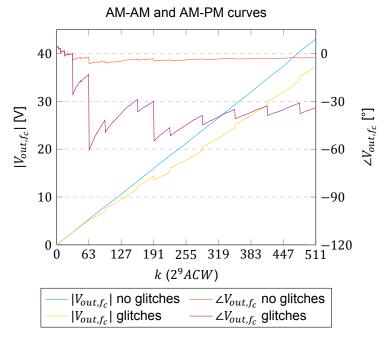

|      | Effect of glitches on AM-AM and AM-PM                                                          | 88  |

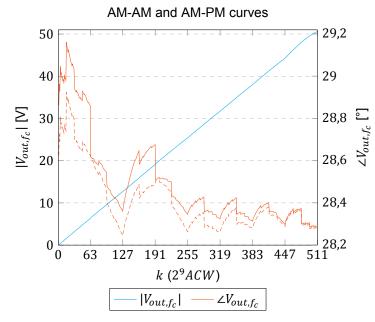

|      | AM-AM and AM-PM curves after applying multiphase RF clocking                                   | 90  |

|      | Flip-chip setup illustrating inshing and distance requirements for wirebonding                 | 91  |

|      | LDMOS layout version 1                                                                         | 92  |

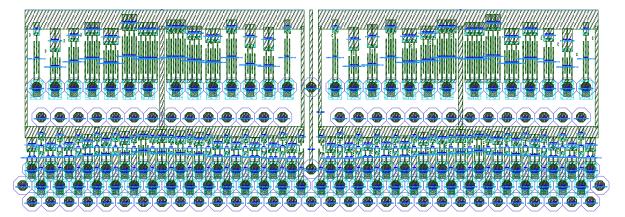

|      | CMOS layout version 1                                                                          | 93  |

|      | S-parameters from farthest input to output from 0 GHz to 48 GHz                                | 94  |

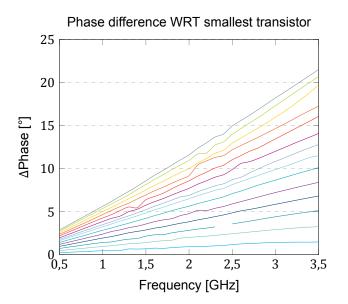

|      | Phase differences due to the layout with respect to the smallest transistor                    | 94  |

|      | LDMOS layout version 2                                                                         | 95  |

|      | CMOS layout version 2                                                                          | 95  |

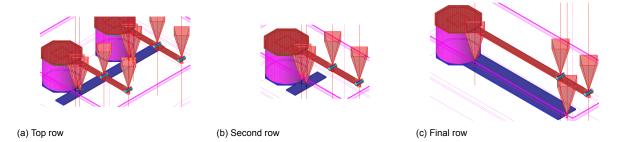

| 5.29 | 3D layouts of flip-chip connections, bump pads and required interconnect to ESD capa-          |     |

|      | citances and CMOS drive transistors                                                            | 96  |

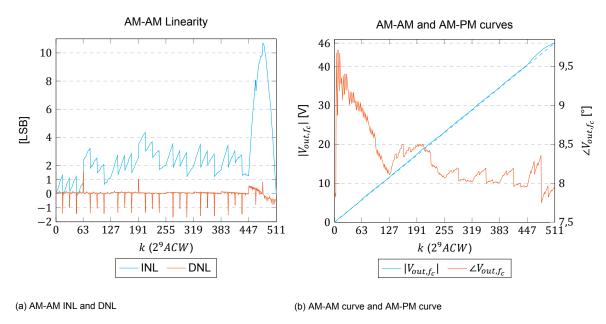

|      | Post-layout AM-AM linearity of implemented DRAC at $f_c = 3  \text{GHz}  \dots \dots \dots$    | 98  |

| 5.31 | Post-layout power and efficiency of implemented DRAC at $f_c=3\mathrm{GHz}$                    | 99  |

| 6.1  | Full RF-DAC                                                                                    | 102 |

| 6.2  | Class-D off-chip driver model with CMOS input and output capacitances                          | 102 |

| 6.3  | Simplified Class-D off-chip driver model with input and output capacitances                    | 103 |

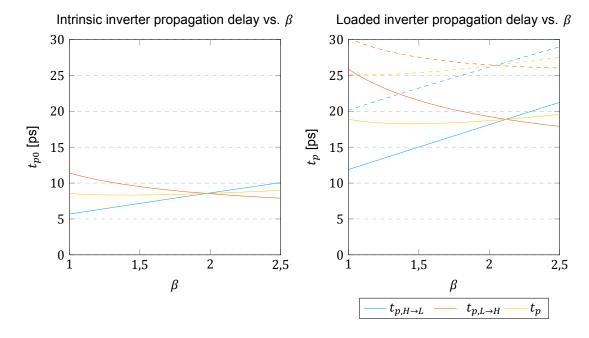

| 6.4  | Thick oxide 270 nm CMOS propagation delays                                                     | 103 |

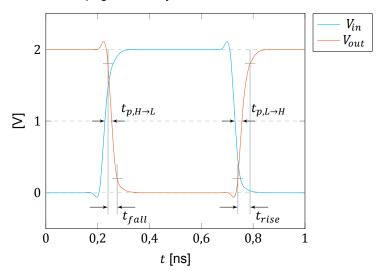

| 6.5  | The relationship between propagation delays and rise and fall times                            | 104 |

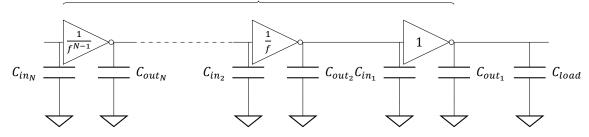

| 6.6  | An inverter chain of length $N$ scaled by a factor $f$                                         | 105 |

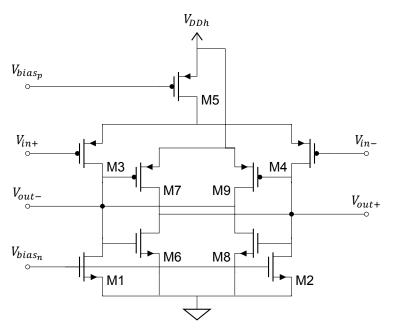

| 6.7  | Designed OTA with enhanced output swing                                                        | 100 |

| 6.8  | OTA DC output characteristics                                                                  |     |

| 6.9  | OTA transient waveforms for $V_{DDh} = 2.0 \text{V}$                                           |     |

| 0.5  | O 1/Λ ((α)(3)()()() wavelottis for ν <sub>DDh</sub> — 2,0 ν                                    | 103 |

List of Figures xiii

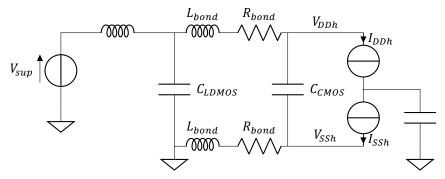

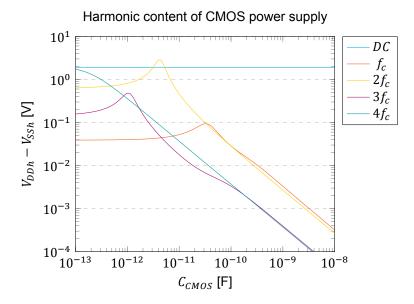

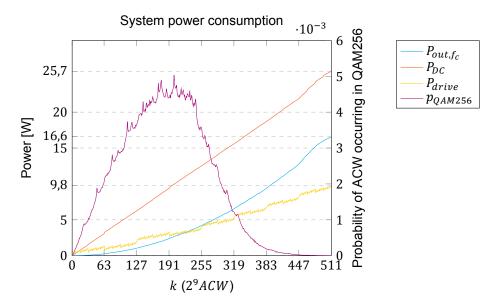

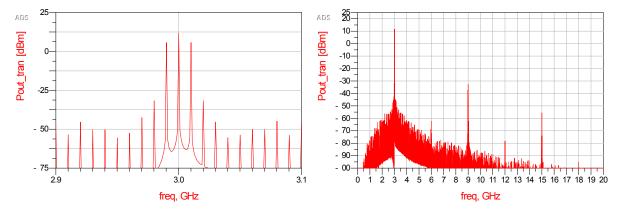

| 6.11<br>6.12<br>6.13 | Complete output chain circuit diagram  Complete output chain transient simulation  Supply decoupling circuit diagram  Harmonic content of CMOS power supply voltage  DRAC output power and DC power, CMOS driver power and QAM256 output probability vs. ACW | 109<br>110<br>111 |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| A.2<br>A.3           | Pre-layout, with sub-optimum AM-AM linearization                                                                                                                                                                                                             | 125<br>126        |

|                      | LDMOS baseline AM-AM and AM-PM curves for $V_{in}=6\mathrm{V}$                                                                                                                                                                                               |                   |

|                      | GaN baseline AM-AM and AM-PM curves                                                                                                                                                                                                                          |                   |

## **List of Tables**

| 2.1                      | Different subclasses of Class-E and their design set [26, 27]                                                          | 31                                                 |

|--------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 4.1<br>4.2<br>4.3        | Comparison between GaN25 and LDMOS LM8                                                                                 | 57<br>65<br>67                                     |

| 5.6<br>5.7<br>5.8<br>5.9 | Design sets and values for $TGW=1\mathrm{mm}$                                                                          | 73<br>76<br>79<br>81<br>82<br>90<br>96<br>97<br>97 |

| 6.1                      | System power consumption contributor and efficiency comparison at 3 GHz                                                | 114                                                |

| 7.1                      | Simulation based power efficiency comparison with measurements from literature                                         | 119                                                |

|                          | Ideal switch Class-E quasi load insensitive quasi parallel-circuit design set OTA transistor widths and bias voltages  |                                                    |

| B.1                      | Design set and values when using $V_{in}=6\mathrm{V}$ , with $TGW=50.0\mathrm{mm}$ (push-pull) and $f_c=3\mathrm{GHz}$ | 131                                                |

| C.1                      | Design set and values with $TGW = 18,9 \mathrm{mm}$ and $f_C = 1 \mathrm{GHz}$                                         | 135                                                |

1

### Introduction

Sharing information is a basic human need. As means of direct sharing we use verbal communication and therefor we developed spoken language. The urge to share indirectly, even to unknown people, was satisfied by written communication. In prehistoric times this was done by cave murals, for anyone to be seen who might stumble upon such cave. A portable way of written communication was scratching pictographs in stone tablets. These pictographs eventually became standardized of which Egyptian hieroglyphs are a good example. Better portability was introduced by writing on papyrus. Written communication continued to evolve, the primal pictographs evolved into an alphabet, papyrus was replaced by paper and from around 1440 we had the possibility to use a printing press instead of having to write everything manually.

It was only in 1894 that Guglielmo Marconi laid the fundamentals for the next step in sharing information: wireless communication<sup>1</sup>. Heinrich Hertz had previously proved the existence of the Electro-Magnetic (EM) waves theorized by James Clerk Maxwell. Marconi showed that information could by transferred by controlling Radio Frequency (RF) EM waves using a spark-gap transmitter. This transmitter was patented by Marconi in 1897 and later exploited commercially by "Marconi's Wireless Telegraph Company". These spark-gap transmitters used a large bandwidth, had low information content and a poor power efficiency [1].

Wireless communication has known incredible development since then. Important inventions that made this possible were the triode vacuum tube by Lee de Forest in 1906, the regenerative receiver in 1913, the super-heterodyne receiver during World War I and Frequency Modulation in 1933 by Edwin H. Armstrong, the invention of the transistor by William B. Shockley, John Bardeen and Walter H. Brattain in 1947, and the invention of the Integrated Circuit (IC) by Jack Kilby in 1958. In the early 1980s the first generation of 'modern' wireless telephone technology was launched, to be replaced in the 1990s by the digital second generation of mobile telecommunications, in Europe known as GSM and still in use today.

Of course developments did not stop there. Today we have access to high speed mobile networks of the fourth generation (4G) and we expect to be wirelessly connected at all times and places for our social interactions. I am no exception to that, as anecdotally illustrated in figure 1.1. This is a screenshot of my smartphone, connected to a 4G+ network<sup>2</sup> with a few recent unread messages of the popular instant messaging service WhatsApp and another application literally requesting me to share more.

<sup>&</sup>lt;sup>1</sup>It is debatable whether Guglielmo Marconi or Nikola Tesla is the father of wireless communication. Marconi's patent was granted in England in 1897, while Tesla filed a patent in the U.S. that same year. In 1900 Marconi also filed for a U.S. patent, but the patent was granted to Tesla. However, this decision was reversed in 1904 by the U.S. Patent Office and Marconi won the Nobel Prize in 1911. In 1943—after the death of both Tesla and Marconi—the U.S. Supreme court again reversed the decision, possibly a politically biased verdict as the "Marconi Company" at that time was suing the U.S. Government for use of its patents during World War I.

<sup>&</sup>lt;sup>2</sup>4G+ is Long Term Evolution (LTE)-Advanced with Carrier Aggregation. In this case an aggregation of a channel of 10 MHz on the 800 MHz carrier and a channel of 20 MHz on the 1800 MHz carrier, allowing for a total download rate of 225 Mbit s<sup>-1</sup>.

2 1. Introduction

Figure 1.1: Smartphone lock-screen with push messages, illustrating today's need for connectivity

### 1.1. Growing Required Wireless Data Capacity

Technological development keeps continuing, allowing for more wireless capacity. Not without reason, data rate demands have been growing exponentially in the past and are expected to continue to do so [2]. As much as 1 GiB/day/user is expected by 2020 [3]. Also the amount of connected users keeps steadily increasing, of which the recent milestone of having 1 billion daily WhatsApp users is a prime example [4]. To cope with the increasing data demands the network operators have to increase their capacity. An example of this is that Vodafone has started providing peak data rates of 1 Gbit s<sup>-1</sup> in some locations of the Netherlands by aggregating 4 carriers [5].

It will not stop there, as this will become normal in the fifth generation (5G) of mobile communication, which is expected by 2020. A peak data rate of 10 Gbit s<sup>-1</sup> is aimed for in the specifications for 5G and a minimum data rate of 100 Mbit s<sup>-1</sup> for all connected users at any given moment [6]. This implies a thousandfold increase in total wireless capacity.

### 1.1.1. Energy consumption

Increasing the wireless capacity by a factor thousand may not also increase the power consumption of the infrastructure by the same factor, this would be unsustainable. With current growth it is expected that by 2030 the entire ICT sector will be responsible for nearly 2% of the global greenhouse gas emissions, with a staggering amount of 1,25 Gigatonnes of carbon dioxide equivalents [7].

Not only the environmental aspect of the power consumption will be an issue, there is also an economical aspect involved. If continued at the current rate the total energy bill will increase to US\$343 billion [2]. The network operators are not too keen on paying for this out of their own pockets, for example, Orange is putting power consumption management at the heart of its corporate strategy to prevent its annual power bill reaching the US\$1 billion mark by 2020 [9]. During the nighttime there is a lot less wireless traffic, which was recognized by Tele2. They have admitted that they are powering down their 2600 MHz base stations during the nighttime, unless they observe increased data demand sustained for more than 2 minutes [8].

That the network operators are not willing to pay for it does not mean the average customer will. Not only in the economical sense, but also in terms of convenience. The base stations are not the only components in the network that will demand more energy with increased data speeds, the receivers will as well. As can also be seen in figure 1.1, right next to the 4G+ icon there is a battery indicator. Any increase in power consumption will lead to a shorter lasting battery. This is especially important for the expected advance of Internet of Things (IoT) devices, as many of these devices are expected to operate in the order of a few years on a single battery charge.

### 1.2. RF Transmitter Architectures

All information in electronic communication systems is in the form of binary data. This binary information is modulated by a transmitter (TX) to a *bandpass* RF signal, ready to be transmitted. This modulated bandpass bandpass RF signal s(t) can be represented by [10]:

$$s(t) = \Re \left\{ g(t)e^{j\omega_c t} \right\} \tag{1.1}$$

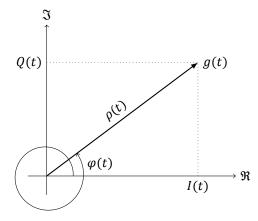

where  $f_c = \omega_c/2\pi$  the carrier frequency and g(t) the complex *baseband* envelope of the modulated signal. We can say that *the complex function* g(t) *modulates the phasor*  $e^{j\omega_c t}$ . Because g(t) is complex, its instantaneous value can be represented in the complex plane as shown in figure 1.2.

Figure 1.2: Representation of g(t) in the complex plane

This instantaneous baseband value can be represented by Cartesian and polar coordinates:

$$g(t) = I(t) + jQ(t) \equiv \rho(t)e^{j\varphi(t)}$$

(1.2)

Using these representations, the modulated signal s(t) can be rewritten as:

$$s(t) = \rho(t)\cos[\omega_c t + \varphi(t)] \tag{1.3}$$

$$= I(t)\cos(\omega_c t) - Q(t)\sin(\omega_c t) \tag{1.4}$$

where  $\rho(t)$  represents the Amplitude Modulation (AM) and  $\varphi(t)$  the Phase Modulation (PM) of the RF signal. Similarly, I(t) represents the in-phase signal and Q(t) the quadrature signal. The polar signals  $\rho(t)$  and  $\varphi(t)$  can be best used to describe what is happening at circuit level in terms of currents and voltages [11], while the Cartesian signals best correspond to the digital baseband information.

As there are two ways of describing the modulated RF signal, there are also two general transmitters: Cartesian or I/Q transmitters and polar transmitters. Traditionally these transmitters are implemented in an analog fashion. These types of transmitters are discussed in section 1.2.1, as well as the two modulation techniques. It is also possible to implement these transmitters digitally, as discussed in section 1.2.2.

### 1.2.1. Analog RF TX Architectures

The polar coordinates are defined and calculated as follows:

$$\rho(t) \triangleq |g(t)| = \sqrt{I^2(t) + Q^2(t)}$$

(1.5)

$$\varphi(t) \triangleq \angle g(t) = \tan^{-1}\left(\frac{Q(t)}{I(t)}\right) + 2n\pi$$

(1.6)

which result in the following reverse computations for the Cartesian coordinates:

$$I(t) = \Re\{g(t)\} \equiv \rho(t)\cos[\varphi(t)] \tag{1.7}$$

$$Q(t) = \Im\{g(t)\} \equiv \rho(t)\sin[\varphi(t)] \tag{1.8}$$

4 1. Introduction

As can be seen in these equations, the conversion between I/Q and  $\rho/\theta$  is highly non-linear. The I/Q notation for the modulated passband signal, equation (1.4), is fairly straightforward. As the signal summation is linear, the analysis of the frequency content of both the baseband and bandpass signal are relatively easy. More importantly, as the baseband conversion from Cartesian to polar is nonlinear it implies that the polar signals require larger bandwidth, called *bandwidth expansion* [12]. The baseband I/Q signals require the same bandwidth  $f_{BB}$  as the RF output signal.

bandwidth expansion

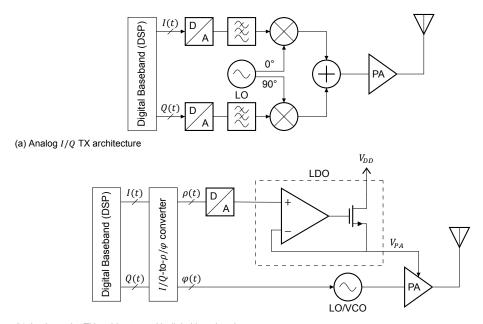

(b) Analog polar TX architecture with digital baseband

Figure 1.3: Examples of analog modulation architectures

### Analog I/Q TX

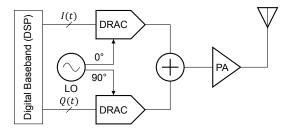

Most likely due to their smaller required baseband bandwidth and the relatively easy frequency domain analysis, the I/Q transmitters have been the de-facto industry standard for transmitters requiring arbitrary amplitude and phase. These transmitters usually have an architecture similar to what is shown in figure 1.3a. First the I(t) and Q(t) signals are generated by a Digital-to-Analog Converter (DAC), then filtered if necessary and up-converted to RF. This up-conversion requires a Local Oscillator (LO) with a 0° and 90° offset. After up-conversion these signals are (linearly) summed and offered to the input of a Power Amplifier (PA), boosting the RF signal power up to the required transmit levels.

### **Analog Polar TX**

This type of transmitter operates by modulating the amplitude and phase separately. Then this information is recombined in, for example, the PA. This architecture is shown in figure 1.3b. Here the LO functions as Phase Modulator (e.g. by a Voltage Controlled Oscillator (VCO)). Amplitude Modulation is achieved by modulating the PA's supply voltage, hence a non-linear PA can be used with excellent power efficiency. With the increasing awareness of energy consumption this is a big advantage. However, special attention must be paid to the timing alignment of the amplitude and phase signal paths to prevent distortion. Furthermore this architecture is unfit for wideband signals due to aforementioned bandwidth expansion.

### 1.2.2. Digital-Intensive RF TX Architectures

Silicon Complementary Metal-Oxide-Semiconductor (CMOS) technology underwent huge improvements and financial cost optimization over time. A general trend observed in 1965 by Gordon Moore was the optimum number of transistors in an IC for the lowest prize per transistor would roughly double every year [13]. Nowadays this observation, best known as Moore's Law, proved somewhat a self-fulfilling prophecy. Transistor gate lengths shrink by a factor  $\sqrt{2}$  every two years, effectively halving

required device area and hence doubling the number of devices on a single IC. This so called *technology scaling* causes lower cost per device, lowering intrinsic delay (increased speed) and lowering supply voltages [14]. The lower supply voltages mainly benefits digital circuitry because of decreased power consumption, however this causes an increased power consumption for analog circuitry whilst keeping other performance similar [15].

technology scaling

digital RF

This gave rise to the concept of *digital RF*: instead of conveying information in the signal amplitude, the information is transferred in the time-domain and in digital codewords. With technology scaling the time-domain resolution keeps improving. Meanwhile the voltage resolution keeps reducing due to lowering supply voltages, up to the point that it can be stated that the time-domain resolution of digital transitions, in combination with the additional information provided by digital codewords, in highly advanced silicon CMOS is superior to the voltage resolution of analog signals in the same process [16].

Using this concept the analog components can be replaced by digital counterparts, allowing the modulators to be implemented in advanced CMOS in an energy efficient manner. An additional advantage of digital electronics is the high reconfigurability compared to analog electronics, allowing for, e.g., adjustable (digital) filters and Digital Pre-Distortion (DPD).

### **Digital Polar TX**

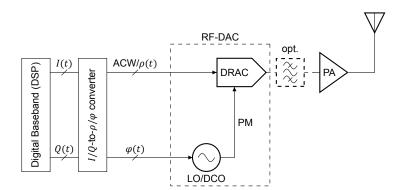

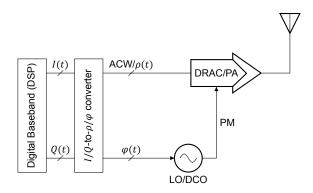

A digital-intensive polar transmitter is quite similar to its analog counterpart. Amplitude and phase are modulated separately and then recombined as shown in figure 1.4. This recombining is not done in a PA, but in a Digital-to-RF-Amplitude Converter (DRAC). This is a Digital-to-Analog Conversion directly at the required RF output frequency, thus effectively a DAC and mixer combined. This DRAC acts like an amplitude modulator by supplying it with a so called Amplitude Code Word (ACW). The phase modulated signal functions as input clock of the DRAC, which is generated by for example a Digitally Controlled Oscillator (DCO). The phase modulator and DRAC together form a Radio Frequency Digital-to-Analog Converter (RF-DAC). Before offering the RF-DAC output to an external PA the signal is optionally filtered—if the spectral purity of the RF-DAC is not sufficient—by for example Surface Acoustic Wave (SAW)-filters [17].

This digital architecture suffers from the same bandwidth expansion as the analog polar architecture, as well as the required timing alignment between the amplitude and phase signal paths. A drawback is that it loses the energy efficiency advantage of analog polar transmitters in the final stage due to external PA. However the power consumption of the digital modulator can improve over time due to technology scaling and can be superior to that of an analog modulator. That improves overall system power efficiency at low required output powers, which can be beneficial in for example IoT-applications.

Figure 1.4: Digital polar TX architecture

### Digital I/Q TX

It is also possible to make a digital intensive I/Q transmitter, which again is quite similar to its analog counterpart. Its general architecture is shown in figure 1.5. The I(t) and Q(t) signals are generated by two DRACs directly at the RF frequency. Just as with the digital polar transmitter the DRAC functions both as DAC and as mixer. It requires a LO with a  $0^{\circ}$  and  $90^{\circ}$  offset. The DRAC outputs are summed and then fed to an external PA. It does not suffer from the bandwidth expansion the digital polar architecture

6 1. Introduction

suffers from, generally resulting in better linearity than the digital polar architecture. However, generally the power consumption is higher than that of a polar architecture.

Figure 1.5: Digital I/O TX architecture

### 1.3. Thesis Goals

As mentioned in section 1.2.2 in the digital polar transmitter, the transmitter loses efficiency due to the external PA which was not the case in the analog polar transmitter. But what if we would be able to combine the PA and RF-DAC? Would this improve overall power efficiency? This results in the following research question:

"Is it possible to design a power RF-DAC, in such a way that this RF-DAC also functions as the PA, with good power efficiency?"

Figure 1.6: Combined RF-DAC and PA TX architecture

The goal of this thesis is to answer above question by designing a power DRAC as core component of the intended power RF-DAC. Its basic architecture is shown in figure 1.6. As the intention is to be able to connect the power RF-DAC directly to an antenna without additional filtering, its output signal should have good spectral purity, thus putting constraints on the linearity of the RF-DAC. The choice for a digital polar architecture is made as it will have better power efficiency, as is the case for the analog polar modulator.

Several technologies are available to make the components of the power RF-DAC. Two high power analog technologies are available, being Fraunhofer IAF Gallium Nitride (GaN) 250 nm and Ampleon Laterally Diffused Metal-Oxide-Semiconductor (LDMOS) LM8. These are most likely suitable for the power DRAC design. Also available is a high integration digital technology, TSMC CMOS 40 nm 1P7M4X1Z1U, which could be used to do the Digital Signal Processing (DSP) and include the phase modulator. Designs for these on CMOS are already available within the Electronics Research Laboratory (ELCA) research group and are therefore outside this thesis scope.

Taking in above considerations the following objectives are set for this thesis:

The RF-DAC targets (5G) mobile cellular application, hence the operational frequency of the power RF-DAC should be in the Ultra High Frequency (UHF) range: 617 MHz to 2690 MHz and/or 3300 MHz to 5000 MHz [18]

- The RF-DAC's operational frequency should be agile and only dependent of external components, such as the applied matching network at the output

- Select semiconductor technologies to implement the power RF-DAC in

- Depending on the selected technology the targeted peak output power of the DRAC has to be determined

If Fraunhofer IAF GaN 250 nm is selected the targeted peak output power is 50 W to 100 W If Ampleon LDMOS LM8 is selected the targeted peak output power is 10 W to 20 W

- Select a suitable circuit topology to implement the high power RF-DAC

- Design a power DRAC

The designed DRAC should have high drain efficiency

The designed RF-DAC should have—within the constraints of the available circuitry—a reasonable system power efficiency, preferably as high as possible

The designed RF-DAC's linearity should allow for ACPR levels better than 50 dBc

### 1.4. Thesis Organization

The thesis is structured as follows:

In part I the definitions and theoretical groundwork is laid out. This starts with discussing Power Amplifier theory, the used model assumptions and the operating principles of the different PA classes in chapter 2. In chapter 3 the operation of a DRAC is discussed, starting with the basics from a DAC. In its last section the theory of PAs and DRACs is combined to make the first step towards a power DRAC. Readers that have experience with these topics may skip these chapters, although it will help the understanding of the rest of the thesis as all relevant definitions are made within these chapters.

In part II the implementation of the RF-DAC design is discussed. Part II starts with chapter 4 where the different design choices during the design process are established, including choice of semiconductor technologies, models for the DRAC driver and resulting circuit topology. Due to the limitations of the technologies the choice will be made to implement the DRAC in LDMOS and a dedicated driver in CMOS. With the choices made the actual design steps and simulation results are discussed in chapter 5. At the end of this chapter a suitable layout for the DRAC is proposed.

In chapter 6 the first groundwork for a CMOS driver design is laid out, making it reasonable that a design compatible with the LDMOS DRAC is possible, but the full CMOS driver design lies outside this thesis scope. With the simulation results from the CMOS driver it is possible to make estimates regarding the system performance and these are discussed in section 6.5. The technology that is used to implement the presented power RF-DAC is not optimized for this purpose, therefore the resulting system performances can be improved by technology development. Estimates on how the technology could be used in a different way and resulting system performances are discussed as well.

Lastly, in chapter 7 the thesis conclusions are presented, together with a discussion on the results and recommendations for future work.

# Theory

### **PA Basics**

In this chapter the operation principles of PAs are discussed. First in section 2.1 the core performance metrics regarding PAs are defined. Then in section 2.2 the power flows at different frequencies are defined and relationships between them described. Finally section 2.3 starts by defining the model used for the active device used in a PA, after which the different classes of PA operation are described using the active device model.

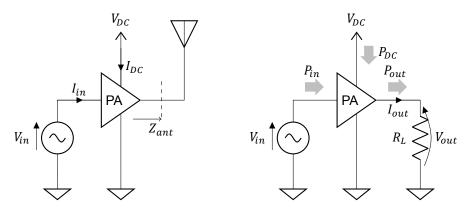

### 2.1. Definitions

By its very nature, an amplifier is a three-port device that converts Direct Current (DC) power to an output with a reasonably similar power spectrum of its input signal [19, 20]. In the case of a RF PA, the output is typically connected to an antenna. The antenna can be characterized by a loading impedance  $Z_{ant}$ , which is designed to be resistive at the (bandpass) design frequencies. Hence, at these frequencies, the antenna can be represented by a single load resistor  $R_L$ . The power dissipated by  $R_L$  is, by definition, equal to the power of the EM wave radiated by the antenna [21]. This load resistance is usually 50  $\Omega$ , but it can be converted to a higher or lower value to be seen by the active device of the PA. Note that the bandpass signal is assumed to be *narrowband*, meaning that the signals present in the circuit can be assumed to effectively consist of only sinusoids of the fundamental frequency and its harmonics [20]. In this thesis, the formal PA output quantity is assumed to be the voltage  $V_{out}$ , although assuming it to be a current delivered to an ohmic load would be just as correct.

narrowband

In the next sections the core performance metrics for a PA will be defined, which are power, gain, efficiency, linearity and the Peak-to-Average Power Ratio.

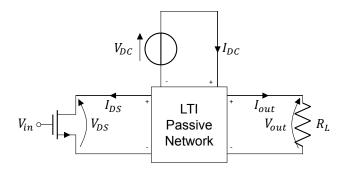

Figure 2.1: Power flows in a general PA

### 2.1.1. **PA Power**

There are three important power flows within a PA, these being the input power  $P_{in}$ , the output power  $P_{out}$  and the supply power  $P_{DC}$ . These power flows are illustrated in figure 2.1.

12 2. PA Basics

instantaneous output power

The output power is defined as the power delivered by the PA and flowing into the load (antenna) and varies over time. The instantaneous output power is defined as

$$p_{out}(t) \triangleq V_{out}(t) \cdot I_{out}(t) \tag{2.1}$$

output power

time average The time average output power is defined as

$$P_{out} \triangleq \langle p_{out}(t) \rangle \equiv \lim_{\tau \to \infty} \int_{-\tau/2}^{\tau/2} p_{out}(t) dt$$

(2.2)

where  $\langle \cdot \rangle$  is the time average operator. In case of a periodic output with period T the equation simplifies

$$P_{out} = \frac{1}{T} \int_{-\tau/2}^{\tau/2} p_{out}(t) dt$$

(2.3)

Assuming a resistive load this gives

$$P_{out} = \frac{\langle V_{out}^2(t) \rangle}{R_L} = \frac{V_{out,RMS}^2}{R_L}$$

(2.4)

RMS where the Root Mean Square (RMS) voltage is defined as

$$V_{out,RMS} \triangleq \sqrt{\langle V_{out}^2(t) \rangle}$$

(2.5)

input power supply power In a similar way, equations can be defined for input power and supply power

$$P_{in} \triangleq \langle p_{in}(t) \rangle = \langle V_{in}(t) \cdot I_{in}(t) \rangle \tag{2.6}$$

$$P_{DC} \triangleq \langle p_{DC}(t) \rangle = \langle V_{DC}(t) \cdot I_{DC}(t) \rangle \tag{2.7}$$

Since a PA converts power between different frequencies it might happen that power gets spread across the frequency spectrum. Typically only the power of the modulated bandpass around the carrier frequency  $f_c$  is useful and any additional harmonics should be filtered away. Therefore it is useful to define the fundamental average output power

fundamental average output power

$$P_{out,f_c} = \frac{V_{out,f_c}^2}{2R_L} = \frac{V_{out,f_c,RMS}^2}{R_L}$$

(2.8)

where  $V_{out,f_c}$  is the amplitude of the sinusoidal output voltage at  $f_c$ .

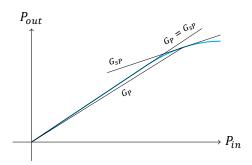

### 2.1.2. Gain

The gain of a PA can be defined as the dimensionless ratio between the useful output power, the fundamental average output power  $P_{out,f_c}$ , and the required input power  $P_{in}$  to drive the PA. This ratio is usually expressed in dB and is defined as

$$G_{P,dB} \triangleq 10 \log_{10} \left( \frac{P_{out,f_c}}{P_{ln}} \right)$$

(2.9)

slope power gain

where  $G_P$  is the gain, more specifically the *ratiometric power gain*.

Another metric of power gain is the slope power gain  $G_{SP}$  which is defined as

$$G_{SP,dB} \triangleq 10 \log_{10} \left( \frac{dP_{out,f_c}}{dP_{in}} \right)$$

(2.10)

Both gain definitions are large signal quantities. As long as the amplifier operates linearly these two power gain measures are equal to each other and the small signal gain [19]. Both gains are illustrated in figure 2.2

2.1. Definitions

Figure 2.2: Different power gain measures

### 2.1.3. Efficiency

Conservation of power dictates that the amount of power that comes out of a system should always be less or equal to the amount of power that was put in, with the difference being dissipated in the form of heat or by undesired parasitic radiation of EM waves. An ideal amplifier would require negligible input power and would convert all DC supply power to useful output power, basically generating no heat. However, as practical PAs are not ideal, it is useful to define some measures of power efficiency.

First it is useful to see how well a PA output stage converts the DC supply power into useful output power. This is simply the ratio between the useful generated output power and the consumed DC supply power by the active device, called the *drain* or *collector efficiency*

drain efficiency

$$\eta_D \triangleq \frac{P_{out,f_c}}{P_{DC}} \tag{2.11}$$

Perhaps a more honest way of expressing PA efficiency is by taking the ratio of the useful output power and all power put into the PA together, called the *total efficiency*

total efficiency

$$\eta_T \triangleq \frac{P_{out,f_c}}{P_{DC} + P_{in}} \tag{2.12}$$

This can include also any amount of driver stages required to drive a PA and defines the *total chain* or system efficiency

total system efficiency

$$\eta_{T,system} \triangleq \frac{P_{out,f_c}}{P_{DC} + \sum_{i=0}^{n} P_{DC,i} + P_{in}}$$

(2.13)

in which case  $P_{in}$  is the input power of the first driver stage and  $P_{DC,i}$  the DC power consumption of the  $i^{th}$  stage in the chain.

Lastly, a commonly used power efficiency figure of merit in the RF and microwave field is the *Power Added Efficiency (PAE)*

PAE

$$PAE \triangleq \frac{P_{out,f_c} - P_{in}}{P_{DC}} \tag{2.14}$$

This equation suggests that part of the output power is physically coming from the input power, which is not true for most, if not all, modern PAs.

It is common to display an efficiency measure as percentage.

### 2.1.4. Linearity

As the whole point of a PA in a TX system is to boost the power of a modulated bandpass signal to power levels required to transmit, it would be nice if the PA output signal is an exact linearly scaled replica of the input signal. The extent to which that is true is referred to as *linearity*. The accuracy in which the signal is reproduced can be split in to two types: amplitude linearity and phase linearity. Any non-linearity is referred to as distortion.

nearity

non-linearity distortion

In systems where only Phase Modulation (PM) is applied (constant envelope systems) the only linearity one needs to take care of is the Input Phase to Output Phase conversion (PM-PM) distortion. Similarly for Amplitude Modulation (AM) systems (constant phase systems) this is Input Amplitude to

14 2. PA Basics

Output Amplitude conversion (AM-AM) distortion. When both AM and PM are applied in one system also Input Amplitude to Output Phase conversion (AM-PM) distortion comes into play.

Modern communication systems require both amplitude and phase modulation. The two foremost distortion mechanisms in a polar modulator are AM-AM distortion and AM-PM distortion [21]. These distortion profiles are static approximations and are usually shown by plotting the AM-AM, AM-PM etc. profiles. The static approximation is attained by (periodic) steady-state values. Ideally the AM-AM curve should be a straight line through the origin (constant derivative, or constant power gain) and the AM-PM curve should be flat (zero derivative).

Both AM-AM and AM-PM curves can change in a dynamic setting due to environmental effects, such as temperature or supply voltage changes due to fluctuating bias current. An example could be that the PA had high output power causing a voltage (IR) drop and increased temperature, followed by a lower output power. Then it takes some time for the voltage to return to 'normal' and the amplifier to cool to nominal value, hence affecting the accuracy of the lower power signal. These effects are referred to as *memory effects*, since what happened in the past affects the signal in the future.

Multiple measures for quantifying linearity are used. Looking at a typical AM-AM curve initially the relation between input and output power is linear, indicating constant gains  $G_P = G_{SP}$ . When the PA starts to saturate non-linearity occurs, which causes the gains to diverge. The output power where  $G_P$ compression point is 1 dB lower than its value in the linear region is called the 1 dB compression point  $P_{-1 \, dB}$ .

Perhaps more important are the non-linearities that become apparent in the frequency spectrum. The power outputted at integer multiples of the carrier frequency compared to the power at the carrier harmonic distortion itself is referred to as harmonic distortion and is often expressed in dB

$$HD_{k,dB} \triangleq 10 \log_{10} \left( \frac{P_{out,k \cdot f_c}}{P_{out,f_c}} \right) = 10 \log_{10} \left( \frac{V_{out,k \cdot f_c}^2}{V_{out,f_c}^2} \right)$$

(2.15)

where  $V_{out,k\cdot f_c}$  is the amplitude of the sinusoidal output voltage at  $k\cdot f_c$ . Most significant are usually HD2, HD3 Second order Harmonic Distortion (HD2) and Third order Harmonic Distortion (HD3). The total po-THD wer in the harmonics summed is referred to as Total Harmonic Distortion (THD) and is expressed as percentage

$$THD \triangleq \frac{\sum_{i=2}^{\infty} P_{out,i \cdot f_c}}{P_{out,f_c}} = \frac{\sqrt{\sum_{i=2}^{\infty} V_{out,i \cdot f_c}^2}}{V_{out,f_c}}$$

(2.16)

These harmonics are usually unwanted and filtered to suppress them at the output, for that reason HD2 and HD3 might give slightly optimistic values for how linear the PA actually is. Another way is by specifying the Third order Intercept Point (IP3) in a two-tone test. This is done by applying two frequencies at the input with equal amplitude, with tone spacing  $f_{ts}$  centered around the carrier frequency, and observing the Third order InterModulation distortion (IM3) at the output. With every 1 dB increase in signal amplitude the IM3 products increase by 3 dB. The virtual point where the output IM3 product power would be equal to the output power of the desired frequencies is defined as the IP3. It can be specified as the output power or as the input power to reach this point, being respectively referred to as OIP3 and IIP3. These measures should be more ore less independent from the tone spacing  $f_{ts}$ and the carrier frequency f<sub>c</sub>. A signature of memory effects is that the IM3 products actually do change with  $f_{ts}$  and  $f_c$  [22].

Complex modulated signals, however, are far from similar to a two-tone test. Hence in PA specifications for communication purposes other measures—related to the specifications of the targeted standard—are used. These measures are Adjacent Channel Power Ratio (ACPR) and Error Vector Magnitude (EVM). ACPR, rather self explanatory, is the ratio of power outputted in an adjacent channel one signal bandwidth away and the power outputted in the main channel where both channel bandwidths are equal and is expressed in dBc. EVM is the accuracy in which symbols are transmitted within the main channel itself. As explained in section 1.2 and illustrated in figure 1.2 a symbol can be represented in the complex plane. All possible symbols together make up the constellation diagram where a single symbol is referred to as a constellation point. The error vector is defined as the difference between the actual transmitted constellation point  $\hat{g}[k]$  and the ideal constellation point g[k] of the  $k^{th}$  symbol

> $\varepsilon[k] = \hat{g}[k] - g[k]$ (2.17)

memory effect

intercept point

intermodulation

constellation diagram constellation point Note that the value of g represents a complex voltage. The EVM can be defined as

$$EVM[k] = \sqrt{\frac{|\varepsilon[k]|^2}{N^{-1} \sum_{i=1}^{N} |g[i]|^2}}$$

(2.18)

The RMS value of the EVM is defined as

$$EVM_{RMS} = \sqrt{\frac{\sum_{i=1}^{N} |\varepsilon[i]|^2}{\sum_{i=1}^{N} |g[i]|^2}}$$

(2.19)

Usually a RMS EVM and a peak EVM,  $EVM_{pk} = \max_{k} (EVM[k])$ , are specified.

### 2.1.5. Peak-to-Average Power Ratio

The *Peak-to-Average Power Ratio (PAPR)* is not a fundamental property of a PA, but more of a result of the used modulation scheme. In an amplitude modulated system the output power is—per definition—not constant. The PAPR gives a measure of how much AM is present and is defined as the ratio of the PAPR peak RF output power to the average RF output power

$$PAPR = \frac{P_{out,pk}}{P_{out,avg}} \tag{2.20}$$

The PAPR is often expressed in dB

$$PAPR_{dB} = 10 \log_{10} \left( \frac{P_{out,pk}}{P_{out,avg}} \right)$$

(2.21)

Note that the peak output power is not the same as the peak instantaneous output power. Peak output power is also referred to as peak envelope power. In other words, when the output signal is a single tone then  $PAPR_{dB} = 0$  dB.

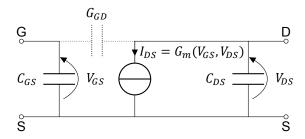

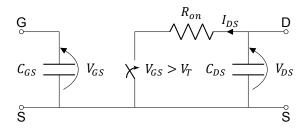

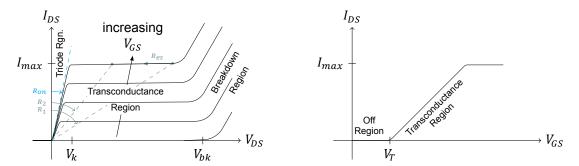

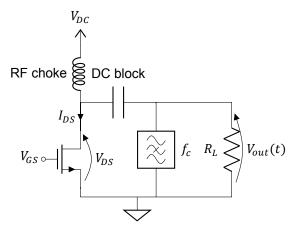

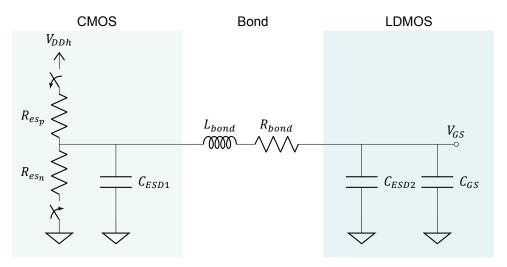

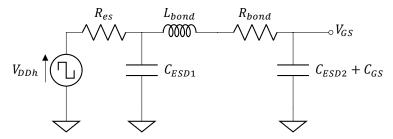

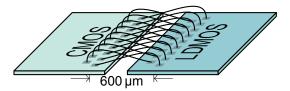

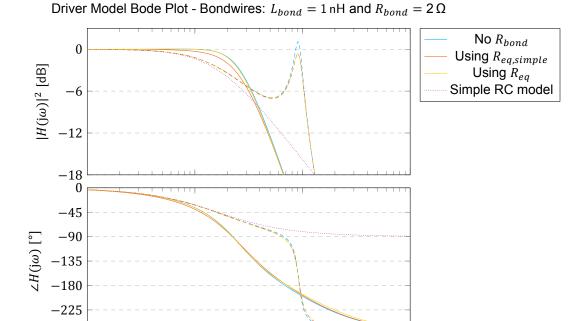

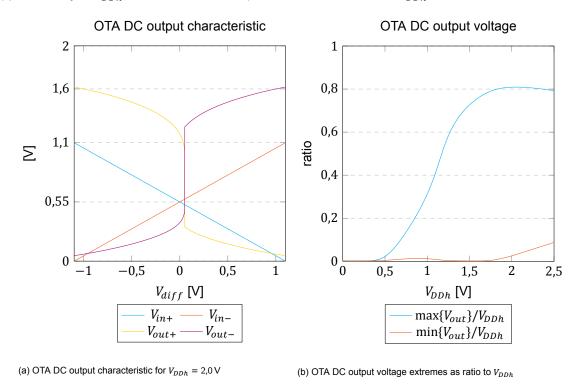

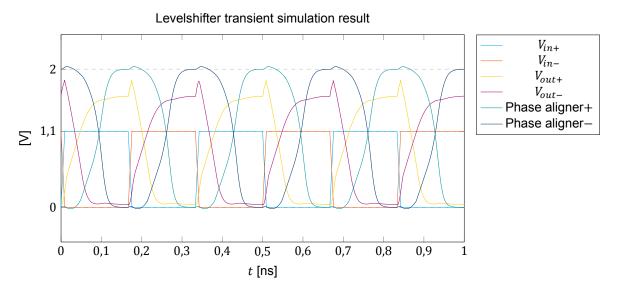

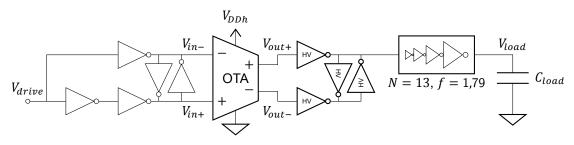

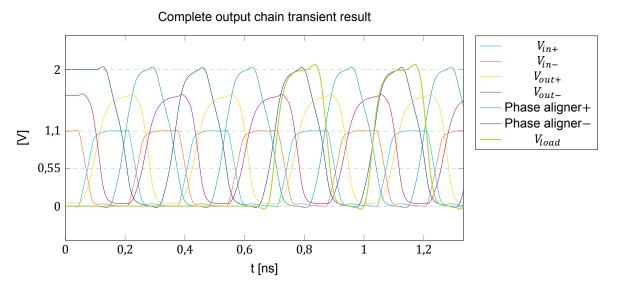

In a multi carrier system the peak power occurs when all carrier voltage waves add up constructively, therefore the PAPR increases with the number of carriers squared, if no special measures are taken to prevent this.