# Isolated DC/DC Converters for DC Distribution Grids in Rural Electrification

Jesse Echeverry

# Isolated DC/DC Converters for DC Distribution Grids in Rural Electrification

to obtain the degree of Master of Science in Electrical Power Engineering (EPE) at the Delft University of Technology.

| Student number:<br>Project duration: | 4776372<br>Jan 11, 2020 – October 28, 2020                                  |                                                        |  |  |

|--------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------|--|--|

| Supervisors:                         | Dr. Ir. Laurens Mackay,<br>Ir. Sachin Yadav,                                | DC-Opportunities R&D<br>TU Delft, DC-Opportunities R&D |  |  |

| Thesis committee:                    | Prof. Dr. Ir. Pavol Bauer,<br>Dr. Ir. Zian Qin,<br>Dr. Ir. Milos Cvetkovic, | TU Delft<br>TU Delft<br>TU Delft                       |  |  |

This thesis is confidential and cannot be made public until May 1, 2021.

An electronic version of this thesis is available at http://repository.tudelft.nl/.

# Acknowledgment

Writing a master's thesis can be described as a difficult task that demands time, dedication, and skill. If one sets ambitious research goals and rises up to meet the challenges, it can be a catalyst for personal growth. I have found, in my experience, that this has been the case. Over the past nine months, I have experienced many things; I have worked on my thesis, observed the effects of the coronavirus pandemic on society, worked with talented individuals, and developed new inspirations for my future work. These recent experiences have convinced me that unification, understanding, and working together to help the Earth and our immediate environments should be my focus moving forward. My personal development and completion of the thesis were only possible because of the unwavering support of my advisors, family, and friends. And to them, I dedicate this work.

This work is dedicated to the following people:

- 1. My brother, Kennedy Echeverry, who has supported me as a friend throughout my life and as a clutch last-minute proofreader, among other things.

- 2. My parents, Samuel and Paula, for making me who I am today and offering endless support in all aspects of my life.

- 3. Dr. Laurens Mackay, for the guidance in my thesis and setting an example of leadership, hard work, and dedication.

- 4. Dr. Zian Qin and Sachin Yadav for the guidance and advisory throughout my thesis.

- 5. Lukas Irazusta as my advisor for rural electrification, and all of the DC bros for the help and friendship over the past year.

- 6. All of the family and friends who have supported me in the past 2 years, in Delft, in Aikido, in the US, and in Colombia.

Jesse Edward Echeverry Delft, Netherlands October 2020

## Abstract

Roughly 840 million people, predominately from rural communities in sub-Sahara Africa, still lack access to electricity. The direct current (DC) microgrid is an emerging grid infrastructure that meshes efficiently with DC based technology such as photovoltaics, batteries, consumer electronics, and electric vehicles. This characteristic of DC microgrids designates them as a preferred solution for new grid infrastructures in rural electrification applications. In order to establish a DC microgrid, power electronic interfaces (PEI) are required for regulating power flow and interconnecting different grid components of the microgrid. In this thesis, the PEI (operating at 200-900 W) connecting a 350 V DC-microgrid to a solar home system (compatible with USB-C) is investigated. A unidirectional half-bridge LLC converter and a bidirectional dual active half-bridge (DAHB) converter (both utilizing gallium-nitride (GaN) transistors and planar transformers (PT)) are designed and tested. A working prototype of the halfbridge LLC converter with a center-tapped secondary is presented and the waveforms at maximum load and no-load conditions are analyzed. A complete design and efficiency approximation for a DAHB converter with a center-tapped secondary and active snubber circuits is included. In addition, simulations (in PLECS) of the designed DAHB converter provide waveform results for both the forward and reverse power flow direction. The results of the work discuss how high frequency operated, half-bridge isolated DC/DC topologies with GaN transistors and planar transformers are an excellent composition of technology for these rural electrification applications. The GaN transistor is most effective in a low voltage (up to 650 V), high performance scheme, and offers inherent benefits which allow for high frequency operation and thus, smaller passive components. Moreover, the effect of current collapse (an adverse effect in GaN transistors) is discussed and analyzed from a design standpoint. The benefits of planar transformers in low-medium power (up to 900 W) rural electrification applications and an indepth PT design process are presented. Additionally, rural electrification safe extra-low voltage (SELV) standards require that PT designs must have reinforced (or double) isolation between primary and secondary windings. Taking this into consideration, two proposed PT configurations using a U-core and planar E-core, respectively, are compared. The main conclusions of this work aim to bridge the gap for the design and implementation of efficient DC microgrid variable power output converters for use in rural electrification applications.

**Keywords:** Rural Electrification, DC Microgrid, Half-bridge LLC, Dual Active Half-bridge (DAHB), GaN Switching, Current Collapse, Planar Transformers, Safe Extra-low Voltage (SELV)

# Contents

| Ac  | knov                                     | vledgment                                                                                                                                                                                                                                                                                                                                                                                              |   |

|-----|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| At  | ostra                                    | ct v                                                                                                                                                                                                                                                                                                                                                                                                   | , |

| Та  | ble o                                    | f Contents viii                                                                                                                                                                                                                                                                                                                                                                                        |   |

| No  | omen                                     | clature xi                                                                                                                                                                                                                                                                                                                                                                                             |   |

| Lis | st of                                    | Figures xiii                                                                                                                                                                                                                                                                                                                                                                                           |   |

| 1   | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Doduction       1         Problem Definition: Rural Electrification, Solar Home Systems, and the DC Microgrid.       1         Problem Definition: Power Electronics       3         Motivation.       3         Research Questions       4         Outline       5                                                                                                                                    |   |

| 2   | Lite<br>2.1<br>2.2<br>2.3                | rature Review and Background Information7Topology Comparison72.1.1Buck, Boost, and Buck-Boost Converters72.1.2Flyback Converter82.1.3Forward Converter92.1.4Push-pull Converter102.1.5Isolated Resonant Converters112.1.6LLC Converter112.1.7DAB Converter15Topology Selection18Gallium Nitride (GaN) Switching192.3.1Reverse Conduction in E-mode GaN HEMT202.3.2Layout Considerations for GaN HEMT20 |   |

| 3   | <b>Pla</b> r<br>3.1<br>3.2               | 2.3.3Current Collapse212.3.4GaN vs. Silicon Carbide (SiC) Vs. Silicon MOSFET21har Transformers25Isolated Transformer Characteristics253.1.1Integrated Magnetic Structures253.1.2Isolation263.1.3Planar Transformer Overview27Electromagnetic Theory28                                                                                                                                                  |   |

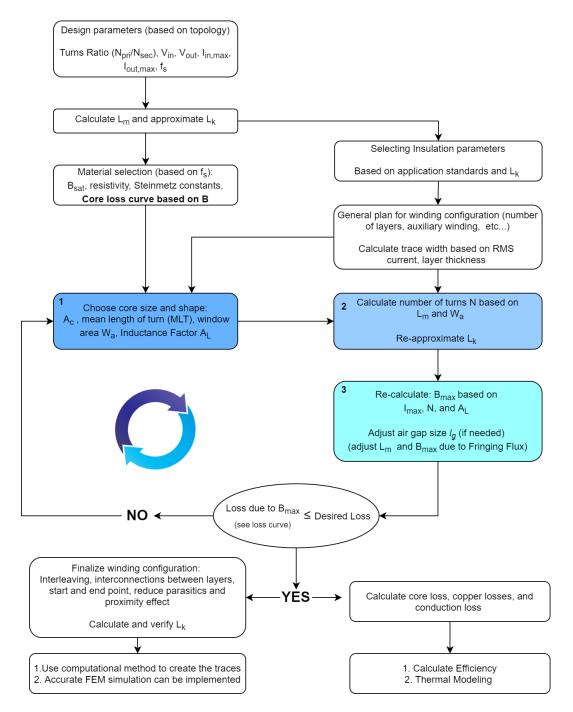

|     |                                          | 3.2.1       Leakage Inductance       30         3.2.2       Winding Capacitance.       32         3.2.3       Fringing Flux       32         Losses       32         3.3.1       Copper and Conduction Losses       32         3.3.2       Core Losses       34         Planar Transformer Design and Construction       35         3.4.1       Design Process       35                                |   |

|    | 3.5       Coding Traces and Layout in Python         3.6       Conclusions and Findings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                      |  |  |  |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| 4  | Unidirectional LLC Prototype Modeling, Design, and Construction4.1Preliminary Design4.2Transformer Design4.3Simulation4.4Losses and Efficiency4.5Thermal Considerations4.6Gate Driver and Layout Considerations4.7Additional Modules and Controls                                                                                                                                                                                                                                                                                                                                                | . 44<br>. 46<br>. 46<br>. 48<br>. 48                                                 |  |  |  |  |

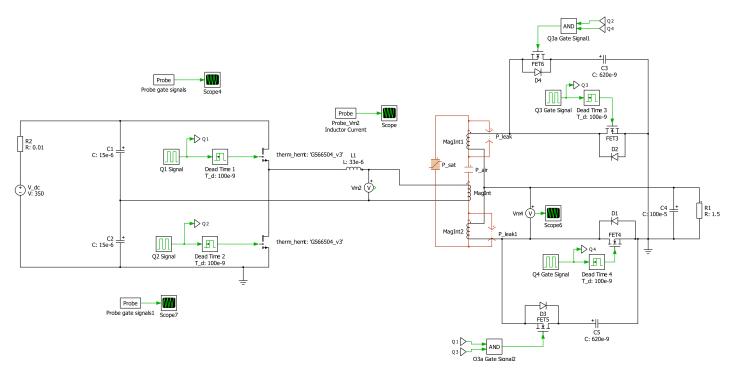

| 5  | Bidirectional DAHB Prototype Modeling and Design         5.1       Preliminary Design         5.2       Transformer Design         5.3       Simulation         5.4       Losses and Efficiency         5.5       Thermal Considerations         5.6       Additional Modules and Controls         5.7       Schematic                                                                                                                                                                                                                                                                           | . 54<br>. 55<br>. 56<br>. 57<br>. 58                                                 |  |  |  |  |

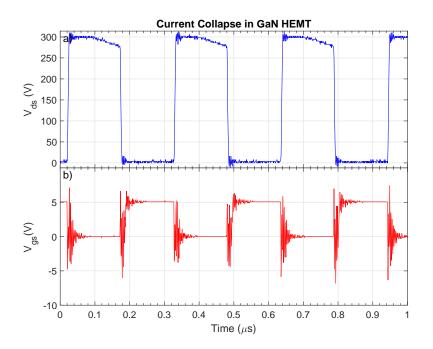

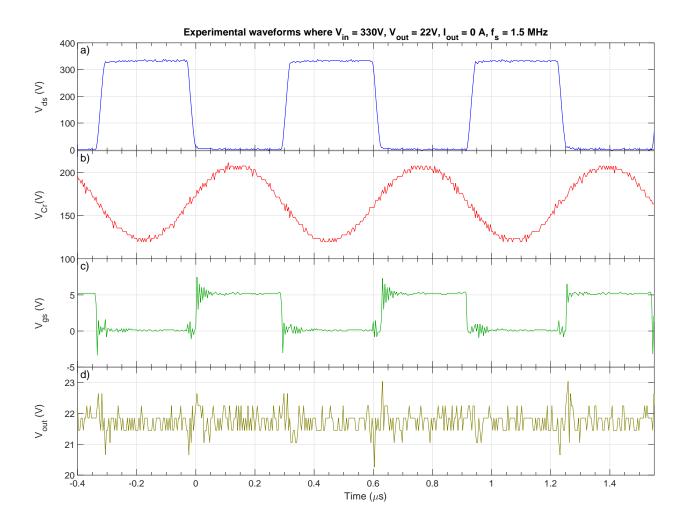

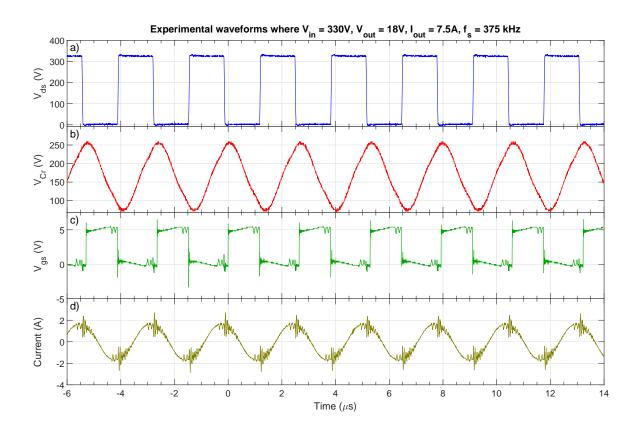

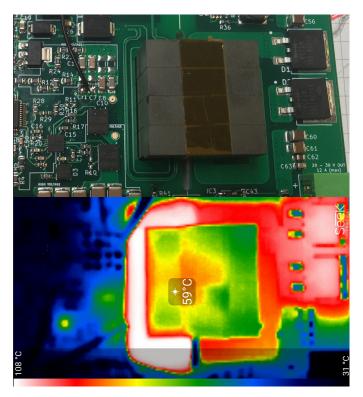

| 6  | Results and Analysis         6.1       Unidirectional Half-bridge LLC Converter         6.1.1       Measuring the Leakage Inductance         6.1.2       Accurate Equivalent Circuit Model of the Tank         6.1.3       Current Collapse in GaN HEMT         6.1.4       Experimental Waveforms         6.1.5       Testing Setup         6.1.6       Discussion of Limitations         6.1.7       Recommendations         6.2       Bidirectional DAHB Converter         6.2.1       Simulation Waveforms         6.2.2       Planar Transformer Design         6.2.3       Recommendations | . 62<br>. 62<br>. 64<br>. 65<br>. 67<br>. 68<br>. 68<br>. 68<br>. 69<br>. 69<br>. 70 |  |  |  |  |

| 7  | Conclusion         7.1       Answering Research Questions         7.2       Conclusion         7.3       Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 74                                                                                 |  |  |  |  |

| Α  | Appendix Soft Switching<br>A.1 ZVS in LLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                      |  |  |  |  |

| В  | Appendix Supplementary Information for GaN SwitchingB.1 GaN Normally "off" TransitorsB.2 Paralleling GaN Transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                      |  |  |  |  |

| С  | Appendix Supplementary Information for the Magnetics Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 83                                                                                   |  |  |  |  |

| D  | Appendix Supplementary Information for the Design Chapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                      |  |  |  |  |

| Bi | Bibliography 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                      |  |  |  |  |

# Nomenclature

| η           | Efficiency                                     |

|-------------|------------------------------------------------|

| μ           | Total permeability of a material               |

| $\mu_o$     | Permeability of free space                     |

| $\mu_r$     | Relative permeability of a material            |

| Φ           | Phase shift                                    |

| $\phi$      | Flux                                           |

| ρ           | Resistivity                                    |

| $\tau_{dt}$ | Dead time                                      |

| $	au_{rr}$  | Reverse recovery time                          |

| а           | Voltage gain characteristic of the transformer |

| $A_c$       | Core cross-sectional area                      |

| $A_L$       | Inductance factor                              |

| $A_w$       | Trace cross-sectional area                     |

| В           | Flux density                                   |

| $B_s$       | Flux density saturation point                  |

| $C_{DS}$    | Drain to source capacitance                    |

| $C_{GD}$    | Gate to drain capacitance                      |

| $C_{GS}$    | Gate to source capacitance                     |

| $C_{HB}$    | Parasitic capacitance summation                |

| $C_r$       | Resonant capacitor                             |

| $C_{WW}$    | Winding-to-winding capacitance                 |

| d           | Relationship between input and output for DAHB |

| $D_{pen}$   | Penetration depth                              |

| dc          | Duty cycle 50%                                 |

| $F_{FF}$    | Fringing flux factor                           |

| $f_{R1}$    | Resonant frequency of the tank                 |

| $f_{R2}$    | Lower resonance frequency                      |

*f*<sub>SR</sub> Self-resonant frequency

| $f_s$           | Switching frequency                |

|-----------------|------------------------------------|

| Н               | Magnetizing force                  |

| $H_s$           | Magnetizing force saturation point |

| i <sub>2</sub>  | Leakage inductance current         |

| I <sub>cc</sub> | Gate driver supply current         |

| I <sub>d</sub>  | Drain current                      |

| i <sub>L</sub>  | Tank inductor current              |

| $K_f$           | Waveform coeffficient              |

| $l_g$           | Length of the air gap              |

| $L_k$           | Leakage inductance                 |

| $L_m$           | Magnetizing inductance             |

| $L_p$           | Parallel component of inductance   |

| $L_r$           | Resonant inductor                  |

| $L_s$           | Series component of inductance     |

| $l_w$           | Length of a trace                  |

| mmf             | Magnetomotive force                |

| MPL             | Mean path length                   |

| Ν               | Turns ratio of a Transformer       |

| Q               | Quality factor                     |

| $Q_{rr}$        | Reverse recovery charge            |

| $R_{ac}$        | AC loss component                  |

| $R_{dc}$        | DC loss component                  |

| $R_{ds(on)}$    | Drain to source (on) resistance    |

| $R_l$           | Load resistance                    |

| $T_s$           | Switching period                   |

| V <sub>cr</sub> | Voltage across resonant capacitors |

| $V_F$           | Forward voltage drop of a diode    |

| $V_{HB}$        | Voltage across the half-bridge     |

| $V_H$           | High voltage                       |

| $V_L$           | Low voltage                        |

| W               | Length of the core window          |

| 147             | Area of the core window            |

$W_a$  Area of the core window

# **List of Figures**

| 1.1<br>1.2<br>1.3 | Conceptual illustration of the electrification ladder<br>Diagram of a DC Microgrid<br>A diagram highlighting the node where a point of load converter (a specific type of PEI)<br>connects to the DC microgrid. This node is comprised of not only the bi-directional<br>DC/DC converter (most relevant for this research) but also to a maximum power point<br>tracking (MPPT) converter for the solar connection and USB type C compatible connec-<br>tions for the SHS | 2<br>2<br>4 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

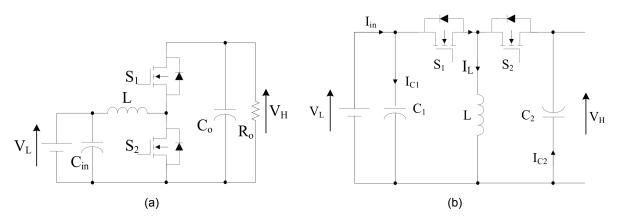

| 2.1               | (a) Schematic of a bidirectional (non-isolated) Buck and Boost (b) Schematic of a bidi-                                                                                                                                                                                                                                                                                                                                                                                   | -           |

| <u>.</u>          | rectional (non-isolated) Buck-Boost                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7<br>9      |

| 2.2<br>2.3        | Schematic of a bidirectional flyback converter                                                                                                                                                                                                                                                                                                                                                                                                                            | 9<br>10     |

| 2.3               | Schematic of a bidirectional push-pull converter                                                                                                                                                                                                                                                                                                                                                                                                                          | 11          |

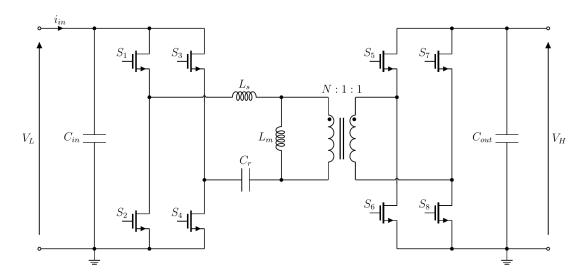

| 2.5               | Schematic of a bidirectional LLC converter, where the magnetizing inductance $L_m$ can also be denoted as $L_p$ which represents the parallel component of inductance in the                                                                                                                                                                                                                                                                                              |             |

| ~ ~               | resonant tank                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12          |

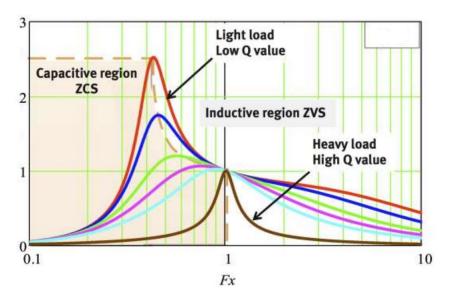

| 2.6               | Gain curve for a LLC converter, where $F_x = f_{R1}$                                                                                                                                                                                                                                                                                                                                                                                                                      | 13          |

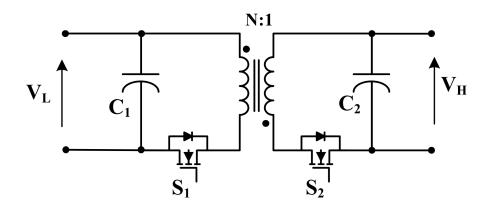

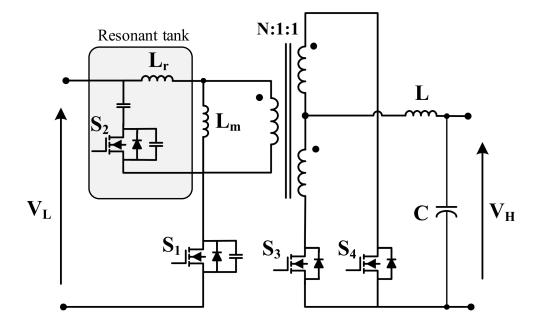

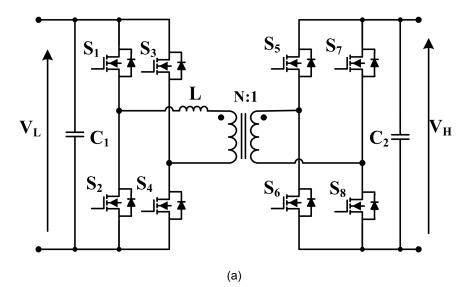

| 2.7               | (a) Schematic of a bidirectional dual active bridge (DAB) converter (b) Schematic of a bidirectional dual Active half-bridge (DAHB) converter                                                                                                                                                                                                                                                                                                                             | 16          |

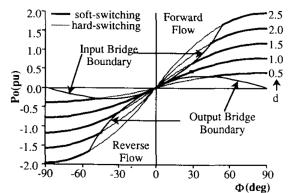

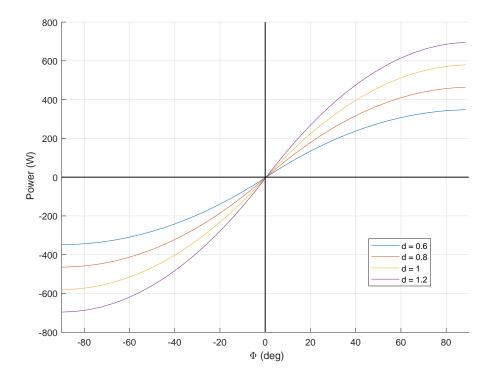

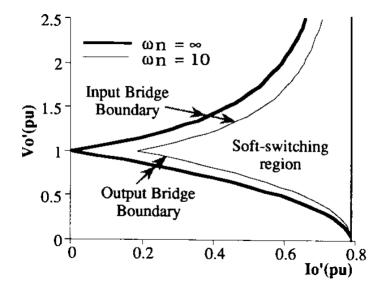

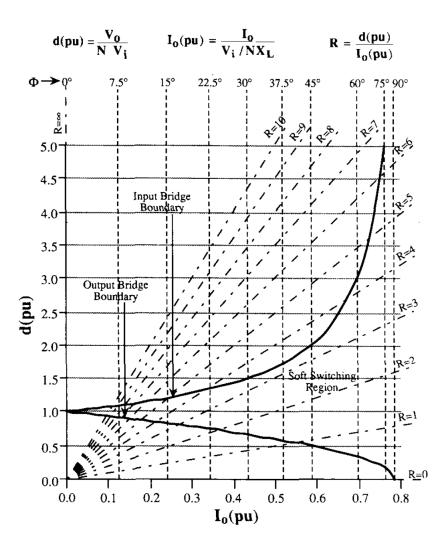

| 2.8               | Bidirectional power flow characteristics portrayed by a power output versus phase shift                                                                                                                                                                                                                                                                                                                                                                                   | 10          |

| 2.0               | relation. d is the power relationship between input and output                                                                                                                                                                                                                                                                                                                                                                                                            | 17          |

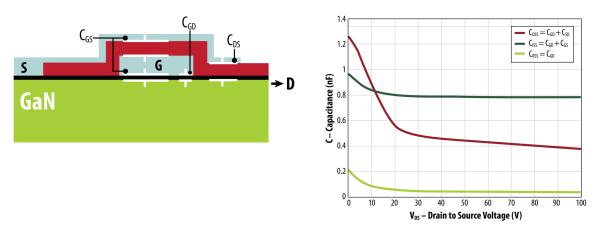

| 2.9               | Locations of parasitic capacitance within the cross section of the GaN transistor junction.                                                                                                                                                                                                                                                                                                                                                                               | ••          |

|                   | The graph shows the magnitude of each of the individual parasitic capacitances                                                                                                                                                                                                                                                                                                                                                                                            | 20          |

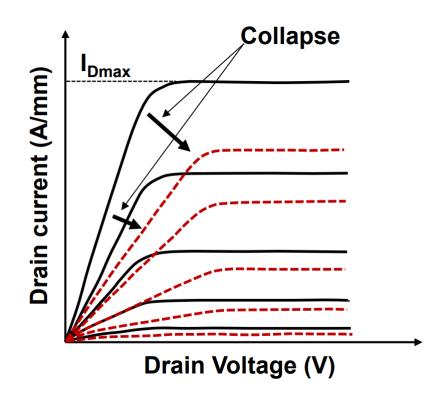

| 2.10              | IV curve for a GaN transistor where the effects of current collapse can be seen alongside                                                                                                                                                                                                                                                                                                                                                                                 |             |

|                   | normal IV characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21          |

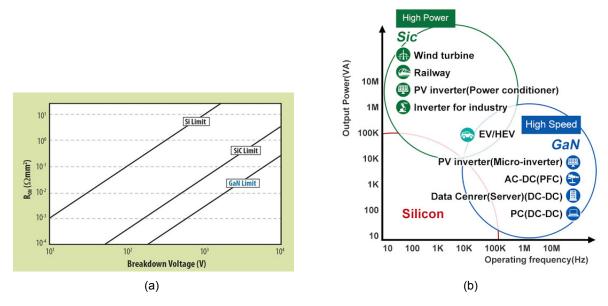

| 2.11              | Graph which portrays the comparison between the breakdown voltage and on-resistance                                                                                                                                                                                                                                                                                                                                                                                       | ~~          |

| 0.40              | of Si, SiC, and GaN                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22          |

| 2.12              | (a) Comparison between the breakdown voltage and on-resistance of Si, SiC, and GaN                                                                                                                                                                                                                                                                                                                                                                                        | າາ          |

|                   | (b) Application map for semiconductor devices based on output power and frequency .                                                                                                                                                                                                                                                                                                                                                                                       | 23          |

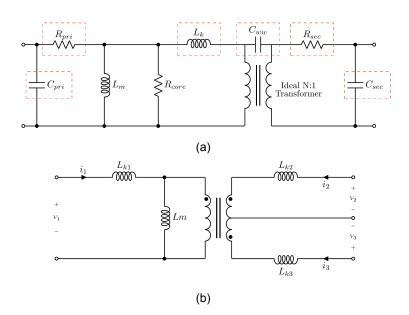

| 3.1               | (a) Circuit model portraying the parasitic elements of a transformer. (b) Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                              |             |

|                   | model for a N:1:1 winding center-tapped secondary transformer for the case where $L_m$                                                                                                                                                                                                                                                                                                                                                                                    |             |

|                   | $>> L_k$                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26          |

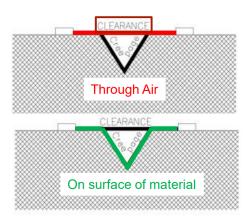

| 3.2               | Clearance and Creepage in a Transformer                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27          |

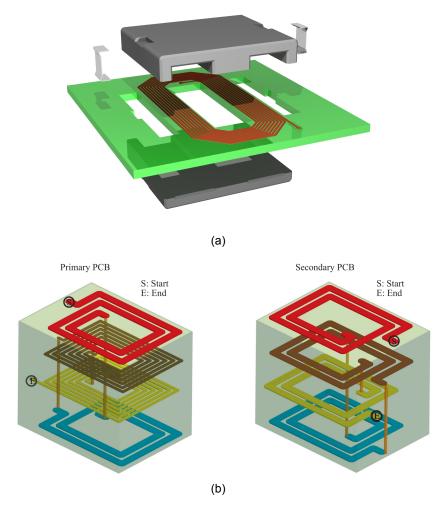

| 3.3               | 3D representations of a Planar Transformer                                                                                                                                                                                                                                                                                                                                                                                                                                | 28          |

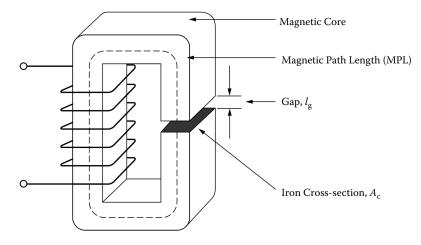

| 3.4               | A basic magnetic core with an air gap                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29          |

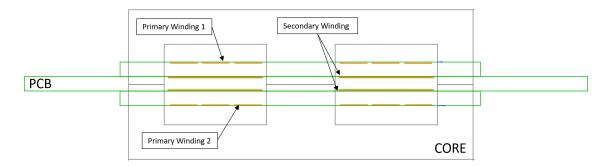

| 3.5               | Cross sectional image of a planar transformer with 3 PCBs, a 6:1 turns ratio, and an                                                                                                                                                                                                                                                                                                                                                                                      |             |

|                   | interleaved winding configuration where the secondary is sandwiched by the primary                                                                                                                                                                                                                                                                                                                                                                                        | 31          |

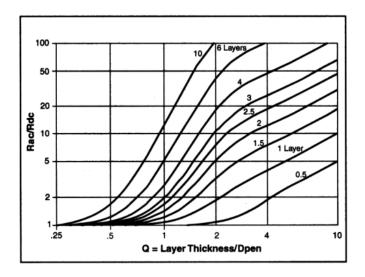

| 3.6               | Dowell Graph where the x-axis is Q = layer thickness / $D_{pen}$ and the y-axis is the ratio                                                                                                                                                                                                                                                                                                                                                                              | ~~          |

| 3.7               | between $R_{AC}$ and $R_{DC}$                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33<br>34    |

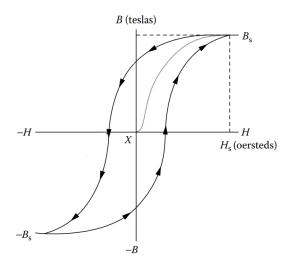

| 3.7<br>3.8        | A typical hysteresis curve                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34<br>36    |

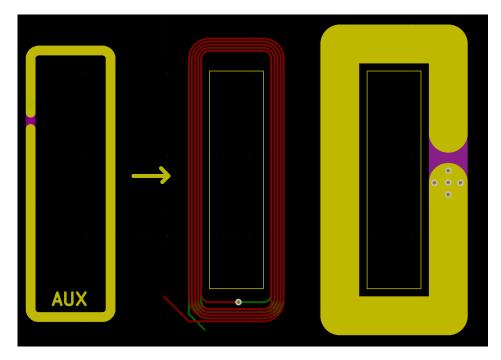

| 3.8<br>3.9        | Traces generated by a python script. An auxiliary winding created with two layers in                                                                                                                                                                                                                                                                                                                                                                                      | 50          |

| 0.0               | parallel was extracted from the primary side and shown on the left                                                                                                                                                                                                                                                                                                                                                                                                        | 38          |

|                   | · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

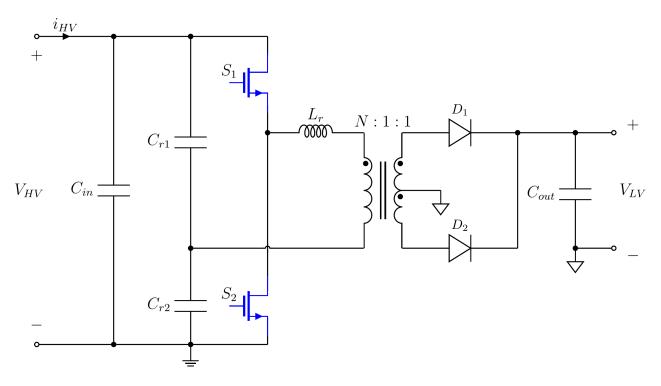

| 4.1        | Basic Schematic for the unidirectional LLC converter where $L_r = L_k$                                                                                                                                                                                                                                                                                                                          | 41       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

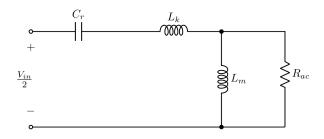

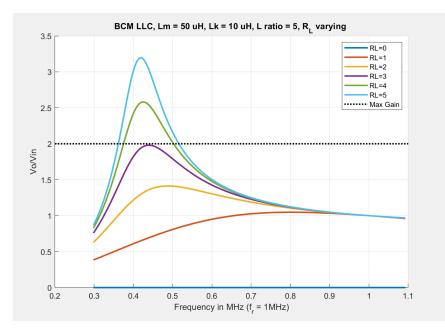

| 4.2<br>4.3 | Equivalent circuit model for an LLC resoanct tank where $L_m >> L_k$<br>Gain curve for the designed LLC converter, where $f_{R1} = 1$ MHz and the black dotted line<br>represents the maximum gain of the system which would be the worst-case-scenario if<br>$V_{in}$ was 300 and $Vout$ needed to be 30 V                                                                                     | 42<br>43 |

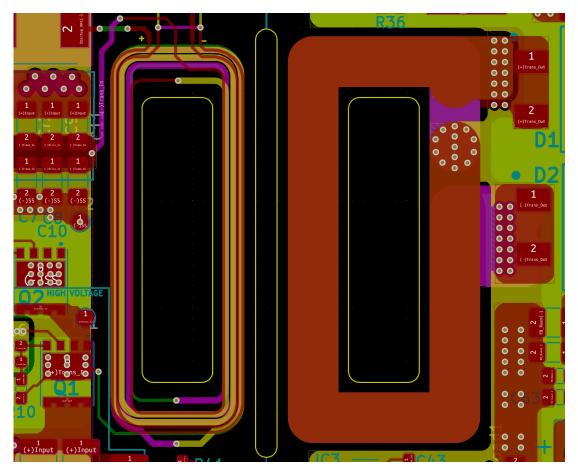

| 4.4        | Layout of the planar transformer for the unidirectional half-bridge LLC converter. The top layer (red), primary side (left), includes 2 parallel traces creating an auxiliary winding and one primary turn (out of the 10 required turns). The secondary side is a center-tapped configuration with 2 turns, each containing one inner layer in parallel in order to increase current handling. | 45       |

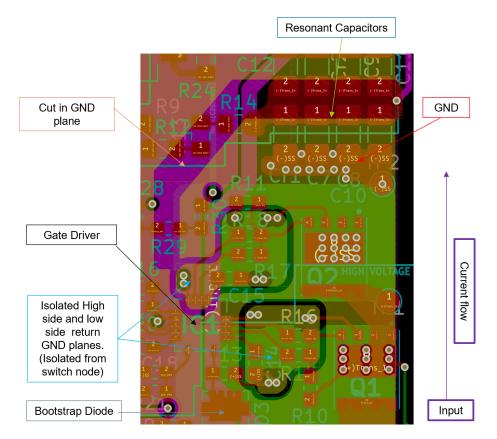

| 4.5        | PCB layout for the unidirectional half-bridge LLC converter where the traces and foot-<br>prints are shown. The red, yellow, pink, and green coloration depicts which layer the<br>trace or footprint is on and they refer to the top, first inner, second inner, and bottom                                                                                                                    | 10       |

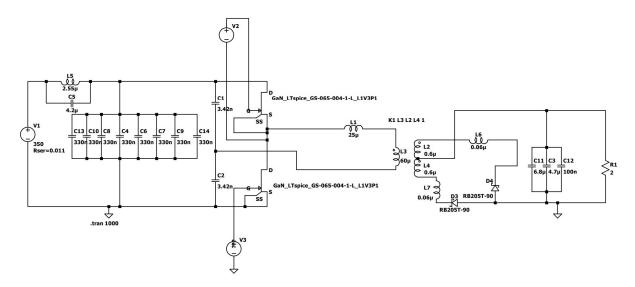

| 4.6        | layers, respectively                                                                                                                                                                                                                                                                                                                                                                            | 48<br>49 |

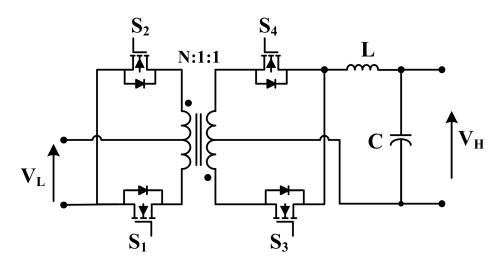

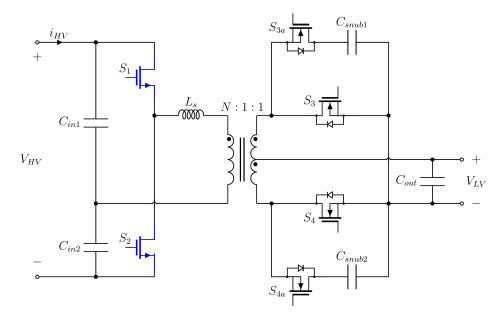

| 5.1        | Basic Schematic for the bidirectional MDAHB converter                                                                                                                                                                                                                                                                                                                                           | 51       |

| 5.2        | Phase versus power relationship based on equation 5.1. <i>d</i> is the input to output relationship $N * Vout/V_{HB}$ where $VHB = V_{in}/2$ . d = 0.85 is the nominal 350 V input and 25 V output relationship                                                                                                                                                                                 | 53       |

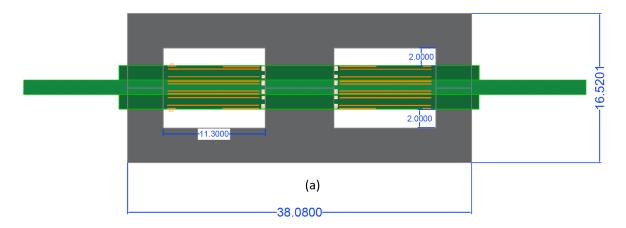

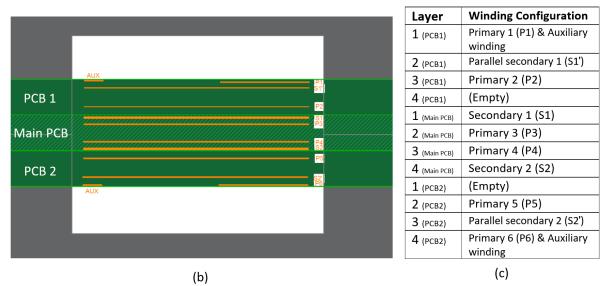

| 5.3        | (a) Complete cross-sectional area of the DAHB PT (including relevant core dimensions in mm) (b) Zoom-in of the cross sectional area of the left most window of the planar E-Core (in order to view the winding configuration) (c) Explanatory table for the layers and                                                                                                                          |          |

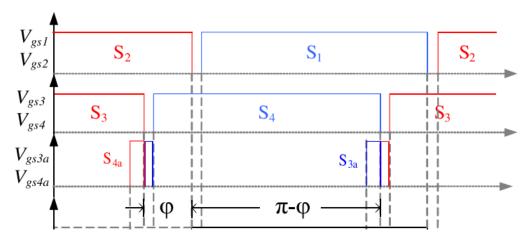

| 5.4        | winding configurations                                                                                                                                                                                                                                                                                                                                                                          | 54       |

| 5.5        | reverse conduction mode                                                                                                                                                                                                                                                                                                                                                                         | 58<br>59 |

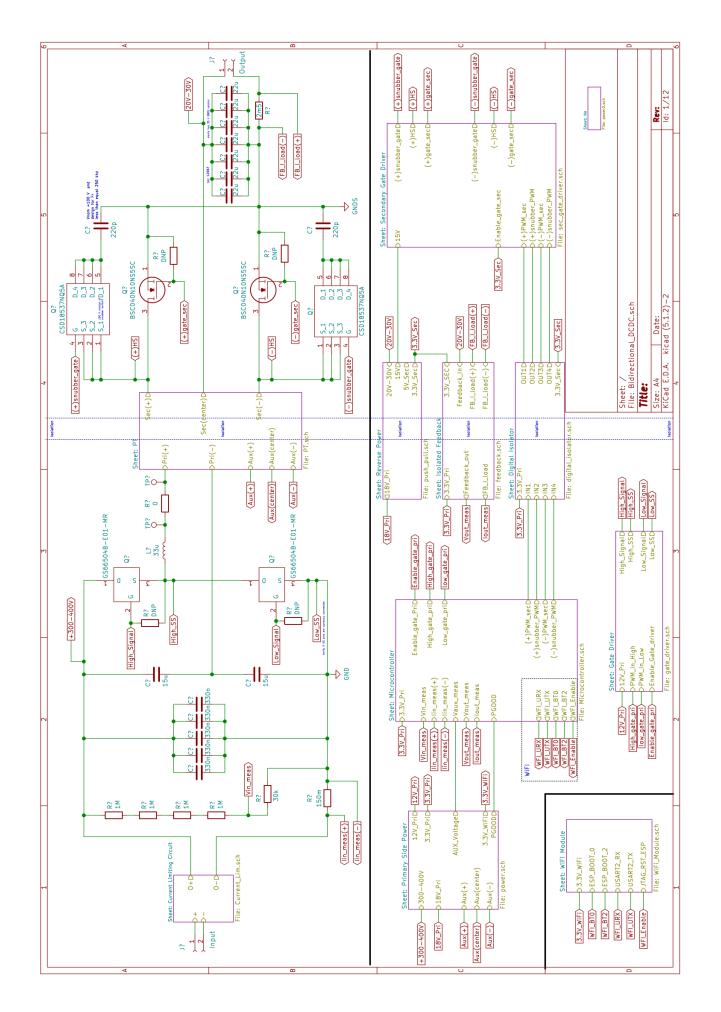

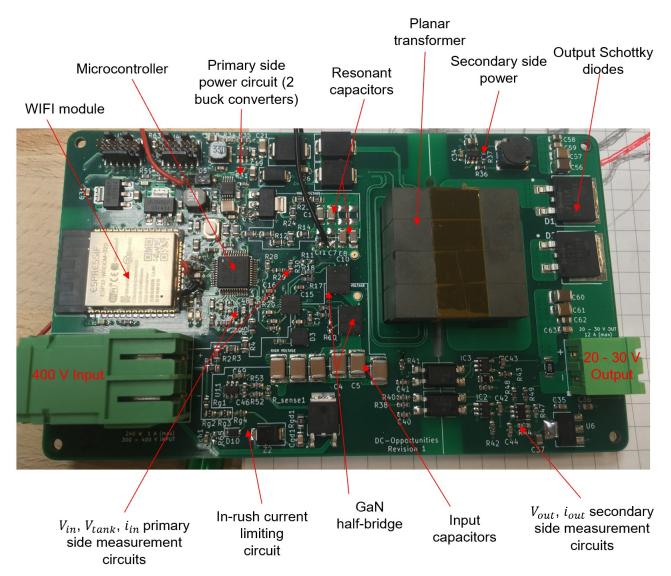

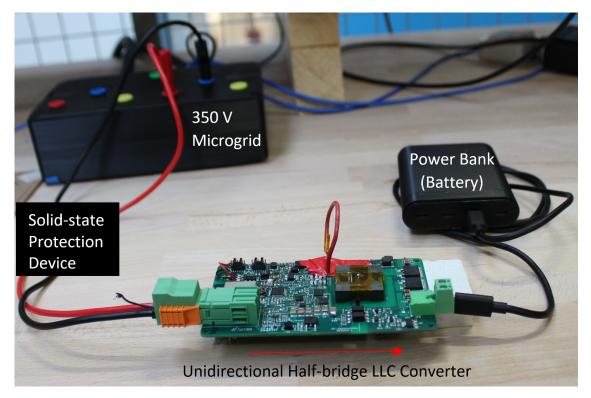

| 6.1        | Hardware Overview of the Unidirectional LLC converter. Dimensions 120 mm x 70 mm                                                                                                                                                                                                                                                                                                                | 61       |

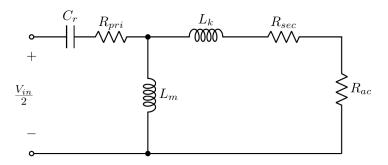

| 6.2        | Actual equivalent circuit model for the unidirectional LLC converter where $L_k$ is the equivalent leakage of the primary and secondary added in series                                                                                                                                                                                                                                         | 63       |

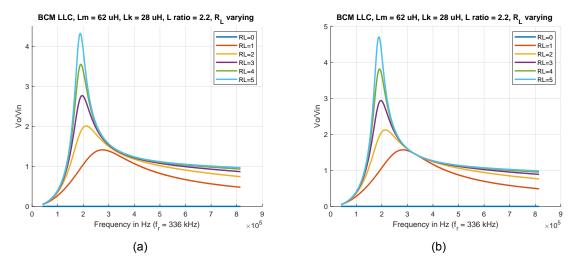

| 6.3        | (a) Actual gain versus frequency curve for the unidirectional LLC converter (b) Ideal gain versus frequency curve (not considering series resistance components) for the unidirec-                                                                                                                                                                                                              | 05       |

| 6.4        | tional LLC converter                                                                                                                                                                                                                                                                                                                                                                            | 63       |

| 6.6        | 350 V ) were used in the calculation $\dots$ Experimental waveforms at no load where $V_{ds}$ and $V_{gs}$ are the voltages of the bottom                                                                                                                                                                                                                                                       | 64       |

|            | side switch in the half-bridge and $V_{cr}$ is the voltage across the resonant capacitors. The                                                                                                                                                                                                                                                                                                  |          |

| 6.7        | output voltage $V_{out}$ is approximately 22 V at $V_{in}$ equal to 330 V Experimental waveforms at full load (7.5 A) where $V_{ds}$ and $V_{qs}$ are the voltages of the                                                                                                                                                                                                                       | 65       |

| 0.7        | bottom side switch in the half bridge and $V_{cr}$ is the voltage across the resonant capacitors                                                                                                                                                                                                                                                                                                | 66       |

| 6.8        | Thermal Behavior at a 150 W load $I_{out} = 7.5A$                                                                                                                                                                                                                                                                                                                                               | 67       |

| 6.9        | Picture of the verified working test set up for the half bridge LLC converter: 350V input and 24 V output to a SHS                                                                                                                                                                                                                                                                              | 67       |

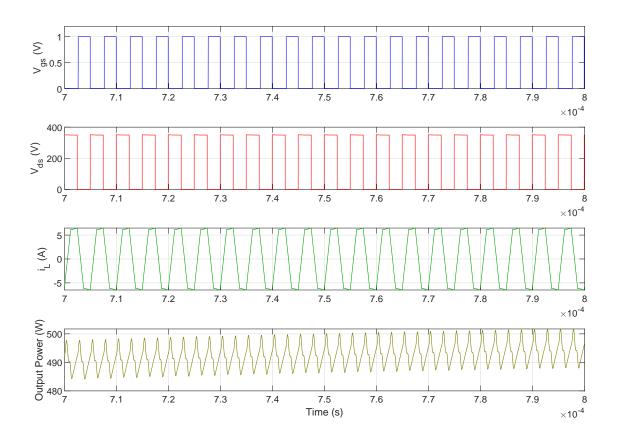

| 6.10       | Simulation results for forward operation at steady-state where $V_{in}$ = 350 V, $V_{out}$ = 27 V,                                                                                                                                                                                                                                                                                              |          |

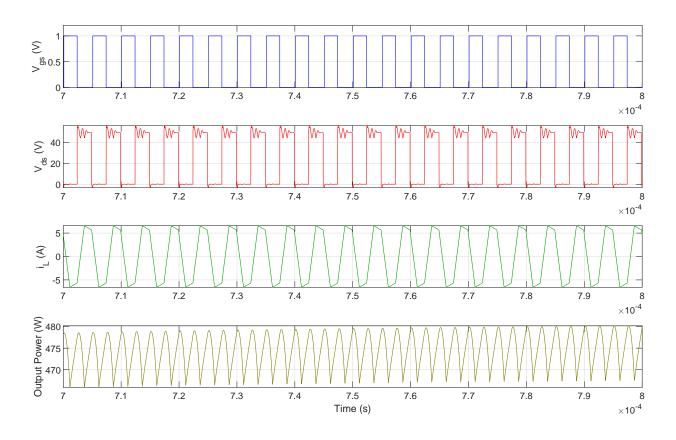

| 6 11       | $I_{out}$ = 18 A, $f_s$ = 200 kHz, and $\Phi = \pi/2$ Simulation results for reverse operation at steady-state where $V_{in}$ = 25 V, $V_{out}$ = 345 V,                                                                                                                                                                                                                                        | 69       |

| 0.11       | $I_{out}$ = 1.4 A, $f_s$ = 200 kHz, and $\Phi = \pi/2$                                                                                                                                                                                                                                                                                                                                          | 70       |

| A.1        | Effect of magnetizing inductance on the ZVS range in a DAB converter                                                                                                                                                                                                                                                                                                                            | 78       |

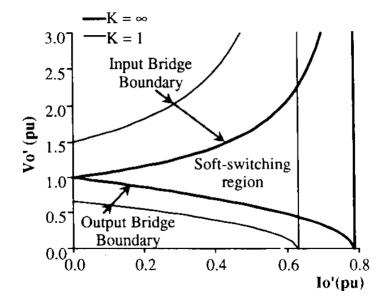

| A.2<br>A.3 | Effect of parasitic capacitance on the ZVS range in a DAB converter                                                                                                                                                                                                                                                                                                                             | 78       |

| A.5        | range also depicted                                                                                                                                                                                                                                                                                                                                                                             | 79       |

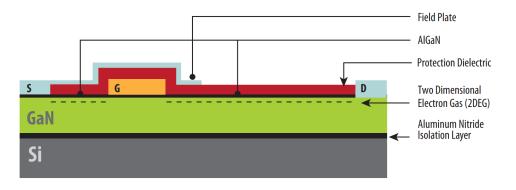

| B.1 | Structure of an enhancement-mode GaN HEMT                                          | 81 |

|-----|------------------------------------------------------------------------------------|----|

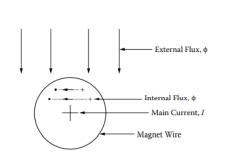

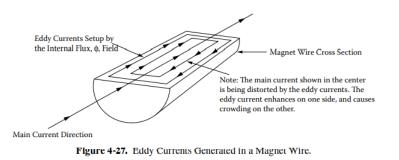

| C.1 | Diagram presenting a visual representation of eddy currents in a copper wire       | 83 |

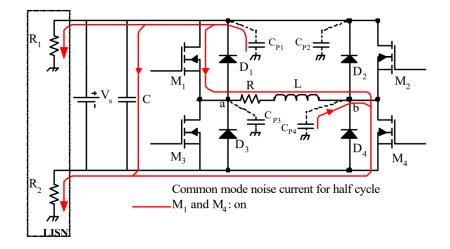

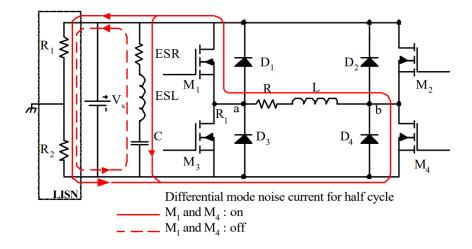

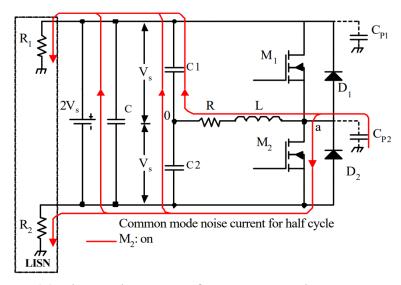

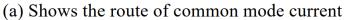

| D.3 | Differential and common-mode currents in full bridge circuit                       |    |

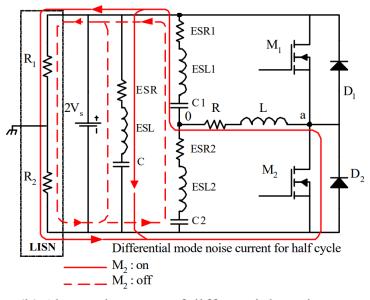

|     | is FR4 material and prepreg (pre-impregnated) is fiberglass impregnated with resin | 88 |

### Chapter 1

## Introduction

In this chapter, the relevant background for rural electrification and the DC microgrid (a smaller variant of a direct current (DC) distribution grid) is presented. Furthermore, the motivation for the work is elaborated.

#### 1.1 Problem Definition: Rural Electrification, Solar Home Systems, and the DC Microgrid

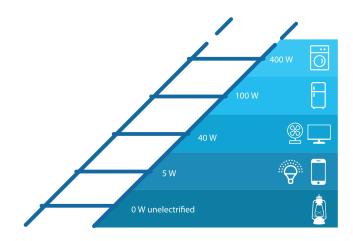

The large-scale emergence of decentralized renewable energy generation alongside the modern "green energy" ideologies permeating throughout the political and societal spectrum are setting a new standard for the future of power and the modernized power grid. When considering the future of power, the 840 million people who have no access to electricity and an additional one billion more who still have an unreliable electricity connection [1, 2] remain as one of the major concerns moving forward. A stable electrical connection provides rural communities with the ability to utilize their natural energy sources, such as solar or wind. As an example, in sub-Sahara Africa, 573 million out of 840 million people lack electricity [1]. Individuals in these communities typically work as farmers and in hard labor conditions. Moreover, this group is poverty-stricken and lacks sufficient medical care, education, and other social welfare. In order for these communities to grow in a positive manner, especially in regard to education, access to electricity is vital. However, it is still unclear what is the most effective way to achieve rural electrification and studies are currently being conducted on methods which are based on new available technology. In order to discuss the pathways towards electrification, it is necessary to identify the different tiers or steps that are needed in the electrification process. This process takes into consideration the trend that the power demand required by a user increases over time. This growth in the electrification process can be visualized by the electrification ladder (presented in [3, 4]) shown in figure 1.1. Each rung of the ladder represents a different power level that has unique loads and appliances associated with it. Higher levels represent the increase in the number of appliances, and therefore, the overall electricity demand.

Three different rural electrification pathways— grid extension, stand-alone solar-based solutions, such as solar home systems (SHS), and centralized microgrids —are critically examined in [5]. The results of the study in [5] are developed based the on circumstances seen by the communities with no access to electricity. Additionally, the study considers current developing technology when proposing the conclusions. Grid extensions (expanding the national grid's network to provide electricity access [6]) are a costly endeavor and this results in an infeasible method for providing electricity to these communities. However, SHSs are a less expensive and more viable solution. The pathway employing SHSs can achieve the 5 W, 40 W, and sometimes 100 W tier of electrification but it is only a stepping stone along the path and is not the ultimate solution.

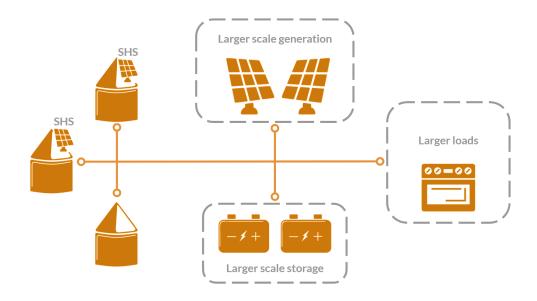

A DC microgrid has unique characteristics such as energy sharing, inherent plug and play capability, and its ability to grow over time. In figure 1.2, the architecture of a typical DC microgrid used in rural electrification is shown. The microgrids are usually centralized with central power generation and storage. It is important to distinguish that although smaller SHS based forms of these grids do have a decentralized way of delivering electricity, the most robust and higher power forms of these off-grid

Figure 1.1: Conceptual illustration of the electrification ladder. As a household scales up the ladder, the electricity demand- in Watts (W) -increases through the addition of higher power (or greater number of) appliances [5]

microgrids generally have centralized large-scale PV and battery storage architecture. Centralized microgrids are a vital part of the electrification process but directly implementing a full grid into a rural community has many downsides. Most significantly, the cost is high compared to starting with individual SHSs. Furthermore, an overall demand estimation is needed in the design of a microgrid. This estimation relies on many assumptions and it is difficult to predict the changes in electricity demand over time. In order to perfect this process and find the best pathway to electrification, the implementation of a bottom-up DC microgrid is proposed as the key "missing link" between all of the possible electrification pathways [5]. The bottom-up characteristic refers to building up in a logical or modular manner in order to properly account for the overall demand of the community. Additionally, it is more economically suitable for these communities to have an implementation process that requires multiple smaller investments versus a single large investment.

Figure 1.2: Diagram of an interconnected SHS-based meshed DC microgrid with additional centralized generation and storage. The bottom house is shown without an SHS, revealing that purely consumptive houses can join the microgrid.

The modular process begins with an individual SHS for each home. The evolved form of a single SHS is an interconnected SHS meshed DC microgrid which can be established by the interconnection of existing SHSs. This form of a DC microgrid is decentralized (represented by the homes and interconnections on the left side of figure 1.2). These decentralized solutions, can provide on demand

electricity for lower levels of power as well as enable energy sharing between homes. Conversely, a centralized grid (with larger photovoltaic (PV) panels and energy storage systems (ESSs)) can grant consistent higher levels of power proportionate to the 100 W and 400 W load level. In time, when the national grid arrives, a previously established DC microgrid can readily serve as a ready distribution grid for communities naturally requiring more power demand as they develop. Additionally, the process of implementing grid extensions reduces to a simplified electrical connection at the perimeter of villages because the interior is already interconnected by a DC microgrid.

#### **1.2 Problem Definition: Power Electronics**

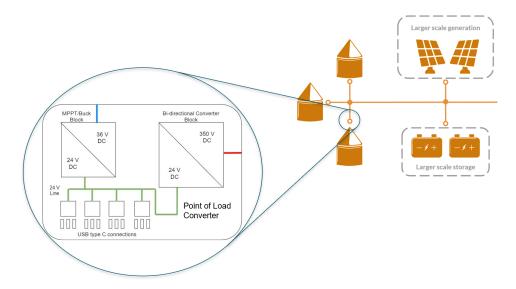

Power electronics serve as the interface between different components of a DC microgrid. In figure 1.2, each node represents a power electronic interface (PEI). Therefore, it is essential to successfully implement many DC/DC conversions (occasionally a DC/AC conversion for some loads), with both unidirectional and bidirectional power flow, to each part of the DC microgrid. These microgrids for rural electrification work at a 300 - 400 Volt (V) range, typically at a nominal 350 V. Solar home systems provide power to low power loads in tiers 1 to 2 of the electrification ladder with 12 V battery and 12 V distribution [7]. This SHS operating voltage can vary up to but not exceeding a voltage of 48 V [8]. There are also new emerging connectivity methods like the USB type C load connection. Its inherent power delivery characteristics allows for the DC/DC power electronic converter to have an adjustable voltage that can vary from 5 - 20 V.

The PEIs at the PV panel, ESS or battery bank, and high power load are quite similar to the SHS connections of the DC microgrid. However, the nominal values for the voltage differ from the standard DC voltage at the SHS-to-DC microgrid connection. In order to facilitate greater tiers of consumption, these nodes of the microgrid require a higher voltage level because it minimizes the distribution losses. Furthermore, the voltage level at these nodes often varies depending on series/parallel configurations (for PV and batteries) and, for the high power loads, it is dependent on the operation voltage of the appliance which generally is either at 110 V or 240 V.

At the heart of many power electronic devices, there is a transformer. The transformer is responsible for the stepping-up (or stepping-down) of the voltage. A transformer and its windings of wires naturally have a unique characteristic called the turns ratio. This ratio is responsible for the gain in the voltage and current from its input to output (regarded as primary and secondary sides in practice). Transformers also grant electric isolation between the primary and secondary sides of a switching converter. A planar transformer (PT) is a contemporary and innovative design of a traditional transformer. Most notably, it can be recognized by its lack of wires which are replaced by traces on a printed circuit board (PCB). It is described as planar because these transformers are typically very flat and use specific core types that are horizontal and flat. The core (generally an iron or ferrite material) makes up the overall shape of the transformer to other through electromagnetic induction. It so happens that planar transformers have unique attributes that mesh well with the type of converters found at PEIs in DC microgrids used in rural electrification.

#### 1.3 Motivation

Historically, DC/DC converters for high power applications, such as wind turbines and electric vehicle (EV) charging, are rated at 1 kW or greater due to the nature of the loads and the high societal demand for power. Moreover, alternating current (AC) has dominated as the main form of electricity in power transmission. This AC infrastructure usually pushes the DC/DC conversions to happen externally via a converter attached to the load itself. These converters are usually referred to as point of load converters. Therefore, DC/DC conversion typically finds its main applications in low power, such as power supplies, and household loads. These applications are typically limited to less than 100 W. Converters designed for the 200 W to 1 kW range do exist, such as server power supply used in telecommunications [9], but are usually only used in definitive specialized applications. This category of converter is more uncommon and less explored in literature compared to the other power ranges of converters previously discussed.

However, due to the emergence of the DC microgrid and the movement to provide stable electricity access to all, a new niche of converters has been brought to light. This class of converter operates in the 200 W to 900 W range and are specifically designed to work in a decentralized DC microgrid environment. These converters must also have voltage regulation at the output in order to provide the correct voltage level to different loads, thereby one converter is used to satisfy all household load requirements and the grid connection. It is important to mention that converters in rural electrification fall in this power range but also similar PEI applications at this power level could be utilized in the modernized hybrid AC/DC grid of the future, presented in [10], to provide the needed DC/DC conversion in the DC part of the grid.

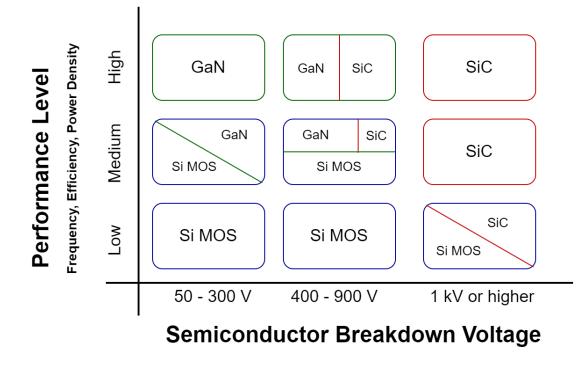

The motivation for this thesis is to find the best topologies, switching technology, and to create successful designs for a unidirectional and bidirectional version of a **DC microgrid variable power output converter**. The research specifically focuses on the DC/DC converters that connect a SHS to the DC microgrid (the connection point is shown in detail in figure 1.3). The Gallium nitride (GaN) transistor is the preferred switch technology for this application due to its effectiveness in the low voltage (up to 650 V), high performance scenario. GaN transistors have inherent benefits such as zero reverse recovery, low switch resistance, and low parasitic capacitance which allows for high frequency operation with low switching losses resulting in smaller passive components. The work also takes into consideration the unique possibilities available to the design due to the lower power (200 - 900 W) characteristic of these converters. In addition, the advantages and design of the planar transformer will be explored for these applications. This research aims to bridge the gap from the standard DC/DC converter of this power level to a more effective and efficient converter custom-fit for a DC microgrid, especially those used in rural electrification.

Figure 1.3: A diagram highlighting the node where a point of load converter (a specific type of PEI) connects to the DC microgrid. This node is comprised of not only the bi-directional DC/DC converter (most relevant for this research) but also to a maximum power point tracking (MPPT) converter for the solar connection and USB type C compatible connections for the SHS

#### 1.4 Research Questions

- How can a unidirectional DC/DC converter be designed for the interconnection of a 350V DC microgrid to individual households for rural electrification that includes high switching frequency GaN technology?

- 2. How can a bidirectional DC/DC converter be designed to achieve the same purpose but also with a higher power rating?

- 3. How to design a PCB based planar transformer for these two converters and why is a planar transformer preferred for these applications ?

#### 1.5 Outline

The report is divided into 7 chapters and is followed by an appendices which contains supporting information for additional reference. The following list provides the title and a small summary for each chapter:

#### **Chapter 1: Introduction**

• Provides the relevant background for rural electrification and the DC microgrid (a smaller variant of a direct current (DC) distribution grid) is presented. Furthermore, the motivation for the work is elaborated.

#### **Chapter 2: Literature Review and Background Information**

• Provides the design theory for the main converters used in this research. Alongside the review, an analytical topology selection process (comparing multiple topologies) is presented. The section ends with a theoretical overview and analysis of Gallium nitride (GaN) switching.

#### **Chapter 3: Planar Transformers**

• Describes the theory and design process for creating a planar transformer. It will conclude by presenting the benefits of these transformers, especially for the power levels typically found in rural electrification.

#### Chapter 4: Unidirectional Half-bridge LLC Prototype Modeling, Design, and Construction

Provides the complete design process for the unidirectional Half-bridge LLC DC/DC converter. The process includes simulations, transformer design, thermal considerations, and PCB layouting.

#### Chapter 5: Bidirectional DAHB Prototype Modeling and Design

• Provides the complete design process for the bidirectional DAHB converter. The process includes simulations, transformer design, and thermal considerations.

#### **Chapter 6: Results and Analysis**

• Provides a summary of the testing results for the unidirectional half-bridge LLC converter and the simulation results for the bidirectional DAHB converter. Moreover, it will analyze findings, provide explanations, and give recommendations based on the results.

#### **Chapter 7: Conclusion**

• Provides answers to the research questions and the conclusions of the work. Additional recommendations for future work are also included.

### **Chapter 2**

# Literature Review and Background Information

Chapter 2 provides the design theory for the main converters used in this research. Alongside the review, an analytical topology selection process (comparing multiple topologies) is presented. The section ends with a theoretical overview and analysis of Gallium nitride (GaN) switching.

#### 2.1 Topology Comparison

The following review is comprised of the more prominent single-stage topologies which permit bidirectional power flow, galvanic isolation, and efficient DC/DC conversion. Two separate converters were designed for this work; a unidirectional and a bidirectional version.

#### 2.1.1 Buck, Boost, and Buck-Boost Converters

Figure 2.1: (a) Schematic of a bidirectional (non-isolated) Buck and Boost (b) Schematic of a bidirectional (non-isolated) Buck-Boost [13]

A boost/buck converter steps up/down a DC voltage from input to output. The circuit operation is dependent on the conduction state of the switches. During the on state, current within the inductor increases and the anti-parallel diode in the other switch blocks current flow. In the off state, energy is transferred from the inductor to the capacitor resulting in a decreasing inductor current. Since current through the inductor can not instantaneously change, the diode of the switch conducts current [11]. Steady state operation can be characterized as discontinuous conduction mode (DCM) or continuous conduction mode (CCM). In DCM, the inductor current reaches zero in each cycle however, in CCM, the inductor current never reaches zero. Duty cycle control is used to adjust and regulate the voltage output.

A conventional boost/buck converter (seen in figure 2.1a) is typically non-isolated and can be transformed to operate bidirectionally with the use of switches in place of diodes. Parallel combination of an inductor and capacitor, typically seen at the outputs of both types of converters, acts as a second order low pass filter to reduce output voltage ripple. The only variant of these converters that fits the application niche would be a version that includes coupled inductors in the design in order to provide isolation. Coupled inductors can be normally coupled or inverse coupled. Inverse coupling allows for a larger inductance given an inductor of the same size that is normally coupled. The flux adds together to result in a higher flux with a smaller ripple. Inverse coupling can reduce core losses in the coupled inductor and allow for a smaller component to achieve the same level of inductance. There are tradeoffs in the design to consider but this section is limited to an overview of different configurations that can be implemented into boost/buck converters to allow for a more feasible design.

An interleaved version of these converters, in essence, is an exact replica of the converter in parallel with the original. The benefit of this is to half the current in each inductor while also decreasing the value of output voltage ripple. An interleaved configuration reduces the size of the passive components and, in certain scenarios, can reduce price, adverse thermal effects, and surface area of the system. More information can be found in [12]. The cascading of multiple of converters can also be implemented in order to increase the overall voltage boost (or reduction) ability of the converter and reduce current stress [13]. This is when two or more converters are connected in a series-like cascaded formation.

It is rare to find an example of a bidirectional isolated converter that uses the standard boost/buck set up. One example is the primary parallel isolated boost converter (PPIBC) introduced in [14]. It is possible that by using one or more of the aforementioned adjustments alongside coupled inductors, a converter could be designed for a rural electrification application. However, due to limited literature coverage of a bidirectional version with isolation and the tendency for an increasing number of components as more functionalities are added, these topologies are limited in this regard.

As for the buck-boost converter (non-isolated version shown in figure 2.1b), this topology is mostly used in its non-isolated form as a cascaded addition to a more conventional dual active full bridge switch converter. There are cases such as the buck-boost used in [15] with a coupled inductor. It uses three active switches along with three diodes. The converter uses both zero-current switching (ZCS) and zero-voltage switching (ZVS) to reduce losses. A buck-boost converter can operate in the kilo-watt power range but has multiple passive components because of the need for snubber circuits. There are some favorable options such as the converter presented in [15] but it remains a less popular topology choice in literature for bidirectional isolated converters.

#### 2.1.2 Flyback Converter

The flyback converter is one of the most common topologies utilized in low power applications. The flyback is known for its limitations at medium and high power ranges. This is a result of large ripple current in Boundary Conduction Mode (BCM) and DCM operation, the increased size of the coupled inductor, and high voltage stress of the switch. A flyback converter stores energy in the magnetic field of an air gap in a coupled inductor while the converter switch is conducting. When the transistor turns off, the magnetic field deteriorates and the energy stored in the air gap is drawn by the output load of the flyback converter. The flyback converter can be described as two inductors sharing a common core, in which the widings have opposite polarities.

However, because of the recent advancements in switching technology, there are switch options that have lower drain to source resistance and higher break down voltages. This has allowed for the emergence of flyback in the medium voltage range, realistically up to 300 W. A bidirectional DC-DC isolated version is shown in figure 2.2. It only requires two switches, where one is for active power flow in one direction and the other works as a diode for rectifying the output. The flyback converter should be operated in DCM or BCM mode so that soft switching can be implemented. This reduces the voltage ringing, the EMI, and losses in the switch.

Figure 2.2: Schematic of a bidirectional flyback converter [13]

The voltage stress on the switch in a flyback is high because it is composed of the input voltage, the reflected voltage of the output and the voltage spike due to the leakage inductance of the coupled inductor. Therefore, the switch voltage rating can be derived as  $V_{in} + N * (V_{out} + V_{fwd}) + L_k di/dt$  where  $V_{fwd}$  is the forward voltage drop of the diode and  $L_k di/dt$  is equal to the voltage due to the leakage inductance multiplied by the rise in current over time [16].

#### 2.1.3 Forward Converter

The forward converter is a DC/DC conversion topology that uses a transformer and its turn ratio to increase or decrease the output voltage. It provides galvanic isolation for the load and has multiple output windings which can be used to simultaneously produce both higher and lower voltage outputs [17]. The output voltage is determined by the input voltage, transformer turns ratio and duty cycle. The transformer has same-polarity windings, higher magnetizing inductance, and no air gap which also signifies that it does not store energy in the transformer [17]. A forward converter passes energy directly to the output through transformer during the conduction phase of the switch.

The bidirectional version of the forward converter, shown in figure 2.3, utilizes a clamped circuit to achieve ZVS. There have been hybrid configurations mentioned in literature within the 300 W to 900 W power range. These hybrid configurations are referred to as Forward-Flyback, Push-pull Forward, and Flyback-Push-pull. In these converters, the primary side of the transformer is derived from one of the mentioned isolated topologies and the secondary is derived from another, either current-fed or voltage-fed [13].

The multiple-switch forward converter is an effective topology for applications that require high efficiency and effective power handling capability for up to 500 W of power. The forward converter is often compared to flyback because they have similar efficiencies at relatively the same power levels. The forward converter has a disadvantage due to the presence of an extra inductor on the output and, additionally, is not well suited for high voltage outputs. The forward converter has an advantage over the flyback converter when high output currents are needed for the load. Since the output current is non-pulsating, it is well-suited for applications with currents that exceed 15 A [18].

Figure 2.3: Schematic of a bidirectional forward converter [13]

#### 2.1.4 Push-pull Converter

In a bidirectional push-pull converter (shown in figure 2.4), current flowing in the transformer primary is supplied from a pair of switches in a symmetrical push-pull circuit configuration. The switches are controlled with an alternating on and off signal which results in a transformer current that is periodically reversed. Consequently, current is drawn from the input line in both halves of the switching cycle. Push–pull converters have steadier input current, create less noise on the input line, and are more efficient in higher power applications.

A push-pull topology uses two primary windings to create a dual drive winding. This will utilize the core of the transformer in a significantly more efficient manner than the flyback or the forward converters. Moreover, push-pull converters will have smaller filters compared to the forward converters at the same power level [18]. On the downside, only half of the copper winding is conducting current at a time, hence increasing the resistance and copper losses compared to a transformer of a similar size.

The leading problems recorded in literature with push-pull converters are unbalanced flux in the windings and large voltage stress on the switches. Flux in the primary and secondary windings of the center-tapped transformer (discussed more in chapter 3) can become unbalanced and cause heating/loss. As for switch stress issues, each transistor must block more than twice the amount of voltage. There is also the added stress of the voltage spike at the beginning of the cycle due to energy caught in the leakage inductance of each winding in the center-tapped configuration. Stress on the switch makes the push-pull an undesirable topology choice for power factor correction (PFC) applications.

Figure 2.4: Schematic of a bidirectional push-pull converter [13]

#### 2.1.5 Isolated Resonant Converters

Resonant conversion is a longstanding topic known for providing converters with high efficiency, high power density, and smooth waveforms. Resonant converters are based on a "resonant inverter", which is a system that converts a DC voltage into a sinusoidal voltage [19]. It then provides this AC signal or power to a load. A network of switches creates a square-wave voltage that is applied to a resonant tank which is tuned to the fundamental component of the square wave [19]. The resonant tank will interact with the fundamental component and react in a negligible way with higher order harmonics, so that its voltage and current will be predominantly sinusoidal. The tank circuit is characterized by two reactive elements; the resonant capacitor ( $C_r$ ) and resonant inductor ( $L_r$ ) which can also be denoted as  $L_s$  as the series inductance component of an integrated magnetic structure. Different configurations of  $C_r$  and  $L_r$  define the power transfer behavior and classify the type of resonant converter. However, only a few of the different possible combinations are able to be used in an actual converter. The two basic structures are the series resonant converter and parallel resonant converter, comprised of one tank inductor and one capacitor. Multiple resonant elements can be combined to form multi-resonant converters, such as LCC, LLC, and CLLC converters, to name a few. The main difference between these converters is the frequency and output voltage gain relationship. In the case of multi-resonant converters, there are multiple resonant frequency points because of the different interactions between reactive elements of the tank at specific operating conditions. Another beneficial quality of resonant converters is the inherent zero-voltage switching capability for the primary side power switches and (in some cases) soft commutation for the output rectifier [20]. For the context of this thesis, the LLC converter will be the main resonant topology discussed. A more in-depth comparison of LLC, LCC, and CLLC converters can be seen in Appendix A.

#### 2.1.6 LLC Converter