#### The Zoom ADC An Energy Efficient ADC for High Resolution

Gonen, B.

10.4233/uuid:5bea521a-d6ac-4f6a-b45f-d2a87fec53ed

**Publication date**

**Document Version** Final published version

Citation (APA)

Gonen, B. (2021). The Zoom ADC: An Energy Efficient ADC for High Resolution. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:5bea521a-d6ac-4f6a-b45f-d2a87fec53ed

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# The Zoom ADC: An Energy Efficient ADC for High Resolution

#### Dissertation

for the purpose of obtaining the degree of doctor

at Delft University of Technology

by the authority of the Rector Magnificus Prof.dr.ir. T.H.J.J. van der Hagen

chair of the Board for Doctorates

to be defended publicly on

Wednesday 14, July 2021 at 15:00 o'clock

by

#### **Burak GÖNEN**

Master of Science in Electrical Engineering, Delft University of Technology, the Netherlands born in Elbistan, Turkey This dissertation has been approved by the promotor.

Composition of the doctoral committe:

Rector Magnificus chairperson

Prof.dr. K.A.A. Makinwa Delft University of Technology, promotor

Independent members:

Prof.dr.ir. K. Bult Delft University of Technology

Prof.dr. S. Pavan Indian Institute of Technology, Madras, India

Dr. Y. Chae Yonsei University, Korea

Dr. P. J. A. Harpe Eindhoven University of Technology

Dr. D. Hall University of California, San Diego

Dr.ir. R.H.M. van Veldhoven NXP Semiconductors, the Netherlands

Prof.dr. C. Vaucher Delft University of Technology, reserve member

This research was funded by NXP Semiconductors.

Copyright ©2021 by Burak Gönen.

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without written permission of the author.

ISBN 978-94-6384-229-7

Printed by Proefschriftmaken in the Netherlands.

#### **Summary**

Analog-to-digital converters (ADCs) are an indispensable part of the digital age we are living in, as they form the interface between physical reality and virtual reality. Higher ADC energy efficiency is the dominant focus of ADC design research due to the high impact of ADC energy consumption to total energy consumption of the systems they are employed in. The energy consumption of an ADC increases with its resolution within a given signal bandwidth, which makes the efficiency of high-resolution ADCs even more important. Although the average energy efficiency of ADCs improved orders of magnitude in the last two decades, the high energy consumption of high-resolution ADCs was still restrictive for a large range of applications. This thesis investigates how the zoom ADC architecture can achieve both high resolution and high energy efficiency.

In Chapter 1, an introduction to the thesis is given and the importance of ADC energy efficiency is discussed. First an overview of the developments in ADC energy efficiency in the past two decades is presented. The zoom ADC, which was in its infancy when this thesis work started, is then identified as a suitable architecture for improving high-resolution ADC energy efficiency. This is followed by a detailed motivation of this thesis work.

Delta-sigma modulators (DSM) are the backbone of most high-resolution ADCs. For this reason, the fundamentals of their energy efficiency are analyzed in Chapter 2. In this deep dive into the lower limits of DSM energy consumption, the impact of noise and nonlinearity on both discrete-time (DT) and continuous-time (CT) DSMs are considered. This analysis yielded several interesting findings. Firstly, it is found that efficient amplifiers should be used to reduce the impact of thermal noise, especially for the first integrator of the DSMs. When efficient amplifiers are used, the circuit nonlinearity is found to be more dominant than thermal noise for both DTDSMs and CTDSMs but this is more severe for CTDSMs. Reducing the input swing of the loop-filter is shown to be the best way to reduce the impact of circuit nonlinearity. Energy efficient architectures, such as multi-bit DSMs, FIR-DAC DSMs and the zoom ADC, are observed to be doing exactly this. The properties of these architectures and a brief comparison of them are given.

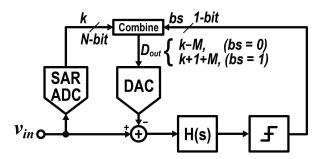

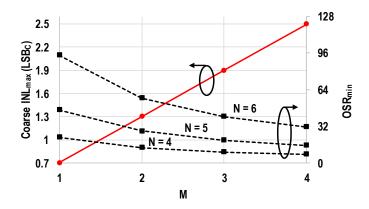

Chapter 3 presents the system-level design of zoom ADCs. Firstly, the zoom ADC architecture is explained. This is followed by an in-depth analysis of the static and dynamic error sources. The static error sources are mostly related to the unit element mismatch of the DAC of a zoom ADC, the use of over-ranging in combination with dynamic element matching (DEM) techniques is proposed. Furthermore, the quantization noise leakage of the coarse ADC into the output of a zoom ADC is discussed and digital and analog methods to alleviate this are proposed. The dynamic errors mainly result from the delay between the coarse and fine ADC sampling moments, the dynamic zoom ADC architecture making use of a coarse ADC running in tandem with its fine DSM is introduced. The impact of the sampling rate of the coarse ADC in a dynamic zoom ADC is investigated.

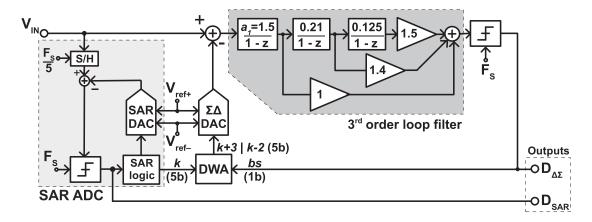

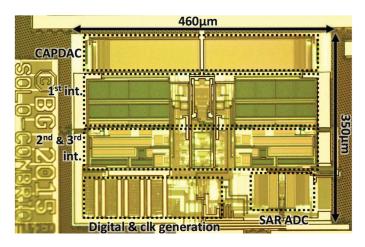

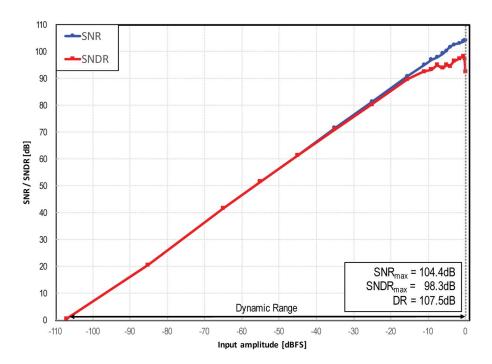

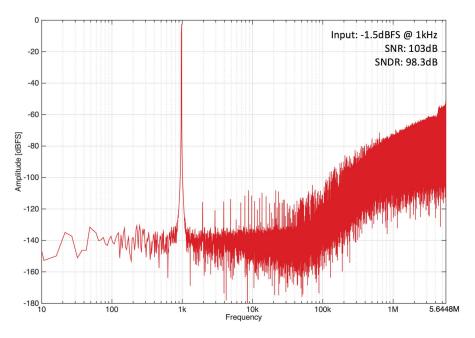

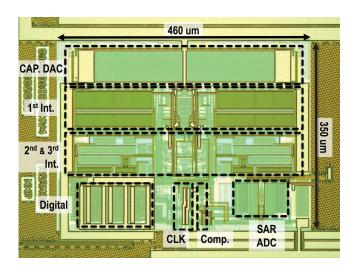

Chapter 4 discusses the design of dynamic zoom ADCs for audio applications. The input signal bandwidth of the incremental zoom ADCs before this implementation were limited to Hz range because of the sequential operation of their coarse ADC and fine DSM. The coarse and fine converters of the dynamic zoom ADC introduced in this thesis work in tandem, making it possible to achieve kHz input signal bandwidth required for audio applications. The coarse ADC of the designs is a 5-bit synchronous successive-approximation register (SAR) ADC. This is followed by a 3<sup>rd</sup>-order feed-forward compensated 1-bit fine DTDSM. The amplifiers used in the integrators of the loop-filter are based on a dynamically biased inverter which combines auto-zeroing with biasing of the amplifier. Since this amplifier is pseudodifferential, it is prone to high common-mode signals at its input. A differential sampling scheme with high common-mode rejection is used to boost the common-mode rejection ratio (CMRR) of the ADC. A first prototype achieved 98.3 dB signal-to-distortion ratio (SNDR) and 107.5 dB dynamic range (DR) in a 20 kHz bandwidth while consuming 1.65 mW corresponding to a figure-of-merit (FOM) of 178.3 dB. A revised version of this, the second prototype, achieved 103 dB SNDR and 109 dB DR, while its power consumption dropped to 1.12 mW and its FOM increased to 181.5 dB. In terms of bandwidth, this represents a 1000fold improvement on incremental zoom ADCs, while maintaining their state-of-the-art energy efficiency.

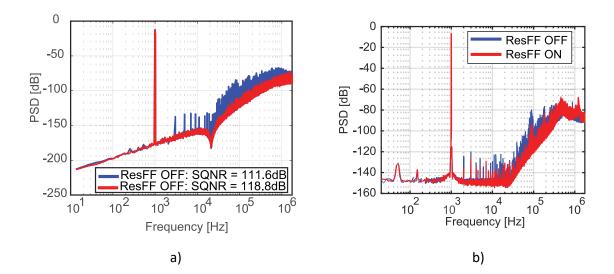

Chapter 5 describes a dynamic zoom ADC for instrumentation applications. Based on an asynchronous SAR, which allows the DSM references to be updated after every clock cycle, this zoom ADC is more robust to out-of-band interferers, and has relaxed loop filter requirements and, hence, increased overall energy efficiency. The use of the 5-bit asynchronous SAR ADC made it possible to reduce the over-ranging factor to its minimum. This resulted in not only increased signal-to-quantization-noise ratio (SQNR) but also a reduced loop-filter input swing. The reduced swing made it possible to use fully-differential current-starved inverter

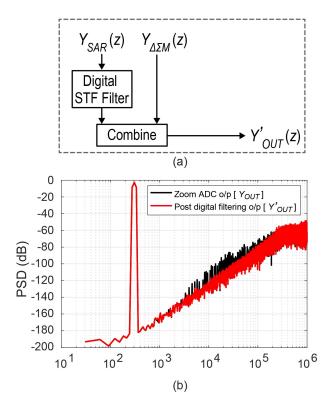

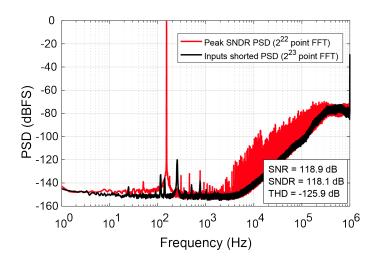

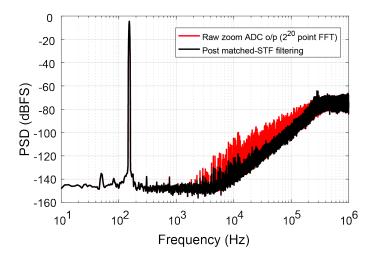

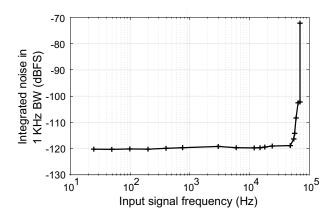

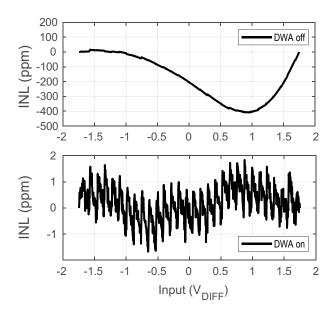

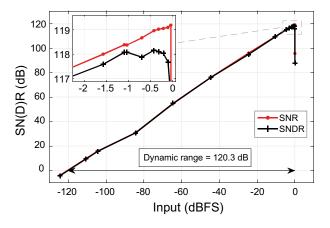

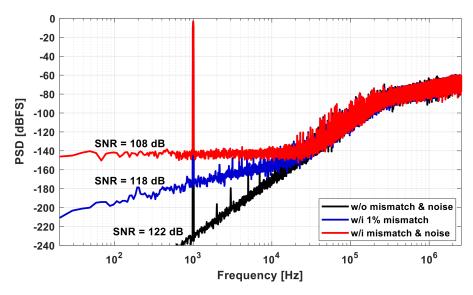

amplifiers in the loop-filter, which are much simpler compared to the dynamically-biased amplifiers in the previous applications. 1/f noise and offset are reduced by use of correlated double-sampling (CDS) in the first integrator. The non-unity STF of the loop-filter is found to be the reason behind imperfect cancellation of the SAR ADC quantization error giving rise to the spectral "fuzz" seen at the previous dynamic zoom ADC implementations. This is addressed in digital, similar to multi-stage noise-shaping (MASH) ADCs. The ADC achieves a peak signal-to-noise ratio (SNR), SNDR and total harmonic distortion (THD) of 119.1, 118.1 and -125.9 dB respectively. The measured DR of the ADC is 120.3 dB and its power consumption is 280  $\mu$ W resulting in 185.8 dB FOM.

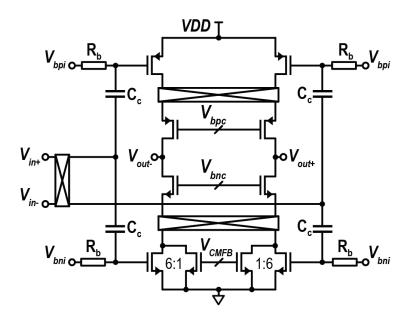

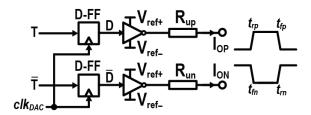

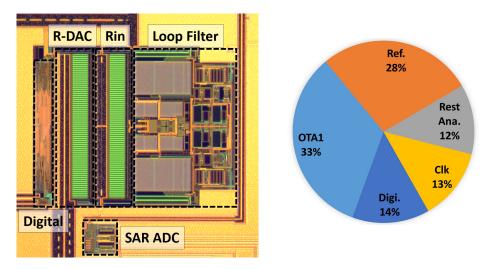

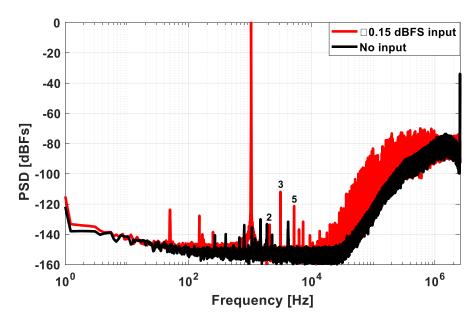

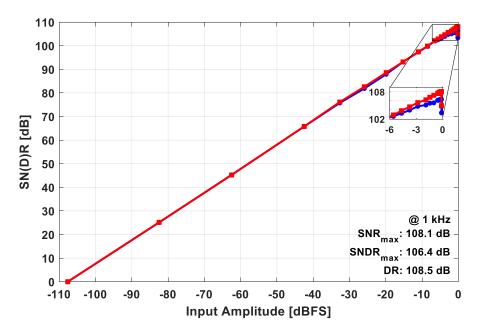

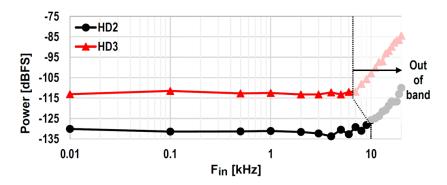

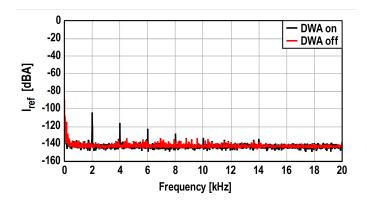

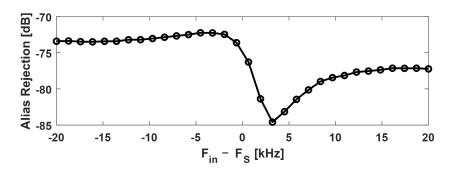

Chapter 6 presents the design of a CT zoom ADC for audio applications. It combines an asynchronous 5-bit SAR ADC with a  $3^{rd}$ -order 1-bit CTDSM. As found in Chapter 2, the amplifier linearity has a larger impact on the energy efficiency of CTDSMs. For improved energy-efficiency and linearity, its first integrator is based on a capacitively-coupled pseudo-differential inverter-based amplifier, which is more linear compared to a fully-differential amplifier. The amplifier is chopped at the sampling frequency to mitigate its 1/f noise while not resulting in chopping related artifacts. Inter-symbol-interference (ISI) in the DAC of a CTDSM is an important nonlinear error source. This is addressed by a novel ISI reduction technique based on a matched-pair layout in the resistive non-return-to-zero (NRZ) DAC. The ADC achieves 108.1 dB peak SNR, 106.4 dB peak SNDR and 108.5 dB DR in a 20 kHz bandwidth while dissipating only 618  $\mu$ W, and its FOM is 185.8 dB.

Chapter 7 summarizes the main findings of this thesis, discusses other applications of the developed techniques, and includes some proposals for future work. The circuit nonlinearity of the 1st-integrator of a high-resolution DSM is the main factor determining the energy consumption. This resulted in the observation that the key to improve the energy efficiency of a high-resolution DSM is to reduce its loop-filter's input swing. The zoom ADC is a competitive architecture achieving this while not complicating the circuit design. Unlike prior zoom ADCs based on sequential two-step conversion, which were too slow for audio applications, the dynamic zoom ADCs proposed in this thesis are suitable for digitization of kHz range audio signals by employing concurrent coarse and fine conversions.

#### **Samenvatting**

Analoog-digitaalomzetters (ADCs) zijn een onmisbaar onderdeel van het digitale tijdperk waarin we leven, omdat zij de verbinding vormen tussen de fysieke en virtuele realiteit. In onderzoek naar ADC ontwerpen overheerst de focus op grotere ADC energie-efficiëntie, vanwege de grote impact van het energieverbruik van de ADC op het totale energieverbruik van de systemen waarin zij gebruikt worden. Het energieverbruik van een ADC groeit parallel aan zijn resolutie binnen een bepaalde signaal bandbreedte. Dit maakt de efficiëntie van hoge resolutie ADCs éxtra belangrijk. Hoewel de gemiddelde energie-efficiëntie van ADCs tientallen orders verbeterd is in de afgelopen twee decennia, bleef het hoge energieverbruik van hoge resolutie ADCs limiterend voor een grote reeks aan toepassingen. Dit proefschrift onderzoekt hoe de zoom ADC architectuur zowel hoge resolutie als hoge energie-efficiëntie kan bereiken.

Hoofdstuk 1 geeft een introductie van het proefschrift en bespreekt het belang van ADC energie-efficiëntie. Allereerst wordt een overzicht gegeven van de ontwikkelingen in ADC energie-efficiëntie in de afgelopen twee decennia. De zoom ADC, die nog in de kinderschoenen stond op het moment dat het werk aan dit proefschrift begon, wordt vervolgens benoemd als een passende architectuur om de energie-efficiëntie van hoge resolutie ADCs te verbeteren. Hierop volgt een gedetailleerde motivatie voor dit proefschrift.

Delta-sigma modulators (DSM) zijn de basis van de meeste hoge resolutie ADCs. Daarom worden de grondbeginselen van hun energie-efficiëntie geanalyseerd in Hoofdstuk 2. In dit diepgravend onderzoek naar de lagere limieten van DSM energieverbruik wordt de impact van ruis en niet-lineariteit op zowel tijdsdiscrete (DT) en tijdscontinue (CT) DSMs beschouwd. Deze analyse resulteerde in verschillende interessante bevindingen. Allereerst wordt ontdekt dat efficiënte versterkers gebruikt moeten worden om de impact van thermische ruis te reduceren, vooral in de eerste integrator van de DSMs. Het blijkt dat bij gebruik van efficiënte versterkers de niet-lineariteit van het circuit dominanter is dan de thermische ruis. Dit geldt voor zowel DT DSMs en CT DSMs, maar het meest voor CT DSMs. Het reduceren van de signaalzwaai van het lusfilter wordt gepresenteerd als de beste manier om de impact van de niet-lineariteit van het circuit te reduceren. Energie-efficiënte architecturen, zoals meerdere-

bits DSMs, FIR-DAC DSMs en de zoom ADC, laten precies ditzelfde zien. Daarom volgt een uiteenzetting van de eigenschappen van deze architecturen en een korte vergelijking ervan.

Hoofdstuk 3 presenteert het ontwerp van zoom ADCs op systeemniveau. Allereerst wordt de zoom ADC architectuur uitgelegd. Dit wordt gevolgd door een diepgaande analyse van de statische en dynamische foutbronnen. De statische foutbronnen zijn vooral gerelateerd aan de mismatch in het eenheidselement van de digitaal-analogomzetter (DAC) van een zoom ADC; het gebruik van over-ranging in combinatie met dynamische matching van de elementen (DEM) wordt daarom voorgesteld. Voorts wordt de lekkage van de kwantisatieruis van de grove ADC naar de uitgang van een zoom ADC besproken en worden zowel digitale als analoge methodes voorgesteld om dit te verlichten. De dynamische fouten resulteren vooral uit de vertraging tussen de sample momenten van de grove en fijne ADC. Daarom wordt de dynamische zoom ADC architectuur geïntroduceerd, gebruikmakend van een grove ADC die in tandem loopt met zijn fijne DSM. De impact van de samplefrequentie van de grove ADC op een dynamische zoom ADC wordt onderzocht.

Hoofdstuk 4 behandelt het ontwerp van dynamische zoom ADCs voor audiotoepassingen. De bandbreedte van het ingangssignaal van de incrementele zoom ADCs vóór deze implementatie was gelimiteerd tot het hertz bereik vanwege de sequentiële operatie van hun grove ADC en fijne DSM. De grove en fijne omzetters van de dynamische zoom ADC worden in dit proefschrift in tandem geïntroduceerd, waardoor het mogelijk is om een kilohertz ingangssignaal bandbreedte te bereiken, die nodig is voor audiotoepassingen. De grove ADC in deze ontwerpen is een 5-bit synchrone successive-approximation register (SAR) ADC. Dit wordt gevolgd door een derde orde voorwaartsgekoppeld gecompenseerde 1-bit fijne DT DSM. De versterkers die worden gebruikt in de integrators van het lusfilter zijn gebaseerd op een dynamisch gevoede inverter die auto-zeroing combineert met het instellen van de versterker. Omdat de versterker pseudo-differentieel is, is het gevoelig voor hoge common-mode signalen aan zijn ingang. Een differentieel sample schema met hoge common-mode onderdrukking wordt gebruikt om de common-mode rejection ratio (CMRR) van de ADC te boosten. Een eerste prototype bereikte 98.3 dB signal-to-distortion ratio (SNDR) en 107.5 dB dynamisch bereik (DR) in een 20 kHz bandbreedte, en verbruikte 1.65 mW. Dit komt overeen met een figureof-merit (FOM) van 178.3 dB. Een aangepaste versie hiervan, het tweede prototype, bereikte 103 dB SNDR en 109 dB DR, terwijl het vermogensverbruik daalde naar 1.12 mW en zijn FOM verhoogde naar 181.5 dB. Wat betreft bandbreedte vertaalt dit zich in een 1000-maal verbetering op incrementele zoom ADCs, en tegelijkertijd behoudt het zijn 'state-of-the-art' energie-efficiëntie.

Hoofdstuk 5 beschrijft een dynamische zoom ADC voor instrumentatie toepassingen.

Gebaseerd op een asynchrone SAR, die het toestaat dat de DSM referenties vernieuwd worden na elke klok periode, is deze zoom ADC robuuster dan out-of-band omvormers, en het heeft toegeeflijke lusfilter vereisten; waardoor de totale energie-efficiëntie groter is. Het gebruik van de 5-bit asynchrone SAR ADC maakte het mogelijk om de over-ranging factor te reduceren tot zijn minimum. Dit resulteerde niet alleen in een vergroot signal-to-quantization-noise ration (SQNR), maar ook in een verminderde signaalzwaai in het lusfilter. Deze verminderde zwaai maakte het mogelijk om volledig differentiële stroom-gelimiteerde inverter-gebaseerde versterkers in het lusfilter te gebruiken. Deze zijn eenvoudiger in vergelijking met de dynamisch ingestelde versterkers in de eerdere toepassingen. 1/f ruis en offset zijn verminderd door het gebruik van gecorreleerde dubbele sampling (CDS) in de eerste integrator. De signaal transferfunctie van het lusfilter is ongelijk aan 1 en blijkt daardoor de reden te zijn voor de imperfecte onderdrukking van de kwantisatiefout in de SAR ADC, die de oorzaak blijkt voor de spectrale 'fuzz' die wordt gevonden in voorgaande dynamische zoom ADC implementaties. Dit wordt behandeld in het digitale domein, op een soortgelijke manier als multi-stage noiseshaping (MASH) ADCs. De ADC bereikt een piek signal-to-noise ratio (SNR), SNDR en total harmonische vervorming (THD) van respectievelijk 119.1, 118.1 en -125.9 dB. Het gemeten dynamische bereik van de ADC is 120.3 dB en het vermogensverbruik is 280  $\mu$ W, resulterend in 185.8 dB FOM.

Hoofdstuk 6 presenteert het ontwerp van een CT zoom ADC voor audiotoepassingen. Het combineert een asynchrone 5-bit SAR ADC met een  $3^e$  orde 1-bit CT DSM. Zoals aangetoond in Hoofdstuk 2, heeft de lineariteit van de versterkers een grotere impact op de energieefficiëntie van CT DSMs. Voor verbeterde energie-efficiëntie en lineariteit, is zijn eerste integrator gebaseerd op een capacitief gekoppelde pseudo-differentiele inverter-gebasseerde versterker, die lineairder is dan een volledig differentiele versterker. De versterker is gechopt op de sample frequentie om zijn 1/f ruis op te verwijderen, zonder te resulteren in artefacten gerelateerd aan het choppen. Inter-symbool-interferentie (ISI) in de DAC van een CTDSM is een belangrijke foutbron van niet-lineaireit. Dit wordt behandeld met een vernieuwende ISI verminderingstechniek gebaseerd op een matched-pair layout in de op weerstanden gebaseerde non-return-to-zero (NRZ) DAC. De ADC bereikt 108.1 dB piek SNR, 106.4 piek SNDR en 108.5 dB DR in een 20 kHz bandbreedte, terwijl het slechts 618  $\mu$ W verbruikt, en zijn FOM is 185.8 dB.

Hoofdstuk 7 vat de hoofdbevindingen van dit proefschrift samen, bespreekt mogelijke andere toepassingen van de ontwikkelde technieken, en bevat enkele voorstellen voor toekomstig werk. De niet-lineariteit van het circuit van de  $1^e$  integrator van een hoge resolutie DSM is de belangrijkste factor voor het vaststellen van het energieverbruik. Dit resulteerde in de ob-

servatie dat het reduceren van de signaalzwaai van het lusfilter de sleutel is tot het verbeteren van energie-efficiëntie van een hoge resolutie DSM. De zoom ADC is een competitieve architectuur die dit bereikt zonder het circuit ontwerp te compliceren. Anders dan eerdere zoom ADCs gebaseerd op sequentiële conversie in twee stappen, die te langzaam waren voor audiotoepassingen, is de dynamische zoom ADC zoals aangedragen in dit proefschrift wél geschikt voor digitalisering van kilohertz bereik audiosignalen, door opeenvolgend grove en fijne omzettingen te gebruiken.

## **Contents**

| St | ımma    | ry            |                                                                      | V     |

|----|---------|---------------|----------------------------------------------------------------------|-------|

| Sa | menv    | atting        |                                                                      | ix    |

| C  | onten   | ts            |                                                                      | xiii  |

| Li | st of l | Figures       |                                                                      | xvii  |

| Li | st of ' | <b>Fables</b> |                                                                      | xxiii |

| 1  | Intr    | oductio       | n                                                                    | 1     |

|    | 1.1     | Previo        | ous Work                                                             | 2     |

|    | 1.2     | Motiva        | ation                                                                | 3     |

|    | 1.3     | Thesis        | Organization                                                         | 4     |

|    | 1.4     | Refere        | ences                                                                | 4     |

| 2  | Ene     | rgy Effi      | ciency of High Resolution Delta-Sigma Modulators                     | 5     |

|    | 2.1     | Introd        | uction                                                               | 5     |

|    | 2.2     | Energy        | y Consumption Due to Thermal Noise                                   | 5     |

|    | 2.3     | Therm         | nal Noise and Linearity Limited Conversion Energy in Discrete-Time   |       |

|    |         | Delta-        | Sigma Modulators                                                     | 6     |

|    |         | 2.3.1         | Thermal Noise                                                        | 6     |

|    |         | 2.3.2         | Linear and Nonlinear Settling Error                                  | 7     |

|    |         | 2.3.3         | Thermal Noise and Amplifier Nonlinearity Limited Energy Efficiency   | 9     |

|    | 2.4     | Therm         | nal Noise and Linearity Limited Conversion Energy in Continuous-Time |       |

|    |         | Delta-        | Sigma Modulators                                                     | 11    |

|    |         | 2.4.1         | Thermal Noise                                                        | 11    |

|    |         | 212           | Amplifier Nonlinearity                                               | 12    |

**xiv** Contents

|   |      | 2.4.3    | Impact of Circuit Nonlinearity on Energy Efficiency                 | 12 |

|---|------|----------|---------------------------------------------------------------------|----|

|   | 2.5  | Energy   | Efficiency of the State-of-the-Art DSMs and Zoom ADCs               | 14 |

|   | 2.6  | Compa    | arison of the Energy Efficiency of High Linearity DTDSMs and CTDSMs | 16 |

|   | 2.7  | Loop F   | Filter Input Swing Reduction                                        | 19 |

|   | 2.8  | Zoom     | ADC                                                                 | 21 |

|   | 2.9  | Refere   | nces                                                                | 22 |

| 3 | The  | Zoom A   | ADC                                                                 | 25 |

|   | 3.1  | Zoom     | ADC Architecture                                                    | 26 |

|   | 3.2  | Static 1 | Errors                                                              | 27 |

|   |      | 3.2.1    | Over-ranging                                                        | 27 |

|   |      | 3.2.2    | Gain Error and STF                                                  | 29 |

|   |      | 3.2.3    | DAC Mismatch Errors and Dynamic Element Matching                    | 31 |

|   |      | 3.2.4    | Non-unity STF                                                       | 33 |

|   | 3.3  | Dynan    | nic Errors                                                          | 37 |

|   | 3.4  | Refere   | nces                                                                | 41 |

| 4 | A Di | iscrete- | Γime Dynamic Zoom ADC for Audio Applications                        | 45 |

|   | 4.1  | Dynan    | nic Zoom ADC                                                        | 45 |

|   | 4.2  | System   | n Level Design                                                      | 46 |

|   |      | 4.2.1    | Coarse Resolution, Bandwidth, and Over-ranging                      | 46 |

|   |      | 4.2.2    | DSM                                                                 | 47 |

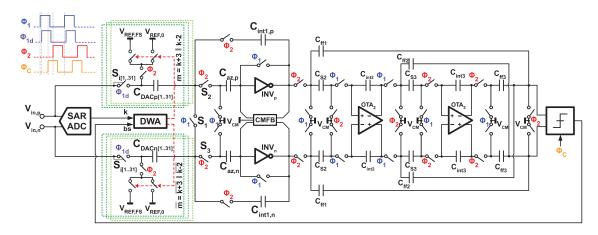

|   | 4.3  | Circuit  | Design                                                              | 48 |

|   |      | 4.3.1    | DAC                                                                 | 49 |

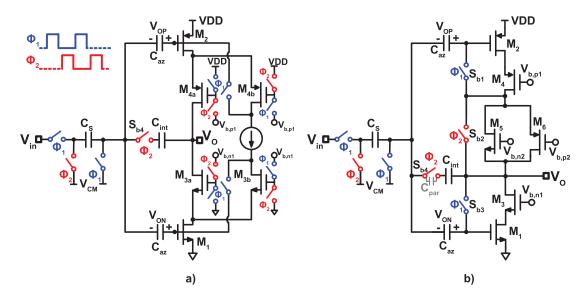

|   |      | 4.3.2    | Loop Filter Integrators                                             | 50 |

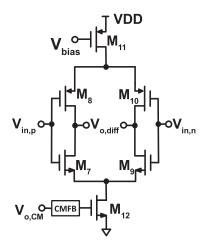

|   |      | 4.3.3    | SAR ADC                                                             | 52 |

|   | 4.4  | Measu    | rement Results of Prototype 1                                       | 53 |

|   | 4.5  | Measu    | rement Results of Prototype 2                                       | 56 |

|   | 4.6  | Refere   | nces                                                                | 59 |

| 5 | A Di | iscrete- | Time Zoom ADC for Instrumentation Applications                      | 61 |

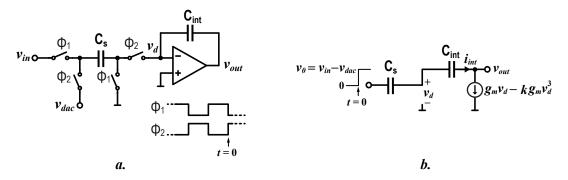

|   | 5.1  | Zoom     | ADC with Asynchronous SAR ADC                                       | 61 |

|   |      | 5.1.1    | Maximum Input Frequency and Over-ranging                            | 62 |

|   |      | 5.1.2    | Loop Filter Order, Coarse Resolution and OSR                        | 63 |

|   |      | 5.1.3    | Linearity Relaxation and Out-of-Band Fuzz                           | 64 |

|   |      | 5.1.4    | SAR ADC Requirements                                                | 66 |

Contents

|    |      | 5.1.5 DAC                                                | 66  |

|----|------|----------------------------------------------------------|-----|

|    | 5.2  | Implementation Details                                   | 67  |

|    |      | 5.2.1 DSM                                                | 67  |

|    |      | 5.2.2 Current-Starved Inverter OTAs                      | 69  |

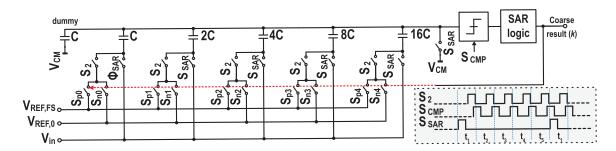

|    |      | 5.2.3 5-bit Asynchronous SAR ADC                         | 70  |

|    | 5.3  | Experimental Results                                     | 71  |

|    | 5.4  | References                                               | 75  |

| 6  | A C  | ontinuous-Time Zoom ADC for Low Power Audio Applications | 77  |

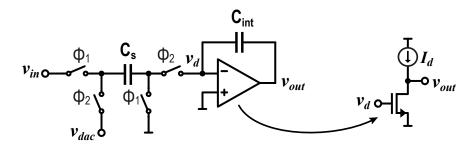

|    | 6.1  | Continuous-Time Zoom ADC                                 | 78  |

|    | 6.2  | Circuit Implementation                                   | 80  |

|    |      | 6.2.1 Loop filter                                        | 81  |

|    |      | 6.2.2 Capacitively Coupled Pseudo-Differential Amplifier | 81  |

|    |      | 6.2.3 DAC                                                | 84  |

|    |      | 6.2.4 Asynchronous SAR ADC and Alias Rejection           | 86  |

|    | 6.3  | Measurement Results                                      | 86  |

|    | 6.4  | References                                               | 91  |

| 7  | Con  | clusions                                                 | 93  |

|    | 7.1  | Main Findings                                            | 93  |

|    | 7.2  | Other Applications of This Work                          | 97  |

|    | 7.3  | Future Work                                              | 98  |

|    | 7.4  | References                                               | 99  |

| Aŗ | pend | ices                                                     | 103 |

| ٨  | Tho  | rmal Noise Limited Energy Consumption in Integrators     | 105 |

| A  | A.1  | Switched-Capacitor Integrator                            | 105 |

|    | A.1  |                                                          | 103 |

|    | ۸.2  | A.1.1 Amplifier Noise                                    |     |

|    | A.2  | Continuous-Time Integrator                               | 109 |

|    | A 2  | A.2.1 Amplifier Noise                                    | 110 |

|    | A.3  | References                                               | 112 |

| B  | Imp  | act of Amplifier Nonlinearity in Integrators             | 113 |

|    | B.1  | Continuous-Time Integrator                               | 113 |

|    | B.2  | Switched-Capacitor Integrator                            | 115 |

|    | B.3  | References                                               | 116 |

| C   | Amp     | olifier Energy Consumption                                              | 117 |

|-----|---------|-------------------------------------------------------------------------|-----|

|     | C.1     | Amplifiers in Switched-Capacitor Integrators                            | 117 |

|     | C.2     | Amplifiers in Continuous-Time Integrators                               | 119 |

|     | C.3     | References                                                              | 120 |

| D   | Line    | arity Analysis of Fully-Differential and Pseudo-Differential Amplifiers | 121 |

|     | D.1     | References                                                              | 124 |

| Ac  | know    | ledgments                                                               | 127 |

| Lis | st of I | Publications                                                            | 129 |

| Ab  | out t   | he Author                                                               | 131 |

## **List of Figures**

| 1.1  | Energy-per-conversion vs SNDR for the ADCs published in last two decades                  | 2  |

|------|-------------------------------------------------------------------------------------------|----|

| 1.2  | [1]                                                                                       | 3  |

| 1,2  | The list 200m ABC implementation [2].                                                     | 3  |

| 2.1  | A simple sample and hold                                                                  | 5  |

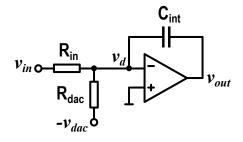

| 2.2  | DTDSM input stage with single capacitor                                                   | 6  |

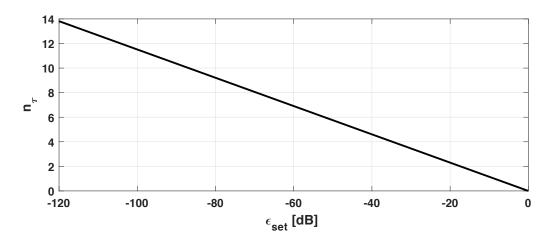

| 2.3  | $n_{\tau}$ vs relative settling error                                                     | 8  |

| 2.4  | SC integrator with single stage amplifier                                                 | 10 |

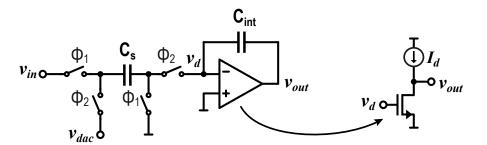

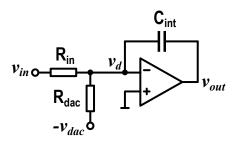

| 2.5  | CTDSM input stage with R-DAC                                                              | 11 |

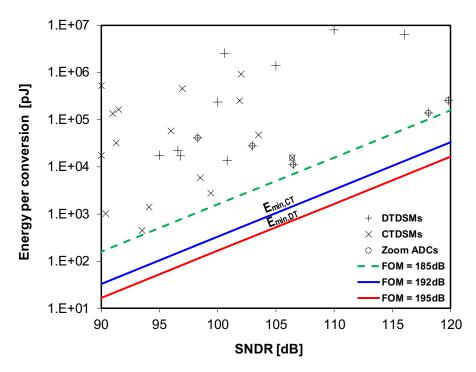

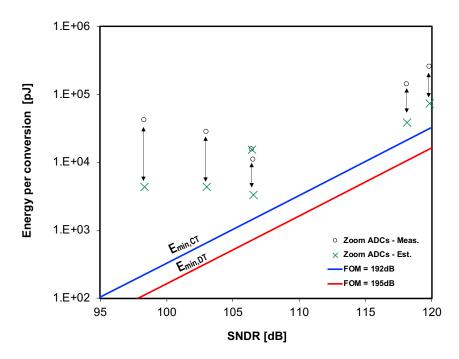

| 2.6  | SNDR vs Energy per conversion for state-of-the-art high resolution ADCs                   |    |

|      | and low energy bounds found for DTDSMs and CTDSMs in (2.19) and (2.30)                    |    |

|      | respectively [14]                                                                         | 14 |

| 2.7  | SNDR vs measured and estimated energy consumption for published zoom                      |    |

|      | ADCs                                                                                      | 16 |

| 2.8  | $g_m$ vs HD3 for the simulated DT and CT modulators. $g_m R_{in}$ and $n_\tau$ values are |    |

|      | also given.                                                                               | 18 |

| 2.9  | Estimated $E_{tot}$ of the simulated DT and the CT modulators                             | 18 |

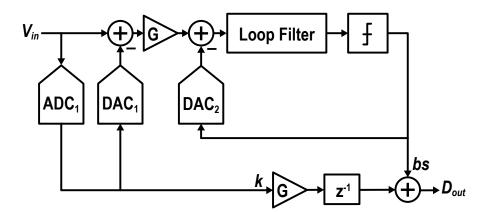

| 2.10 | A DSM with an FIR filter incorporated in its feedback                                     | 20 |

| 2.11 | Simplified block diagram of a $0 - N$ MASH ADC                                            | 20 |

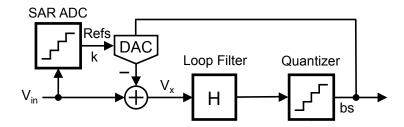

| 2.12 | Block diagram of a zoom ADC                                                               | 21 |

| 3.1  | The system level block diagram of a zoom ADC                                              | 26 |

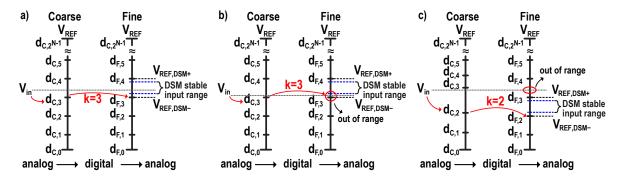

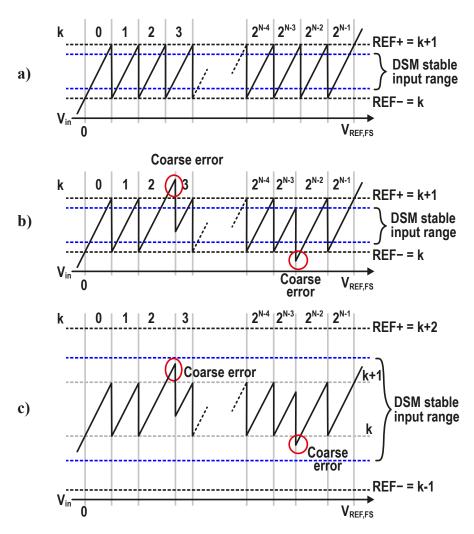

| 3.2  | Chosen quantization levels and references of the fine DSM when the coarse                 |    |

|      | ADC outputs $k = 3$ . a) Ideal situation. b) $V_{in}$ is close to one of the coarse       |    |

|      | quantization levels, and outside the stable input range of the DSM. c) Different          |    |

|      | coarse ADC quantization levels cause errors in the chosen references $(k = 2)$            |    |

|      | of the DSM                                                                                | 27 |

xviii List of Figures

| 3.3  | Input of the DSM for various input voltages $V_{in}$ with a) an ideal coarse ADC      |    |

|------|---------------------------------------------------------------------------------------|----|

|      | and references chosen by the DAC, b) non-ideal coarse quantization levels             |    |

|      | yielding an error in the chosen references, c) over-ranging $(M = 1)$ causing         |    |

|      | the input value to be within the range of the chosen references                       | 28 |

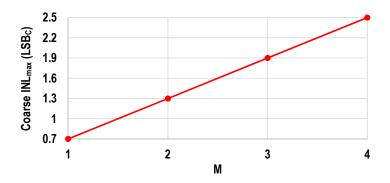

| 3.4  | Maximum INL of the coarse ADC which results in less than 10 dB SQNR                   |    |

|      | degradation for different $M$ values                                                  | 28 |

| 3.5  | System level block diagram of a $0-N$ MASH ADC                                        | 30 |

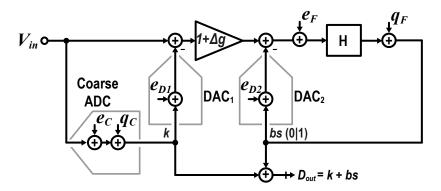

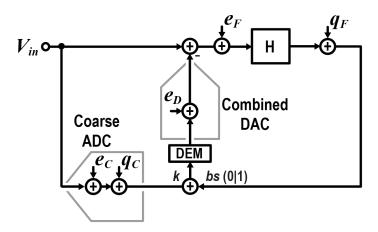

| 3.6  | System level block diagram of a zoom ADC                                              | 31 |

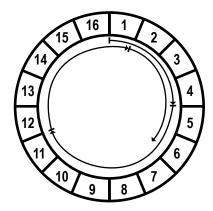

| 3.7  | Rotational unit selection of DWA for the sequence $\{4,7,6,5\}$                       | 32 |

| 3.8  | Output spectrum of a zoom ADC showing the effect of the DWA induced noise.            | 33 |

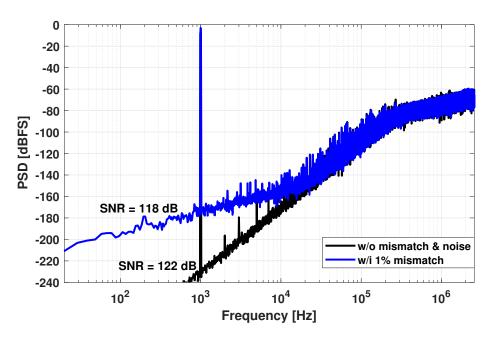

| 3.9  | a) Example of a feed-forward compensated loop filter. b) Resulting STF and            |    |

|      | NTF                                                                                   | 34 |

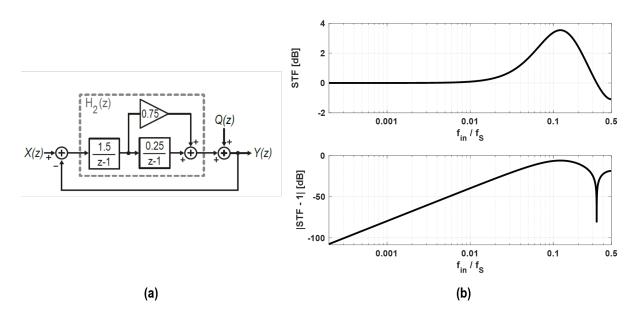

| 3.10 | a) Intuitive block diagram of the zoom ADC described in [7] ( $N = 5$ and $M =$       |    |

|      | 1). b) Spectrum at internal nodes of the loop filter and the zoom ADC's output.       | 35 |

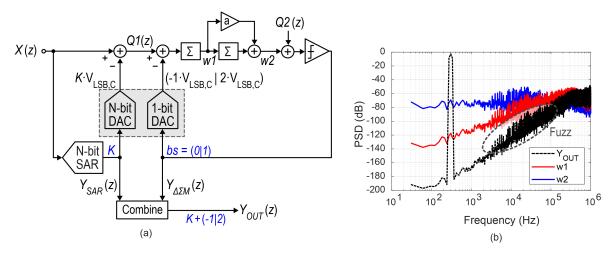

| 3.11 | a) Fuzz filtering using a digitally matched STF filter. b) The resulting zoom         |    |

|      | ADC output spectrum                                                                   | 35 |

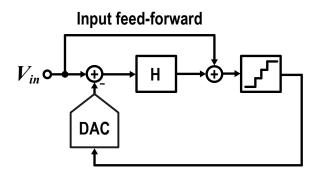

| 3.12 | General input feed-forward DSM                                                        | 36 |

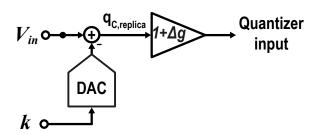

| 3.13 | Replica coarse quantization noise feed-forward path                                   | 36 |

| 3.14 | The out-of-band cancellation achieved by $q_C$ feed-forward in a) simulation, b)      |    |

|      | measurement                                                                           | 37 |

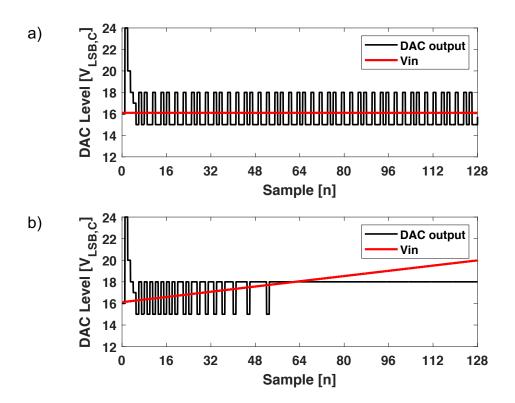

| 3.15 | Sequential zoom ADC operation in the time domain. a) Static inputs. b)                |    |

|      | Dynamic inputs                                                                        | 38 |

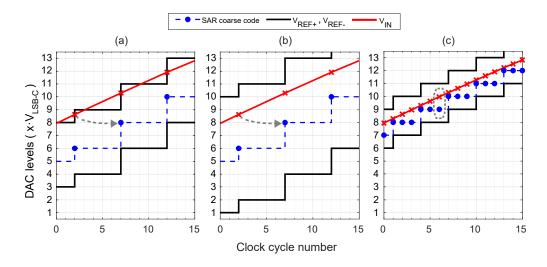

| 3.16 | Time domain operation of the dynamic zoom ADC for a fast changing input.              |    |

|      | a) Coarse code and corresponding fine-reference are updated at every 5 cycles         |    |

|      | by an 5-bit SAR ADC for a) $M = 2$ , for b) $M = 4$ . c) Fine-reference is updated    |    |

|      | every cycle by an 5-bit asynchronous SAR, with an over-ranging of $M = 1$ [7].        | 38 |

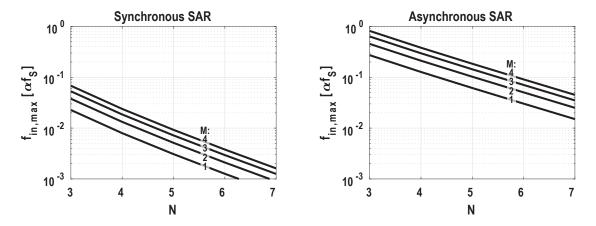

| 3.17 | $f_{in,max} [\alpha f_S]$ vs N for synchronous and asynchronous SAR ADCs with differ- |    |

|      | ent <i>M</i> values                                                                   | 40 |

| 4.1  | The system-level block diagram of the dynamic zoom ADC                                | 46 |

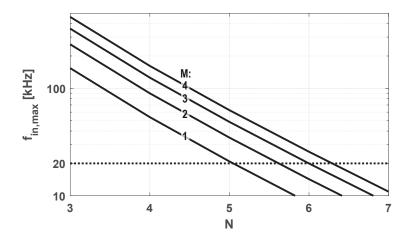

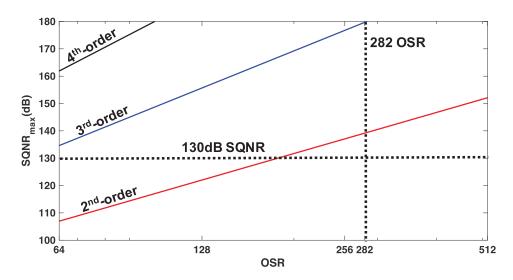

| 4.2  | $f_{in,max}$ vs N for $f_s = 11.29$ MHz and different M values                        | 47 |

| 4.3  | SQNR <sub>max</sub> of a zoom ADC with 5-bit SAR ADC, and a first-, second-, and      |    |

|      | third-order DSM versus OSR                                                            | 47 |

| 4.4  | System level block diagram of the implemented dynamic zoom ADC                        | 48 |

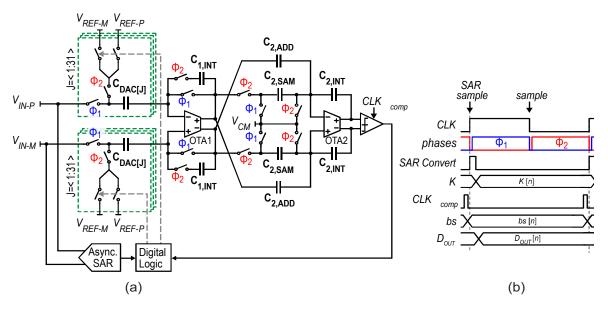

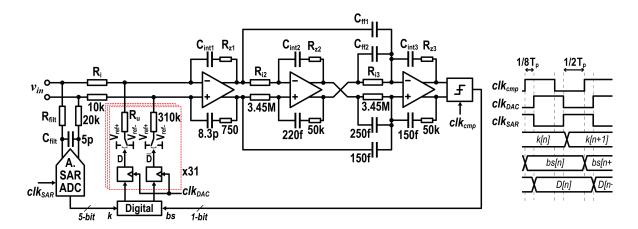

| 4.5  | Simplified schematic of the implemented dynamic zoom ADC,                             | 49 |

List of Figures xix

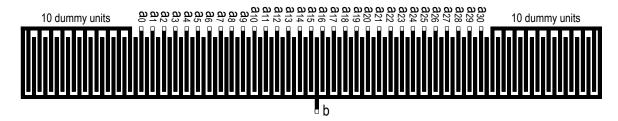

| 4.6  | Layout of the implemented capacitive DAC                                                 | 50 |

|------|------------------------------------------------------------------------------------------|----|

| 4.7  | a) Inverter-based integrator used in [3]. b) Proposed inverter-based integrator.         | 51 |

| 4.8  | Simplified schematic of OTA <sub>2</sub> and OTA <sub>3</sub>                            | 52 |

| 4.9  | Simplified schematic of the SAR ADC                                                      | 52 |

| 4.10 | Chip micrograph of prototype 1                                                           | 53 |

| 4.11 | SNR and SNDR versus input signal amplitude (1 kHz)                                       | 54 |

| 4.12 | Measured output spectrum of the zoom ADC                                                 | 54 |

| 4.13 | Chip micrograph of prototype 2                                                           | 55 |

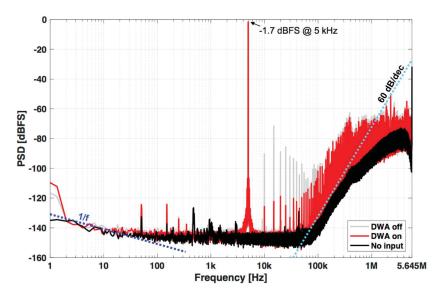

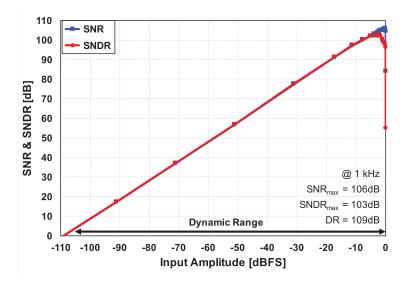

| 4.14 | Measured output spectrum of the zoom ADC with 0.9V output drivers                        | 57 |

| 4.15 | Measured SNR and SNDR versus input amplitude (DWA on)                                    | 57 |

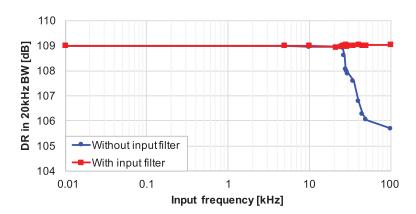

| 4.16 | DR in 20 kHz BW in the presence of in- and out-of-band full-scale inputs with            |    |

|      | and without an LPF at the input with 30 kHz corner frequency (DWA on)                    | 58 |

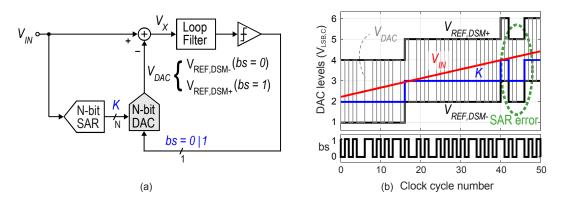

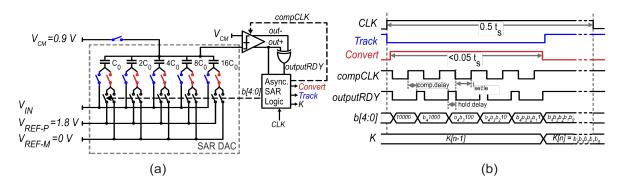

| 5.1  | a) Simplified block diagram of the dynamic zoom ADC. b) Time domain                      |    |

|      | waveforms of different signals in the zoom ADC with an over-ranging of                   |    |

|      | M=1.                                                                                     | 62 |

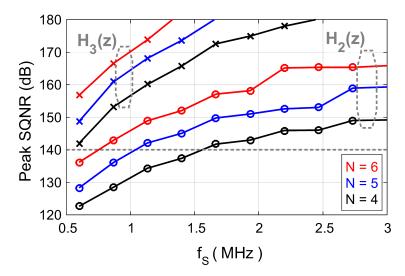

| 5.2  | SQNR vs sampling frequency $f_S$ for a $2^{nd}$ and $3^{rd}$ order loop filter employing |    |

|      | a 4,5,or 6-bit asynchronous SAR ADC as the coarse quantizer with an over-                |    |

|      | ranging of $M = 1$ on the fine-references                                                | 64 |

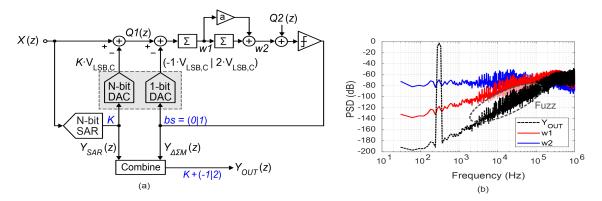

| 5.3  | a) Intuitive block diagram of the coarse-fine operation of the <i>N</i> -bit DAC. b)     |    |

|      | Spectrum at internal nodes of the loop filter and the zoom ADC's output when             |    |

|      | N = 5 and $M = 1$                                                                        | 65 |

| 5.4  | a) Fuzz filtering using a digitally matched STF filter. b) Its effect on the zoom        |    |

|      | ADC output spectrum.                                                                     | 66 |

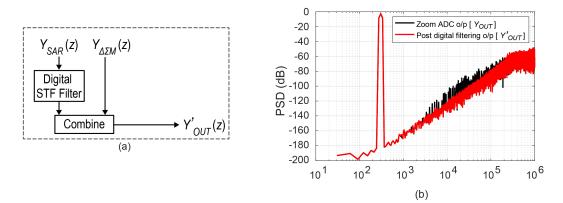

| 5.5  | A dynamic zoom ADC employing 1-bit $2^{nd}$ -order modulator with a coarse               |    |

|      | 5-bit asynchronous SAR quantizer                                                         | 67 |

| 5.6  | a) Simplified schematic of the dynamic zoom ADC. b) Timing diagram of the                |    |

|      | zoom ADC.                                                                                | 68 |

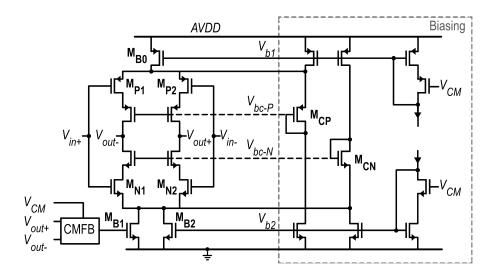

| 5.7  | Schematic of the current-starved inverter OTAs                                           | 69 |

| 5.8  | a) Simplified schematic of the asynchronous SAR ADC. b) Timing diagram                   |    |

|      | of the SAR ADC                                                                           | 70 |

| 5.9  | Die-micrograph of the prototype dynamic zoom ADC                                         | 71 |

| 5.10 | Measured output spectrum of the zoom ADC at peak SNDR (with a –0.5 dBFS                  |    |

|      | sine-wave input signal) and with inputs shorted.                                         | 71 |

| 5.11 | Fuzz filtering of the output spectrum using a digital matched STF filter                 | 72 |

**xx** List of Figures

| 5.12 | Integrated noise floor across different input frequencies with a -1.5 dBFS am-                    |     |

|------|---------------------------------------------------------------------------------------------------|-----|

|      | plitude                                                                                           | 74  |

| 5.13 | Measured INL with and without DWA                                                                 | 74  |

| 5.14 | Measured SN(D)R across input amplitude                                                            | 74  |

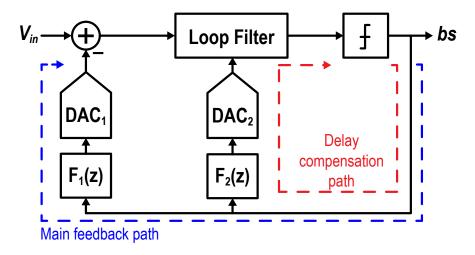

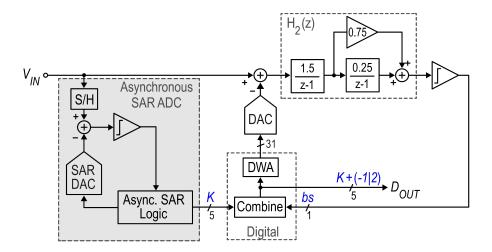

| 6.1  | Block diagram of the CT zoom ADC                                                                  | 78  |

| 6.2  | Acceptable coarse ADC INL level and minimum OSR vs over-ranging factor                            |     |

|      | (M)                                                                                               | 79  |

| 6.3  | Output spectra of the CT zoom ADC with different error sources                                    | 79  |

| 6.4  | Simplified schematic of the proposed CT zoom ADC. The units for the resis-                        |     |

|      | tors are ohms, and for the capacitors are farads                                                  | 80  |

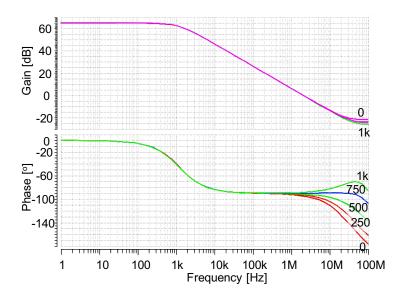

| 6.5  | Gain and phase of the 1 <sup>st</sup> -integrator with $g_m = 2.5$ mS and $C_{int1} = 8.3$ pF for |     |

|      | various $R_{z1}$ values (0 $\Omega$ to 1 $k\Omega$ )                                              | 82  |

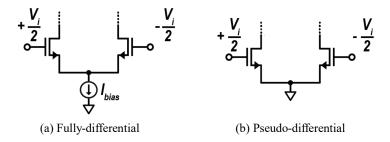

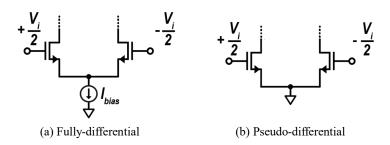

| 6.6  | Fully-differential (a) and pseudo-differential (b) amplifiers                                     | 83  |

| 6.7  | Nonlinear components of $I_{out}$ for fully-differential and pseudo-differential am-              |     |

|      | plifiers                                                                                          | 83  |

| 6.8  | Simplified schematic of the proposed amplifier                                                    | 84  |

| 6.9  | $I_{DAC}$ and $I_{OTA}$ for NRZ and RZ DACs                                                       | 85  |

| 6.10 | Simplified schematic of an R-DAC cell                                                             | 86  |

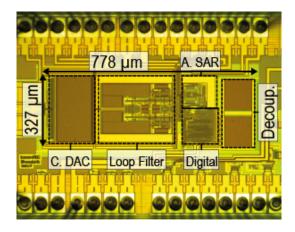

| 6.11 | Chip photograph and power breakdown                                                               | 87  |

| 6.12 | Measured output spectrum (-0.15 dBFS input signal at 1 kHz, and no signal.                        |     |

|      | 2 <sup>23</sup> points 8 average with Hanning window)                                             | 88  |

| 6.13 | Measured SNR and SNDR across input amplitude                                                      | 89  |

| 6.14 | HD2 and HD3 across input frequency                                                                | 89  |

| 6.15 | Measured I <sub>ref</sub> power spectrum for DWA on and off                                       | 89  |

| 6.16 | Measured alias rejection of the CT zoom ADC around $f_s$                                          | 90  |

| 7.1  | Energy-per-conversion vs SNDR for the ADCs published in last two decades                          |     |

|      | (Based on the data presented in [15])                                                             | 95  |

| A.1  | A simple sample and hold                                                                          | 105 |

| A.2  | DTDSM input stage with single capacitor                                                           | 107 |

| A.3  | Single transistor amplifier                                                                       | 107 |

| A.4  | CTDSM input stage with R-DAC                                                                      | 110 |

| B.1  | The CT integrator                                                                                 | 113 |

List of Figures xxi

| B.2 | a) The SC integrator. b) The small signal equivalent during the integration              |     |

|-----|------------------------------------------------------------------------------------------|-----|

|     | phase $(\Phi_2)$                                                                         | 115 |

| C.1 | SC integrator with single stage amplifier                                                | 118 |

| D.1 | Fully-differential (a) and pseudo-differential (b) amplifiers                            | 121 |

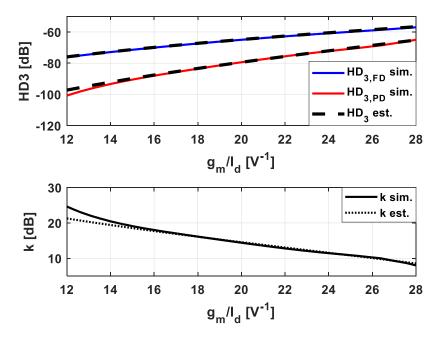

| D.2 | HD3 and $k$ vs $g_m/I_D$ for pseudo-differential and fully-differential input pairs      |     |

|     | $(L = 0.7 \mu m)$                                                                        | 123 |

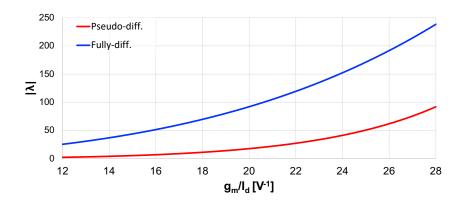

| D.3 | Calculated $ \lambda $ vs $g_m/I_D$ for pseudo-differential and fully-differential input |     |

|     | pairs (L = $0.7\mu$ m)                                                                   | 124 |

## **List of Tables**

| 4.1 | Performance summary and comparison for prototype 1    | 55 |

|-----|-------------------------------------------------------|----|

| 4.2 | Performance summary and comparison for prototype 2    | 58 |

| 5.1 | Performance summary and comparison with previous work | 73 |

| 6.1 | Performance summary and comparison with previous work | 90 |

| 7.1 | Comparison of state-of-the-art high resolution ADCs   | 96 |

## **Chapter 1**

#### Introduction

We are living in a digital age. But since the real world remains stubbornly analog, techniques to efficiently digitize physical quantities such as sound, color, light intensity, temperature, and humidity are essential. This usually involves the use of a sensor that performs a first conversion of such quantities into analog signals such as voltage, current, and charge. This is then followed by an analog to digital conversion. Analog-to-digital converters (ADCs) are thus an indispensable part of our digital age, as they form the interface between physical reality and virtual reality.

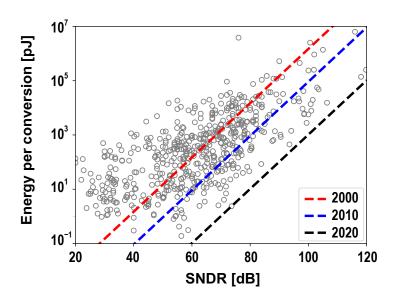

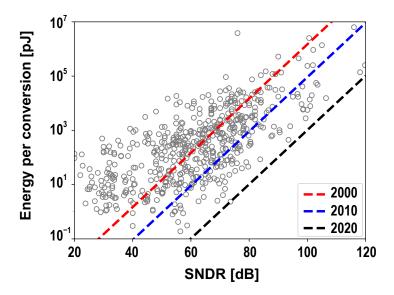

Over the last few decades, there has been an enormous improvement in ADC energy efficiency. Based on the data presented in [1], the energy-per-conversion ( $E_{conv}$ ) vs signal-to-noise and distortion ratio (SNDR) of ADCs published in the last two decades is shown in Fig. 1.1. The lines representing the lowest  $E_{conv}$  for each decade are also shown, showing that it has improved 16-fold between 2000 and 2010, and 90-fold between 2010 and 2020. This represents a total improvement of more than three orders-of-magnitude in only two decades. This has made many new applications possible, from digital cameras and high-bandwidth internet to smartphones and wearables. The popularity of these applications, in turn, has only increased the demand for ADCs with even better performance.

Although CMOS technology scaling has helped fuel this impressive progress, the biggest contributor, especially in the last decade, has been a better understanding of the architectural trade-offs inherent to ADC design. Successive-approximation (SAR) ADCs have experienced a revival, with new architectures that leverage the improved digital performance provided by CMOS scaling while minimizing hardware complexity. The result has been a rapid improvement in the energy efficiency of low to medium resolution ADCs, i.e. 30 to 70 dB SNDR, whose  $E_{conv}$  is mainly dominated by the energy associated with amplitude quantization. How-

2 Introduction

Figure 1.1: Energy-per-conversion vs SNDR for the ADCs published in last two decades [1].

ever, designing SAR ADCs with higher resolution (> 70 dB SNDR) becomes harder due to component mismatch, which requires extensive calibration, and low thermal noise requirements, which increases the energy consumption of their capacitive digital-to-analog converters (DAC) and comparators. The high resolution design space (> 70 dB SNDR) has been traditionally dominated by delta-sigma-modulators (DSMs), due to their ability to trade-off resolution for speed and thus decouple the energy associated with quantization from that required to reduce thermal noise. Although an immense amount of progress has been made in understanding DSMs, improvements in the energy efficiency of very high resolution (> 100 dB SNDR) designs has been comparatively slow. The work described in this thesis represents an attempt to investigate how a new architecture, the zoom ADC, can achieve both high resolution and high energy efficiency.

#### 1.1 Previous Work

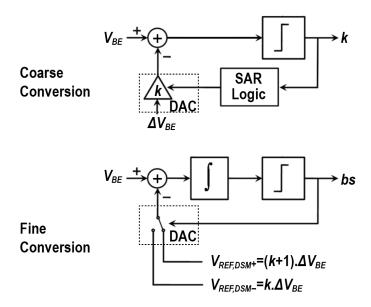

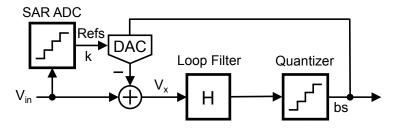

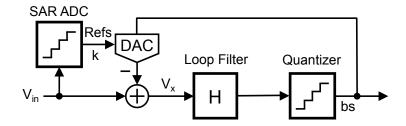

In 2010, Souri et al. described a high-resolution ADC that used a SAR ADC to perform an initial coarse conversion, followed by a DSM for a fine fine conversion as shown in Fig. 1.2 [2]. Intended for use in a temperature sensor, it exploited the fact that temperature changes are slow, and so the input signals ( $V_{BE}$  and  $\Delta V_{BE}$ ) were essentially constant during a conversion. The key idea behind this "zoom" ADC was to use the information obtained during the coarse conversion to zoom in and narrow the conversion range of the DSM. This reduces the ADC's

1.2 Motivation 3

Figure 1.2: The first zoom ADC implementation [2].

overall energy consumption, and as such the resulting temperature sensor had state-of-the-art energy efficiency. In later work by Chae et al. [3], a similarly energy-efficient stand-alone zoom ADC was described, which, at that time, represented a more than 10-fold improvement in the state-of-the-art. Shortly thereafter, a capacitance-to-digital converter (CDC) also achieved high energy efficiency by using a similar architecture [4]. Despite their high energy efficiency, however, one drawback of these designs was that they were only suitable for the digitization of quasi-static signals (< 20 Hz bandwidth).

#### 1.2 Motivation

In 2014, when this thesis work started, the main goal was to overcome the bandwidth limitations of zoom ADCs while maintaining their excellent energy efficiency. As a natural first step, the aim was to improve the input signal bandwidth to kHz range. This drove an exploration of the architectural trade-offs inherent to zoom ADCs and resulted in the dynamic zoom ADC architecture (Chapter 3).

Improving the energy efficiency of very high-resolution ADCs represents a challenge due to their low thermal noise and high linearity requirements. At first sight, noise and linearity may seem to be orthogonal specifications. However, ADC designers often observe a trade-off between them, whose exact nature is concealed by architectural complexity. The zoom ADC, due to its architectural simplicity and flexibility, presents an opportunity to understand

4 Introduction

the trade-off between noise and linearity. This motivated the choice of very high-resolution applications such as audio and instrumentation for the ADC designs described in this thesis (Chapter 4-6).

#### 1.3 Thesis Organization

In Chapter 2, the energy efficiency limits of high-resolution DSMs, for both discrete-time and continuous-time architectures are analyzed. In Chapter 3, the system-level design trade-offs of zoom ADCs are discussed. The rest of the thesis is divided into two parts. In Chapters 4 and 5, two dynamic zoom ADC designs based on discrete-time delta-sigma modulators (DTDSM) are presented: the former intended for audio applications, and the latter for instrumentation applications. The audio design was the first dynamic zoom ADC, and it allowed the various system-level trade-offs to be explored and proven in silicon. Using the findings from this first design, the second design then achieved both improved energy efficiency and linearity. In Chapter 6, a dynamic zoom ADC based on a continuous-time delta-sigma modulator (CTDSM) is presented. Compared to the previous designs, the use of a continuous-time DSM presents extra design challenges. These are explained and the methods to tackle them are discussed in depth. Chapter 7 then concludes this thesis, underlining its contributions and suggesting some future work.

#### 1.4 References

- [1] B. Murmann, *ADC performance survey 1997-2020*. [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html.

- [2] K. Souri, M. Kashmiri, and K. Makinwa, "A CMOS temperature sensor with an energy-efficient zoom ADC and an inaccuracy of  $\pm 0.25$ °C (3 $\sigma$ ) from -40°C to 125," in *Dig. Tech. Papers ISSCC*, Feb. 2010, pp. 310–311.

- [3] Y. Chae, K. Souri, and K. A. A. Makinwa, "A 6.3  $\mu$ W 20 bit incremental zoom-ADC with 6 ppm INL and 1  $\mu$ V offset," *IEEE Journal of Solid-State Circuits*, vol. 48, no. 12, pp. 3019–3027, Dec. 2013.

- [4] S. Oh, W. Jung, K. Yang, D. Blaauw, and D. Sylvester, "15.4b incremental sigma-delta capacitance-to-digital converter with zoom-in 9b asynchronous SAR," in *Proc. Symp. VLSI Circuits*, Jun. 2014, pp. 1–2.

## Chapter 2

## **Energy Efficiency of High Resolution Delta-Sigma Modulators**

#### 2.1 Introduction

As discussed in Chapter 1, high-resolution ADCs are often thermal noise limited. Thus it is important to understand how the presence of thermal noise limits the amount of energy consumed per conversion. In real circuits, energy is also consumed to overcome other error sources such as settling inaccuracy and circuit nonlinearity. In this chapter, the impact of thermal noise, settling inaccuracy and circuit nonlinearity on ADC energy efficiency will be analyzed.

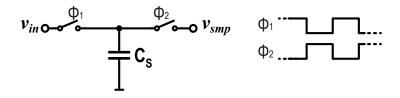

#### 2.2 Energy Consumption Due to Thermal Noise

Although there is no universally accepted lower limit of ADC energy consumption, a physical lower limit of the required energy to overcome thermal noise can be found. An ADC can be

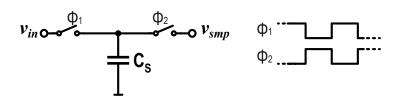

Figure 2.1: A simple sample and hold.

modelled as a simple sample-and-hold, as in Fig. 2.1. Its resolution, expressed as signal-to-noise ratio (SNR), will then be limited by the sampled noise, which is known to be  $\frac{kT}{C_s}$ . The energy required to drive the sample and hold with a certain SNR can then be considered to be a lower limit for the ADC conversion energy,  $E_{min}$ . From the analysis in Appendix A, this is found to be:

$$E_{min} = kT \text{ SNR} \tag{2.1}$$

This result describes the energy required to sample the signal, but does not account for the energy needed to quantize its amplitude.

#### 2.3 Thermal Noise and Linearity Limited Conversion Energy in Discrete-Time Delta-Sigma Modulators

#### 2.3.1 Thermal Noise

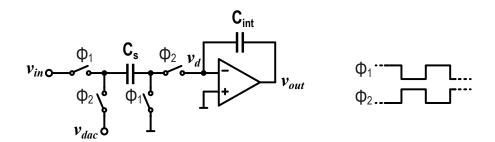

The energy consumed per conversion by a typical first stage of a DTDSM in which the sampling capacitor is also used to implement its feedback DAC as shown in Fig. 2.2 is found in Appendix A as:

$$E_{min,DT} = 4kT \text{ SNR}. (2.2)$$

In (2.2), the amplifier was assumed to be noiseless. In reality, all amplifiers exhibit thermal and 1/f noise  $^1$ . As found in Appendix A, the energy consumed in one conversion period considering the amplifier thermal noise is:

Figure 2.2: DTDSM input stage with single capacitor.

$<sup>^{1}1/</sup>f$  noise may be dominant in low bandwidth high resolution ADCs. This can be alleviated by the use of dynamic techniques such as auto-zeroing or chopping. Thus, 1/f noise will be ignored in the noise related analyses.

$$E_{th,DT} = 2(1 + \Gamma_n)kT \text{ SNR}$$

(2.3)

where  $\Gamma_n$  is noise excess factor <sup>2</sup> expressing the efficiency of the amplifier as defined in Appendix A and explained in detail in [1]. In the case of  $\Gamma_n = 1$ , there will be no excess noise and (2.3) is equal to (2.2). A low  $\Gamma_n$  can be achieved by avoiding current sources, load resistors, and extra current branches as in the case of folded-cascode amplifiers [1].  $\Gamma_n = 1$  is obtained if all the transistors used in the amplifier are input transistors, as is the case in inverter-based amplifiers [3, 4] <sup>3</sup>. Their  $\Gamma_n$  can be reduced further by stacking [7].

#### 2.3.2 Linear and Nonlinear Settling Error

In switched-capacitor (SC) circuits the signal must settle to the level of accuracy necessary to maintain signal integrity. This is directly related to the required resolution because the sampling capacitance of the system is determined by noise requirements, as discussed in Section 2.2. The relative error within the settling time,  $t_{set}$ , can be expressed as:

$$\mathcal{E}_{set} = e^{-n_{\tau}} \tag{2.4}$$

where  $n_{\tau}$  is the ratio of  $t_{set}$  and the system time constant  $\tau$ :

$$n_{\tau} = \frac{t_{set}}{\tau}.\tag{2.5}$$

Assuming  $C_s = C_{int}$ ,  $\tau$  is:

$$\tau = \frac{C_s}{g_m} \tag{2.6}$$

where  $g_m$  is the transconductance of the amplifier, which is assumed to be single-stage.

The complete settling is achieved when the settling error is smaller than the other contributions such as thermal noise and quantization noise. This condition can be expressed as:

$$\varepsilon_{set} < \frac{1}{\sqrt{\text{SNR}}}.$$

(2.7)

Fig. 2.3 is a plot of  $n_{\tau}$  vs relative settling error. It can be seen that for high resolution, complete settling requires quite a high value of  $n_{\tau}$ . For example,  $n_{\tau} \simeq 14$  is needed to achieve 120 dB SNR. From (2.5) and (2.6),  $n_{\tau}$  is proportional to  $g_m$ . Since the capacitance value is

<sup>&</sup>lt;sup>2</sup>Note that the noise excess factor defined in [1] is different than noise efficiency factor defined in [2].

<sup>&</sup>lt;sup>3</sup>Inverter-based amplifiers using switched-capacitor biasing techniques could exhibit excess noise [5, 6].

Figure 2.3:  $n_{\tau}$  vs relative settling error.

determined by the thermal noise requirements, the only way to increase  $n_{\tau}$  is to increase  $g_m$ . This will increase the energy consumption.

Considerable energy can be saved by accepting so-called incomplete settling, i.e. using a smaller  $n_{\tau}$  than is necessary for complete settling [1, 8, 9]. Although this results in a larger  $\varepsilon_{set}$ , this will be a linear gain error if  $n_{\tau}$  is constant and  $g_m$  is linear. An integrator with incomplete settling can then be modeled as a leaky integrator, similar to an integrator with limited DC gain  $A_0$ . The gain error due to incomplete settling is given as:

$$\varepsilon_{set} \approx \frac{1}{A_0}.$$

(2.8)

As a rule of thumb, DC gain of each amplifier in a single-loop DSMs should be [10]:

$$A_0 \gtrsim \text{OSR}.$$

(2.9)

From (2.8) and (2.9)

$$\varepsilon_{set} < \frac{1}{\text{OSR}}.$$

(2.10)

Required  $n_{\tau}$  can be found by using (2.4)

$$n_{\tau} > \ln(\text{OSR}).$$

(2.11)

For example, a modulator with OSR = 128 would only need  $n_{\tau}$  = 5 as it is seen in Fig. 2.3. This can be reduced even further if the loss of gain is compensated by adjusting the feedback factor.

Another lower limit on  $n_{\tau}$  results from amplifier nonlinearity, which is mainly due to the nonlinear  $g_m$  of the input transistors. This causes both harmonic distortion and quantization noise folding and is an important limitation on SNDR [11]. Since most high-resolution DSMs are fully-differential, the most dominant nonlinearity is often third-order  $g_m$  nonlinearity, usually expressed by their third-order distortion-to-signal-ratio (HD3). The HD3 of a DTDSM with an N-bit DAC is analyzed in Appendix B and found to be:

$$HD3 = \frac{\lambda}{2} e^{-n_{\tau}} \frac{\hat{V}_{in}^2}{2^{3N-2}}$$

(2.12)

where  $\lambda$  is a third-order nonlinearity factor, and  $\hat{V}_{in}$  is the peak-to-peak amplitude of the maximum input signal. Note that a lower HD3 indicates less nonlinearity. The latter can be expressed as a fraction of the ADC's full-scale voltage reference range  $V_{FS}$ :

$$2\hat{V}_{in} = \eta_{\nu} V_{FS}. \tag{2.13}$$

Combining (2.12) and (2.13), the  $n_{\tau}$  for a desired HD3 level for a DTDSM with an N-bit DAC is found as

$$n_{\tau, \text{HD3}} = \ln\left(\frac{\lambda \, \eta_{\nu}^2 V_{FS}^2}{\text{HD3}}\right) - (3N+1) \ln 2.$$

(2.14)

Note that lowering  $n_{\tau}$  below 2 does not improve energy efficiency because of the increase in thermal noise explained in [9]. Thus,  $n_{\tau} = 2$  the optimum settling factor for highest energy efficiency when only thermal noise is considered.

## 2.3.3 Thermal Noise and Amplifier Nonlinearity Limited Energy Efficiency

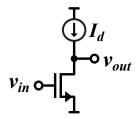

Appendix C reports the results of an analysis performed to understand the effect of  $n_{\tau}$  on the energy efficiency of DTDSM input stages implemented with a single stage-amplifier<sup>4</sup> as shown in Fig. 2.4. Assuming the settling time is half a clock period  $(t_{set} = \frac{0.5}{f_s})$ , the energy consumed by the amplifier is found to be:

$$E_{amp,DT} = 8kT \text{ SNR } (1 + \Gamma_n) \frac{V_{gt}}{\eta_v^2 \eta_c V_{dd}} n_\tau \qquad (2.15)$$

where  $\eta_v$  is voltage efficiency factor, which defines how efficiently the voltage headroom is used,  $\eta_c$  is the current efficiency factor, which defines how much of the amplifier's supply cur-

<sup>&</sup>lt;sup>4</sup>A similar analysis of switched-capacitor amplifiers is presented in [1].

Figure 2.4: SC integrator with single stage amplifier.

rent is contributing to the transconductance, and  $V_{gt}$  is the overdrive voltage of the transistor. Note that  $V_{gt}$  is equal to difference of the gate bias voltage  $(V_g)$  and the threshold voltage  $(V_{th})$  for strong inversion, but constant and equal to roughly 80 mV for weak inversion [1]. More detailed definitions of  $\eta_v$  and  $\eta_c$  are given in Appendix C.

The total energy per conversion is given by the sum of the energy consumed to drive the input and the reference given in (2.3) and the energy consumed by the amplifier given in (2.15):

$$E_{tot,DT} = 2kT \text{ SNR } (1 + \Gamma_n) \left( 1 + \frac{4V_{gt}}{\eta_v^2 \eta_c V_{dd}} n_\tau \right).$$

(2.16)

As expected, the  $\Gamma_n$  is quite dominant. An important observation is that  $\eta_v$  has a significant impact on the energy consumption. In other words, the input stage should use its voltage swing efficiently.  $\eta_c$  is also important, making current re-use structures such as inverter-based amplifiers ( $n_c = 2$ ), single current branch structures such as telescopic amplifier ( $\eta_c = 1$ ), and stacked amplifiers desirable, but amplifiers with extra current branches such as folded-cascode amplifier ( $\eta_c = 0.5$ ) undesirable.

If an inverter-based amplifier is used, and the input voltage swing is maximized ( $\eta_c = 2$ ,  $\eta_v = 1$ ), and the excess noise is minimized ( $\Gamma_n = 1$ ) (2.16) will become:

$$E_{tot,DT} = 4kT \text{ SNR } \left(1 + \frac{2V_{gt}}{V_{dd}} n_{\tau}\right). \tag{2.17}$$

As can be seen from (2.17),  $V_{gt}$  should be as small as possible, while the highest possible  $V_{dd}$  should be used.  $V_{gt}$  has its lowest and constant value, roughly 80 mV at room temperature, in weak-inversion [1, 12]. Hence, a weak-inversion operation is desired. However, this may not be possible for high clock frequencies depending on the adopted technology node [1, 12]. Furthermore,  $n_{\tau}$  should be minimized for high energy efficiency. This can be achieved by using incomplete settling and reducing  $n_{\tau}$  to the lowest possible for level required for achieving the required HD3 level as given in (2.14). Using (2.14) in (2.17) and assuming

$V_{FS} = V_{dd}$ , the total energy consumption can be expressed when  $n_{\tau}$  is determined by the HD3 requirement as:

$$E_{tot,DT} = \begin{cases} 4kT \text{ SNR } \left(1 + \frac{2V_{gt}}{V_{dd}} \left( \ln \left( \frac{\lambda \eta_{v}^{2} V_{dd}^{2}}{\text{HD3}} \right) - (3N+1) \ln 2 \right) \right) & n_{\tau,\text{HD3}} > 2\\ 4kT \text{ SNR } \left(1 + \frac{4V_{gt}}{V_{dd}} \right) & n_{\tau,\text{HD3}} \le 2. \end{cases}$$

(2.18)

Note that  $n_{\tau}=2$  is assumed as a lower limit for an optimum efficiency. Considering  $\frac{4V_{gt}}{V_{dd}}\ll 1$  when an amplifier in weak-inversion is used, the minimum energy required by the input stage of a DTDSM is found to be again:

$$E_{min\ DT} = 4kT\ SNR. \tag{2.19}$$

## 2.4 Thermal Noise and Linearity Limited Conversion Energy in Continuous-Time Delta-Sigma Modulators

#### 2.4.1 Thermal Noise

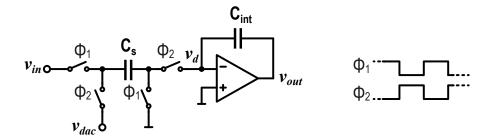

An example of a CTDSM input stage based on an ideal amplifier and a resistive DAC (R-DAC)<sup>5</sup> is shown in Fig. 2.5. The total energy consumed in one conversion period is found in Appendix A to be:

$$E_{min\ CT} = 8kT\ SNR. \tag{2.20}$$

Figure 2.5: CTDSM input stage with R-DAC.

$<sup>^5</sup>$ Current DACs (I-DAC) are also used in CTDSMs. However, I-DACs exhibit more thermal and 1/f noise [13] compared to R-DACs, making them unsuitable for high resolution DSMs. For this reason, the analysis in this thesis is limited to CTDSMs employing R-DACs.

This assumes a noiseless amplifier. In reality, the amplifier in Fig. 2.5 will exhibit thermal noise. Assuming  $R_{in} = R_{dac}$ , the total energy consumed in one conversion period to drive the input and DAC resistors is found to be:

$$E_{th,CT} = \eta_P \, 8kT \, \text{SNR}. \tag{2.21}$$

where  $\eta_P$  is an excess power consumption factor defined in Appendix A to accommodate the increased power consumption due to amplifier noise. This result does not include the energy consumed by the amplifier itself. The energy consumed by an amplifier is strongly related to its  $g_m$ , which is often chosen considering linearity requirements. Thus, in order to find the amplifier energy consumption, the relationship of  $g_m$  and the linearity should be defined.

#### 2.4.2 Amplifier Nonlinearity

Amplifier nonlinearity affects the SNDR of CTDSMs in a similar way to their DT counterparts by causing distortion and quantization noise fold-back [11]. The impact of the third-order  $g_m$  nonlinearity on the HD3 level for a CTDSM with an N-bit quantizer is found in Appendix B as:

$$HD3 = \frac{\lambda}{2^{3N-1} (2 + g_m R_{in})^3} \eta_v^2 V_{FS}^2$$

(2.22)

where  $\lambda$  is a third-order nonlinearity factor,  $\eta_v$  is voltage efficiency factor, and  $g_m R_{in}$  is an important design parameter that defines the linearity of the input stage shown in Fig. 2.5 similar to  $n_{\tau}$  for an SC input stage. For a given HD3 level,  $g_m R_{in}$  can be found by using (2.22) as:

$$g_m R_{in} = \frac{1}{2^N} \sqrt[3]{\frac{2\lambda \eta_v^2 V_{FS}^2}{\text{HD3}}} - 2.$$

(2.23)

### 2.4.3 Impact of Circuit Nonlinearity on Energy Efficiency

The power consumption of the single-stage OTA in Fig. 2.5 is dependent on  $g_m$ , which is often determined by linearity requirements for high resolution designs. The energy consumed by the amplifier in Fig. 2.5 found in Appendix C to be:

$$E_{amp,CT} = \frac{16kT \text{ SNR } V_{gt}(g_m R_{in} + 2\Gamma_n)}{\eta_v^2 \eta_c V_{dd}}.$$

(2.24)

The total energy consumption  $E_{tot,CT}$  is the sum of  $E_{th,CT}$  from (2.21) and  $E_{amp,CT}$  from (2.24):

$$E_{tot,CT} = 8kT \text{ SNR}\left(\eta_P + \frac{2V_{gt}}{\eta_v^2 \eta_c V_{dd}} (g_m R_{in} + 2\Gamma_n)\right). \tag{2.25}$$

$\eta_P$  is defined in Appendix A as:

$$\eta_P = 1 + \frac{2\Gamma_n}{g_m R_{in}} \tag{2.26}$$

Using (2.26) in (2.25):

$$E_{tot,CT} = 8kT \text{ SNR} \left( 1 + \frac{2\Gamma_n}{g_m R_{in}} + \frac{2V_{gt}}{\eta_v^2 \eta_c V_{dd}} (g_m R_{in} + 2\Gamma_n) \right). \tag{2.27}$$

It can be seen from (2.27) that there is an optimum  $g_m R_{in}$  which result in minimum  $E_{tot,CT}$ . The  $\Gamma_n$  is quite dominant as expected. The  $\frac{V_{gt}}{\eta_v^2 \eta_c V_{dd}}$  part again appears, similar to (2.16).

If an inverter-based amplifier is used ( $\eta_c = 2$ ), and the input voltage swing is maximized ( $\eta_v = 1$ ), and the excess noise is minimized ( $\Gamma_n = 1$ ), (2.25) becomes:

$$E_{tot,CT} = 8kT \text{ SNR} (g_m R_{in} + 2) \left( \frac{1}{g_m R_{in}} + \frac{V_{gt}}{V_{dd}} \right)$$

(2.28)

The optimum  $g_m R_{in}$  is then found as:

$$g_m R_{in} = \sqrt{\frac{2V_{dd}}{V_{gt}}}. (2.29)$$

$g_m R_{in}$  should be chosen according to (2.29) for the lowest  $E_{tot,CT}$ . However,  $g_m R_{in}$  is often defined by linearity requirements as expressed in (2.23) for high resolution and high linearity CTDSMs as determined in Section 2.4.2. This is the main source of excess energy consumption in such CTDSMs.

The minimum energy required for a CTDSM can then be found by using (2.29) in (2.28) and assuming  $\frac{V_{gt}}{V_{dd}} \ll 1$ . The result is again:

$$E_{min,CT} = 8kT \text{ SNR} \tag{2.30}$$

which is equal to (2.21) for  $\eta_P = 1$ . The energy consumption when  $g_m R_{in}$  is determined by linearity requirements, which can be defined by a certain HD3 level, is found by using (2.23) in (2.28), and assuming  $V_{FS} = V_{dd}$  to be:

$$E_{tot,CT} = 8kT \text{ SNR} \left( 1 + \frac{1}{2^N} \sqrt[3]{\frac{2\lambda V_{dd}^2}{\text{HD3}}} \frac{V_{gt}}{V_{dd}} \right).$$

(2.31)

Figure 2.6: SNDR vs Energy per conversion for state-of-the-art high resolution ADCs and low energy bounds found for DTDSMs and CTDSMs in (2.19) and (2.30) respectively [14].

# 2.5 Energy Efficiency of the State-of-the-Art DSMs and Zoom ADCs

In the analysis above it is found that the thermal-noise limited energy per conversion for DTDSMs and CTDSMs in (2.3) and (2.21), respectively. It is shown that the power consumption of a single-stage OTA is dependent on several factors related to amplifier efficiency such as  $\Gamma_n$ , voltage efficiency ( $\eta_v$ ), current efficiency ( $\eta_c$ ), and also  $g_m$  nonlinearity. It is observed that, even though the amplifier can be optimized at the circuit level to have high efficiency, its nonlinearity would result in excess energy consumption for high SNDR designs. When amplifier nonliearity is taken into account, the total energy per conversion of DTDSMs and CTDSMs is given by (2.18) and (2.31), respectively. These are related to HD3, which is often the dominating error source for high SNDR ADCs.

When efficient amplifiers are used, and nonlinearity is negligible, i.e. when the input swing of the loop filter is very small, the lower limits of energy consumption of DTDSMs and CTDSMs are given in (2.19) and (2.30) respectively. These lower limits, corresponding to 195 dB and 192 dB figure-of-merit (FOM)<sup>6</sup> respectively, are plotted in Fig. 2.6 together with

$<sup>^6</sup>$ FOM = DR + 10 log(Signal bandwidth / Power) is defined in [10].

the energy consumption of state-of-the-art high resolution DTDSMs and CTDSMs published between 1997-2020 [14]. Note that in Fig. 2.6, SNR is assumed to be equal to SNDR, which assumes that the distortion is negligible. In practice though, this is not the case, resulting in excess energy consumption. The trend-line of the current state of the art is equivalent to 185 dB FOM<sup>7</sup>. This means that state-of-the-art designs consume almost 10 times more energy than the theoretical minimum.

It is seen from Fig. 2.6 that zoom ADCs are at the current state-of-the-art. However, their energy consumption is still far from the theoretical minimum. As it is proposed above, this gap for a large part can be explained when taking the circuit nonlinearity into account. Since the necessary data about their design details are readily available, it to would be intresting to compare their actual energy consumption to the predicted energy consumption by using (2.18) and (2.31).

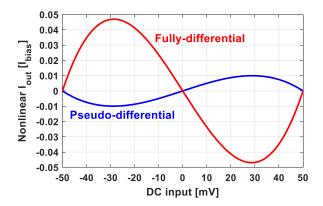

All of these state-of-the-art zoom ADCs use inverter-based current-reuse amplifiers [4–6, 15, 16], which means  $\Gamma_n = 1$  and  $\eta_c = 2$ . Most of the designs use 5-bit quantization (N = 5) and their input voltage range is optimized ( $\eta_v = 1$ ). The input transistors of the amplifiers are in weak inversion ( $V_{gt} = 80 \ mV$ ), and the  $V_{dd}$  of the process is 1.8 V. The  $g_m$  nonlinearity of amplifier input stages is analyzed in Appendix D. From this,  $\lambda = 50$  is found for an inverter-based pseudo-differential amplifier design in weak inversion for the process technology used in this thesis. By using these parameters, and assuming the noise and the harmonic distortion powers to be equal, the energy consumption can be estimated from (2.18) and (2.31) for zoom ADCs with DT and CT DSMs respectively. These are shown in Fig. 2.7 together with the actual energy consumption of the designs. Our analysis captures an important part of excess energy consumption due to nonlinearity and makes a more accurate estimation of energy consumption in spite of being limited to the energy consumed by the first stage only. This helps the designer to identify the system and circuit level trade-offs, minimize the energy consumption while not compromising the performance.

$<sup>^{7}185</sup>$  dB FOM is roughly equal to 38kT SNR.

Figure 2.7: SNDR vs measured and estimated energy consumption for published zoom ADCs.

# 2.6 Comparison of the Energy Efficiency of High Linearity DTDSMs and CTDSMs

When considering the excess energy consumption due to nonlinearity, the interesting observation can be made that the effect of  $g_m$  on linearity for DTDSMs and CTDSMs is considerably different. To demonstrate this, let us find the  $g_m$  necessary for a certain HD3 by rewriting (2.14) by using  $n_{\tau} = \frac{g_m}{2 f_s C_s}$ :

$$g_m = 2 f_s C_s \left( \ln \left( \frac{\lambda \, \eta_v^2 V_{FS}^2}{\text{HD3}} \right) - (3N+1) \ln 2 \right).$$

(2.32)

The same can be achieved for a CTDSM by using (2.23), resulting in:

$$g_m = \frac{1}{R_{in}} \left( \frac{1}{2^N} \sqrt[3]{\frac{2\lambda \, \eta_v^2 \, V_{FS}^2}{\text{HD3}}} - 2 \right). \tag{2.33}$$

As seen from (2.32) and (2.33) the relation of  $g_m$  and HD3 is logarithmic for a DTDSM while it is cubic for a CTDSM. As will be demonstrated later, this means that for high linearity requirements, a DTDSM is more energy-efficient than a CTDSM.

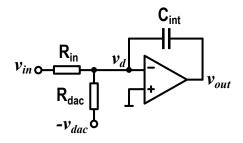

To demonstrate this,  $3^{rd}$ -order 1-bit DT and CT modulators with the input stages shown

in Fig. 2.2 and Fig. 2.5 were simulated. They were designed to have the SNR of  $108\,\mathrm{dB}$ , and  $\mathrm{OSR}=128$ . The  $g_m$  of their first stage amplifier, which had a nonlinearity factor  $\lambda=0.1^8$ , was then swept<sup>9</sup>. The input resistor of the CTDSM ( $R_{in}$ ) is found to be  $8\,\mathrm{k}\Omega$  for the full-scale input range of  $1.8\,\mathrm{V}$  by assuming  $\frac{1}{g_m}\ll R_{in}$ , and  $\Gamma_n=1$  by using the analysis in Appendix A. The sampling capacitance of the DTDSM ( $C_s$ ) is found to be  $12.2\,\mathrm{pF}$ , which is chosen by using the same analysis with the same assumptions. The integration capacitances were  $24.4\,\mathrm{pF}$  and  $12.2\,\mathrm{pF}$  for the CT and the DT modulators respectively.

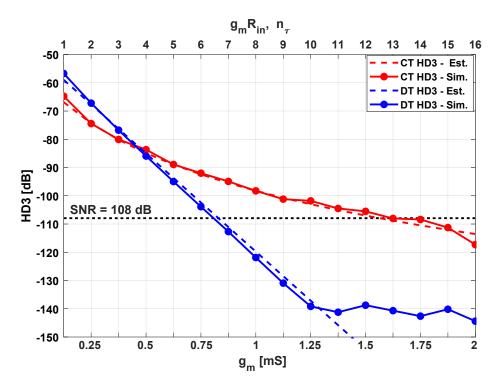

A single-tone sinusoidal input with 0.35 V amplitude at 1 kHz is applied to both modulators and the simulated HD3 results are shown in Fig. 2.8 together with the estimated values obtained from (2.12) and (2.22) for different  $g_m$  values. Note that for the same  $g_m$ , the given  $R_{in}$  and  $C_s$  values result in the same  $g_m R_{in}$  and  $n_\tau$  shown in Fig. 2.8, making it easy to compare (2.12) and (2.22). It is expected from (2.32) that the HD3 of the DTDSM will improve exponentially with increased  $g_m$ . Similarly, the HD3 of the CTDSM will improve cubically with increased  $g_m$  for a fixed  $R_{in}$  according to (2.33). From Fig. 2.8 it is clear that for high linearity levels (HD3 < -90 dB) the DTDSM requires much less  $g_m$ , hence its first stage amplifier consumes much less energy, which is in line with our prediction. The saturation of the HD3 below -140 dB for the DTDSM is due to quantization noise level at the harmonic frequency.

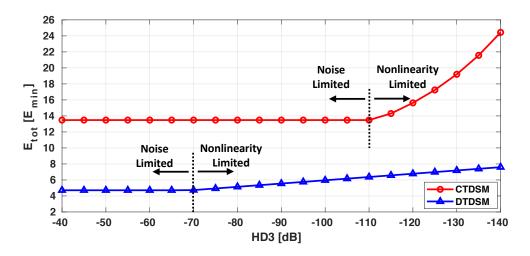

The  $n_{\tau}$  and  $g_m R_{in}$  values for a certain HD3 level can be extracted from Fig. 2.8 and used in (2.17) and (2.25) to calculate the energy per conversion for each modulator. This is illustrated in Fig. 2.9 for the simulated modulators in terms of  $E_{min}$  given in (2.1). Note that for HD3  $> -110 \,\mathrm{dB}$  the CTDSM's  $E_{tot}$  is limited to its minimum value determined in (2.29). Below this level (HD3  $< -110 \,\mathrm{dB}$ ),  $g_m R_{in}$  is increased further than its optimum value due to higher linearity requirements, hence  $E_{tot}$  is increased. The same can be seen for the DTDSM, where its  $n_{\tau}$  is limited to 2 higher than  $-70 \,\mathrm{dB}$  HD3 due to increased noise below this point as given in (2.18).

It is noted that the DTDSM always consumes less energy per conversion than the CTDSM. There are two reasons for this. Firstly, reusing the sampling capacitance as the DAC results in a much smaller loading to the amplifier to achieve the same thermal noise. This establishes the difference in  $E_{tot}$  for a high HD3 (> -110dB). Secondly, the HD3  $\propto e^{-g_m}$  for the DTDSM, and HD3  $\propto \frac{1}{g_m^3}$  for the CTDSM where the former is much stronger function than the latter. This is the reason behind the difference for low HD3 levels (< -110dB). In practice, however, the DTDSM will require much stronger input and reference drivers. Although these often

$<sup>^8</sup>$ Since the simulation setup uses ideal circuit components, a small  $\lambda$  had to be chosen to avoid convergence errors during the simulation.

<sup>&</sup>lt;sup>9</sup>The loop-filter order, SNR and OSR values are chosen to be compatible the implementations presented in Chapter 4 and Chapter 6.

Figure 2.8:  $g_m$  vs HD3 for the simulated DT and CT modulators.  $g_m R_{in}$  and  $n_\tau$  values are also given.

Figure 2.9: Estimated  $E_{tot}$  of the simulated DT and the CT modulators.

consume more energy than the first stage of a DTDSM [17], they are usually not reported [14].

## 2.7 Loop Filter Input Swing Reduction