**Delft University of Technology**

## Computation-in-Memory for Modern Applications using Emerging Technologies

Shahroodi, T.

DOI 10.4233/uuid:80a31436-92dd-4d85-89c6-e8d2e0f5d666

Publication date 2024

**Document Version** Final published version

### Citation (APA)

Shahroodi, T. (2024). *Computation-in-Memory for Modern Applications using Emerging Technologies*. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:80a31436-92dd-4d85-89c6-e8d2e0f5d666

### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

#### Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

## COMPUTATION-IN-MEMORY FOR MODERN APPLICATIONS

USING EMERGING TECHNOLOGIES

## COMPUTATION-IN-MEMORY FOR MODERN APPLICATIONS

USING EMERGING TECHNOLOGIES

# Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. dr. ir. T.H.J.J. van der Hagen, voorzitter van het College voor Promoties in het openbaar te verdedigen op dinsdag 12 March 2024 om 12:30 uur

door

# Taha Shahroodi

Master of Science in Informatik Eidgenössische Technische Hochschule (ETH) Zürich, Switzerland, geboren te Teheran, Iran. Dit proefschrift is goedgekeurd door de promotoren.

promotor: Prof. dr. ir. S. Hmadioui promotor: Dr. ir. J.S.S.M. Wong

Samenstelling promotiecommissie bestaat uit:

| Rector Magnificus,         | voorzitter                              |

|----------------------------|-----------------------------------------|

| Prof. dr. ir. S. Hamdioui, | Technische Universiteit Delft, promotor |

| Dr. ir. J.S.S.M. Wong,     | Technische Universiteit Delft, promotor |

Onafhankelijke leden:Dr. ir. S. StuijkTechnische Universiteit Eindhoven, NLProf. dr. ir. I. O'ConnorÉcole Centrale de Lyon, FranceDr. ir. T.G.R.M. van LeukenTechnische Universiteit DelftProf. dr. ir. W.A. SerdijnTechnische Universiteit DelftDr. S.D. CotofanaTechnische Universiteit DelftProf. dr. ir. P.F.A. Van MieghemTechnische Universiteit Delft

Technische Universiteit Delft, reservelid

Keywords:Computation-in-Memory, Processing-in-Memory, Bioinformatics,<br/>Computer Architecture, Hardware/Software Co-Design, MemristorPrinted by:Ipskamp Printing, the Netherlands

Front & Back: "buitenbeentje" by T. Shahroodi.

Copyright © 2024 by T. Shahroodi

ISBN 978-94-6384-534-2

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

To my loving parents, Dariush and Tahere, and the best brother ever, Emad.

# **CONTENTS**

| Su | mm   | ary     |                                                                | xiii |

|----|------|---------|----------------------------------------------------------------|------|

| Sa | men  | vatting | y .                                                            | xv   |

| Ac | knov | vledge  | ments                                                          | xvii |

| 1  | Intr | oducti  | on                                                             | 1    |

|    | 1.1  | Motiv   | ation                                                          | . 2  |

|    | 1.2  | Limita  | ations of Traditional Computing Systems                        | . 3  |

|    | 1.3  | Proble  | em Discussion                                                  | 10   |

|    | 1.4  | Soluti  | on Direction and Research Topics.                              | . 11 |

|    |      | 1.4.1   | Identify and improve Bioinformatics and Neural Network kernels |      |

|    |      |         | using CIM                                                      |      |

|    |      | 1.4.2   | Exploring emerging (memory) technologies for CIM               |      |

|    | 1.5  |         | s Statement                                                    |      |

|    | 1.6  |         | ibutions                                                       |      |

|    | 1.7  | Thesis  | s Outline                                                      | . 14 |

| 2  | Bac  | kgrour  | nd and State-of-the-Art                                        | 17   |

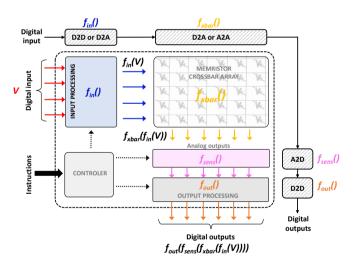

|    | 2.1  | Comp    | outation-In-Memory (CIM)                                       |      |

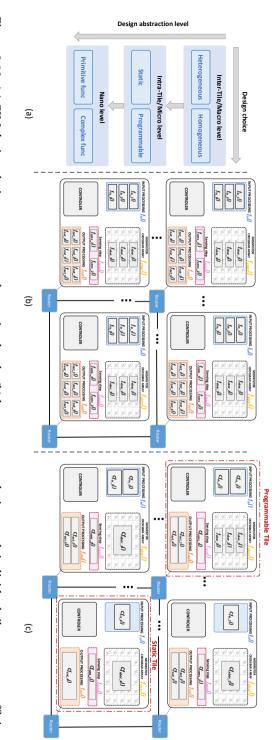

|    |      | 2.1.1   | CIM designs classification based on computation location       |      |

|    |      | 2.1.2   | Illustration of generic CIM tile                               |      |

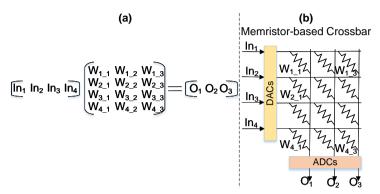

|    |      | 2.1.3   | Potential Emerging Technologies for CIM                        | 21   |

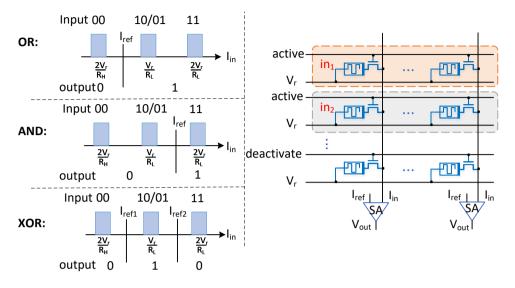

|    |      | 2.1.4   | Primitive functions in CIM classes                             | . 29 |

|    |      | 2.1.5   | Abstraction of CIM Design Choices                              | . 33 |

|    | 2.2  | Mode    | rn Applications                                                |      |

|    |      | 2.2.1   | Bioinformatics and genomics                                    | . 35 |

|    |      | 2.2.2   | Neural Network                                                 | 41   |

|    | 2.3  | State-  | of-the-Art CIM Designs and Simulators                          |      |

|    |      | 2.3.1   | General-Purpose State-of-the-Art CIM Designs and Simulators    | . 44 |

|    |      | 2.3.2   | Specific-Purpose State-of-the-Art CIM Designs and Simulators   | 46   |

| 3  |      | rdfish  |                                                                | 49   |

|    | 3.1  | Backg   | ground and Motivation                                          |      |

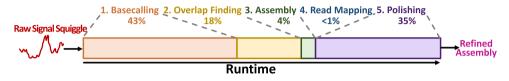

|    |      | 3.1.1   | Genome Sequencing Pipeline                                     | 51   |

|    |      | 3.1.2   | Basecalling                                                    | 52   |

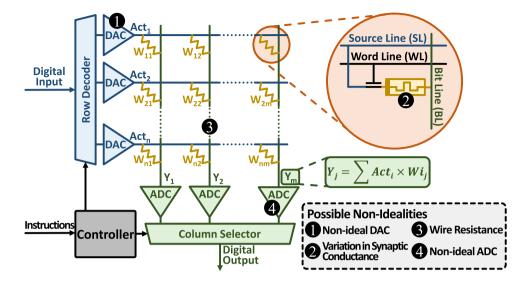

|    |      | 3.1.3   | Memristor-based CIM and Associated Non-Idealities              | 53   |

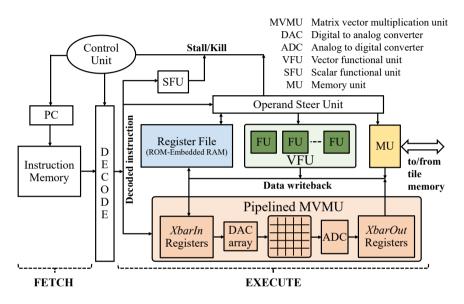

|    |      | 314     | Programmable Inference Architecture                            | 55   |

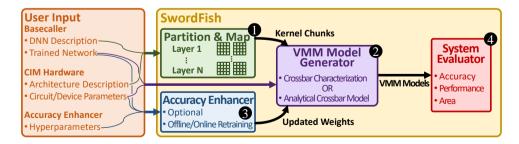

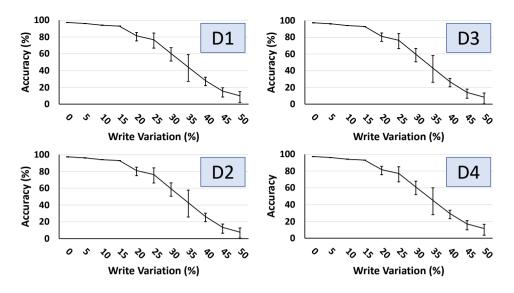

|   | 3.2  | Sword   | lfish Framework                                                |

|---|------|---------|----------------------------------------------------------------|

|   |      | 3.2.1   | Swordfish Overview                                             |

|   |      | 3.2.2   | Partition & Map                                                |

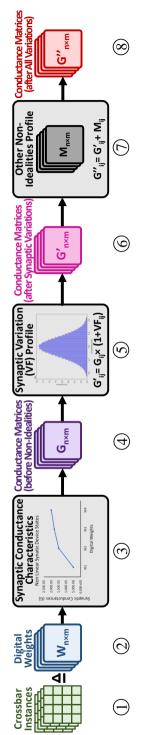

|   |      | 3.2.3   | VMM Model Generator         57                                 |

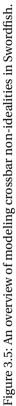

|   |      | 3.2.4   | Accuracy Enhancer                                              |

|   |      | 3.2.5   | System Evaluator                                               |

|   |      | 3.2.6   | Swordfish Evaluation Challenges                                |

|   | 3.3  | Evalu   | ation Methodology                                              |

|   |      | 3.3.1   | Implementations and Models                                     |

|   |      | 3.3.2   | Simulation Infrastructure                                      |

|   |      | 3.3.3   | Evaluation Metrics                                             |

|   |      | 3.3.4   | Datasets and Workloads                                         |

|   | 3.4  | Sword   | Ifish Evaluation                                               |

|   |      | 3.4.1   | Effect of Quantization on Accuracy without Accuracy Enhance-   |

|   |      |         | ment                                                           |

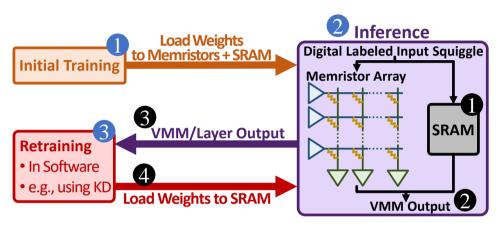

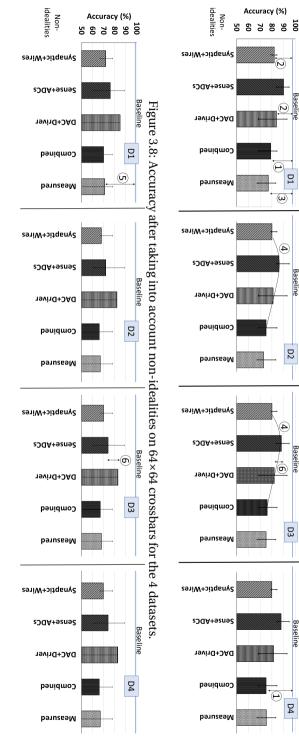

|   |      | 3.4.2   | Effect of Non-idealities on Accuracy without Accuracy Enhance- |

|   |      |         | ment                                                           |

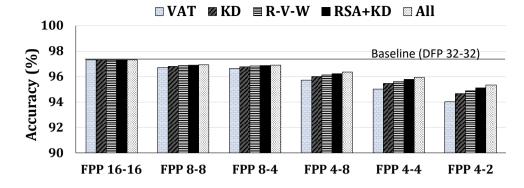

|   |      | 3.4.3   | Effect of Accuracy Enhancement on Quantized Basecallers 69     |

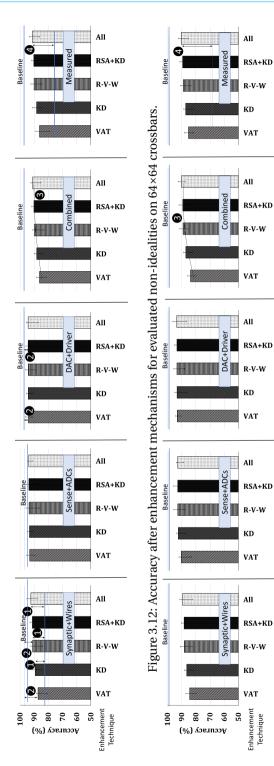

|   |      | 3.4.4   | Effect of Accuracy Enhancement on Non-idealities 70            |

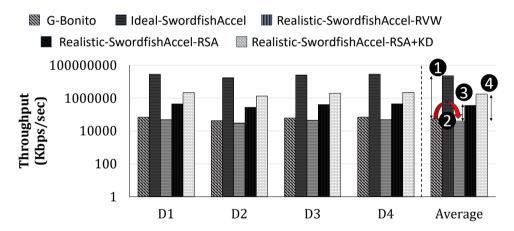

|   |      | 3.4.5   | Throughput Analysis of SwordfishAccel    74                    |

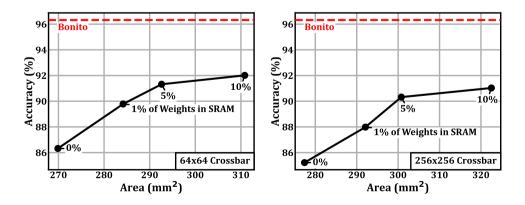

|   |      | 3.4.6   | Area vs. Accuracy Analysis                                     |

|   |      | 3.4.7   | Verdict on Realistic-SwordfishAccel                            |

|   | 3.5  | Discu   | ssions and Future Works                                        |

|   |      | 3.5.1   | Applicability of Swordfish Looking forward 76                  |

|   |      | 3.5.2   | Other DNN-based Applications                                   |

|   |      | 3.5.3   | Better Accuracy Enhancement Techniques.    77                  |

|   | 3.6  | Concl   | usion                                                          |

| 4 | Rati | tlesnak | zejake 79                                                      |

|   | 4.1  |         | sal and Architecture                                           |

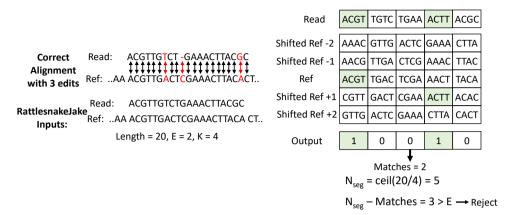

|   |      | 4.1.1   | RattlesnakeJake's Algorithm    81                              |

|   |      | 4.1.2   | RattlesnakeJake's Architecture                                 |

|   |      | 4.1.3   | RattlesnakeJake Algorithm to Hardware Mapping                  |

|   | 4.2  | Evalu   | ations                                                         |

|   |      | 4.2.1   | Evaluation Methodology                                         |

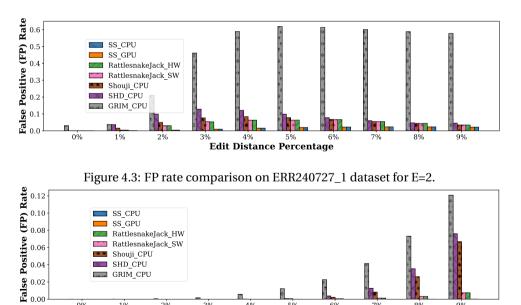

|   |      | 4.2.2   | Accuracy Analysis                                              |

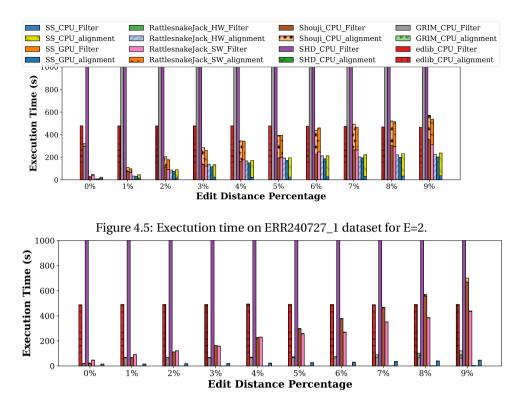

|   |      | 4.2.3   | Throughput and Execution Time                                  |

|   | 4.3  | Discu   | ssions and Future Works                                        |

|   |      | 4.3.1   | RattlesnakeJake for Long Sequence Alignment    87              |

|   |      | 4.3.2   | Potential Design Improvements                                  |

|   | 4.4  | Concl   | usion                                                          |

| 5 | Siev | eMem    | 89                                                             |

|   | 5.1  |         | ation and Profiling                                            |

|   | 0.1  | 5.1.1   | Shared Kernels in Filters                                      |

|   |      |         | Data Movement in Fitlers                                       |

|   |      | 0.1.2   |                                                                |

|   | 5.2   | Propo  | sal and Architecture                           |

|---|-------|--------|------------------------------------------------|

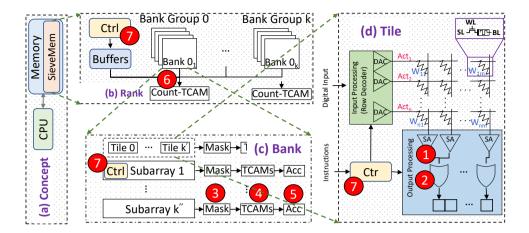

|   |       | 5.2.1  | SieveMem Architecture                          |

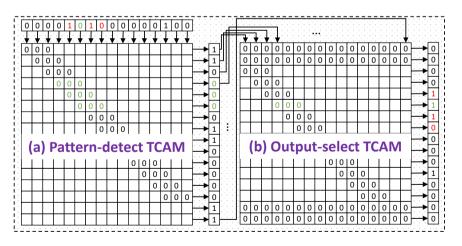

|   |       | 5.2.2  | SieveMem Example Support for SHD 94            |

|   |       | 5.2.3  | BandedKrait Algorithm                          |

|   |       | 5.2.4  | BandedKrait on SieveMem (Mem-BandedKrait)      |

|   | 5.3   | Evalua | ations                                         |

|   |       | 5.3.1  | Evaluation Methodology                         |

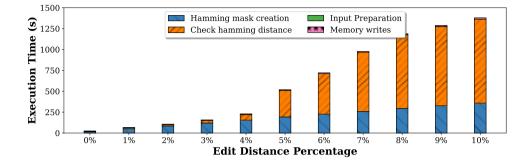

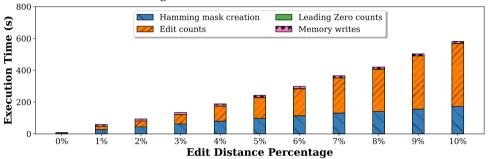

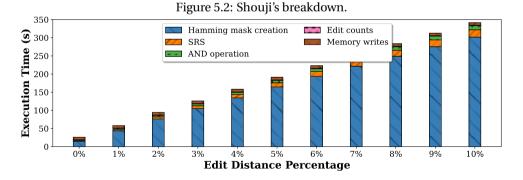

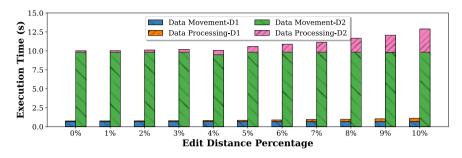

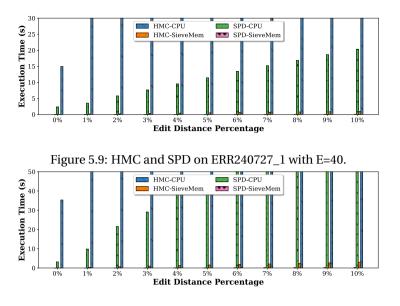

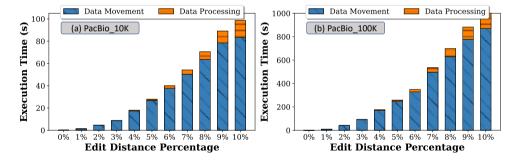

|   |       | 5.3.2  | Execution Time of Supported Kernels            |

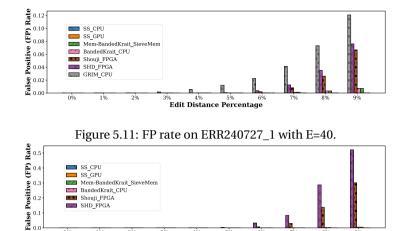

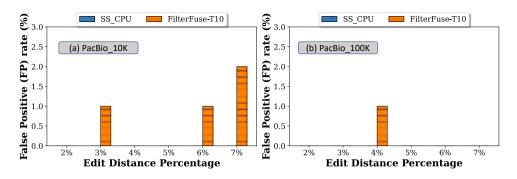

|   |       | 5.3.3  | Filtering Accuracy                             |

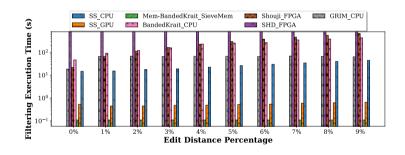

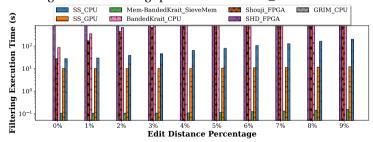

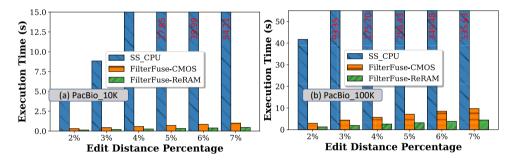

|   |       | 5.3.4  | Filtering Speed                                |

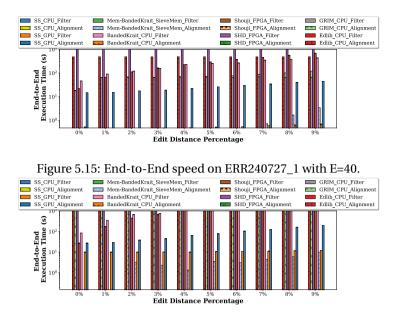

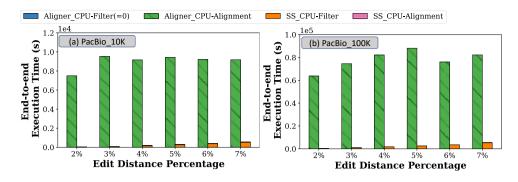

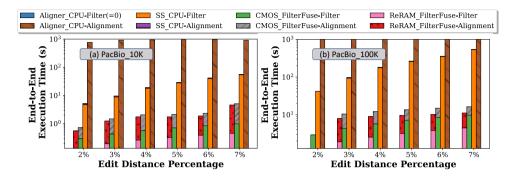

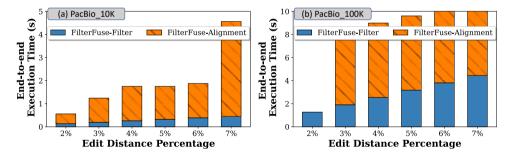

|   |       | 5.3.5  | End-to-end Alignment Speed                     |

|   | 5.4   | Discu  | ssions and Future Works                        |

|   |       | 5.4.1  | SieveMem for Long Sequence Alignment           |

|   |       |        | Potential Design Explorations                  |

|   | 5.5   | Concl  | usion                                          |

| 6 | Filte | erFuse | 105                                            |

| Ŭ | 6.1   |        | ation                                          |

|   | 011   | 6.1.1  | Long Reads vs. Short Reads                     |

|   |       | 6.1.2  | Limitations of SotA filters for long reads     |

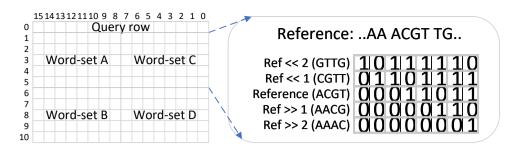

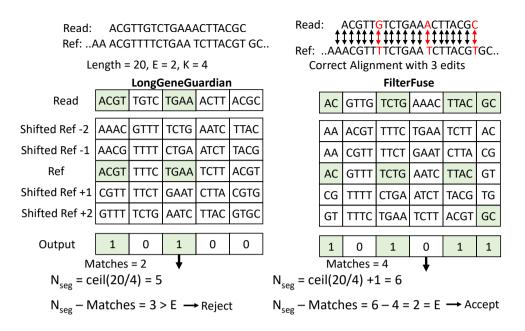

|   | 6.2   |        | GeneGuardian Algorithm                         |

|   | 6.3   |        | Fuse Architecture                              |

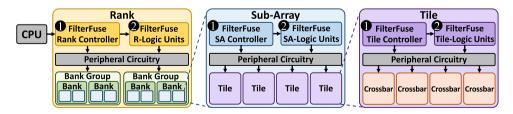

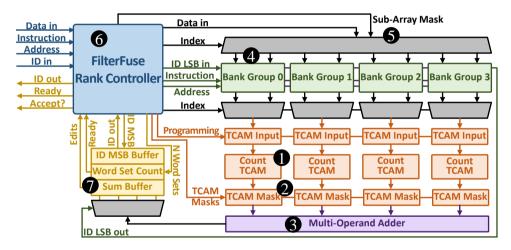

|   |       | 6.3.1  | FilterFuse Overview                            |

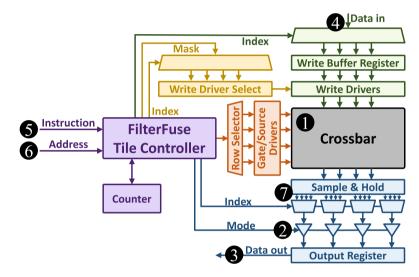

|   |       | 6.3.2  | Tile Architecture    112                       |

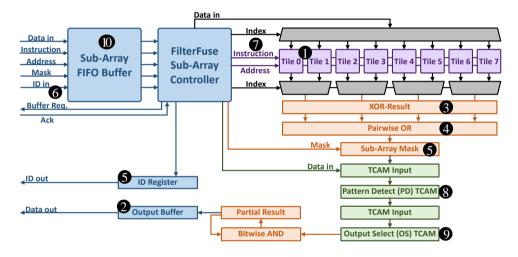

|   |       | 6.3.3  | Sub-Array Architecture                         |

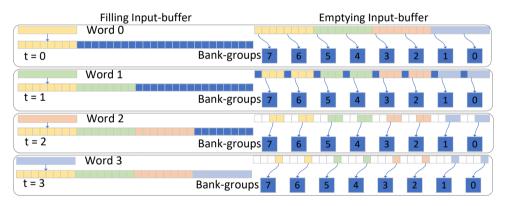

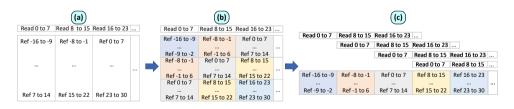

|   |       | 6.3.4  | Bank and Bank-Group Architecture               |

|   |       | 6.3.5  | Rank Architecture                              |

|   |       | 6.3.6  | Data Mapping in FilterFuse                     |

|   |       | 6.3.7  | Long Read Compatibility                        |

|   |       | 6.3.8  | LongGeneGuardian on Software vs. on FilterFuse |

|   | 6.4   | Evalua | ation Methodology                              |

|   | 6.5   | Evalua | ation Results                                  |

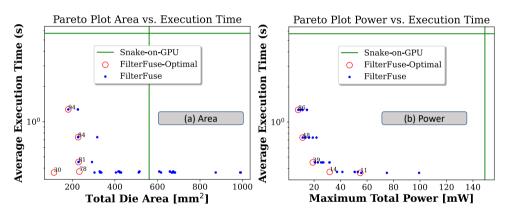

|   |       | 6.5.1  | Design Space Exploration                       |

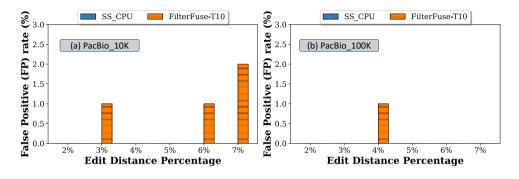

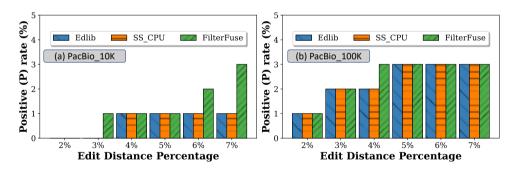

|   |       | 6.5.2  | Filtering Accuracy                             |

|   |       | 6.5.3  | Filtering Speed                                |

|   |       | 6.5.4  | End-to-end Alignment Speed                     |

|   |       | 6.5.5  | Area and Power Analysis                        |

|   | 6.6   | Concl  | usion                                          |

| 7 | Den   | neter  | 127                                            |

| • |       |        | round and Motivation                           |

|   |       | 7.1.1  | Metagenomic Profilers                          |

|   |       | 7.1.2  | Problems of Food Profilers                     |

|   |       | 7.1.2  | hyperdimensional computing                     |

|   |       | 1.1.0  |                                                |

|   | 7.2 | Deme   | ter                                              |

|---|-----|--------|--------------------------------------------------|

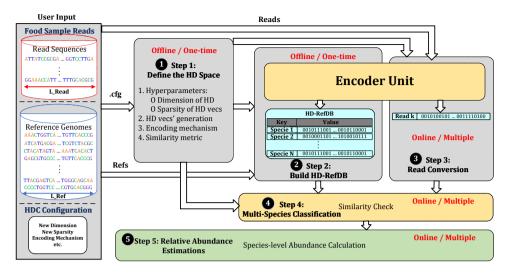

|   |     | 7.2.1  | Step 1: Define the HD Space135                   |

|   |     | 7.2.2  | Step 2: Build Demeter's Reference Data Structure |

|   |     | 7.2.3  | Step 3: Demeter's Read Conversion                |

|   |     | 7.2.4  | Step 4: Multi-Species Classification per Read    |

|   |     | 7.2.5  | Step 5: Species Level Abundance Estimation       |

|   | 7.3 | Deme   | ter's Evaluation                                 |

|   |     | 7.3.1  | Methodology                                      |

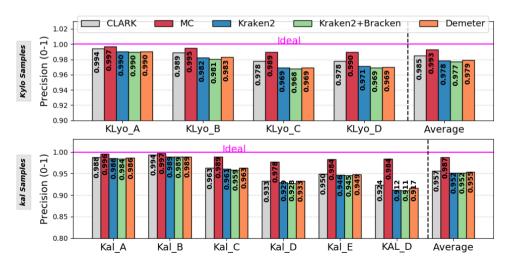

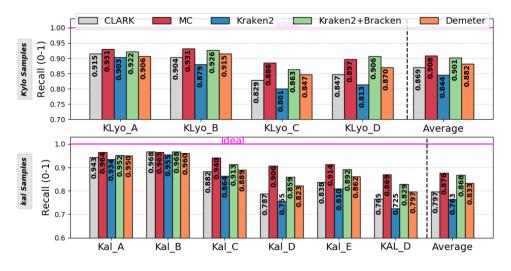

|   |     | 7.3.2  | Demeter's Accuracy Analysis                      |

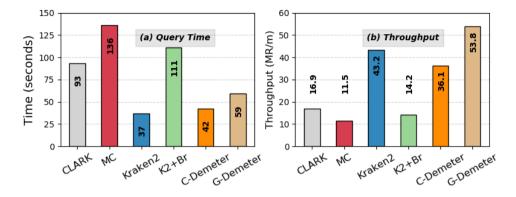

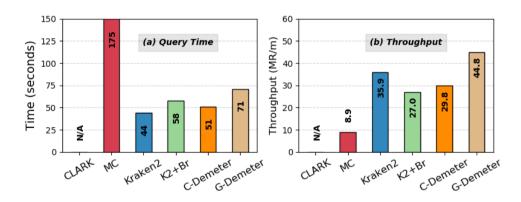

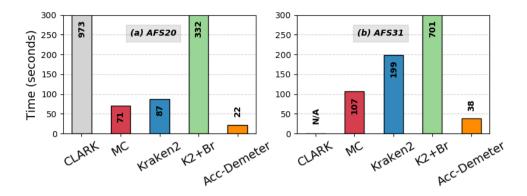

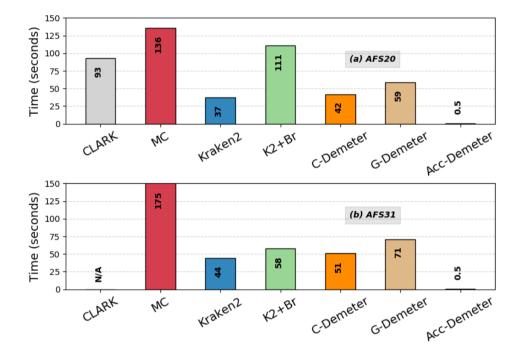

|   |     | 7.3.3  | Demeter's Software Performance Analysis          |

|   |     | 7.3.4  | Demeter's Memory Analysis                        |

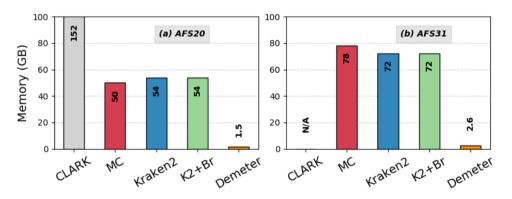

|   | 7.4 | Deme   | ter's PIM-enabled Accelerator                    |

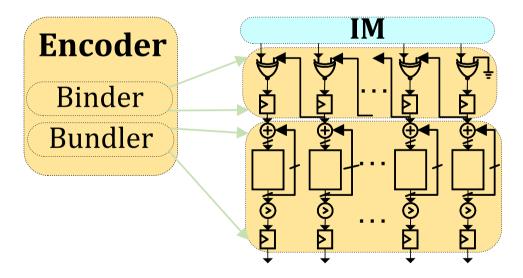

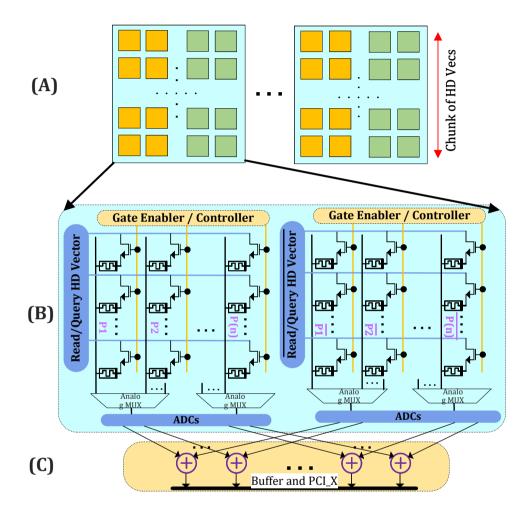

|   |     | 7.4.1  | Overview of Demeter's Accelerator                |

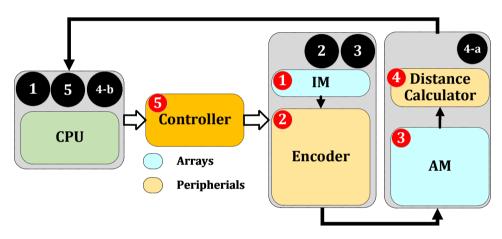

|   |     | 7.4.2  | Item Memory (IM) Design                          |

|   |     | 7.4.3  | Encoder Design                                   |

|   |     | 7.4.4  | Associate Memory (AM) Design                     |

|   |     | 7.4.5  | Similarity Check Hardware                        |

|   |     | 7.4.6  | Controller Unit                                  |

|   | 7.5 | Syster | n Integration of Acc-Demeter                     |

|   |     | 7.5.1  | Address Translation                              |

|   |     | 7.5.2  | Coherence                                        |

|   |     | 7.5.3  | Interrupts                                       |

|   |     |        | ISA Extensions and Programming Interface         |

|   | 7.6 | Acc-D  | emeter's Evaluation                              |

|   |     | 7.6.1  | Methodology                                      |

|   |     | 7.6.2  |                                                  |

|   |     |        | Acc-Demeter's Power and Area Analysis            |

|   | 7.7 |        | ssions and Future Works                          |

|   | 7.8 | Concl  | usion                                            |

| 8 | Kra | kenOn  | Mem 157                                          |

|   | 8.1 | Motiv  | ation                                            |

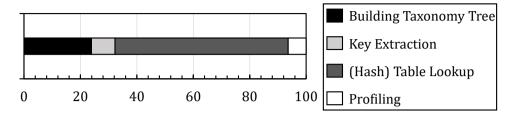

|   |     | 8.1.1  | Kraken2's Execution Breakdown                    |

|   |     | 8.1.2  | Limitation of Previous PIM-enabled Designs       |

|   | 8.2 | Krake  | nOnMem Design                                    |

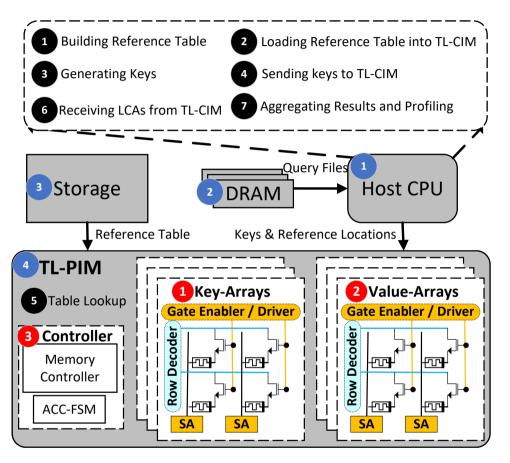

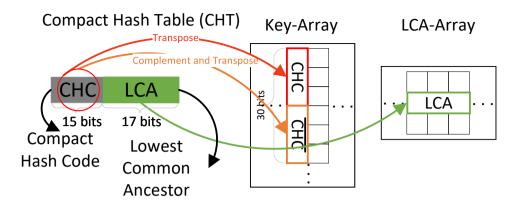

|   |     | 8.2.1  | A High-Level Overview                            |

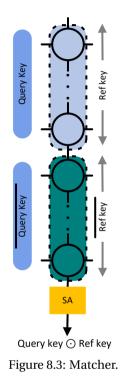

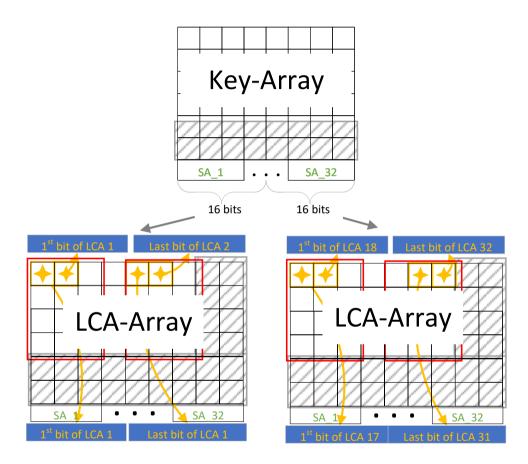

|   |     | 8.2.2  | TL-PIM: Matching Mechanism                       |

|   |     | 8.2.3  | TL-PIM: Taxonomic Retrieval                      |

|   |     | 8.2.4  | TL-PIM: Controller                               |

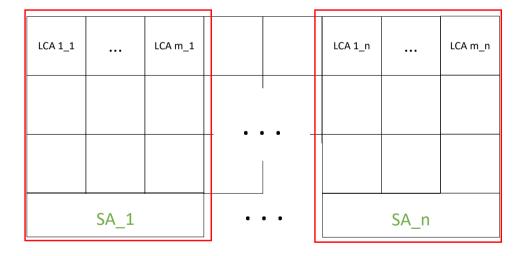

|   |     | 8.2.5  | Relation between LCA-Arrays and Key-Arrays       |

|   |     | 8.2.6  | Optimizations                                    |

|   |     | 8.2.7  | KrakenOnMem Profiling Walk Through               |

|     | 8.3      | Discussions and Future Works                                         | 170 |

|-----|----------|----------------------------------------------------------------------|-----|

|     | 8.4      | Evaluation Methodology                                               | 171 |

|     | 8.5      | Experimental Results                                                 | 172 |

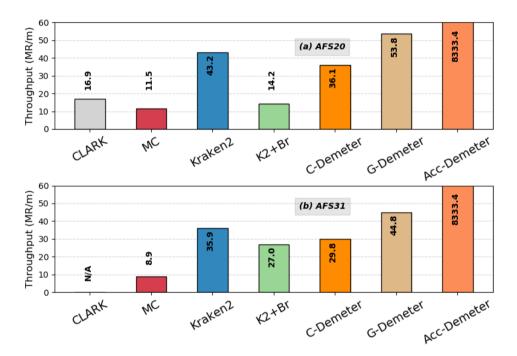

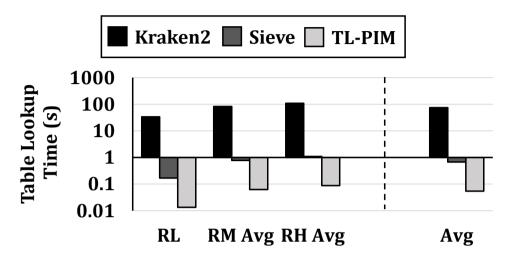

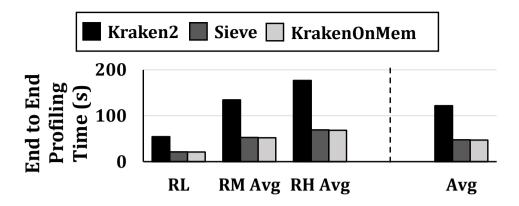

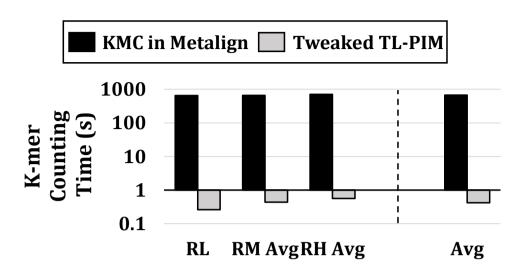

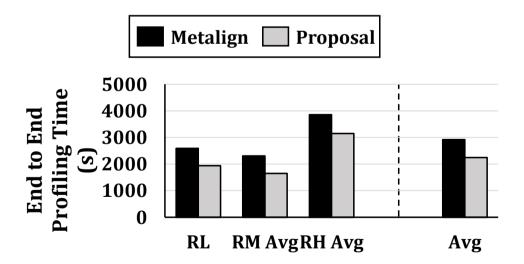

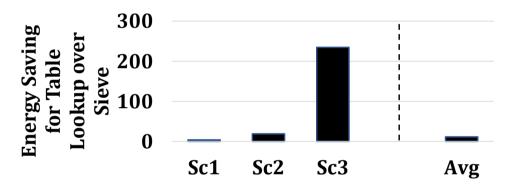

|     |          | 8.5.1 Performance Analysis                                           | 172 |

|     |          | 8.5.2 Power and Area Analysis                                        | 176 |

|     | 8.6      | Conclusion                                                           | 178 |

| 9   | Ligh     | tSpeed                                                               | 179 |

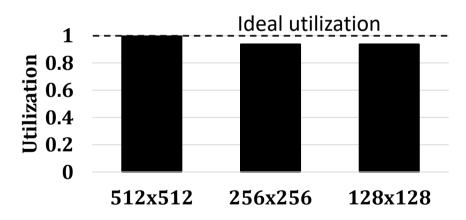

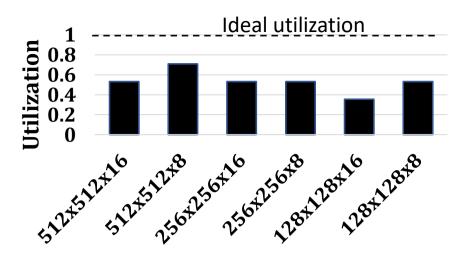

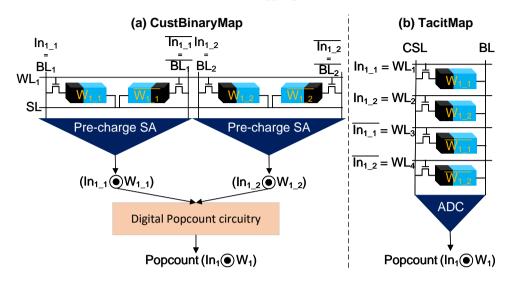

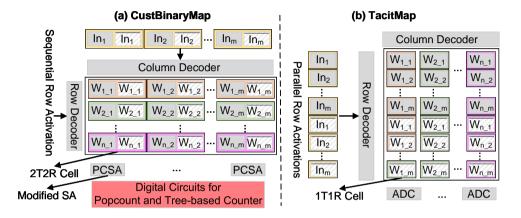

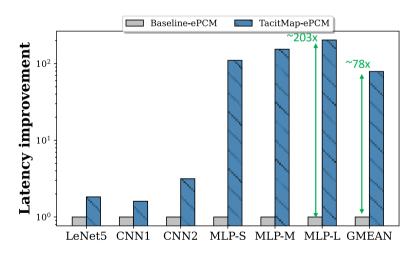

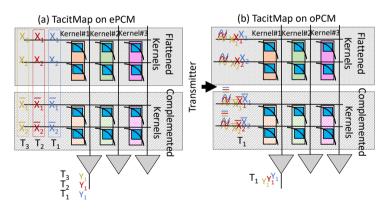

| -   | <u> </u> | TacitMap for BNN.                                                    | 180 |

|     |          | Evaluations                                                          |     |

|     |          | 9.2.1 Networks and Datasets                                          |     |

|     | 9.3      | Conclusion                                                           |     |

| 10  |          |                                                                      | 185 |

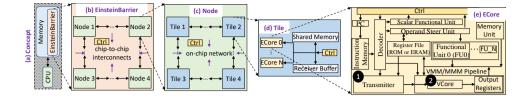

| 10  |          | EinsteinBarrier Architecture                                         |     |

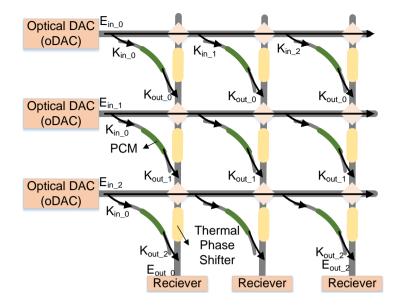

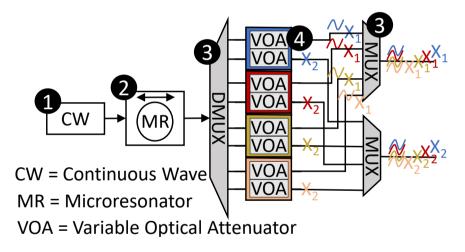

|     | 10.1     | 10.1.1 oPCM-based WDM-enabled ECore                                  |     |

|     |          | 10.1.2 oPCM-based ECore Overheads.                                   |     |

|     | 10.2     | Evaluation Methodology                                               |     |

|     | 10.2     | 10.2.1 Implementations and Models                                    |     |

|     |          | 10.2.2 Designs and Baselines                                         |     |

|     |          | 10.2.3 Networks and Datasets.                                        |     |

|     | 10.3     | Evaluation Results                                                   |     |

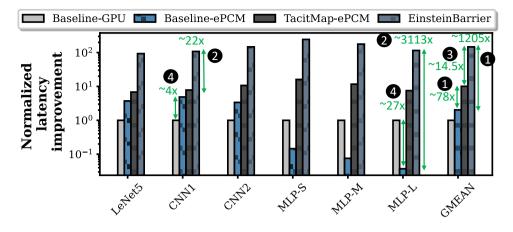

|     | 1010     | 10.3.1 Performance Analysis                                          |     |

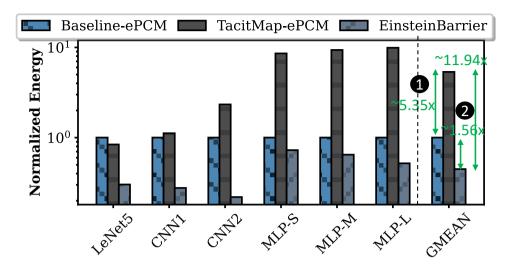

|     |          | 10.3.2 Energy Analysis                                               |     |

|     | 10.4     | Discussions and Future Works                                         |     |

|     |          | Conclusion                                                           |     |

| 11  | Con      | clusion                                                              | 195 |

| 11  |          | Summary                                                              |     |

|     |          | Future Research Directions                                           |     |

|     | 11.2     | 11.2.1 Extending the Proposed Techniques                             |     |

|     |          | 11.2.2 Leveraging and Cascading the New-Found CIM Designs in End-to- | 100 |

|     |          | End Pipelines                                                        | 200 |

|     |          | 11.2.3 New Bottlenecks after Exploiting the Proposed CIM Designs     |     |

| Ер  | ilogu    | le                                                                   | 207 |

| -   | Ŭ        |                                                                      | 209 |

|     |          |                                                                      |     |

| Cu  | rricu    | ılum Vitæ                                                            | 241 |

| Lis | st of I  | Publications                                                         | 243 |

# **SUMMARY**

Modern applications like Genomics and Machine Learning (ML) hold the potential to reshape our understanding of diseases' genetic origins and guide machines in executing tasks and making predictions without our explicit programming. The successful, widespread integration of these modern applications can usher in advancements in diagnostics, individualized medicine, and routine tasks such as language interpretation, image analysis, and object categorization. However, our traditional computing infrastructures fall short when accommodating the distinct characteristics of these new applications. Specifically, (1) these applications handle an immense and ever-expanding data working set, and (2) each succeeding version of these applications and their associated use cases necessitates quicker and more energy-efficient analysis of these vast data sets. This is because our traditional computing systems largely hinge on (1) the von-Neumann architecture, a design that distinctly positions processing entities (like CPUs and GPUs) away from storage components (like memories and flash drives), and (2) the CMOSbased technology. While attempting to meet the performance and energy demands of our modern applications, these fully CMOS-based systems based on von-Neumann architecture have increasingly struggled and hit inherent roadblocks, with data movement overhead being the predominant issue.

To alleviate the data movement bottleneck, contemporary research revisits a concept historically known as Computation-In-Memory (CIM) or, alternatively, Processing-In-Memory (PIM). At its core, CIM emphasizes positioning computational capabilities close to, or within, the memory units storing the data. This placement might be within memory chips, in memory controllers, amid caches, or embedded in the logic layers of 3Dstacked memories. As a computational model, architectures leveraging CIM (referred to as CIM architectures) stand to tackle the issue of data movement overhead inherent in the von-Neumann architecture by diminishing or outright eradicating the data movement between computational locales and data storage areas. Moreover, from a technological perspective, emerging memory technologies, including memristive devices and circuits, show potential to replace traditional memory systems, addressing some of the challenges posed by CMOS-based designs.

Irrespective of the specific CIM architecture deployed to optimize performance or energy efficiency in modern applications, there are substantial practical challenges to address and ponder upon first. Both system designers and developers face these hurdles and design decisions, which are critical to surmount CIM's widespread acceptance across various computational areas and application domains.

In this dissertation, our focus is twofold: (1) We delve into the acceleration and streamlined execution of various steps in two pivotal application realms: genomics and ML; and (2) We explore several emerging memory technologies alongside circuit and architectural strategies, that show promise in enhancing CIM designs, specifically tailored for modern applications.

Therefore, in this thesis, we identify and propose strategies and designs to ameliorate the constrained performance of key kernels in genomics and ML. Recognizing that applications within these realms consist of diverse functions or kernels, it is imperative for a designer to possess a thorough understanding of them. Each function/kernel can be characterized by distinct data and control flows, calling for varied features to be enabled in either a von-Neumann or a CIM architecture. To enhance the efficacy of each function/kernel, we first profile them individually and then within a larger context of their corresponding pipeline, followed by discerning the best avenues for their memory mapping in a CIM architecture. We then undertake a concurrent assessment of essential adjunct components alongside the memory array, commonly referred to as the peripheries. For a designer, proficiency in the applications executable on a CIM system leveraging emerging memory technologies is indispensable. Grasping the fundamental characteristics of CIM and having an overarching view of its scope becomes vital prior to its integration. We aim to aggregate critical application features, improvement opportunities, and design decisions and refine them to their core essence. Through this, we aspire to shed light on present design options and identify kernels demanding heightened attention. Such insights can be instrumental in revealing prospective directions, encompassing supported kernels along with their respective merits and trade-offs.

We exploit emerging technologies and architect state-of-the-art CIM designs that optimally serve the targeted kernels, keeping a holistic improvement perspective at the forefront. Delving into emerging (memory) technologies, such as memristive devices like PCM and STT-MRAM, is crucial. These devices provide a suite of advantages, including non-volatility, compactness, and a natural aptitude for conducting logical operations (for instance, the logical AND). Additionally, other emerging technologies, such as integrated photonics, have the potential to enhance the CIM paradigm further with their capacity for high-frequency and low-latency functions. Our ambition is to integrate multiple such technologies, harnessing their distinct attributes, to craft a CIM design that surpasses the SotA counterparts across key benchmarks, be it in execution speed or energy.

This thesis demonstrates that when CIM is fused with emerging (memory) technologies, there is a marked enhancement in the performance of several Genomics pipelines and Machine Learning applications. It is our aspiration and conviction that the evaluations, methodologies, and findings detailed in this dissertation will empower the broader community to comprehend and address contemporary and upcoming challenges that revolve around enhancing the performance and energy efficiency of modern applications through the integration of (re)emerging computing paradigms and technologies. Additionally, our work provides insights for adapting these technologies to novel applications, ensuring they deliver optimal benefits.

# SAMENVATTING

Moderne toepassingen zoals Genomics en Machine Learning (ML) hebben het potentieel om ons begrip van de genetische oorsprong van ziekten te hervormen en machines te begeleiden bij het uitvoeren van taken en voorspellingen zonder expliciete programmering. De succesvolle, wijdverbreide integratie van deze moderne toepassingen kan vooruitgang betekenen op het gebied van diagnostiek, gepersonaliseerde geneeskunde en routinetaken zoals taalinterpretatie, beeldanalyse en objectcategorisatie. Onze traditionele computerinfrastructuren schieten echter tekort bij het om de kenmerken van deze nieuwe toepassingen te accommoderen. In het bijzonder behandelen deze toepassingen een enorme en steeds uitbreidende dataset (1), en elke volgende versie vereist snellere en energiezuinigere analyse van deze enorme datasets (2). Dit komt doordat onze traditionele computersystemen voornamelijk afhankelijk zijn van de von-Neumann-architectuur (1) en op CMOS-technologie (2) gebaseerd zijn. Bij het proberen te voldoen aan de prestatie- en energie-eisen van moderne toepassingen, hebben deze volledig CMOS gebaseerde von-Neumann-architecturen steeds meer problemen ondervonden en lopen ze tegen inherente obstakels, waarvan het dataverplaatsing bij gegevensverwerking het belangrijkste probleem is.

Om het probleem van dataverplaatsing bij gegevensbeweging aan te pakken, herziet hedendaags onderzoek een concept dat historisch bekend staat als Gegevensverwerking-In-Geheugen (GIG). In de kern benadrukt GIG het plaatsen van rekenkundige mogelijkheden dichtbij, of binnen, de geheugeneenheden die de gegevens opslaan. Deze plaatsing kan in geheugenchips zijn, in geheugencontrollers, te midden van caches of ingebed in de logische lagen van 3D-geheugens. Architecturen die gebruik maken van GIG (aangeduid als GIG-architecturen) hebben als doel het probleem van gegevensbeweging dat inherent is aan de von-Neumann-architectuur aan te pakken door de gegevensbeweging tussen verwerkingslocaties en geheugens te verminderen of volledig te elimineren. Bovendien tonen opkomende geheugentechnologieën, waaronder memristorcomponenten en -circuits, potentieel om traditionele geheugensystemen te vervangen en enkele uitdagingen van op CMOS gebaseerde ontwerpen aan te pakken.

Ongeacht de specifieke GIG-architectuur die wordt ingezet om de prestaties of energie-efficiëntie in moderne toepassingen te optimaliseren, zijn er aanzienlijke praktische uitdagingen die aangepakt moeten worden. Zowel systeemontwerpers als ontwikkelaars staan voor deze hindernissen en ontwerpbeslissingen, die cruciaal zijn voor het overwinnen van de brede acceptatie van GIG in verschillende computergebieden en toepassingsdomeinen. In deze dissertatie ligt onze focus op twee aspecten: (1) We duiken in de versnelling en stroomlijning van verschillende stappen in twee cruciale toepassingsgebieden: genomics en ML; en (2) we verkennen verschillende opkomende geheugentechnologieën naast circuit- en architectuurstrategieën, die belofte tonen om GIG-ontwerpen te verbeteren die specifiek afgestemd zijn op moderne toepassingen.

Daarom identificeren en stellen we in dit proefschrift strategieën en ontwerpen voor

om de beperkte prestaties van essentiële kernels in genomics en ML te verbeteren. Omdat toepassingen binnen deze gebieden bestaan uit diverse functies of kernels, is het cruciaal voor een ontwerper om een grondig begrip hiervan te hebben. Elke functie of kernel kan worden gekenmerkt door verschillende gegevens- en besturingsstromen, wat vraagt om verschillende functies in zowel een von-Neumann- als een GIG-architectuur. Om de effectiviteit van elke functie of kernel te vergroten, profileren we ze eerst individueel en vervolgens binnen de grotere context van hun pipeline, gevolgd door het bepalen van de beste geheugenmapping in een GIG-architectuur. Vervolgens voeren we een gelijktijdige beoordeling uit van essentiële aanvullende componenten naast de geheugenarray, vaak aangeduid als de perifere componenten. Voor een ontwerper is bekwaamheid in de toepassingen die kunnen worden uitgevoerd op een GIG-systeem dat gebruik maakt van opkomende geheugentechnologieën onmisbaar. Het begrijpen van de fundamentele kenmerken van GIG en het hebben van een alomvattend beeld van de reikwijdte ervan is cruciaal voorafgaand aan de integratie. We streven ernaar om kritieke toepassingskenmerken, verbeteringsmogelijkheden en ontwerpbeslissingen samen te brengen en ze te verfijnen tot hun kern. Hierdoor hopen we inzicht te verschaffen in de huidige ontwerpmogelijkheden en kernels te identificeren die meer aandacht vergen. Dergelijke inzichten zijn instrumenteel om toekomstige richtingen te bepalen, waaronder de ondersteunde kernels samen met hun respectieve voordelen en afwegingen.

We maken gebruik van opkomende technologieën en ontwerpen GIG-architecturen die optimaal de kernels implementeren, met een holistisch verbeteringsperspectief voor ogen. Het verkennen van opkomende (geheugen)technologieën, memristorcomponenten zoals PCM en STT-MRAM, is cruciaal. Deze componenten bieden een reeks voordelen, waaronder niet-vluchtigheid, compactheid en een inherente geschiktheid voor het uitvoeren van logische bewerkingen (bijvoorbeeld de logische EN-operatie). Daarnaast hebben andere opkomende technologieën, zoals geïntegreerde fotonica, het potentieel om het GIG-paradigma verder te verbeteren door hun hoogfrequente en snelle eigenschappen. Onze ambitie is om meerdere van dergelijke technologieën te integreren, gebruik makend van hun unieke kenmerken, om een GIG-ontwerp te creëren dat de tegenhangers overtreft op belangrijke benchmarks, zowel qua uitvoeringssnelheid als energieverbruik.

Dit proefschrift toont aan dat wanneer GIG wordt samengevoegd met opkomende (geheugen)technologieën, er een merkbare verbetering is in de prestaties van verschillende genomics-pipelines en Machine Learning-toepassingen. Het is onze ambitie en overtuiging dat de evaluaties, methodologieën en bevindingen die in dit proefschrift worden beschreven, de bredere gemeenschap in staat zullen stellen om hedendaagse en toekomstige uitdagingen die draaien om het verbeteren van de prestaties en energieefficiëntie van moderne toepassingen door de integratie van (her)opkomende rekenparadigma's en technologieën te begrijpen en aan te pakken. Bovendien biedt ons werk inzichten voor het aanpassen van deze technologieën aan nieuwe toepassingen, zodat ze optimale voordelen kunnen opleveren.

# ACKNOWLEDGEMENTS

This thesis marks three years of my efforts throughout my graduate studies and many individuals who, directly or indirectly, have contributed to its completion or how I experienced it. Therefore, I would like to take this moment to highlight them and express my gratitude.

First, I thank my promoters, **Said Hamdioui** and **Stephan Wong**. In the research group **Said** established at TU Delft, I have gained essential skills that will shape my career path. **Said**, from the outset of my Ph.D., you placed faith in my research and my organizational skills, even nominating me as our research group's representative on the department's Ph.D. council. For that, I am thankful.

I thank **Stephan Wong**, my promoter, daily supervisor, and constant advocate. **Stephan**, your astute feedback on my work has been pivotal in advancing my research. Your extensive experience across research, academia, and administrative tasks and willingness to share them have enriched my understanding of the system. Beyond this, I also deeply appreciate the autonomy you granted me in exploring research avenues I was passionate about. Your faith in me was evident when you entrusted me with teaching responsibilities, shared your instructional methods and early graduation techniques, and backed my internships. Most crucially, your unwavering presence, shielding me from internal and external strife and uplifting my spirit during challenging times, has been invaluable. My heartfelt thanks for everything.

I owe an immeasurable gratitude to my enduring advisor and life mentor, **Onur Mutlu**. Having the privilege of being his student since 2018 has been transformative. I am deeply thankful for his unwavering support and guidance throughout this journey. **Onur**, your persistent push for grand visions, unyielding commitment to research, and challenges to elevate my capabilities have sculpted me as a researcher standing here. The environment you fostered within SAFARI, coupled with your unwavering trust in me, has endowed me with the insights, tools, and perspective essential for my personal and professional evolution. I am confident that the wisdom and skills imparted by **Onur** and those gained under his supervision will remain integral to my growth in research, science, and engineering. Cheers, **Onur**.

I am grateful to the committee members of this thesis, **Sander Stuijk**, **Ian O'Connor**, **Rene van Leuken**, **Wouter Serdijn**, and **Sorin Cotofana**. Your insightful feedback has been crucial in enhancing my thesis, and I eagerly anticipate witnessing the influence of our future collaborative efforts.

I would like to extend my gratitude to my academic partners. **Ian O'Connor** and **Alberto Bosio**, thank you for welcoming me into your research group. The knowledge you passed on about optical phase change memory and FeFET, the critical discussions on my work, and the essential measurement data you provided have significantly enhanced my research journey. The one-on-one meetings in Lyon hold particular importance to me. I am optimistic about the continuance of our rewarding collaboration. My thanks to **Asif Ali Khan** for bridging our collaboration. Our technical exchanges, particularly those centered around pre-alignment filters and racetrack memory, were enlightening. I am also grateful for the platform you provided me to present a technical discourse on my research at the Chair for Compiler Construction (CCC) in TU Dresden. Moreover, our casual, non-research conversations during our interactions in Germany added a pleasant dimension to our professional relationship. My sincere thanks to each one of you.

I am grateful to researchers and members of the various departments at TU Delft, the SAFARI research group at Eidgenössische Technische Hochschule (ETH) Zürich, and Institut des Nanotechnologies de Lyon (INL) at École Centrale de Lyon (ECL) for their steadfast support throughout this journey. While the path to a Ph.D. can often feel solitary and lonely, each of you played a role in mitigating that solitude, transforming what is typically an individual endeavor into a collective experience. Mahdi, your presence as a sounding board and officemate has been invaluable. I also extend my heartfelt gratitude to other members of the TU Delft family, including but not limited to, Robert, Moritz, Christiaan, Folkert, Sumit, Amin, Abdullah, Motta, Alireza, Michael, Guilherme, Matti, Asmae, Hanzhi, Abdulqader, Rajendra, Sicong, Pantazis, Fouwad, Arne, Mark, Yash, Heba, Francis, and Paul. Our shared moments, from delightful lunches and daily coffee breaks to numerous discussions, have been highlights of my time in the office. Equally, my time at INL and SAFARI was enriched by interactions with friends like Minesh, Haocong, Skanda, Rahul, Ataberk, Raphael, Tracy, and many more. I cherish the moments of academic collaboration and the bonds of friendship forged. Your support has been a cornerstone in my academic and personal growth, and I wish each of you success and happiness in your future endeavors. Thank you all.

Throughout my life, spanning the Netherlands, Switzerland, France, Germany, and Iran, I was fortunate to encounter many incredible souls who enriched my life beyond the confines of my work. Mina, Danial, and Bahador, I cherish our enduring friendship, one that defies the vast geographic distances between us. Your messages and laughs always brightened my mornings. My heartfelt gratitude extends to Shibashish, Melanie, Sarah, Skanda, Maria, Minesh, Linus, Julius, Ninad, and Sandra, housemates, officemates, classmates, or clubmates, who transitioned into my dear close friends and loved ones. Our shared moments, from our late-night discussions and explorations in the Zürich forests and city to aimless rides and random events in Italy or the Netherlands, have been foundational in making my journey so fulfilling. You have been the backbone of encouragement and positivity, always ready to lend an ear, and your ever-present support, abundant encouragement, and undying positivity were all one can ask for. My dearest friends, your consistent companionship was instrumental in helping me find my footing in Zürich and the Netherlands. From introducing me to the city's nuances to crafting countless treasured memories, I am deeply appreciative. Here is to more delightful evenings at the lake, in the forest, or in our fantastic hobby room and gardens. Lastly, a big shout-out to my sports companions, Karin, Bram, Florence, Fiske, and Thomas. Your relentless mantra of "5×/week, no excuses", our "4 more" signals, tough sparrings, and our regular dinners and meetings marked by spirited dialogues on topics ranging from coding in Rust and hackathons to finance to fashion have been truly exhilarating. Every minute with you was not just about health or fitness but also about bonding and growth. Cheers to all of you and the memories shared, and to many more in the future.

I am eternally grateful to my family and friends from back home or abroad. Their deep love and enduring support have been the bedrock upon which I have built my dreams. A special mention goes to my cousin, **Eiman**. Despite the whirlwind of leading a highly successful startup, **Eiman** always found moments to offer me priceless advice and wisdom. I extend my gratitude to **Ali** for his unwavering support in the Netherlands, both emotionally and physically. Our dinners at his residence were delightful and a highlight for my weeks. To my beloved grandparents, aunts, uncles, and extended family, your unwavering support has been a cornerstone of my endeavors. Those occasional messages, brimming with love and buoyant words of motivation, have been my guiding light, pushing me forward even during challenging times. Your faith in me has made all the difference, and I remain forever indebted to your kindness and belief.

To the very foundation of my being, the pillars of my strength and determination, I owe the deepest debt of gratitude to my parents, **Dariush** and **Tahere**, and my brother, Emad: Every step I took in this demanding world of scientific endeavor, I found my footing on the strong base you laid down for me. Your tireless dedication, unvielding efforts, and immeasurable love were my guiding stars. Dariush, from you, I learned the art of resilience, even in life's harshest moments and in the face of profound sorrow. Your wisdom has been the compass by which I have navigated challenges. The world could shift under my feet, but the lessons you imparted and the love you have shown me remain steadfast. Thank you! Tahere, in every setback and moment of self-doubt, your emotional anchor and words of encouragement set me back on course. Your unwavering belief in me and gentle encouragement have always been my saviors. **Emad**, my dear brother, the bond we share is beyond words. You have been a sanctuary of patience, an embodiment of love, and a wellspring of support. Our shared moments, be they of joy, fights, or simply day-to-day life, are treasures in my heart. Even when I was difficult and lost my way, you stood steadfast, echoing your belief in me. Beyond just being siblings, our bond has grown into an unrivaled camaraderie. You have witnessed my peaks and valleys, constantly extending a hand of support, love, and understanding. My heart brims with gratitude for every gesture, word, and a lifetime of shared memories and moments with you. Emad, not just my brother, but my beacon and inspiration, thank you!

# 1

# **INTRODUCTION**

The minute you get away from fundamentals –whether its proper technique, work ethic, or mental preparation– the bottom can fall out of your game, your schoolwork, your job, whatever you are doing.

Michael Jordan

Modern applications such as genomics and Machine Learning (ML) promise transformative advancements to human lives. However, the execution of these applications has bottlenecked with traditional computing infrastructures, primarily due to data movement overheads inherent in von-Neumann and CMOS-based designs. Recently, researchers explored the Computation-In-Memory (CIM) paradigm to reduce these overheads, placing computation close to memory storage. When combined with emerging technologies like memristive devices, such CIM architectures can replace traditional systems and address data movement overhead and some other limitations inherent to fully CMOS-based technologies. However, implementing CIM brings practical challenges for system designers and developers, impacting widespread acceptance. In this chapter, we first discuss the impacts of modern applications on our lives and their unique features separating them from traditional ones. We then discuss the limitations of traditional systems mainly based on von-Neumann architecture and CMOS technology for high-performance and/or energyefficient execution of modern applications. We motivate CIM and emerging memory technologies as a potential solution for efficient, futuristic systems for modern applications. After that, we discuss the main opportunities and challenges such CIM designs introduce. Following, we discuss the research directions and topics this thesis explores. Finally, we present our thesis statement and list our contributions and thesis organization.

### 1.1. MOTIVATION

Genomics and Machine Learning (ML) are two examples of modern applications revolutionizing our world. Genomics is a branch of genetics that investigates the interactions between genes and non-genic genome regions and how they mold observable traits and biological functions. Genomics brings about a remarkable increase in our comprehension of biology and illness. Genomics sheds light on the genetic foundations of diseases, paving the way for superior diagnostics and treatment approaches. This way genomics lays the groundwork for progress in personalized medicine, allowing for treatment methods to be customized based on a person's genomic data. Advancing genomics studies that hold the key to unlocking the potential of precision medicine, facilitating virus surveillance, and driving advancements in healthcare [1–17].

ML is an application domain focusing on the development of algorithms and statistical models for computer systems to "learn" from experience, i.e., to perform tasks and make decisions/predictions without being explicitly programmed to do so. Currently, we use ML applications in many of our day-to-day tasks such as language processing [18] object recognition [19], and image classification [20, 21]. In particular, momentous developments in Deep Neural Network (DNN) in the past decade have led to significant improvements in the accuracy and execution time of computer vision tasks such as object detection and recognition [22–24].

These modern applications, i.e., genomics and ML, share two main critical features:

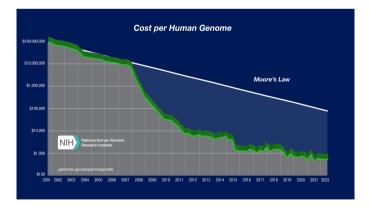

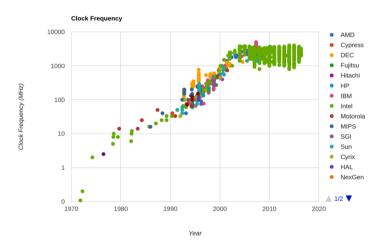

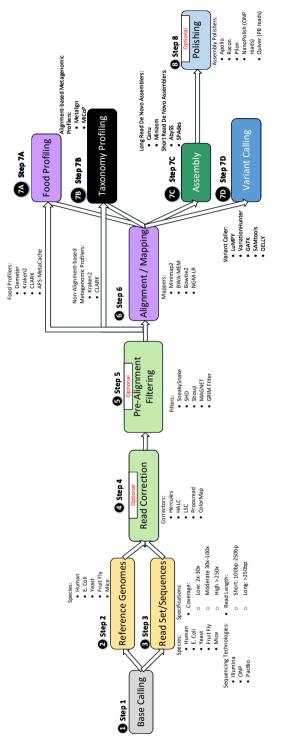

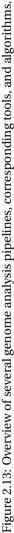

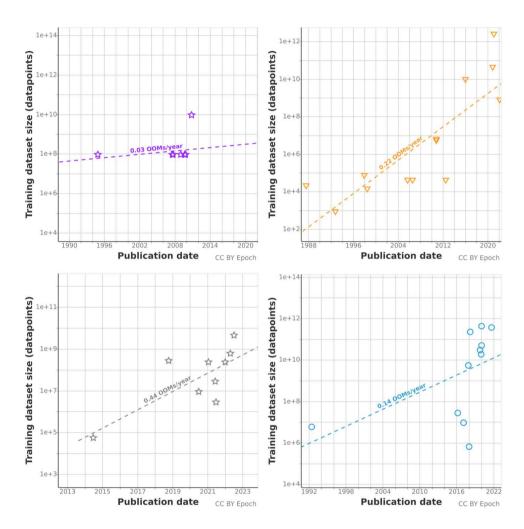

• Their data working set size is rapidly growing. For example, one can characterize many of the existing genomics pipelines as simple and data-hungry sequences of operations that require high parallelization. Fig. 1.1 depicts the significant reduction in the cost of data acquisition in genomics, next to Moore's law ascending growth, helping the exponential growth of the data working set size of its kernel. It is estimated that the working datasets of the genomics domain scale faster than those produced by YouTube and Twitter for Machine Learning-based (ML-based) applications [25–27].

Figure 1.1: The nature of the reductions in DNA sequencing costs over the years against Moore's Law [26].

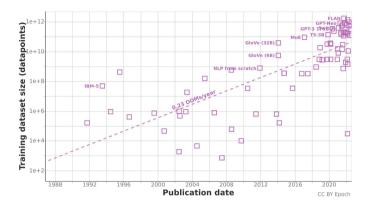

ML applications are the same. For another example, Fig. 1.1 presents the trend in training datasets of language-based ML over the years. The growth of the data working set is apparent from the models developed for this task. Other ML tasks follow a similar trend (Section 2).

Figure 1.2: The growth rate of dataset size in ML for language based tasks such as text generation and classification [28].

• The demand for faster analysis of such large data working sets is increasing. Particularly in genomics, the swift processing of genomics data plays a crucial role in unleashing the full potential of precision medicine, bolstering virus surveillance capabilities, and propelling advancements in healthcare. Moreover, ML applications also demand fast analysis for enhanced automation, expedited explorations, and more efficient decision-making processes.

Unfortunately, our traditional computing systems only rely on von-Neumann architecture [29–31] and CMOS technology that fundamentally have already faced major limitations while they tried to keep up with the high performance and energy-efficiency demand of genomics and ML applications [15, 32].

## **1.2.** LIMITATIONS OF TRADITIONAL COMPUTING SYSTEMS

Traditional computing systems adopt solely on CMOS technology and the von-Neumann architecture: a processor-centric architecture that separates the processing units (CPUs, GPUs, etc.) and storage units (memories, flashes, etc.) [29–31]. This choice introduces some challenges and limitations for our modern applications that we discuss next.

The sole reliance on CMOS technology recently introduced technological limitations when we try to keep up with the high performance and energy-efficiency demand of modern applications [32]. In the past decade, we have witnessed significant advancements in semiconductor technology regarding the feature size of the transistors and the number of transistors on a single chip. These advances advocate two famous laws in

computer architecture: Moore's Law and Dennard's Law. Moore's Law [33] and Dennard's Law [34] are two closely-related observations regarding the advancement of semiconductor technology, focusing on different aspects. Moore's Law states that the number of transistors on a chip will double approximately every two years. This exponential growth leads to an increase in computational power. Dennard's Law, on the other hand, targets the power consumption and performance scaling of transistors as their feature size decreases, i.e., they shrink in size. Dennard's Law states that as transistors become smaller, their power density remains constant. This allows for increased performance at the same power consumption level.

Unfortunately, semiconductor advancements regarding Moore's and Dennard's laws are slowly coming to an end due to three main limitations:

- Leakage Wall: The continuous scaling of transistors results in the reduction of gate thickness and channel length between the drain and source, shrinking down to a few atomic layers. Consequently, there is an increased likelihood of quantum mechanical tunneling, leading to higher gate leakage current. Moreover, shorter channels can contribute to elevated off-state drain leakage. Additionally, as supply and threshold voltages are scaled down, the static power during the off state of the transistor experiences an increase, forming a leakage wall.

- **Reliability Wall:** With the scaling down of transistor size, even minor variations in the fabrication processes can significantly impact the functionality of the transistors, forming a reliability wall. Additionally, the continued scaling poses challenges in terms of reliable insulation and conduction due to limitations in the dielectric and wiring materials.

- **Cost Wall:** As the size of transistors decreases, the cost of fabrication experiences an exponential increase. This cost escalation is driven by various factors such as equipment, lithography processes, masks, and testing expenses, forming a cost wall.

These limitations motivate us to seek alternative technologies to continue our performance and energy improvements with less reliance on scaling the transistors' feature sizes and their number on a specific chip.

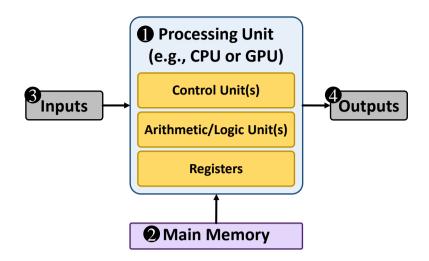

To understand the architectural limitations arising from adapting von-Neumann architecture, Fig. 1.3 depicts this architecture first.

As Fig. 1.3 shows, a von-Neumann architecture comprises three main components: **1** a processing unit (e.g., central processing unit (CPU) or graphics processing unit (GPU)), **2** a memory, and **3** input or **4** output devices. The processing unit executes the program instructions and performs logical or arithmetic operations on the data. The data is loaded from the memory or the input devices, and the results are written back into the memory or sent out to the output devices. The Von Neumann architecture offers four advantages making it suitable for our traditional computing systems and applications:

• Simplicity: The Von Neumann architecture is simple and straightforward, making it easy to understand and implement. This architecture separates the computer's mem-

Figure 1.3: Von-Neumann architecture, i.e., processor-centric architecture, in traditional computing systems.

ory into two distinct types: one for instructions and one for data. This architecture follows the fetch-decode-execute cycle.

- Uniformity: Using a single memory space for both data and instructions simplifies the architecture. This also brings versatility. Such a clear separation allows instructions to be stored in the same form as data. This means that any program can be treated as data and manipulated accordingly.

- Self-modifying code: This architecture allows a program to modify itself since data and instructions are stored in the same memory.

- Hardware Cost: The Von Neumann architecture reduces the hardware cost by utilizing the same memory and peripheries (e.g., buses) for both instructions and data.

- Precedent: The Von Neumann architecture is well-understood and widely used. This establishes a precedent that advocates other advances in computer technology.

Using a single-level, large memory unit in the von-Neumann architecture historically introduced two main challenges for traditional applications: (1) high cost regarding latency and energy consumption for data transactions between the CPU and main memory and (2) requirement of very large memory unit to accommodate the large data working set. For example, previous work [35] shows that the simple off-chip communication between the memory unit (DRAM) and CPU can take up to 200 CPU cycles. Other works [36, 37] show that the energy consumption for moving data for a floating point operation to the CPU consumes more than two orders of magnitude more energy than the energy for the operation within the CPU. 1

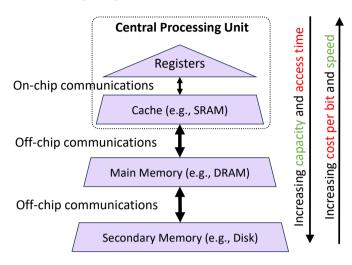

However, system designers overcome these challenges by proposing a hierarchy for memory in the von-Neumann architecture [29, 31]. Fig. 1.4 depicts this memory hierarchy in the traditional computing systems based on von-Neumann architecture.

Figure 1.4: Memory hierarchy in traditional von-Neumann-based systems.

The memory hierarchy tackles the high cost of data movement by exploiting the temporal locality of data and having an SRAM-based cache memory located in the same chip as the CPU. This SRAM cache reduces the access time for the data. However, due to cost reasons (e.g., area overhead), designers keep SRAM caches smaller than the main memory and typically smaller than the data working set of even traditional applications. This hierarchy also tackles the problem of larger than the main memory problem of traditional applications by placing secondary memory storage, also known as a disk. The operating system (OS) manages data transfer from the disk (i.e., secondary memory) to the main memory. Current systems use flashes or hard disk drivers for this secondary memory. Although the secondary memory scales up easily, access time would be much higher due to the technology limitation and architectural complexity.

The sole reliance on the aforementioned von-Neumann architecture and memory hierarchy comes with its own architectural limitations. Beyond just technological advancements in semiconductors, the evolution of architectural design has been instrumental in enhancing the efficiency of computer systems over the past several decades. Nonetheless, the potential for performance enhancement from this factor has recently become limited due to three well-known walls:

• **Power Wall:** The miniaturization of transistors has also allowed a greater number to fit within a fixed area. Table 1.1 illustrates this trend, demonstrating the increased transistor count in various Intel processor generations. With this increase in the number of transistors, processors can now support multiple cores, allowing parallel task execution. This, however, escalates power consumption corresponding to the increased core count. Nevertheless, the amount of power that a chip

1

can draw is finite, and dissipating heat effectively from these chips poses a significant challenge. Consequently, the 'Dark Silicon' phenomenon arises, evidenced by over half of a processor chip remaining inactive at any one time due to power constraints [38]. Fig. 1.5 depicts this phenomenon where the clock frequency, directly linked to power usage and system performance, plateaued recently. These trends underscore that enhancements in system performance can no longer rely solely on escalating clock frequencies and core counts.

| Intel Processor                | <b>Transistor Count</b> | Year |

|--------------------------------|-------------------------|------|

| Intel 4004                     | 2300                    | 1971 |

| Intel 8086                     | 29000                   | 1978 |

| Intel i860                     | 1000000                 | 1989 |

| Pentium 1                      | 3100000                 | 1993 |

| Pentium 4                      | 112000000               | 2004 |

| Core i7                        | 731000000               | 2008 |

| Quad-core + GPU i7             | 1160000000              | 2011 |

| Quad-core + GPU i7 Ivy Bridge  | 1400000000              | 2012 |

| Quad-core + GPU GT2 i7 Skylake | 1750000000              | 2015 |

| 28-core Xeon Plantinum 8180    | 800000000               | 2017 |

Table 1.1: The number of transistors in different generations of Intel processors over the years.

Figure 1.5: Maximum clock frequency achieved by a range of processors across the last several decades [39].

• **ILP Wall:** Instruction Level Parallelism (ILP), which enables the simultaneous execution of multiple instructions, is another potential route for boosting system performance. However, its efficiency is contingent on the innate parallelism of the applications or algorithms. Beyond this threshold, increasing hardware parallelism does not correspondingly raise performance levels. Fig. 1.6 contrasts the predicted performance enhancement per Moore's Law with the actual performance boost as the transistor size is reduced. A key factor contributing to this discrepancy is the inherent limit on application parallelism.

Figure 1.6: Speedup across various process technology nodes, encompassing all organizations and topologies of PARSEC benchmarks [38].

• **Memory Wall:** While processors have seen substantial improvements in energy efficiency and performance, data transmission through I/O ports has lagged behind in terms of progression. As previously mentioned, communication between the processor and off-chip memories, including primary and secondary memory, takes a minimum of 200 CPU cycles [35], and it consumes significantly more power than an internal CPU floating-point operation [36, 37]. Additionally, the volume of data transferable concurrently is capped by the chip's I/O port count. This phenomenon is known as the memory wall. The memory wall significantly influences a system's efficiency, both in energy consumption and performance terms.

These architectural limitations motivate us to seek alternative architectures that can tackle power, ILP, and memory walls and enable our continual improvements regarding performance and energy.

To make matters worse, as discussed previously, the data working set size of modern applications such as Machine Learning or genomics is rapidly growing. The features and requirements of modern applications, with the existing challenges of traditional computing systems, push main memory to quickly become a significant bottleneck across a wide variety of applications, such as those in Machine Learning (ML) and genomics. This happens because such applications require continuous data movement between the compute and memory units in such systems, making memory the system bottleneck. This dilemma, also known as the **data movement bottleneck**, only worsens as this performance and energy consumption gap between two units grows and the sizes of applications' data working set increase. For example, previous works in 2013, 2014, and 2018 [40–42] report that data movement accounts for 35%, 40%, and 62% of the total system energy in various such workloads, respectively.

To alleviate data movement bottleneck, recent works prompt re-examining an old idea, interchangeably called Processing-In-Memory (PIM) or Computation-In-Memory (CIM). The key idea behind CIM is to place some form of computing capability near or inside memory where the data is stored. This can be inside the memory chips, in the memory controllers, within the caches, or in the logic layer of 3D-stacked memories. CIM is a computational paradigm, and architectures that utilize CIM (i.e., CIM architectures) can potentially resolve some of the problems discussed in the von-Neumann architecture by reducing or completely eliminating the data movement between where the computation is performed and where the data is stored.

Note that the idea behind CIM architectures has been around in the field for more than five decades [43–61]. Historically, prior endeavors were not widely adopted due to three main reasons. (1) Challenges associated with combining processing units with conventional main memories (i.e., DRAM), (2) the memory scaling issues prevalent in contemporary technology and applications, and (3) the less significant impact of data movement of traditional applications constraints on system expense, energy, and performance.

However, as we discussed before, the new requirements of modern applications and advancements in contemporary memory architectures, such as the 3D-stacked combination of logic and memory or emerging memory technologies such as memristors, an array of CIM architectures have been investigated in recent studies for various applications [42, 62–99].

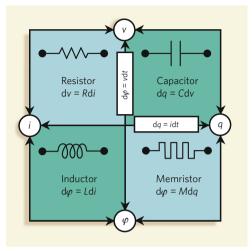

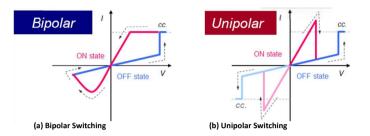

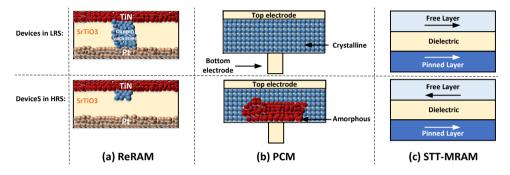

Moreover, looking at it from a technology viewpoint, emerging (memory) technologies, such as memristive devices and circuits based on integrated photonics, hold the promise to supplant conventional memory systems, thereby dealing with or mitigating the problems highlighted earlier. The primary technologies in the memristive sphere are phase change memory (PCM), spin-transfer torque magnetic random-access memory (STT-MRAM), and resistive random-access memory (ReRAM). Unlike traditional memories, which use the presence or absence of charge to represent data, these devices denote data as varying resistance levels, making them non-volatile compared to SRAMbased cache and DRAM-based primary memory. This property lowers the memory's static power consumption, thereby addressing the leakage wall. Regarding physical size, memristors are compact compared to SRAM but align with the size of DRAM or flash memories. Yet, some types of memristive technology permit the storage of multiple bits in a single device, which effectively increases the density. The read and write latency of these devices aligns with that of DRAM and is notably faster than flash memory. Note that even though these devices lag behind SRAM and DRAM regarding endurance and programming energy, they still outperform Flash memories [100–102]. Lastly, as the fabrication processes are still under development, these devices are subject to various imperfections, which may potentially lower their reliability. Numerous research efforts are currently underway to rectify the inconsistencies and non-idealities found in these devices [103, 104].

Therefore, the importance of revisiting CIM in the current times cannot be overstated, using a rejuvenated viewpoint that embraces innovative methodologies and concepts. This should involve the utilization of the latest memory technologies, consideration of practical systems and applications, and an attitude oriented towards simplifying its assimilation and practicality. 1

### **1.3.** PROBLEM DISCUSSION

No matter the strategy implemented for a CIM design for better performance and/or energy efficiency of a modern application, significant practical hurdles exist that both system designers and developers must confront to facilitate its universal acceptance within the computational field and across varied workload domains. Below, we list some open questions and research opportunities at various level of the problem stack that needs to be resolved before CIM adoption for modern applications becomes a reality.

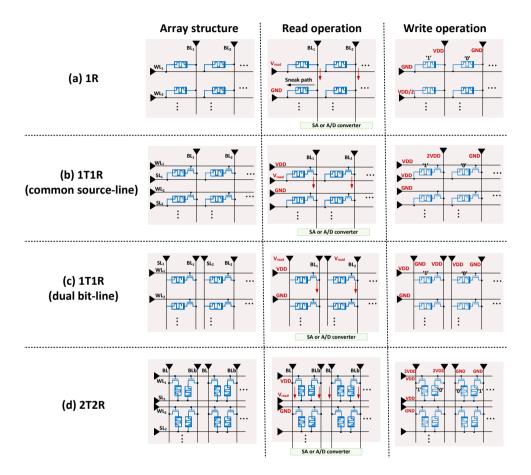

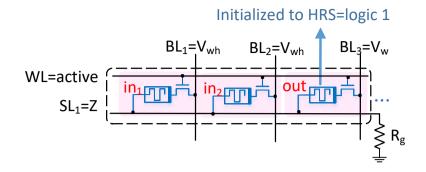

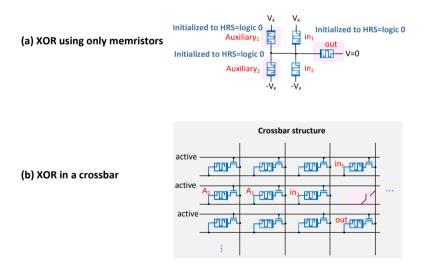

- **Circuit Level.** CIM fundamentally relies on the connectivity between memory devices. To date, previous works [87, 105–107] propose numerous array structures and circuit designs that enable distinct basic operations or facilitate the execution of the same operations in varying manners. Basic operations, such as logical ones, serve as the foundational elements for more complex operations, and their efficiency dramatically impacts the entire system. In addition to the array structure and operations, the inclusion of various analog and digital peripheral circuits is necessary to utilize computation within a memory array fully. However, the design of circuits for CIM is still in its infancy, necessitating further research to discover the most effective design solutions.

- Architecture Level. A CIM architecture also requires consideration of numerous architectural factors due to their potentially substantial impact on the system's performance, energy consumption, size, and even accuracy (at the application level). Although some previous works [69, 108–110] touch base on these matters, more research is required to find the most optimal solutions for managing memory arrays, a potentially specific instruction set dedicated to controlling CIM operations, and tailored communication networks for the system's needs to manage data across multiple memory arrays that might be involved in one application.

- **Compiler Level.** While CIM circuits and architectures can facilitate certain operations within memory arrays, there is a need for a compiler that can dissect an application into sections that can be performed within the memory, breaking it down into operations and instructions the memory can understand. In addition, the manner in which data is arranged in the memory, considering the system's requirements and constraints, can have a significant effect on the system's metrics. Since CIM itself is still in its early developmental stages, optimized compilers for CIM systems have only received minimal attention up to this point [111–113].

- Algorithm and Application Level. A CIM design only suits specific algorithms and applications that are data-intensive, and their operations are supported by the underlying architectures and circuits. Some previous works [108, 114, 115] already target this research direction. However, extensive research is needed to profile the applications, find the suitable ones for a CIM design, and then make the necessary adjustments (e.g., changes to the algorithmic, providing support for the necessary data flow at the architecture and circuit levels, or adjusting the application to tolerate the potential accuracy or performance losses due to device non-idealities) to enable the execution.

A true CIM design can execute the right application or workload and achieves improvements in the application metrics (such as execution time, energy efficiency, etc.) using a tailored (general or specific) algorithm, compiler, architecture, data flow, circuit, and device.

## **1.4.** SOLUTION DIRECTION AND RESEARCH TOPICS

In this dissertation, we seek to investigate (1) acceleration and efficient execution of two application domains, namely genomics and ML, and (2) a few emerging memory technologies and circuit and architectural techniques that might benefit us in a CIM design, having our genomics and ML applications in mind.

We divide the research to be done to achieve these investigations into two steps:

- Identifying and improving the bottlenecked performance of potential kernels in genomics and ML.

- Exploiting emerging technologies to design a state-of-the-art CIM architecture that benefits the target kernels with an end-to-end improvement goal in mind.

Through this integrated approach, we aim to drive transformative advancements in these fields.

### 1.4.1. IDENTIFY AND IMPROVE BIOINFORMATICS AND NEURAL NETWORK KERNELS USING CIM

We target two application domains: genomics and ML. The applications in these domains have different functions or kernels in that a designer must be well-versed. Different functions may involve different data and control flows and may necessitate diverse features to be activated in a von-Neumann architecture or a CIM one. To enhance the efficiency of each function, we first profile them separately and then investigate the optimal ways to map them onto the memory. We also evaluate the necessary components needed alongside the memory array. It is important for a designer to be well-versed in the applications that can be run on a CIM system using emerging memory technologies. Gaining a comprehensive understanding of CIM's principal attributes and a clear perspective regarding CIM's entire breadth is crucial before embarking on its adoption. We aim to collect pivotal data and distill them to their essence. This process could illuminate existing design alternatives and the areas that require additional focus. This valuable insight may assist in pinpointing potential future trajectories, such as supported kernels and their benefits and overheads.

### **1.4.2.** EXPLORING EMERGING (MEMORY) TECHNOLOGIES FOR CIM

Exploring emerging (memory) technologies, such as memristive devices (e.g., PCM and STT-MRAM) that offer several properties such as non-volatility, compactness, and inherent capability for performing logical operations (e.g., logical AND), or integrated photonics that offer high frequency and low latency operations is essential for enhancing the CIM paradigm one step further. We aim to consider multiple of these technologies and use their unique features to build a CIM design that can beat the SotA alternative in one or several comparative metrics such as execution time and/or energy consumption.

### **1.5.** THESIS STATEMENT

Our approach is encompassed by the following thesis statement:

CIM can improve the performance of multiple Genomics pipelines and Machine Learning applications.

To do this, our methods require solving the aforementioned issues with traditional systems and recent CIM works. Therefore, this dissertation addresses the following open questions.

- What kernels or pipeline stages of genomics studies or ML applications can benefit from CIM?

- What is the best memory technology used for such CIM designs?

- What architectures are of potential directions to consider?

- Can we efficiently deploy CIM for our applications using the best memory technologies?

- What does the term "efficiently" means for each kernel and application domain?

## **1.6.** CONTRIBUTIONS

This dissertation makes the following contributions, addressing the discussed research topics and embracing the thesis statement:

- *Evaluation of CIM potential for accelerating basecalling.* We identify an acceleration opportunity for basecalling, the very first computational step in any genome analysis study. We propose a novel hardware/software co-design framework that can effectively accelerate the state-of-the-art Deep Neural Network-based basecalling step on a widely accepted CIM architecture using emerging memristor devices. This framework enables us to, for the first time, to the best of our knowledge, account for the effects of existing non-idealities in the underlying memristors on the end-to-end accuracy of an application that requires significant acceleration but cannot tolerate accuracy loss. We publish this work in [116].

- *A pre-alignment filtering algorithm for short read filtering using CIM.* We first identify that SotA pre-alignment filters for short reads are the (new) performance bottleneck to focus on in a genome analysis pipeline that requires sequence alignment of short reads. We then establish that even pre-alignment accelerators on graphics processing units (GPUs) or field-programmable gate arrays (FPGAs) still do not resolve this performance bottleneck and are themselves limited by the rate at which the data is being fed to them. We propose a hardware/software co-designed (HW/SW co-designed) accelerator based on CIM capable of pre-alignment filtering for short-sequence alignment. We first propose a lightweight and hardware-friendly filtering algorithm. We then exploit emerging non-volatile memories as underlying devices for hardware acceleration. We publish this work under [117].

- *A CIM architecture for short-read pre-alignment filtering.* We profile all the previous pre-alignment filters for short-sequence alignment and discover that they share most of their kernels. We propose a CIM architecture capable of handling these shared kernels. We show that our architecture can accelerate the overall prealignment filtering of short reads by removing the overhead of data movement for all the essential kernels. We extensively evaluate the architecture for previous prealignment filters. Our design can also support any future filter as long as they also require similar kernels. We show this by taking our previous filtering algorithm discussed previously, although it was not involved in our profiling study. We publish this work in [118].

- *An algorithm and CIM architecture for pre-alignment filtering of long reads.* We acknowledge the industry's move towards sequencing long reads. We devise an enhanced data handling and architecture to allow pre-alignment filtering for long reads. Our architecture is based on CIM to take into account that with moving from long reads to short reads, the data movement increases, which can negatively affect the performance. We publish this work in [119].

- *A high-performance and energy-efficient food profiler using CIM.* We pinpoint two critical sources of inefficiency in SotA profilers currently used for food monitoring: (1) requirements for high-end servers with large storage and memory and (2) random accesses to large working datasets, incurring unnecessary data movement. We propose an end-to-end, hardware/software co-designed food profiling framework that efficiently profiles species of a food sample. We reduce the food profiling problem to a multi-object (multi-species) classification problem using hyperdimensional (HD) computing (HDC) followed by an abundance estimation step. We propose a CIM accelerator to mitigate the costs of data movement and shift operations in our HDC solution and simultaneously solve the second problem of profilers as well. This work has been published in [120].

- *A CIM method for k-mer matching and framework for taxonomic profiling.* We build the first hardware/software co-designed framework for taxonomic profiling that exploits *real* memristor (i.e., STT-MRAM) devices and the CIM paradigm. We propose an optimized framework for accelerating Kraken2<sup>1</sup> that notably improves execution time and energy consumption of taxonomic profiling with a negligible area overhead. We achieve this by proposing a memristor-based substrate, called *TL-PIM*, that accelerates the bottleneck of Kraken2 (and many other profilers), the *Table Lookup* operation. We publish this work in [121].

- *A high-performance data mapping for Binary Neural Network using CIM.* We advance SotA CIM accelerators for BNNs by providing a highly parallel data mapping that is compatible with any CIM design capable of performing VMM, e.g., memristor-based crossbars such as ePCM-based or ReRAM-based ones. Our proposed data mapping is designed with the conventional 1T1R memory crossbar

<sup>&</sup>lt;sup>1</sup>Kraken2 is currently the most widely-used and one of the most promising taxonomic profilers based on recent metagenomics challenges.

structure in mind and is, therefore, compatible with many of the already evolving crossbar architectures. We publish this in [122].

• *A CIM accelerator based on optical phase change material for Binary Neural Network.* We propose an oPCM hardware-based CIM implementation incorporating our discussed optimized data mapping for BNNs. Our accelerator ensures maximum parallelism through exploring the potential provided by the features of CIM architecture and the inherent properties of oPCM (via wavelength division multiplexing (WDM). Our design realizes an order of magnitude improvement in latency/throughput without losing the accuracy of the network. We publish this in [123].

## **1.7.** THESIS OUTLINE

- This dissertation is organized into fourteen chapters.

Chapter 2 introduces CIM and its classifications, emerging memory technologies, genomics pipelines, and Neural Network. We first discuss the history of CIM and its types. We then present a background on two emerging technologies: resistive memory devices and integrated photonics. We then introduce two application domains that we believe can benefit from these computing and technological paradigms.

Chapter 3 explores CIM for the acceleration of basecalling, an important step in genomics pipelines. We first provide a background on what basecalling is and what the issues are with SotA basecallers. We then propose a hardware/software co-designed framework to analyze (1) the potential of CIM for basecalling acceleration and (2) strategies to mitigate the possible negative effects of non-idealities. We evaluate the SotA basecaller on a SotA CIM architecture and provide key suggestions and recommendations for system designers of future emerging accelerators for basecalling.

Chapter 4 targets CIM acceleration for another step in the genomics pipeline, prealignment filtering. We first introduce pre-alignment filtering, where it exists, and how it helps the general pipeline. We target pre-alignment of short genomic sequences (called short reads), as currently, the majority of our genomic data are in the form of short reads. We then present a lightweight algorithm that is compatible with CIM architecture.