# SC52045 M.Sc. THESIS REPORT

# TOPOLOGY GENERATION WITH DETAILED COMPONENT DESCRIPTION AND AVOIDANCE OF ISOMORPHIC TOPOLOGIES

by

#### Marco Delgado Schwartz (4268083)

MSc thesis main supervisor: Dr. Peyman Mohajerin Esfahani

Literature review daily supervisor: Dr. Shengling Shi

Thesis daily supervisor: | Phd. Mohammad Boveiri

Company (TNO) supervisor: Dr. Steven Wilkins

Delft Center of Systems & Control (DCSC)

Technical University of Delft

August 19, 2024

Delft, Netherlands

### **PREFACE**

The European Union (EU) has set the goal to have a carbon-neutral economy by 2050 [1]. To achieve this, a key sector to focus on is the transportation sector [2, 3]. It will be especially challenging though to decarbonise the larger vehicles from the transportation sector, the trucks, ships and airplanes [3].

The typical way to respond to this or any other design challenge is by making use of the top-down/sequential design process, where first the larger parts of the design are established, and later the finer details are developed. However such an approach cannot guarantee that the design at the end is optimal or anywhere close to it [4, 5]. This makes the sequential design approach ill-suited to tackle the challenge of decarbonising the EU transportation sector. Co-Design on the other hand, a simultaneous design approach, can guarantee optimality [4, 5], and would be a much more appropriate approach if it wasn't for it being limited to only consider around 10-20 components [6, 7, 8, 5].

The work in this report first investigated where this limitation of 10-20 components comes from. It is described how the problem's source does not originate from topology optimisation, where most research has gone into, but rather that it originates from the topology generation process. The suspicion was that the vast number of isomorphic topologies that are created during the topology generation process make the topology generation process intractable with the current methods when considering more than 10-20 components. Adding more data to describe the components in more detail or adding multiple instances for each component that can be used multiple times across a design only increases the number of isomorphic topologies even further, and with it the computational cost to complete the topology generation process. Since the results of the topology generation process are fed to the topology optimisation process, the entire Co-Design process is then influenced by these isomorphic topologies.

The work that follows therefore focused on topology generation for Co-Design by testing a candidate method that allows topologies to be generated without any of the isomorphic topologies while describing components in more detail than what has been done in literature. The approach taken here relied, unlike what has been done so far, on the use of adjacency matrices and the interconnected system model. With this, new insight into topology generation for Co-Design was developed. The use of adjacency matrices were also key to automate the formation of constraints, which allowed to generate topologies for any set of components, also a first in the literature. The program TopoGen was developed to make this possible. The results that were obtained showed how using requirement chains and ordering instances, at least in simple cases, the 10-20 components limitation is fully overcome. This confirmed that the presence of isomorphic topologies the cause was for 10-20 components limitation in Co-Design. Still, for more complex cases, mistakes were present. However it was also shown how these too may be prevented in the future. This means that with further research and development, the candidate method presented here can be adjusted so that Co-Design can be applied even to complex cases, and therefore be used to develop solutions needed to decarbonise the EU transportation sector.

The report is structured as follows: After the introduction in chapter 1, in chapter 2 the current methods around Co-Design are reviewed. It is revealed that the sub-process of topology generation the reason is as to why Co-Design is restricted to such small sets. This leads to defining the research questions, which are presented in section 2.3. The research questions define the research scope of this thesis, and are all focused on the topic of topology generation for Co-Design. The sections that follow, in chapter 3, present the work that has been done to answer these questions, as well as the results that were obtained along the way. In section 3.1, the basic setup that was used is presented. The sections that follow, from section 3.2 to section 3.4, build on this setup and present intermediate results. In section 3.5 then the candidate method to generate topologies without ismorphic topologies is presented and the test results are shown. The report is finally wrapped up in chapter 4 by summarising the contributions that have been made towards the research questions, as well as presenting a list of recommendations on how to continue the research.

I would like to thank all of my supervisors for the patience and support they have given me throughout my thesis work. From the beginning Peyman has been vocal and proactive in helping me find a topic I was passionate to work on. Shengling guided me through the literature review, and helped me condense my ideas into useful research building blocks. These eventually made me come across the work done by TNO in the field of Co-Design. Upon contacting them on their work, and presenting them what I had been working on so far and planning to do next, Steven invited me to complete my graduation work at their research department. Since then he has been helping me with useful reviews of my work and progress, exposed me to relevant research and ideas, and ensured I could complete my research work at TNO despite it taking longer than expected. On the university side, Mohammad replaced Shengling after Shengling had left for his Post-doc position at MIT. Mohammad has been a reliable contact person throughout my research project. I was able to approach him at all times and he assisted me through the questions I had or the difficulties I had encountered.

Thanks to the freedom and support I was given throughout my entire thesis, I was able to develop and research a topic I was passionate about. While I may have achieved now enough results to finish, and seem to have even made some noteworthy contributions to the field of Co-Design, I by no means feel like I am done. I feel like I am just getting started. What better feeling is there to finish one's engineering MSc?

# **NOMENCLATURE**

#### **Abbreviations**

| CLD         | Component Level Description                                |

|-------------|------------------------------------------------------------|

| CPG         | Constrained Permutation Generator                          |

| CSP         | Constrained Satisfaction Problem                           |

| EU          | European Union                                             |

| FRD         | Functionalities-Requirements-Diagram                       |

| IEA         | International Energy Agency                                |

| ISM         | Interconnected System Model                                |

| MRQ         | Main Research Question                                     |

| PLD         | Port Level Description                                     |

| PPLD        | Property-Port Level Description                            |

| SAT         | Satisfiability Problem                                     |

| SRQ-i       | Supplementary Research Question i                          |

| TF          | Feasible topologies                                        |

| TP          | Potential topologies                                       |

| TPB         | Potential topologies with bijective connections            |

| TPBC        | Potential topologies with bijective compatible connections |

| UAL         | Unweighted Adjacency List                                  |

| UAM         | Unweighted Adjacency Matrix                                |

| Opera       | tors                                                       |

| $(f, \geq)$ | Upper bound of the function $f$                            |

$(f, \leq)$  Lower bound of the function f

- [·] List operator, such as the list of property ULIDs [P-ID]

- [P-ID]<sub>[C-ID,V-ID]</sub> List of property ULIDs, sorted first by the order of the component ULIDs, and then the unit type ULIDs.

- [a..b] List of integers from a to b

- Fuzzy/Boolean composition operator

- $\ell(v)$  Length operator, which provides the number of elements in v.

- $\ell_n(M)$  Length operator, which provides the number of elements in axis n of the matrix M. (0 for rows, 1 for columns).

- $\wedge$ /. Logical and operator

- $\langle \cdot \rangle$  Type operator, such as the node type  $\langle N \rangle$

- ∨ Logical or operator

- $\mu([L_1] \times [L_2])$  Membership operator, that defines which elements in  $L_1$  and  $L_2$  belong together.

- $\mu_r([L_1] \times [L_2])$  Reduced membership operator, that defines which elements in  $L_1$  and  $L_2$  belong together, but removing all rows and columns that have no connections.

- $\nu([L_1] \times [L_2])$  Potential connections operator, that defines which elements in  $L_1$  and  $L_2$  might belong together.

- × Cartesian cross product

- $\zeta([L_1] \times [L_2])$  Compatible connection operator, that defines which elements in  $L_1$  and  $L_2$  are compatible with each other.

#### **Variables**

- $(V_i, V_i)$  Edge between node i and node j

- [C-ID] List of component ULIDs

- [D-ID] List of domain type ULIDs

- [H-ID] List of instance ULIDs

- [N-ID] List of node type ULIDs

- [P-ID] List of property ULIDs

- [R-ID] List of port ULIDs

- [T-ID] List of component type ULIDs

#### [V-ID] List of unit type ULIDs

- B Boolean number set

- $\mathbb{R}$  Real number set

- $\mathbb{Z}$  Integer number set

- $\mathcal{C}$  Set of constraints for CSP

- $\mathcal{D}$  Set of domains for CSP

- $S_c$  Set of components

- $S_r$  Set of requirements

- $\mathcal{T}_f$  Set of feasible topologies such that  $\mathcal{T}_f \subseteq \mathcal{T}_{p,bc} \subseteq \mathcal{T}_{p,b} \subseteq \mathcal{T}_p$

- $\mathcal{T}_p$  Set of potential topologies such that  $\mathcal{T}_p := \{M_0..M_{\ell_0(M)\ell_1(M)}\}$

- $\mathcal{T}_{f,q}$  Number of branches in requirement chain, used to count feasible topologies from requirement chain.

- $\mathcal{T}_{f,r}$  Number of components that meet output requirement, used to count feasible topologies from requirement chain.

- $\mathcal{T}_{p,bc}$  Set of potential topologies with bijective compatible connections such that  $\mathcal{T}_{p,bc} \subseteq \mathcal{T}_{p,b} \subseteq \mathcal{T}_p$

- $\mathcal{T}_{p,b}$  Set of potential topologies with bijective connections such that  $\mathcal{T}_{p,b} \subseteq \mathcal{T}_p$

- $\mathcal{X}$  Set of variables for CSP

- $\mathcal{X}_e$  Set of edge variables

- $\mathcal{X}_n$  Set of node variables

- *u* Input vector

- y Output vector

- L Local map UAM

- $L_n$  Local map UAM of component n

- M Feedback gain of ISM/Connection UAM

- *Q* The UAM which specifies the connections from input ports to output ports.

- r Number of connections placed between available ports

- $R_u$  Number of input ports

- $R_y$  Number of output ports

- u Input from u; Input set from node type.

- $V_i$  Node i

- *y* Output from *y*; Output set from node type.

# **CONTENTS**

| Pr | eface | •              |                                                                        | i        |

|----|-------|----------------|------------------------------------------------------------------------|----------|

| No | omen  | clatur         | e                                                                      | iii      |

| 1  | Intr  | oducti         | on                                                                     | 1        |

| 2  | Cur   | rent M         | ethods & Research Question                                             | 4        |

|    | 2.1   |                | nt Methods                                                             | 4        |

|    | 2.2   |                | ations                                                                 | 7        |

|    |       | 2.2.1          | Problem 1: Rewriting constraints                                       | 7        |

|    |       | 2.2.2          | Problem 2: Slow topology generation                                    | 7        |

|    |       | 2.2.3          | Problem 3: Isomorphic topologies                                       | 8        |

|    |       | 2.2.4          | Conclusion on limitations                                              | 11       |

|    | 2.3   | Resea          | rch Question                                                           | 12       |

| 3  | Met   | hodolo         | ogy & Results                                                          | 14       |

|    | 3.1   | Basic          | Setup                                                                  | 16       |

|    |       | 3.1.1          | Interconnected System Model for Topology Generation                    | 16       |

|    |       | 3.1.2          | Component Description and Composition                                  | 18       |

|    |       |                | 3.1.2.1 Node, Unit and Domain types                                    | 18       |

|    |       |                | 3.1.2.2 Use IDs to record properties and types                         | 19       |

|    |       |                | 3.1.2.3 Ports, instances, components and component types               | 20       |

|    |       |                | 3.1.2.4 Defining memberships and compositions                          | 22       |

|    |       |                | 3.1.2.5 Local maps and connection matrix                               | 25       |

|    |       | 3.1.3          | Validation Tests                                                       | 27       |

|    |       |                | 3.1.3.1 The 3BT-3EM test                                               | 27       |

|    |       |                | 3.1.3.2 The ISO-car test                                               | 28       |

|    |       | 0.1.4          | 3.1.3.3 The Loops & Branches test                                      | 29       |

|    | 0.0   | 3.1.4          | TopoGen Python Program                                                 | 31       |

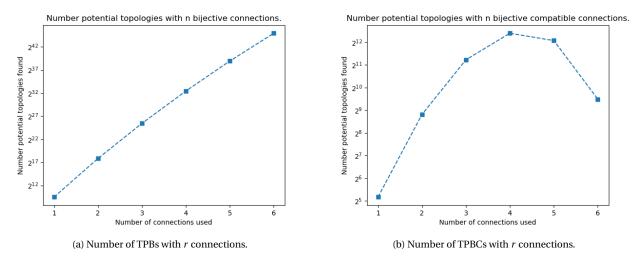

|    | 3.2   |                | tial topologies without constraints                                    | 35       |

|    | 3.3   |                | tial topologies with bijective connections                             | 36       |

|    |       |                | Why use the port-to-port constraint?                                   | 36<br>37 |

|    |       | 3.3.2<br>3.3.3 | Number of potential topologies with bijective connections              | 38       |

|    |       |                | Conclusion                                                             | 40       |

|    | 3.4   |                | tial topologies with bijective compatible connections.                 | 41       |

|    | J.T   |                | Defining the compatibility matrix                                      | 41       |

|    |       | 3.4.2          | Number of potential topologies with bijective compatible connections   | 43       |

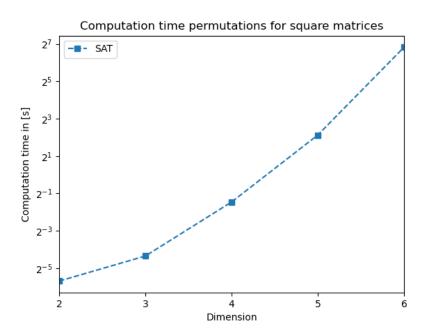

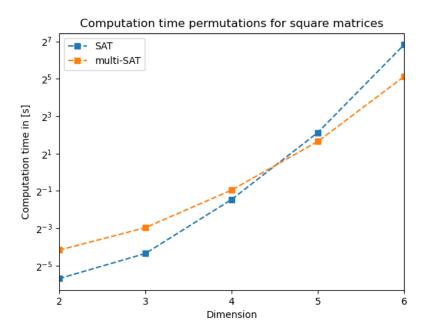

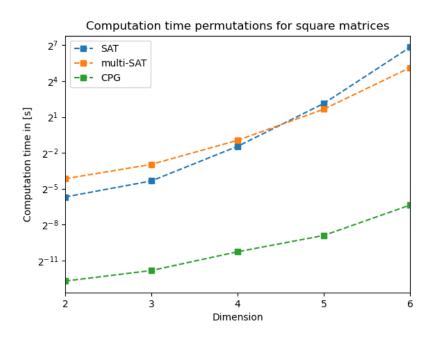

|    |       | 0.1.2          | 3.4.2.1 SAT solvers to find potential topologies                       | 44       |

|    |       |                | 3.4.2.2 Constrained Permutation Generator to find potential topologies |          |

|    |       | 3.4.3          | Conclusion                                                             | 51       |

|    | 3.5   |                | ole topologies without isomorphic topologies                           | 52       |

|    |       |                | Method to avoid isomorphic topologies                                  |          |

|    |       | 3.5.2   | Require   | ment chains for feasible topologies                          | 53   |

|----|-------|---------|-----------|--------------------------------------------------------------|------|

|    |       |         | 3.5.2.1   | Example for requirement chains method                        | 53   |

|    |       |         | 3.5.2.2   | Method for requirement chains while avoiding isomorphic topo | olo- |

|    |       |         |           | gies                                                         | 55   |

|    |       |         | 3.5.2.3   | Presenting the Result of the Requirement Chain               | 58   |

|    |       |         | 3.5.2.4   | Counting number of feasible topologies                       | 59   |

|    |       | 3.5.3   | Feasible  | topologies for the 3BT-3EM test                              | 60   |

|    |       | 3.5.4   | Feasible  | topologies for the ISO-car test                              | 62   |

|    |       | 3.5.5   | Feasible  | topologies for the Loops & Branches test                     | 65   |

|    |       | 3.5.6   | Conclus   | ion                                                          | 70   |

| 4  | Con   | clusio  | 1 & Reco  | mmendations                                                  | 71   |

|    |       | 4.0.1   | Contrib   | utions towards SRQ-2                                         | 71   |

|    |       | 4.0.2   | Contrib   | utions towards SRQ-1                                         | 72   |

|    |       | 4.0.3   | Contrib   | utions towards MRQ                                           | 73   |

|    | 4.1   | Recon   | nmendat   | ions for future work                                         | 75   |

|    |       | 4.1.1   | Improve   | ements to the PPLD                                           | 75   |

|    |       |         | 4.1.1.1   | Building set of components                                   | 75   |

|    |       |         | 4.1.1.2   | More consistency for the PPLD                                | 75   |

|    |       |         | 4.1.1.3   | Expand the component description                             | 75   |

|    |       |         | 4.1.1.4   | More flexibility for connections                             | 76   |

|    |       |         | 4.1.1.5   | Minimising data storage of the sparse UAMs                   | 76   |

|    |       | 4.1.2   | Improve   | ements for the generation of TFs                             | 78   |

|    |       |         | 4.1.2.1   | Review validation tests                                      | 78   |

|    |       |         | 4.1.2.2   | Explore difference between SAT and CPG                       | 78   |

|    |       |         | 4.1.2.3   | Constraints for SAT solver for feasible topology generation  | 78   |

|    |       |         | 4.1.2.4   |                                                              | 78   |

|    |       |         |           | Use matrices to produce requirement chains                   | 78   |

|    |       |         | 4.1.2.6   | Developing topologies on different sets                      | 80   |

| Bi | bliog | graphy  |           |                                                              | 81   |

| A  | Imp   | ortant  | definitio | ons                                                          | 85   |

|    | _     |         |           | tion                                                         | 85   |

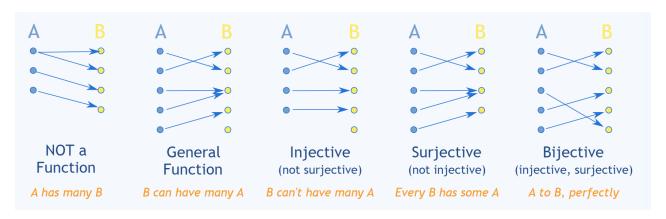

|    | A.2   | •       |           | & Permutations                                               | 86   |

|    | A.3   |         |           | ctive and Bijective Functions                                | 87   |

|    | A.4   | Stirlin | g's appro | ximation                                                     | 88   |

|    |       |         |           | Pseudo-Roolean constraints                                   | 89   |

1

### INTRODUCTION

The European Union (EU) has set the goal to have a carbon-neutral economy by 2050 [1]. In 2020 the transportation sector was responsible for about one-fifth of the global carbon dioxide emissions, with 45% of the emissions coming from cars, 30% from trucks, 12% from airplanes, and 11% from ships [9]. However, as is explained in [2], between 1990 and 2018, while all other sectors have been able to reduce their emissions, the transportation sector has instead been increasing them. Moreover, projections show that from 2019 to 2070, global transport (measured in passenger kilometres) will double, the number of passenger and freight airplanes will triple, and car ownership will increase by 60% [3]. Emissions from shipping alone could increase up to 130% by 2050 from 2008 levels [10]. In order to meet the goal of carbon neutrality by 2050 set by the EU, the transportation sector is therefore a key sector to focus on.

However, this comes with several complications. For one, while the International Energy Agency (IEA) acknowledges the rapid progress that is being made in reducing the emissions from cars, it also states that it will be significantly harder to do this with trucks, ships and airplanes due to their increased size and complexity [11, 3]. Additionally the service life of ships and airplanes are around 30 years, and the current fleet is only halfway through this life [12, 3]. That means that only around 2040, if alternatives exist, these ships and airplanes will start to be replaced. Indeed, the IEA points at ships and airplanes to be the last ones to reduce their emissions [3]. However, even before 2040, and assuming the technology is mature enough, it also takes roughly five to ten years to design a new ship or airplane [13, 14, 15, 16] in the first place. Additionally, it is not just that ships or airplanes need to be redesigned, but also that the technologies that will make it possible to reduce or eliminate their emissions will also require major changes in the supply chain and the infrastructure that are needed for their construction, maintenance and operation [3]. All of this leads to the IEA describing that "reducing CO2 emissions in the transport sector over the next half-century will be a formidable task" [3]. Solutions need to be developed now so that this transition becomes successful.

Reducing CO2 emissions in the transport sector over the next half-century will be a formidable task. It will require structural shifts in the modes used to move people and freight, a shift to low-carbon forms of energy and a stronger focus on using energy more efficiently. This calls for a broad mix of technologies, many of which are at the early stages of development and commercialisation. These include vehicle, powertrain and

engine technologies, and the infrastructure needed to support alternative fuels, as well as digital technologies and software to enable service providers to harness the power of data. (Energy Technology Perspective 2020, IEA. [3])

The usual approach to develop these solutions, designs that meet some set of requirements, is a top-down/sequential design approach. This involves first figuring out the big parts of the design, and then proceeding to figuring out the ever finer details of it. Using this approach it has also been possible to design the trucks, ships and airplanes that operate today.

Nevertheless, as literature explains [4, 5], such a sequential design process comes with several issues. The issues arise from the fact that the first elements that were designed and put into place have been designed without considering the influence of the design elements that are considered in the later stages of the design process. The result is, no matter how rigorous this sequential design process is done, as [4] proceeds to show, there is zero guarantee that the design at the end will be optimal, or anywhere close to being optimal. Additionally, with the increased complexity that comes with bigger vehicles such as airplanes and ships, only few ways of how to assemble the components, the design architecture, can be considered [11]. However, for the energy transition, where new technologies such as batteries or hydrogen fuel cells need to be incorporated [3], multiple design architectures need to be considered. If this however is attempted, with the sequential design approach, again, no guarantee exists that developing these alternatives will be successful or close to performing as well as might be possible or necessary.

Fortunately, an alternative to the sequential design approach exists. This is the simultaneous design approach, more commonly referred to as Co-Design. This approach, unlike the sequential approach, can guarantee that a design ends up being optimal to the requirements it needs to satisfy [5, 4]. While the sequential design approach has the advantage that tasks can be divided and assigned to different people/departments, Co-Design instead is completed as one large optimisation problem with the end result being a tool that can automatically evaluate all possible design architectures, and retrieve the optimal ones.

Such a tool would be extremely helpful to design the solutions required for the energy transition set forward by the EU [17, 5]. Using Co-Design, design architectures that include new technologies can be considered, thereby helping to integrate these alternatives faster into working designs. But even in the case where alternative technologies are not considered, Co-Design can still explore design architectures that have not been examined before, and further optimise existing designs, always with the guarantee of optimality.

Unfortunately though, Co-Design does suffer from one great limitation: It only works when considering at most between 10-20 components for ones design [6, 7, 8, 5]. Beyond that the computational burden of solving the single optimisation problem is so high, it quickly becomes a discussion of having to wait decades or even centuries for one to obtain the optimal design [6].

Still, noteworthy achievements have been accomplished with Co-Design by bypassing the limitation of only being able to consider 10-20 components. For instance, in [5] it is summarised how research has gone into redesigning existing hybrid electric vehicles (HEVs) using the Co-Design approach instead. The redesigned HEVs had significant improvements in performance and reduced emissions. For example, in [18], cited by [5], after redesigning the HEVs considered in the paper, a remarkable 33% decrease in CO2 emissions have been found.

Two strategies are commonly employed to achieve these results despite the 10-20 components

limitation: The first one involves limiting the design architectures to a smaller selection [5], thereby reducing the number of designs to evaluate in the optimisation process behind Co-Design. The second strategy involves combining components together to form fewer but larger components [11], and therefore able to stay under the 10-20 component limitation. Both of these strategies however, due to rejecting in one form or another many of the potential design architectures, sacrifice the most important feature of Co-Design, namely that of guaranteeing the optimality of the final design. Additionally, the sacrifice increases when considering ever-larger vehicles.

Otherwise, the rest of the research effort, as is described in [5], has gone into testing different optimisation algorithms that can handle the highly nonlinear optimisation problem of finding the optimal design architecture from a list of architectures, as well as seeing how these calculations can be sped up. Nevertheless, these do not address the source of the problem, the 10-20 component limitation, as will be explained in chapter 2. The problem namely lies in generating all the different design architectures, i.e. the topology generation.

The research work presented here focuses on this limitation. The hope is that by better understanding how this limitation arises, an alternative approach to topology generation can be assembled, so that Co-Design can executed with plenty more components than just the 10 or 20.

To that end, in chapter 2 first the current methods with respect to Co-Design are described, while introducing important definitions. This is then used to explain from where the 10-20 components limitation comes. All of this put together is used to substantiate the research questions in section 2.3 that are the focus of the research work done here. In chapter 3 the method that was applied to answer these very research questions is presented, showing alongside the results that have been obtained along the way. The section is divided into five parts, where section 3.1 presents the basic setup that was used. The sections that follow, from section 3.2 to section 3.4, build on that setup and present intermediate results. In section 3.5 the candidate method to overcome the 10-20 components limitation is presented, as well as results that have been obtained with it. Finally, in chapter 4, the report is wrapped up by summarising the contributions that have been made towards the research questions. The section ends by providing a list of recommendations on how to continue with the research.

## **CURRENT METHODS & RESEARCH QUESTION**

In the following section, starting with section 2.1, the current methods that are applied for Co-Design are briefly summarised, in context to what will be relevant for the remaining sections hereafter. (For a full review of the current methods that are applied for Co-Design, please refer to [5].) This is then followed by section 2.2, where the most significant limitations of the current methods will be presented. Having described the current methods and limitations, in the final section, section 2.3, the research questions for the thesis are presented.

#### **2.1.** CURRENT METHODS

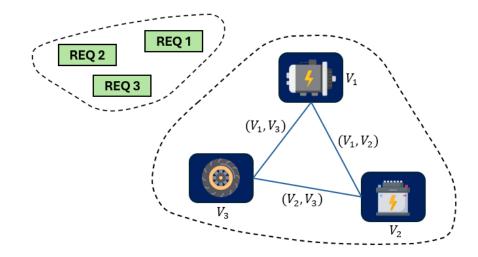

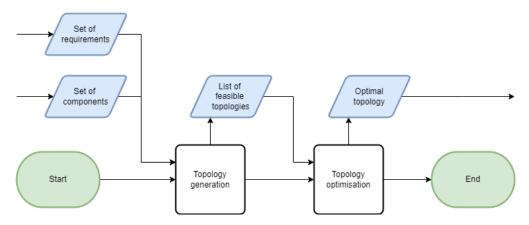

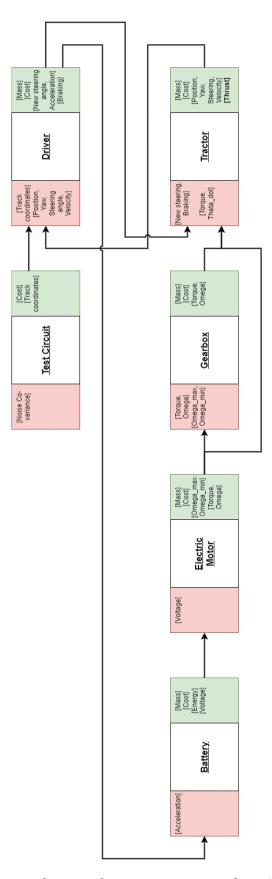

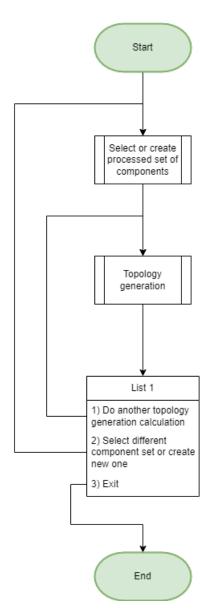

Co-Design is initialised on a set of components  $S_c$  and a set of requirements  $S_r$ , and the goal is to find what components and connections between components should be selected in order to deliver as an output an optimal design that meets the set of requirements. Because components and connections are selected to produce any design, the designs are actually referred to as topologies. In Figure 2.2 a flowchart of the Co-Design process is presented, where the blue parallelograms indicate the data that is being considered, and the two processes that it involves: topology generation and topology optimisation.

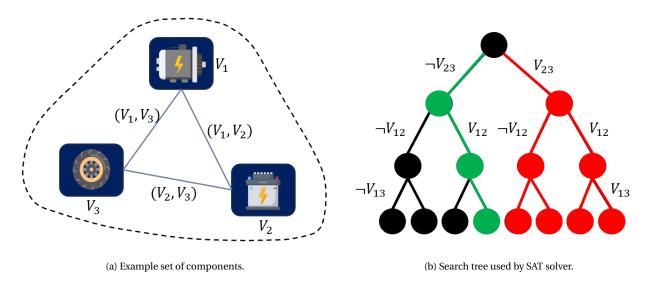

Consider Figure 2.1 as an example for a set of requirements, currently not specified any further, and a set of components with three components, a battery, a wheel and an electric motor. Each component has been given a unique label,  $V_1$ ,  $V_2$  and  $V_3$ . Finally, also the connections one might consider between the components, here represented only as undirected edges, are labelled as tuples of the two components they connect. For example the connection between  $V_2$  (the battery) and  $V_1$  (the electric motor) is labelled as  $(V_1, V_2)$ . (Because here only undirected edges are considered, the equality  $(V_1, V_2) = (V_2, V_1)$  holds.) Once these two sets have been established, topology generation, the first process in Co-Design, is executed, as also shown in Figure 2.2.

The goal of topology generation is to find out which of all the different connections that can be placed, should be chosen, in order to obtain a topology that can fulfil the set of requirements. As is already recognised in [8, 5], this results in a Constrained Satisfaction Problem (CSP), which is defined by a triplet  $(\mathcal{X}, \mathcal{D}, \mathcal{C})$  such that:

- $\mathcal{X} = \{X_1..X_n\}$  is the set of variables for the problem.

- $\mathcal{D} = \{\mathcal{D}_1..\mathcal{D}_n\}$  is the set of domains for each variables such that  $X_i \in \mathcal{D}_i \ \forall i \in [1..n]$ .

Figure 2.1: Example of a set of components  $S_c$  and a set of requirements  $S_r$ .

Figure 2.2: Flowchart of the process behind Co-Design.

• C is the set of constraints such that  $C_{ijk...} \subseteq D_i \times D_j \times D_k \times ...$ , representing a subset of the possible combinations of values of  $X_i, X_j, X_k...$

Considering the example in Figure 2.1 and following the same strategy as in [8], the variables in  $\mathcal{X}$  are each component and connection, i.e.  $\mathcal{X} = \{V_1, V_2, V_3, (V_1, V_2), (V_2, V_3), (V_1, V_3)\}$ . The set of variables  $\mathcal{X}$  can thus be divided into two disjoint sets such that  $\mathcal{X} = \{\mathcal{X}_n, \mathcal{X}_e\}$  :  $\mathcal{X}_n \cap \mathcal{X}_e = \emptyset$ , with  $\mathcal{X}_n = \{V_1, V_2, V_3\}$  representing the components and  $\mathcal{X}_e = \{(V_1, V_2), (V_2, V_3), (V_1, V_3)\}$  the connections. The domain for all variables is  $D_i = \mathbb{B} := \{0, 1\}$ , i.e. components and connections can be turned on or off and can thus be represented as boolean variables. Finally, in [8], the constraints are defined. For example it is defined how many connections each component can make, where when referring back to the example shown in Figure 2.1, one might state that if the battery (an energy source) is selected, i.e.  $V_2 = 1$ , or the wheel (an energy sink), i.e.  $V_3 = 1$ , that both of them can only have one connection. The electric motor on the other hand, if selected, i.e.  $V_1 = 1$ , then it can have two connections. These constraints may be expressed like shown in (2.1):

$$V_2 = (V_1, V_2) + (V_2, V_3)$$

$$V_3 = (V_2, V_3) + (V_1, V_3)$$

$$2V_1 = (V_1, V_3) + (V_1, V_2)$$

(2.1)

Additionally, from the example shown in Figure 2.1, one might state that the connection  $(V_2, V_3)$  never makes sense to place, since there is no compatible connection that can be placed between a battery and a wheel. In such a case a further constraint can be placed such that  $(V_2, V_3) = 0$ . Finally, the set of requirements is also translated as constraints that need to be met. Referring back to Figure 2.1, one might state as a requirement that one would like to have a wheel that spins. This might imply as a constraint that  $V_3 = 1$ .

With this approach [8] proceeds to define the rest of the constraints. The CSP is then solved using Prolog, which, as is explained in [8] is a popular solver to solve CSPs. Any solution that is provided by a CSP solver is referred to as a feasible topology (TF), where each TF specifies the values the variables in  $\mathcal{X}$  take in order to meet all the specified constraints. In the example shown in Figure 2.1, one might obtain then as a TF that the battery needs to be connected to the electric motor, and the electric motor to the wheel. The result could then be presented as shown in Table 2.1:

| $X_i$           | $V_1$ | $V_2$ | $V_3$ | $(V_1, V_2)$ | $(V_2, V_3)$ | $(V_1, V_3)$ |

|-----------------|-------|-------|-------|--------------|--------------|--------------|

| $\mathcal{D}_i$ | 1     | 1     | 1     | 1            | 0            | 1            |

Table 2.1: TF for example shown in Figure 2.1.

As is shown in [8], the assembly of the constraints plays a crucial role. In their case, when using a set of 16 components, i.e.  $|\mathcal{S}_c| = 16$ , 16 variables are needed in  $\mathcal{X}_n$  to specify the selection of the components, i.e.  $|\mathcal{S}_c| = |\mathcal{X}_n|$ . Additionally 136 variables in  $\mathcal{X}_e$  are needed to specify any potential connection between the components. Since undirected edges are considered, the number of potential connections are  $|\mathcal{X}_e| = \frac{1}{2} \left( |\mathcal{X}_n|^2 + |\mathcal{X}_n| \right)$ . This leads to a total of 152 variables in  $\mathcal{X}$ , with the domain of each variable in  $\mathbb{B}$ . Then, without any constraints, the number of potential topologies (TPs) is as shown in (2.2), leading to a total number of 5.7 × 10<sup>45</sup> TPs. This is an enormous number of topologies that amount to a total close to the number of atoms that exist on earth, which is estimated to be at 1.3 × 10<sup>50</sup> [19]. (In fact it would take 18 components instead of 16 to surpass that number.) However, when solving the CSP, only  $|\mathcal{T}_f| = 4'779$  TFs exist.

$$|\mathcal{T}_n| = 2^{\left(\frac{1}{2}|\mathcal{X}_n|^2 + \frac{3}{2}|\mathcal{X}_n|\right)} \tag{2.2}$$

The set of TFs  $\mathcal{T}_f$  is then fed to the next process in Co-Design (see Figure 2.1), topology optimisation, where an optimisation over this list of TFs is executed in order to find the optimal topology, i.e. the topology that satisfies the set of requirements  $\mathcal{S}_r$  at the lowest input cost. The topology optimisation also optimises each component parameter such as the size of the components, as well as developing optimal control for the topology being explored [5]. This leads to a highly nonlinear optimisation problem [4, 5]. As explained in [5], this is also the reason why genetic algorithms or particle swarm algorithms tend to be the algorithms used to complete the topology optimisation, two global search algorithms suitable for the optimisation problem considered the topology optimisation process.

#### 2.2. LIMITATIONS

Having addressed in section 2.1 how the current state of the art deals with Co-Design, in this section, three problems are explained that limit Co-Design to work on only 10-20 components.

#### **2.2.1.** PROBLEM 1: REWRITING CONSTRAINTS

As was explained in section 2.1, the constraints play a crucial role in retrieving the feasible topologies (TFs) in the topology generation process. However, currently, there is no general method that can be applied to develop all of these constraints. Additionally it remains unknown what the impact is of each constraint, i.e. the number of potential topologies (TPs) the constraint eliminates as being not feasible. This leads to two big problems:

First, there is a huge risk that one or another constraint is forgotten. Considering that the number of TPs scales at an approximate rate of  $2^{|\mathcal{X}_n|^2}$  (see (2.2)), and each of the topologies that are not eliminated by the constraints are deemed feasible, the number of TFs one might end up because of a forgotten constraint may make the next process, topology optimisation, prohibitively expensive or downright impossible to complete in full. As is explained in [5], in several studies, only a subset of 4-10 TFs are selected for the topology optimisation. The 4'779 TFs found in [8] are already a challenge. Any constraint that is forgotten can quickly lead to the Co-Design process not being able to be completed at all.

Secondly, the current approach with the constraints forces that with any new set of components, the constraints need to be rewritten. This happens even if the new set of components differs by only one component compared to the original set of components. The consequence is that Co-Design, with the current approach, is an extremely arduous and risky process, as again one may forget a constraint or make a mistake.

Research is therefore needed to produce a reliable method for the constraints used in topology generation. Understanding the impact that each constraint has might help develop such a method.

#### **2.2.2.** PROBLEM 2: SLOW TOPOLOGY GENERATION

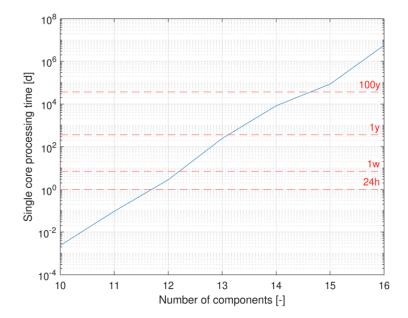

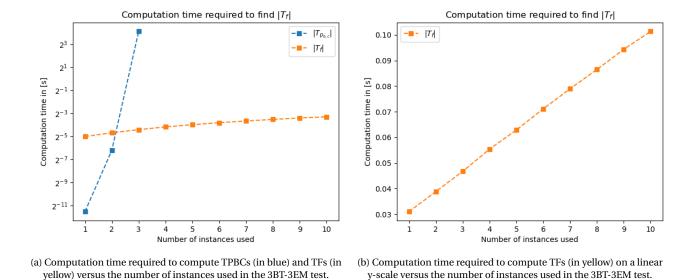

With the current Co-Design approach even with a small set of components, i.e. 10-20 components, the topology generation requires an enormous amount of time in order to complete. Consider the following case studies: In [7], for 11 components, the topology generation took between 45 to 218 seconds to complete, where the calculations were performed on a system using Intel Core i5-M540 @ 2.53 GHz and 8 GB RAM with Win7 and SWI-Prolog 7.4.2. (More on these results in section 2.2.3.) In [8], for the 16 components that they made use of, the topology generation was also completed somewhere under 300 seconds (i.e. under 5 min) with a system using 64-bit Intel(R) Core (TM) i7 @ 2.2 GHz and 8-GB RAM. The work done in [6] stands out from the previous two works by considering much more detailed components and requirements, and provides the best insight of all by showing how the computation time increases with the number of components. This is shown in Figure 2.3, where a single core of a system with Intel i7 7700HQ and 32GB of RAM were used. It can be seen how when selecting 11 components already 2.4 hours are needed to complete the topology generation. Selecting even 1 more component increases the waiting time to around two days. And from then on onwards the discussion quickly becomes about having to wait several years or even decades.

Figure 2.3: Figure from [6], showing how computation time on a log-10 scale increases with the number of components.

This is the main reason why for many studies within the field of Co-Design often only a small subset of only 4-10 TFs is selected [5]. An alternative is to join some of the components already together, e.g. joining a battery and an electric motor, in order to form one larger component. This is the approach used in [11], where a large set of components can be reduced to a smaller set of components before initiating the topology generation. In other papers such as [20, 21, 22] topology generation is omitted entirely, focusing instead on optimising a single topology. However, by disposing many of the TFs that are possible, all of these strategies sacrifice the most crucial advantage of Co-Design; namely the guarantee that at the end of the computations/design process, an optimal design is obtained.

As such research is needed that focuses on how to reduce the computational cost of topology generation. One starting point is to follow up on the suggestion made in [7], which was to look into using SAT solvers instead of the CSP solver that is used for the topology generation in [8, 7], as this might make more efficient computations. Whether this is true or what other alternatives exist to solve topology generation problems efficiently remains however unexplored.

#### **2.2.3.** Problem 3: Isomorphic topologies

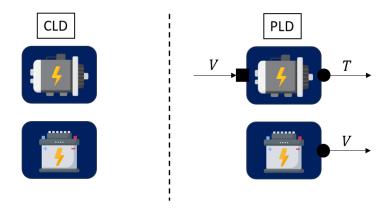

In [7] a comparison is made between how long it takes to complete the topology generation when describing 11 components using a component-level-description (CLD) or a port-level-description (PLD).

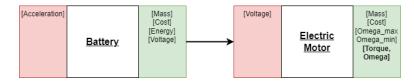

In CLD each component is represented as a node that can be connected to other components using undirected edges. Meanwhile, in PLD, more detail is added to each component by describing the input and output ports it has. To connect these components, directed edges are used instead. In Figure 2.4 an example is shown of an electric motor and a battery described in CLD and in PLD, where in PLD it can be observed that the motor requires an input voltage and provides an output torque, whereas the battery only has one output that provides voltage.

Figure 2.4: Example of a motor and battery described in a component-level-description (CLD), as is shown on the left, and a port-level-description (PLD), as shown on the right.

The reason these two description-approaches were developed in [7] was so that the topology generation performance could be compared. The hope was that with more detailed components, more constraints could be developed. This could then reduce the computation time to find all TFs, since fewer topologies remain to be explored. For example, using PLD to describe components allows for a port-to-port constrained to be expressed, in which any input port can only connect to one output port and vice versa. Such constraint does not exist when using CLD. Additionally, as also explained in [7], having specified for each component what their input and outputs are, the TFs that are generated from the topology generation directly also deliver input-output models that can be simulated. With CLD, the TFs still first need to be developed into models that only then can be simulated. It is therefore clear that there is a good reason to have components be described in more detail rather than less.

If one now refers to the results from [7], which are summarised in Table 2.2, then the expectations are only met partially. When using CLD to describe the 11 components, then 26 constraints could be developed, and using a system of Intel Core i5-M540 @ 2.53 GHz and 8 GB RAM with Win7 and SWI-Prolog 7.4.2, the topology generation could be completed in 45 seconds. On the other hand, when using PLD, indeed, as hoped, many more constraints could be developed. But quite contrary to what was expected, the topology generation was not completed any faster. Quite the opposite in fact; it took five times longer to complete the topology generation.

|                  | CLD | PLD |

|------------------|-----|-----|

| Components       | 11  | 11  |

| Constraints      | 26  | 168 |

| Solving time [s] | 45  | 218 |

Table 2.2: Summarised table of results from [7], showing how long the topology generation took to complete when using CLD or PLD.

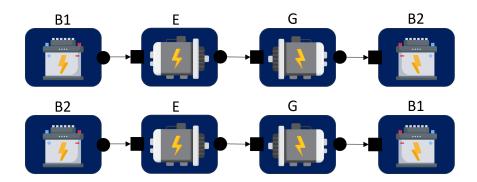

Fortunately in [7] the reason for the significantly higher computation time could be identified. The issue lies with what is referred to in [7] as isomorphic topologies. These are topologies that albeit having different connections turn out to be identical. Figure 2.5 provides an example of two isomorphic TFs. Shown are two chains, where a battery feeds its voltage to an electric motor,

which in turn drives a generator, whose output voltage is used to charge a second battery. Crucially, the batteries B1 and B2 are actually two instances of the same component, i.e. B2 is a copy of B1. Thus whether the chain starts with B1 or B2 and ends with the other makes no difference. However, with the current methods that are employed, the CSP solver does consider these two TFs different.

Figure 2.5: Example of two isomorphic TFs.

In [7] it was shown that when 11 components were used, in CLD a total of 21′536 isomorphic TFs were found. Using PLD instead, adding therefore more detail to the components, resulted in a total of 102′768 isomorphic TFs. Yet after post-processing these solutions to eliminate all isomorphic topologies and end up only with the set of TFs, in both cases almost the same number of TFs were found; 250 TFs for CLD and 262 TFs for PLD. This was used to indicate that increasing the amount of detail to describe the components results in an increased number of isomorphic topologies. Additionally, from the method that was applied to remove the isomorphic topologies, it was shown that isomorphic topologies also increase in number when the number of instances (i.e. copies) is increased.

However for several applications such as the HEVs considered in [5], it is needed that several instances of a component can be used. For example, one might be interested in exploring how HEVs with one single electric motor behave versus ones that have multiple ones. Additionally there often is a lot of data available about each component. Transitioning from a CLD description for the components to a PLD increases the use of the data that is available. And yet, with the current methods, having more instances available and having the components described in detail is being punished by significantly higher computation times for the topology generation process. No method seems to exist yet that can avoid producing these isomorphic topologies, which is why after the CSP solver has produced all TFs in [7], the results are post-processed in order to filter out all isomorphic TFs. (Adding therefore even more computational time to the topology generation process.) Research is therefore needed to see how one can avoid producing these isomorphic TFs in the first place, so that the CSP solver used for topology generation does not waste time searching for TFs it has already found. If such a method were developed, it should lead to a significant reduction in the required computational time to generate all TFs.

#### **2.2.4.** CONCLUSION ON LIMITATIONS

The problems that were described in sections 2.2.1 to 2.2.3 make it clear that the reason why Co-Design is limited to work on only 10-20 components is that with the current methods, topology generation demands an impossibly high computation cost once any more components are considered. However it is also clear that many open questions remain around the process of topology generation itself. Dedicating research into this process would lead to reducing the knowledge gap that exists on this topic. This knowledge may help to develop a topology generation method that is significantly faster and therefore requires a smaller computational cost.

### 2.3. RESEARCH QUESTION

From [5] it seems like most research has focused on topology optimisation, trying to circumvent the problems from topology generation in multiple ways such as described in section 2.2.2. In doing so though, much of the benefit of guaranteeing optimality that comes with Co-Design is sacrificed. Therefore instead research into topology generation is needed, as this would provide the understanding needed to possibly remove the 10-20 components limitation that originates from topology generation.

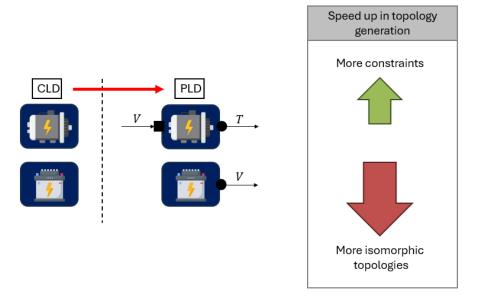

Focusing on topology generation, the most pressing problem seems to be the problem of isomorphic TFs described in section 2.2.3. Like visually summarised in Figure 2.6, instead of the topology generation process speeding up due to the increased number of constraints that can be placed thanks to describing the components in more detail (for example using PLD instead of CLD), the topology generation process actually slows down. This is because the added detail allows for an increased number of isomorphic topologies, whose negative impact is larger than the positive impact of an increased number of constraints.

Figure 2.6: Summarising the problem with isomorphic topologies: When transitioning from a more basic description (such as CLD) to a more detailed one (PLD), more constraints can be placed, which should speed up the topology generation, but more isomorphic topologies are created, which slow the topology generation down [7].

As such it seemed most useful to dedicate research effort to the issue of the isomorphic topologies. The thought was that if a method could be put together that effectively avoids creating isomorphic topologies, the result of it being an additional constraint, then finally it may be possible to additionally benefit from the many more constraints that come with an increased level of component description. The result should be a significant speed up in the topology generation process, since the CSP solver would not need to waste computations on trying to find TFs it has already found, and has several more constraints due to the more detailed component description that allow it to find the TFs more quickly. These benefits will carry then over also to the topology optimisation process, since the optimisation space, the set of TFs, would be drastically smaller without any of the isomorphic topologies, and therefore would require less exploration to find the optimal TFs. Indeed, the entire Co-Design process would be influenced. Avoiding the isomorphic topologies may therefore be the key to removing the 10-20 components limitation

from Co-Design, and thus make it possible to apply Co-Design to develop the solutions needed to decarbonise the EU transportation sector.

Thus the following research question has become the focus of this thesis:

#### Main Research Question (MRQ)

In comparison to the current approach, how does avoiding isomorphic topologies, while using a detailed description of components, influence the time to complete generating all feasible topologies (TFs) when given a set of components and a set of requirements?

However answering such a research question requires a method that can compute TFs while avoiding isomorphic topologies. As explained in section 2.2.3, it seems such method does not yet exist. Therefore any candidate method that is put together and might be able to avoid producing isomorphic topologies will require at the very least to show that it is indeed able to do so in different use cases where such isomorphic topologies otherwise appear.

If this is done while using the same approach as is currently used for topology generation (see chapter 2), then for each use case all of the constraints required to find the TFs will have to be rewritten all over again, like explained in section 2.2.1.

What does stand out from the approach currently taken in topology generation is that even though nodes are used to represent the components and edges are used to represent the connection between the nodes/components [8, 5], no adjacency matrices are made use of, like one might expect when dealing with nodes and edges [23]. The work done in [6] is an exception, where indeed one large adjacency matrix was used to specify what component is connected to some component, i.e. the connection matrix. There already some constraints could be expressed in the form of what indices could not be used in the adjacency matrix.

It therefore seems useful to expand on the method that was used in [6] and see how this might help to reduce the number of constraints that need to be rewritten. Even if not all constraints can be rewritten into matrix form, with the ones where this is possible upper bounds can be expressed on the number of TFs that might exist with a set of components  $S_c$  and a set of requirements  $S_r$ . Such information could provide the insight necessary to see how to speed up topology generation or how to avoid the isomorphic topologies. Therefore the following two supplementary research questions will be considered in this thesis as well.

#### Supplementary Research Question 1 (SRQ-1)

With respect to the current approach, how much does the use of adjacency matrices reduce the number of constraints that need to be rewritten?

#### Supplementary Research Question 2 (SRQ-2)

How much does each constraint used in topology generation restrict the number of feasible topologies (TFs) on a given set of components?

### **METHODOLOGY & RESULTS**

In the previous chapter, chapter 2, it was explained how the current state-of-the-art approaches Co-Design and how its methods around topology generation are the reason it can only consider 10-20 components. After this review the research questions were presented.

In this chapter the methodology used to answer those research questions is described, while presenting the results that have been obtained along the way. The method that is put together here follows two key philosophies:

- 1. Specify not *what* connections to place, but *how* to place connections. In chapter 2 some examples of the constraints that are used by the current state of the art were presented. Of those one can distinguish between local and global constraints, i.e. constraints that apply only to some constraints versus constraints that apply to all components. In CLD many local constraints were placed that would specify to which other components a component could connect to, such as that an electric motor could not connect to a wheel directly but it could connect to a battery. In PLD however the global port-to-port constraint was placed, which specified that any port of any component could connect to only one port of any other component. It is the latter type of constraints that will be favoured, as this should lead to fewer but more effective constraints in comparison to multiple local ones. Additionally when the set of components changes, when using global constraints, these do not have to be rewritten.

- 2. Maximise the use of the data that is available for each component. As was explained in chapter 2, in CLD components are represented as nodes to which other nodes/components can connect to. However without a label under the node which specifies what component it is, there is no information that could help identify what the component is or what it does. This is also a reason why then local constraints are needed that specify which node can connect to which other. The lack of information about the components is compensated with the addition of local constraints. In PLD this is improved. Components can now be identified by their input and output ports, and whether the ports supply a voltage, torque or some other physical quantity. Even without a label one might already be able to guess what each component is. The goal will be to exploit as much of the data that is available for each component as possible, and thus the method builds on the PLD approach described in chapter 2.

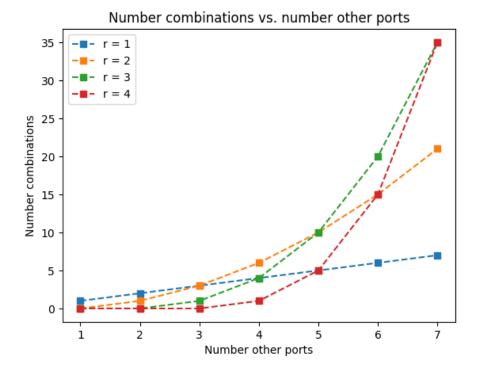

The chapter starts off with section 3.1 by describing the basic setup that was used for which the rest of the work is built upon. Each section that follows builds on the work from the previous sections. The 3BT-3EM test, the first validation test described in section 3.1.3, is used as a case study to compare the results obtained in each section. In section 3.2 the set of potential topologies when no constraints are taken into account (TPs) is considered. In section 3.3 the port-to-port constraint from [7] is applied as a first constraint, to see how it reduces the set of TPs. This is carried on in section 3.4 with a second constraint, which specifies what ports are actually compatible with each other. Finally, in section 3.5, equipped with the knowledge and setup from the previous sections, the set of feasible topologies (TFs) is computed, where all constraints are taken into account. This also includes the proposed method that avoids the emergence of isomorphic topologies.

#### 3.1. BASIC SETUP

In the following section the basic setup that was used is presented. First, in section 3.1.1 the modelling strategy is presented. This is followed with section 3.1.2, where an explanation of how the components are defined is provided, as well as how that data is set up and used. Since the goal is to develop a method that generates feasible topologies (TFs) without producing isomorphic topologies (see MRQ in section 2.3), in section 3.1.3 validation tests are described, which will be used to validate said method. Finally, in section 3.1.4, it is described how all of this has been implemented into a Python program with which the necessary computations are executed.

#### 3.1.1. Interconnected System Model for Topology Generation

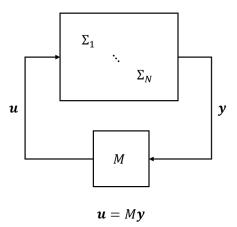

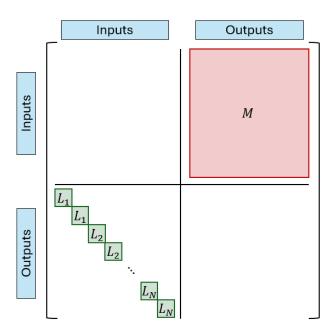

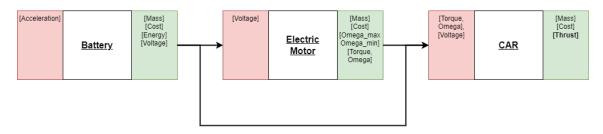

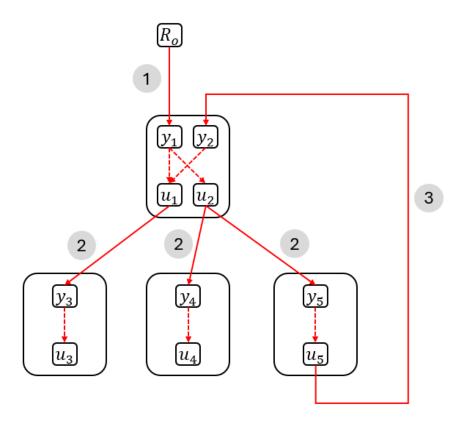

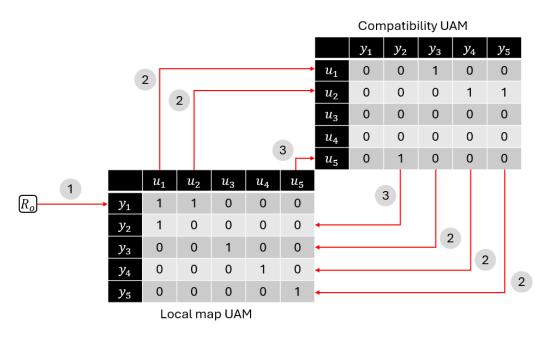

The Interconnected System Model (ISM) that is described in [24] is used as a basis for the method that is put together here. The model is visualised as a flowchart in Figure 3.1, where the subsystems  $\Sigma_1, \ldots, \Sigma_N$  collected in the top box provide the output vector  $\mathbf{y} \coloneqq \begin{bmatrix} \mathbf{y}_{\Sigma_1} ... \mathbf{y}_{\Sigma_N} \end{bmatrix}^T : \mathbf{y} \in \mathbb{R}^q$ . The output vector  $\mathbf{y}$  is then fed into the gain  $M: M \in \mathbb{R}^{p \times q}$ , where the feedback matrix operation  $\mathbf{u} = M\mathbf{y}$  is performed. The input vector  $\mathbf{u} \coloneqq \begin{bmatrix} \mathbf{u}_{\Sigma_1} ... \mathbf{u}_{\Sigma_N} \end{bmatrix} : \mathbf{u} \in \mathbb{R}^p$  is then fed back to the subsystems  $\Sigma_1, \ldots, \Sigma_N$ . The matrix M can therefore be used to define how the subsystems  $\Sigma_1, \ldots, \Sigma_N$  are coupled with each other.

Figure 3.1: The Interconnected System Model (ISM), where the subsystems  $\Sigma_1, ..., \Sigma_N$  are fed the input u: u = My, and provide the outputs y.

Define each component in  $S_c$  as a subsystem in the ISM. Additionally define the matrix M to be boolean, i.e.  $M \in \mathbb{B}^{p \times q}$ :  $\mathbb{B} := \{0,1\}$ . Then for each  $m_{i,j}$  in M, it specifies whether there exists a connection between the output  $y_j$  and the input  $u_i$ . In other words, the matrix M can be used to specify the connections that exist between components, i.e. the topology.

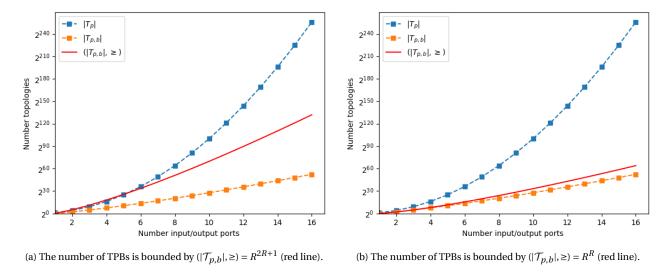

Because M is a boolean matrix, there exists a finite set of potential topologies  $\mathcal{T}_p := \{M_1..M_{pq}\}$ , where with  $\mathbf{y} \in \mathbb{R}^q$  and  $\mathbf{u} \in \mathbb{R}^p$ , the number of potential topologies (TPs) is  $|\mathcal{T}_p| = 2^{pq}$ . However, as is shown in section 3.3 to section 3.5, many connections that exist in M can actually not be placed. This reduces the number of TPs that exist. Additionally, the goal is to use the set of components  $\mathcal{S}_c$  in order to meet a set of requirements  $\mathcal{S}_r$ . Topologies that achieve this are referred to as feasible topologies (TFs), such that  $\mathcal{T}_f \subseteq \mathcal{T}_p$ .

In [8, 7] additional boolean variables exist that specify whether a component/subsystem is selected or not. Here however it will be assumed that a component is selected if a connection has

been established between it and some other component, just like it was done in [6]. The reasoning is that it makes little sense to establish a connection between two components if any of those two components are not present. The booleans  $m_{i,j}$  contained in M are therefore all the booleans that will be considered.

It is worth mentioning that the ISM resembles a lot to the typical feedback loop used in control engineering. The main difference is that while usually the feedback gain M is such that  $M \in \mathbb{R}^{p \times q}$ , here M is a boolean matrix such that  $M \in \mathbb{B}^{p \times q}$ . Additional constraints that specify which connections can be placed restrict M even further. As such, when trying to obtain the ideal topology from a set of components  $\mathcal{S}_c$  to meet a set of requirements  $\mathcal{S}_r$ , this is like designing the ideal feedback gain M, but with the challenge that M is extremely restricted in the values it can take.

The ISM also helps to differentiate between different requirements that can be placed. Three different requirements have been defined here:

- Output requirements: From the set of components  $S_c$  a certain output  $y \in y$  may be required. If a single output is required, then the TFs require a component that can deliver this output.

- External input requirements: Besides the inputs components may receive from other components through the boolean matrix M, some external inputs may need to be taken into account as well. For a single external input, the TFs require then a component to which this input can be fed to.

- **Global constraints requirements:** Unlike the previous two requirements, for which some component needs to be selected to deliver the correct output or to which some external input can be fed to, this requirement acts on all components of any TF. An example is a constraint on the total mass of the components in a TF.

More requirement types may exist, but this is beyond the scope of this thesis. In fact, in this work, only a single output requirement is going to be considered. This is sufficient to answer the main research question considered in this thesis, as is presented in section 2.3.

#### **3.1.2.** COMPONENT DESCRIPTION AND COMPOSITION

In the following section the description used for the components is defined. This description builds upon the PLD description used in [7] (see section 2.2.3) following the recommendations also mentioned in [7]. Inspiration has also been taken from the physical network modelling approach that is used in Simscape from Mathworks [25]. (Refer to my literature review, section 4.2, on physical network modelling, for more information on this.)

The intention was very much to set up a description that goes beyond the PLD used in [7], and could be expanded in the future to maximise the use of the data that is available about each component. The reason to directly start off with a detailed description rather than a lesser one is so that the emergence of isomorphic topologies cannot be ignored. (As was described in section 2.2.3, using a more detailed component description leads to more isomorphic topologies.)

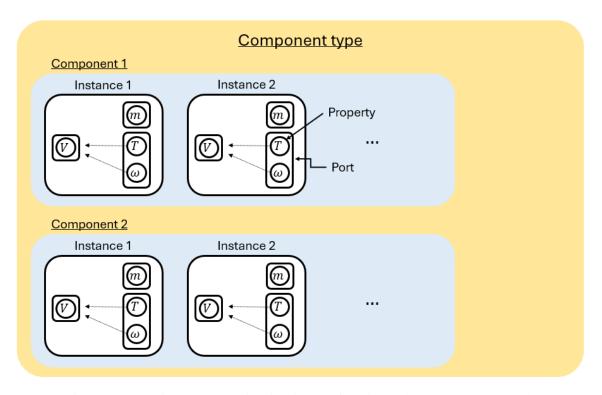

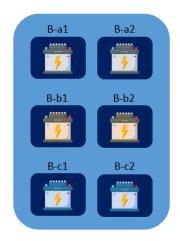

The component description used here, which shall be referred to as the property-port level description (PPLD), starts off by defining properties. These are analogous to the input and output variables that are typically used in state-space or transfer function models. In Figure 3.2 an example is provided of the PPLD applied to a set of electric motors. The properties are shown as the circles with V, m, T or  $\omega$  in them. It is also assumed that the components are modelled as fully observable systems. That means that also the states of the components are available as outputs.

#### 3.1.2.1. NODE, UNIT AND DOMAIN TYPES

The properties are distinguished by the set each property belongs to for each type that exists. To start off, there are three types:

- Node type, which specifies whether the property is an input or an output. In Figure 3.2 the V property is an input property, while the m, T and  $\omega$  properties are all outputs.

- Unit type, which specifies what variable the property is. The V property in Figure 3.2 is a voltage, m is a mass, T is a torque, and  $\omega$  is a rotational speed.

- Domain type, which specifies to what physical domain the property belongs to. The V property in Figure 3.2 belongs to the electrical domain, while the rest of the properties belong to the mechanical one.

To define the types with a bit more detail, consider as an example the node type. All properties will belong to either a set of input properties  $\mathcal{U}$  or to a set of output properties  $\mathcal{Y}$ . Therefore the input and output set are disjoint, i.e.  $\mathcal{U} \wedge \mathcal{Y} = \emptyset$ . The two disjoint sets represent the (discrete) node type, which is denoted using angle brackets, i.e.  $\langle N \rangle \coloneqq \{\mathcal{U}, \mathcal{Y}\}$ .

While the node type is defined by at most two different sets, the other types may have many more sets. This depends on the set of components that is being used. For example in Figure 3.2, if no further components are considered, then the unit type is defined by the four variables V, m, T and  $\omega$ . As such, if the set of components changes, then so do the types.

#### 3.1.2.2. USE IDS TO RECORD PROPERTIES AND TYPES

To keep track of all of these elements, every property and set (for the types) is given a unique ID and saved into a list. The lists are denoted here using square brackets. For example, the list of property IDs is written as [P-ID]. Similarly three other lists can be written for the node, unit and domain type, i.e. [N-ID],[V-ID],[D-ID]. For example the list for the node type [N-ID] is of length 2, containing one ID for the input set  $\mathcal{U}$  and another ID for the output set  $\mathcal{Y}$ .

The IDs that are used are universally unique lexicographically sortable identifiers, otherwise known as ULIDs. As described in [26], these are similar to the more commonly used universal/global unique identifiers (UUID/GUID), which use the current time stamp and random generators to create unique IDs. ULIDs however have the extra feature that they can be sorted by the order in which they have been created. The ability to order components is an essential ingredient for the method that is used to avoid isomorphic topologies, as will be explained in section 3.5.

Figure 3.2: The component description used in this thesis, referred to as the Property-Port Level Description (PPLD), here showing an example of the description for a set of electric motors.

#### 3.1.2.3. PORTS, INSTANCES, COMPONENTS AND COMPONENT TYPES

Once the properties have been defined by these three basic types, they are assembled by further types to define ports, instances, components and component types.

Ports will contain at least one property. These are shown in Figure 3.2 as the rounded rectangles that contain the circles V, m, T and  $\omega$ . The idea behind ports is that in some cases, if a certain output variable is requested, it cannot be requested without also accepting another output variable. For example with the electric motors in Figure 3.2, if one chooses to use the torque output that is provided by the electric motor, then this will be provided with the output  $\omega$  as well.

Additionally, it is assumed that ports can only have either input properties or output properties, but not properties with mixed node types. That implies that ports can be distinguished as well between input ports and output ports.

With the ports defined, instances of components can be formed. The idea behind instances is to allow to make copies of a component. In Figure 3.2 two components are shown. Each component represents a different electric motor. However when considering only one component, all instances represent the same electric motor. As such, each component has at least one instance, and each instance has at least one port.

Here the assumption is used that the output ports and input ports for each instance need to be distinguishable and therefore have unique types for their properties. As such instances/components that would have multiple ports that all provide the same node, unit, and domain type are ignored. (For example multiple voltage outputs.)

Finally, components can be grouped into component types if they are similar enough. This is a strategy that was employed in [27, 20, 22], where multiple components, for example electric motors, are grouped into one type. However in [27, 20, 22] it is not defined when two different components are similar enough to be put into the same component type. Instead, this is defined apriori. Such approach is avoided here, as this would equate to defining local constraints and would therefore require to be rewritten for each new set of components one might consider. Instead here components are grouped together into component types when the components turn out to have the same unit types.

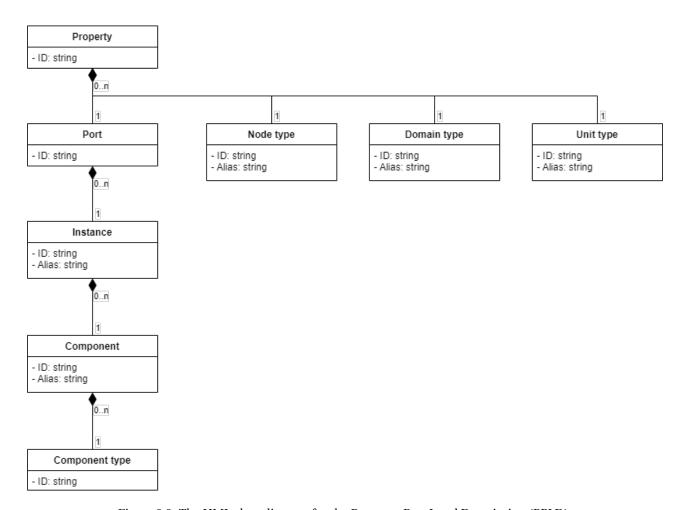

The PPLD assembled here is presented as a UML class diagram in Figure 3.3. The diamond arrows represent composition relationships. Here they indicate for example that at least one property needs to exist before 1 port can be created. (And no port will exist with no properties present.)

$Figure \ 3.3: \ The \ UML \ class \ diagram \ for \ the \ Property-Port \ Level \ Description \ (PPLD).$

Just like with the properties and the node, unit and domain types, also for each port, instance, component and component type a unique ULID is given. This is shown in the attributes of the UML class diagram in Figure 3.3. In total therefore eight different ID lists are made use of:

- [P-ID]: Ordered list/vector of property IDs.

- [T-ID] : Ordered list/vector of component type IDs.

- [C-ID]: Ordered list/vector of component IDs.

- [H-ID]: Ordered list/vector of instances.

- [R-ID] : Ordered list/vector of port IDs.

- [N-ID]: Ordered list/vector of node types.

- [V-ID] : Ordered list/vector of unit types.

- [D-ID] : Ordered list/vector of domain types.

For some of these lists a list aliases is also provided. These also appear as attributes in the UML class diagram in Figure 3.3. For example components are supplied an alias next to their ULID. This could be for instance an alias to specify that a component is a lithium battery. These aliases are merely there to make it easier to review results and debug problems in the code. (More on this in section 3.1.4.) It is always the ULIDs that are used as reference.

#### 3.1.2.4. DEFINING MEMBERSHIPS AND COMPOSITIONS

Besides defining IDs for every element in the PPLD, it must also be specified where each element belongs. (For example which properties belong to some specific port.) To achieve this, unweighted adjacency matrices (UAMs) are used to describe the membership between two elements. This approach is taken directly from the methods used in fuzzy logic, where the membership UAMs are also referred to as relations [28]. The following membership UAMs are defined:

- $\mu([P-ID] \times [T-ID])$ : Membership of each Property ID with each component type.

- $\mu([P-ID] \times [C-ID])$ : Membership of each Property ID with each component ID.

- $\mu([P-ID] \times [H-ID])$ : Membership of each Property ID with each instance.

- $\mu([P-ID] \times [R-ID])$ : Membership of each Property ID with each port ID.

- $\mu([P-ID] \times [N-ID])$ : Membership of each Property ID with each input/output type.

- $\mu([P-ID] \times [D-ID])$ : Membership of each Property ID with each domain type.

- $\mu([P-ID] \times [V-ID])$ : Membership of each Property ID with each unit.

Here the cross product between one list and another indicates that a UAM is formed. The symbol in front of the cross product indicates what the relation between the two lists is. In this case, with the symbol  $\mu$ , it is indicated that the relation refers to a membership. For example, for  $\mu([P-ID] \times [T-ID])$  it is specified to which component type in [T-ID] each property in [P-ID] belongs to.

Defining membership with this strategy allows that (fuzzy) composition like described in [28] can be used. (Refer to appendix A.1 to review the definition of a fuzzy composition.) Consider the case where the relation  $\mu([\text{T-ID}] \times [\text{C-ID}])$  needs to be used. In (3.1) it is then shown how this

can be obtained from the membership UAMs that were defined earlier, where the symbol 'o' is used for the fuzzy composition operator.

$$\mu([P-ID] \times [T-ID])^T \circ \mu([P-ID] \times [C-ID]) = \mu([T-ID] \times [C-ID])$$

(3.1)

Composition can also be used to extract elements that meet certain conditions. Consider as an example that we would like to find all properties whose node type is an input, and that belong to some instance n. The following steps are taken:

1. Select properties whose node type is an input:

$$\mu([P-ID] \times [N-ID]) \circ \mu([N-ID(u)]) = \mu([P-ID|N-ID(u)])$$

Here  $\mu([N-ID(u)])$  provides a boolean vector of length |[N-ID]|, with a 1 for the selected set  $\mathcal{U}$ , here specified by the bracket expression (u).

2. Select properties that belong to some instance n:

$$\mu([P-ID] \times [H-ID]) \circ \mu([H-ID(n)]) = \mu([P-ID|H-ID(n)])$$

3. Use AND operation to find all properties whose node type is an input and that belong to the instance *n*:

$$\mu([\text{P-ID}|\text{H-ID}(n)]) \wedge \mu([\text{P-ID}|\text{N-ID}(u)]) = \mu([\text{P-ID}|\text{H-ID}(n).\text{N-ID}(u)])$$

The period symbol '.' is used as a shorthand here for the AND operation usually expressed by the wedge symbol  $\land$ , in order to make sum-of-product expressions more readable. (See section 2.6.1 on sum-of-products and product-of-sums in [29] for the definition of these boolean expressions.)

Composition is therefore an essential operation in order to manipulate and retrieve the data that is available for any set of components  $S_c$ .

Luckily, it turns out that with the use of UAMs, which are boolean matrices that can only take as values either True or False (1 or 0), the fuzzy composition can be simplified to a regular matrix multiplication.

*Proof.* Let *A* and *B* be two boolean matrices such that  $A \in \mathbb{B}^{p \times q}$  and  $B \in \mathbb{B}^{q \times r}$ , with  $\mathbb{B} := \{0, 1\}$ . The matrix multiplication of *A* and *B* would result in another matrix *C* such that:

$$c_{i,j} = \sum_{k}^{q} a_{i,k} b_{k,j} \tag{3.2}$$

Only three types of  $a_{i,k}b_{k,j}$  products exist:

- $0 \cdot 0 = 0 = \min(0, 0)$

- $1 \cdot 0 = 0 \cdot 1 = 0 = \min(0, 1)$

- $1 \cdot 1 = 1 = \min(1, 1)$

When taking the sum of these products, for the first two cases the sum will always lead to zero. For the third case, if such a product would appear more often when multiplying A and B, then a regular sum would grow to some value  $\geq 1$ . However with boolean variables,  $1 + 1 + \cdots = 1 = \max(1, \ldots, 1)$ .

Therefore, the matrix multiplication of A and B leads to another boolean matrix C, where the matrix multiplication in (3.2) can be expressed using max and min terms instead, like shown in (3.3):

$$c_{i,j} = \max_{k \in K} \min(p_{i,k}, q_{k,j})$$

(3.3)

This expression is identical to the max-min composition from described in [28]. (See appendix A.1).

This is helpful, since for programming packages/libraries that offer functions to make matrix computations are widely available. For example in Python, packages like Numpy, Scipy or Pandas already provide functions to multiply two matrices together, and where one can specify that these matrices are boolean, therefore making composition possible.

Still, to distinguish both from a more general fuzzy composition operation and otherwise from a regular matrix multiplication operation, the matrix multiplication of two boolean matrices will be referred here as a boolean composition.

#### 3.1.2.5. LOCAL MAPS AND CONNECTION MATRIX

Two last elements remain to complete the PPLD: Defining which input properties each output property depends on, referred here as the local map, and defining all potential connections that can be made between components, ignoring all constraints. The local map can also be understood as the internal connections of components that are already set in place, while the potential connections refer to the external connections between components that still need to be set in place.