### Multichannel current-mode stimulator with channel-specific regulated power supply

Varkevisser, Francesc; Costa, Tiago L.; Serdijn, Wouter

10.1109/BioCAS58349.2023.10388577

**Publication date**

**Document Version** Final published version

Published in

Proceedings of the 2023 IEEE Biomedical Circuits and Systems Conference (BioCAS)

Citation (APA)

Varkevisser, F., Costa, T. L., & Serdijn, W. (2023). Multichannel current-mode stimulator with channel-specific regulated power supply. In *Proceedings of the 2023 IEEE Biomedical Circuits and Systems Conference (BioCAS)* IEEE. https://doi.org/10.1109/BioCAS58349.2023.10388577

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

## Multichannel current-mode stimulator with channel-specific regulated power supply

Francesc Varkevisser\*, Tiago L. Costa\*, and Wouter A. Serdijn\*†

Email: {f.varkevisser,t.m.l.costa,w.a.serdijn}@tudelft.nl

\*Section Bioelectronics, dept. Microelectronics, Delft University of Technology, Delft, The Netherlands

†Neuroscience Dept., Erasmus Medical Center, Rotterdam, The Netherlands

Abstract—Developing neuroprosthetic bioelectronic devices requires wirelessly-powered implantable stimulator systems with hundreds to thousands of output channels. Power efficiency optimization is crucial for scaling up the number of output channels. Current-mode electrical stimulation is favored for safety but is power-inefficient in conventional designs, particularly in multichannel stimulators. An adaptive voltage supply can improve power efficiency, but implementing channelspecific voltage supplies in large-scale systems is challenging. Conventional power management suffers from losses and low efficiency due to multiple conversion stages. This work proposes a multichannel current-mode stimulator with a parallel, adaptive ac/dc power management strategy using single-stage phasecontrolled converters to prevent cascaded losses. This allows for generating channel-specific supply voltages within a small area for high power efficiency and high-density electrical stimulation. The proposed circuit was designed and simulated using TSMC 180 nm technology and demonstrates an improvement in the power efficiency of up to 45% with respect to a conventional power-management strategy using a fixed supply voltage.

Index Terms—electrical stimulation, neuromodulation, regulating rectifier

#### I. Introduction

Bidirectional brain-computer interfaces and implantable cortical visual prostheses are promising brain-stimulation applications that demand large-scale multichannel stimulator systems. For example, it is estimated that hundreds to thousands of stimulation channels are needed in a cortical visual prosthesis to provide useful vision to a blind patient [1]. Such implantable devices should be powered through a wireless link to avoid infections that wired solutions would otherwise cause. However, the amount of power that can be transferred is limited due to safety regulations. This poses a challenge to the demand for increasing the number of stimulation channels.

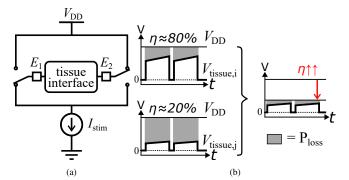

Current-Mode Stimulation (CMS) is often the preferred method for stimulation, as it offers better control over the amount of charge delivered to the neural tissue, an essential requirement to ensure the patient's safety [2]. In this method, pulse trains of biphasic current pulses are applied to the tissue to activate nearby neurons. To apply the pulses to the tissue, a bipolar electrode configuration can be used. This configuration uses a unidirectional current source combined with a switch structure (H-bridge) that reverses the current direction to achieve biphasic pulses, as shown in Fig. 1a.

In CMS, each channel has a different electrode-tissueinterface impedance [3] and different current requirements for activating neurons, which leads to different voltage drops over

This work is part of the INTENSE project funded by the Dutch Research Council (NWO) under grant number 17619

Fig. 1: (a) Bipolar electrode configuration, using unidirectional current source and H-bridge to create biphasic current pulses through the tissue. (b) Losses in conventional CMS output driver for different  $V_{tissue}$  properties (left) and possible efficiency improvement by scaling of the voltage supply (right)

the tissue. This, in turn, leads to different requirements for the ideal power supply voltage in each channel. As illustrated in Fig. 1b, a mismatch between the voltage drop over the tissue and the voltage supply results in an excessive voltage drop over the current source, which leads to power losses. Traditionally, the voltage supply has to accommodate the channel with the highest tissue-voltage requirements, which leads to power losses in all other channels. A scalable voltage supply can reduce overhead losses and increase power efficiency (Fig. 1b) [4]-[9]. Some designs use a feedback loop that includes the external wireless power transmitter to regulate the output voltage by the transmitted power signal [4]. This implementation would require multiple power links to support multi-output voltage regulation, which is not a scalable solution. Alternatively, on-chip DC/DC converters are used [5]-[8], which typically use bulky capacitors or inductors, limiting the scalability. A possible solution is to implement a multi-output DC/DC converter and utilize it for multiple channels [9], [10]. However, another disadvantage of on-chip DC/DC converters is the cascaded inefficiencies in the multiple stages of rectification and regulation of the incoming signal. To overcome this problem, single-stage regulating rectifiers can be used [11]–[13]. A limitation of existing single-stage regulating rectifier implementations is that the output voltage is regulated according to a programmed reference voltage. In order to explore the high energy efficiency of single-stage regulating rectifiers while automatically adapting to the unpredictability of the electrode-tissue interface load conditions, this work proposes a new feedback regulation topology with a compliance monitor based on a phased-controlled regulating rectifier. This allows the current-mode stimulator to have a power supply matched to the needs of the load, hence maximizing the

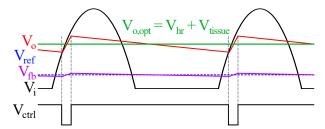

Fig. 2: Timing diagram of the proposed regulating rectifier circuit

power efficiency. Furthermore, the proposed design aims to achieve scalability for high-channel-count systems, allowing for efficient and precise regulation of the output voltage in each module.

#### II. CIRCUIT DESIGN

#### A. System-level design and requirements

In a wirelessly powered implant, the input signal to the system is often an alternating voltage generated by the power-receiving elements. For each channel, to minimize the voltage overhead on the current source and hence optimize the power efficiency, a channel-specific power supply is needed. As illustrated in Fig. 2, the alternating input signal crosses the optimal output voltage,  $V_{o,opt}$ , in each period. Our proposed idea is to design a regulating rectifier that charges a storage capacitor whenever the input signal crosses the optimal output supply voltage.

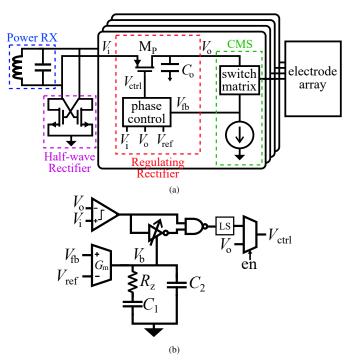

The proposed modular multichannel stimulator architecture is shown in Fig. 3a. Each module contains a current mode stimulator with an individually regulated voltage supply. The proposed regulating rectifier topology consists of a rectifying PMOS transistor,  $M_P$ , a phase-controlling feedback loop, and a storage capacitor,  $C_o$ . The phase controller is enabled when the current source is active. When the phase controller is active, it controls the conduction time of  $M_p$  to regulate the headroom voltage of the current source,  $V_{fb}$ , to a set reference,  $V_{ref}$ . As a result,  $V_o$  is regulated to the appropriate voltage required to deliver the current to the load.

The timing diagram of the circuit is shown in Fig. 2. Because the rectifiers are designed to operate in parallel in multiple modules, each rectifier only receives a half-wave rectified voltage at the input. This omits copies of the control circuits to rectify the other half of the input signal, reducing the circuit's size. To extract power from the complete input signal, it will be equally divided over the available modules. The output power of each rectifier is low since it only supplies one current driver. Therefore,  $C_o$  is small compared to a rectifier that needs to supply full-system loads.

The proposed implementation of the phase controller is illustrated in Fig. 3b; The comparator decides the turn-on time by comparing the input voltage,  $V_i$ , and the output voltage,  $V_o$ , and the duration of the pulse is controlled using a voltage-controlled delay line (VCDL). The control voltage for the VCDL,  $V_b$ , is produced by the error amplifier, which has a frequency compensation network adding two poles and one zero to its transfer function to boost the phase margin of the feedback loop. When the phase controller is disabled, the output multiplexer configures  $M_P$  as a diode-connected

Fig. 3: (a) Proposed system architecture. Each module connects to a half-wave rectified input voltage. (b) Proposed implementation of the phase control feedback circuit.

transistor by connecting its gate to  $V_o$ , and the circuit operates as a passive rectifier.

The circuit is designed for the application of an intracortical visual prosthesis. In this application, a supply voltage of a few volts can be expected [14], [15]. Therefore, the circuit is designed to operate with an input signal with a peak voltage of 5 V. Only at the output, this voltage is required. The rest of the system operates from a 1.8 V supply to reduce power consumption. Because of this, a level shifter (LS) is needed between the control circuit and  $M_P$ . The electrode impedance is in the order of 50 k $\Omega$  while threshold currents between  $30\mu A$  and  $100\mu A$  can be expected [14]. In order to support the clinically relevant range, the output current source can be configured between 20  $\mu A$  and 95  $\mu A$  with 4 bits (LSB = 5  $\mu$ A) resolution. The circuit is designed to operate from a 13.56 MHz input signal, a carrier frequency in the ISM band commonly used for powering biomedical implants. In the presented design, the saturation voltage of the current source is approximately 200 mV. The presented results are simulated with a reference voltage of 250 mV to ensure that the current source is operating in saturation region in steady-state. This work focuses on the implementation of the phase controller and current source. Additional global and local control and power management blocks are needed to complete the system but are left out of Fig. 3a to focus on the scope of this work.

#### B. Transistor-level design

The output voltage of the driver stage does not have strict voltage-ripple requirements as the current source controls the current through the tissue. This relaxes the size of the filter capacitor  $C_o$ . Changes in the output voltage  $V_o$  will reflect to some degree in the produced output current, depending on the output impedance of the current source, which can

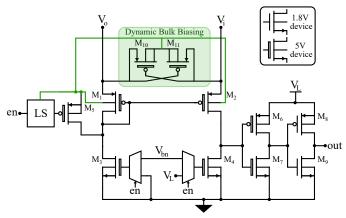

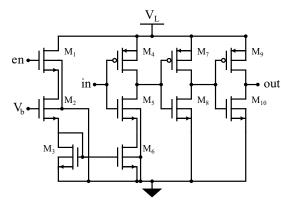

Fig. 4: Circuit implementation of the comparator.  $V_{bn}$  is the bias voltage for  $M_3$  &  $M_4$  when the comparator is enabled.

lead to unbalanced current pulses. However, even perfectly matched current pulses can lead to residual charges on the electrode-tissue interface [2]; thus, charge-balancing circuits will be required to ensure the device's long-term safety. As mentioned in Section I, the required output voltage, depending on the current amplitude and the (unknown) electrode-tissue impedance, is unpredictable and varies for each channel and over time. Therefore, the proposed circuit regulates the voltage over the current source instead and produces an output voltage accordingly. Furthermore, using the voltage on the current driver as the input voltage of the control circuit omits the necessity of a voltage divider used by other designs that use  $V_o$  as an input [11], [12], which saves energy and area.

The comparator is implemented using a common-gate input pair, as depicted in Fig. 4. This omits the requirement of a steady HV supply for the correct circuit operation. A dynamic bulk biasing circuit, consisting of 2 PMOS devices, ensures correct biasing of the input devices to the highest input voltage. It also acts as the voltage supply for the level shifter and  $M_5$ , which turns off  $M_1$  and  $M_2$  when the comparator is disabled, by pulling up their gate voltages. Furthermore, two multiplexers are used at the gates of  $M_3$  and  $M_4$ , controlled by the enable signal, 'en'. When the comparator is enabled, the gates are connected to a bias voltage,  $V_{bn}$ , and when the comparator is disabled, the gate voltages prevent any static current.

The voltage-controlled delay line is implemented using a current-starved inverter, shown in Fig. 5. The bias voltage  $V_b$  limits the maximum current of the input inverter through the current mirror. The inverter consisting of  $M_7$  and  $M_8$  is sized to have a considerable input capacitance. By limiting the inverter's current, the discharge time of this gate capacitance is controlled. The charge time of the capacitor is not limited as this is not relevant for the correct operation of the phase controller.

#### III. RESULTS

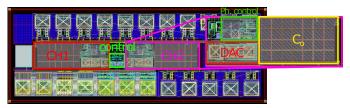

The proposed circuit is implemented in a 180 nm CMOS TSMC process to validate the voltage-regulating operation. The implemented circuit consists of two identical channels, each receiving half of the AC input signal and producing an individually regulated output voltage. The layout of the

Fig. 5: Circuit implementation of the voltage-controlled delay line.

Fig. 6: Layout of the designed system with two channels

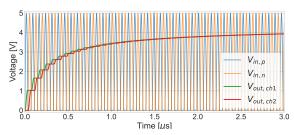

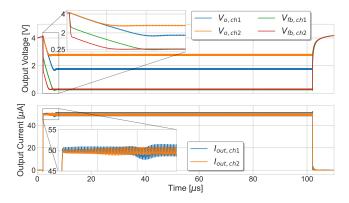

circuit is depicted in Fig. 6. The design has a channel area of 320  $\mu$ m  $\times$  110  $\mu$ m, of which the output capacitor occupies 62%. Fig. 7 shows the start-up process, with the regulators configured as passive rectifiers. Due to the voltage drop over the diode-connected PMOS, the maximum output voltage in passive mode is approximately 4.2 V. Fig. 8 shows the output voltages and currents for a 50  $\mu$ A, 100  $\mu$ s current pulse on both channels, while the load impedance of Channels 1 and 2 are 30 k $\Omega$  and 50 k $\Omega$ , respectively. It can be seen that  $V_{fb}$ of both channels is regulated to the set reference voltage, while the output voltage for both channels is different due to the difference in load impedance. The spikes observed at the output current are due to the switching and resulting ripple on  $V_o$  and  $V_{fb}$ . The regulation speed depends on the output current, discharging the storage capacitor, but both channels settle within 6  $\mu$ s after the onset of the pulse to their regulated output level.

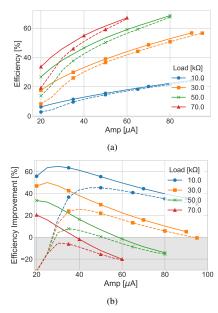

The efficiency of the regulator is calculated for both the schematic design and post-layout simulations by averaging the in- and output power of a 20  $\mu$ s current pulse for a range of current amplitudes and load impedances. The resulting efficiencies are depicted in Fig. 9a. The output current range is limited for higher impedances due to the maximum output

Fig. 7: Post-layout simulated start-up sequence with diode-connected rectifying switches.

Fig. 8: Post-layout simulated output signals for a  $100\mu s$  (starting at t= $2\mu s$ ) current pulse of  $50\mu A$  and  $R_{load,1}$ = $30k\Omega$ ,  $R_{load,2}$ = $50k\Omega$

voltage the circuit can produce. The reported efficiencies do not account for the additional power dissipation in the OTA and digital blocks of the phase controller: the OTA has a static power dissipation of 1.8  $\mu$ W, while the VCDL and other logic only have dynamic switching losses. The 5  $\mu$ A bias current of the comparator is drawn from  $V_i$  and  $V_o$  due to the commongate structure. Therefore, its power consumption is already considered in the presented efficiency values.

To compare the current design with a conventional power management strategy, we calculated the power efficiency of a system with a fixed output voltage of 5 V using (1). Note that this calculation assumes an ideal regulator without any losses. The efficiency improvement of the proposed circuit is calculated with (2), and the results are shown in Fig. 9b.

$$\eta_{fixed} = \frac{I_{stim}^2 R_{load}}{V_{supply} I_{stim}} \cdot 100\% \tag{1}$$

Efficiency improvement =

$$\frac{\eta_{proposed} - \eta_{fixed}}{\eta_{fixed}} \cdot 100\%$$

(2)

#### IV. DISCUSSION

The presented design shows an improvement of the power efficiency by up to 45% for low-impedance channels compared to a fixed supply voltage in post-layout simulations. Several opportunities exist to improve it even further:

- The phase controller has no compensation for the on- or off-timing of the pulse. A delay at the onset of the pulse leads to a voltage difference over M<sub>p</sub>, causing conduction losses. Furthermore, when the required output voltage is near V<sub>i,peak</sub>, off-switching delays also cause degradation in the power efficiency due to reverse currents [16], [17]. Several offset-compensation techniques exist to account for the delays of the phase controller, which would result in improved efficiency [17]–[23].

- In the current design, the phase controller triggers during each period of the input signal. When the output current is small, the conduction pulses become short, which degrades the power efficiency as switching losses are high compared to the energy transferred to  $C_o$ . To improve the efficiency for low currents, additional pulsefrequency modulation (PFM) could be applied [12]. The

Fig. 9: (a) Simulated schematic (solid) and post-layout (dashed) efficiency of the proposed circuit as a function of output current for 4 load impedances, (b) Efficiency improvement of the proposed circuit with respect to a fixed 5V-voltage supply

PFM regulates how often the phase controller is triggered; this increases the pulse duration and hence improves the power efficiency.

• The reference voltage determines the power consumption of the current source. For the presented results, the reference voltage was 250 mV. Improving the current source design to require less voltage headroom for a well-defined output current would allow to decrease  $V_{ref}$ .

As seen in Fig. 9, the post-layout simulations' efficiency is lower than that of schematic simulations, particularly for low-current outputs. This is mainly due to increased delay of the phase controller caused by parasitic capacitances. Furthermore, the minimum pulse width that the phase controller can produce is also affected by parasitic capacitances, which limits the regulating capability of the circuit for low currents. Next to the possible improvements listed above, careful redesign of the critical nodes in the phase controller could improve the post-layout results.

#### V. CONCLUSION

Power efficiency plays an important role in developing large-scale multichannel stimulator systems. Each channel should have an individually regulated supply voltage for optimal efficiency. This work presented a regulating rectifier topology specifically designed for output stages of current-mode stimulator systems. Designed to supply low-power outputs of single-channel stimulators and operate in parallel in a multichannel system, the proposed design enables channel-specific voltage regulation with a scalable design. The current design improves the power efficiency by up to 45% with respect to that of conventional output drivers with a fixed voltage supply, and several improvements are proposed to increase the power efficiency further.

#### REFERENCES

- [1] E. Fernández, A. Alfaro, and P. González-López, "Toward Long-Term Communication With the Brain in the Blind by Intracortical Stimulation: Challenges and Future Prospects," Frontiers in Neuroscience, vol. 14, no. August, 8 2020. [Online]. Available: https://www.frontiersin.org/ article/10.3389/fnins.2020.00681/full

- [2] D. R. Merrill, M. Bikson, and J. G. Jefferys, "Electrical stimulation of excitable tissue: design of efficacious and safe protocols," *Journal of Neuroscience Methods*, vol. 141, no. 2, pp. 171–198, 2 2005. [Online]. Available: https://linkinghub.elsevier.com/retrieve/pii/ S0165027004003826

- [3] T. S. Davis, R. A. Parker, P. A. House, E. Bagley, S. Wendelken, R. A. Normann, and B. Greger, "Spatial and temporal characteristics of V1 microstimulation during chronic implantation of a microelectrode array in a behaving macaque," *Journal of Neural Engineering*, vol. 9, no. 6, p. 065003, 12 2012. [Online]. Available: https: //iopscience.iop.org/article/10.1088/1741-2560/9/6/065003

- [4] E. Noorsal, H. Xu, K. Sooksood, and M. Ortmanns, "Multichannel Microstimulating SoC," in *Handbook of Biochips*. New York, NY: Springer New York, 2022, pp. 1285–1316. [Online]. Available: https://link.springer.com/10.1007/978-1-4614-3447-4\_18

- [5] S. K. Arfin and R. Sarpeshkar, "An Energy-Efficient, Adiabatic Electrode Stimulator With Inductive Energy Recycling and Feedback Current Regulation," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 6, no. 1, pp. 1–14, 2 2012. [Online]. Available: http://ieeexplore.ieee.org/document/6036003/

- [6] Z. Luo, M.-D. Ker, T.-Y. Yang, and W.-H. Cheng, "A Digitally Dynamic Power Supply Technique for 16-Channel 12 V-Tolerant Stimulator Realized in a 0.18- μm 1.8-V/3.3-V Low-Voltage CMOS Process," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 11, no. 5, pp. 1087–1096, 10 2017. [Online]. Available: http://ieeexplore.ieee.org/document/7983416/

- [7] Z. Luo and M. D. Ker, "A High-Voltage-Tolerant and Power-Efficient Stimulator with Adaptive Power Supply Realized in Low-Voltage CMOS Process for Implantable Biomedical Applications," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 8, no. 2, pp. 178–186, 6 2018. [Online]. Available: https://ieeexplore.ieee.org/document/8265617/

- [8] I. Williams and T. G. Constandinou, "An Energy-Efficient, Dynamic Voltage Scaling Neural Stimulator for a Proprioceptive Prosthesis," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 7, no. 2, pp. 129–139, 4 2013. [Online]. Available: http://ieeexplore.ieee.org/ document/6508875/

- [9] A. Rashidi, N. Yazdani, and A. M. Sodagar, "Fully implantable, multi-channel microstimulator with tracking supply ribbon, multi-output charge pump and energy recovery," *IET Circuits, Devices & Systems*, vol. 15, no. 2, pp. 104–120, 3 2021. [Online]. Available: https://onlinelibrary.wiley.com/doi/10.1049/cds2.12007

- [10] M. N. van Dongen and W. A. Serdijn, "A Power-Efficient Multichannel Neural Stimulator Using High-Frequency Pulsed Excitation From an Unfiltered Dynamic Supply," *IEEE Transactions on Biomedical Circuits* and Systems, vol. 10, no. 1, pp. 61–71, 2 2016. [Online]. Available: http://ieeexplore.ieee.org/document/6965660/

- [11] H.-M. Lee, H. Park, and M. Ghovanloo, "A Power-Efficient Wireless System With Adaptive Supply Control for Deep Brain Stimulation," *IEEE Journal of Solid-State Circuits*, vol. 48, no. 9, pp. 2203–2216, 9 2013. [Online]. Available: http://ieeexplore.ieee.org/document/6584038/

- [12] C. Kim, S. Ha, J. Park, A. Akinin, P. P. Mercier, and G. Cauwenberghs, "A 144-MHz Fully Integrated Resonant Regulating Rectifier With Hybrid Pulse Modulation for mm-Sized Implants," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 11, pp. 3043–3055, 11 2017. [Online]. Available: http://ieeexplore.ieee.org/document/8013680/

- [13] T. Lu, Z.-Y. Chang, J. Jiang, K. Makinwa, and S. Du, "A 13.56MHz Fully Integrated 91.8% Efficiency Single-Stage Dual-Output Regulating Voltage Doubler for Biomedical Wireless Power Transfer," in 2023 IEEE Custom Integrated Circuits Conference (CICC). IEEE, 4 2023, pp. 1–2. [Online]. Available: https://ieeexplore.ieee.org/document/10121186/

- [14] E. Fernández, A. Alfaro, C. Soto-Sánchez, P. Gonzalez-Lopez, A. M. Lozano, S. Peña, M. D. Grima, A. Rodil, B. Gómez, X. Chen, P. R. Roelfsema, J. D. Rolston, T. S. Davis, and R. A. Normann, "Visual percepts evoked with an intracortical 96-channel microelectrode array inserted in human occipital cortex," *Journal of Clinical Investigation*, vol. 131, no. 23, 12 2021. [Online]. Available: https://www.jci.org/articles/view/151331

- [15] R. Lycke, R. Kim, P. Zolotavin, J. Montes, Y. Sun, A. Koszeghy, E. Altun, B. Noble, R. Yin, F. He, N. Totah, C. Xie, and L. Luan, "Low-threshold, high-resolution, chronically stable intracortical microstimulation by ultraflexible electrodes," bioRxiv, 1 2023. [Online]. Available: http://biorxiv.org/content/early/2023/02/21/2023.02.20.529295.abstract

- [16] N. Almarri, D. Jiang, P. Langlois, M. Rahal, and A. Demosthenous, "High Efficiency Power Management Unit for Implantable Optical-Electrical Stimulators," *IEEE Open Journal of Circuits and Systems*, pp. 1–1, 2023. [Online]. Available: https://ieeexplore.ieee.org/document/ 10029935/

- [17] L. Cheng, W. H. Ki, Y. Lu, and T. S. Yim, "Adaptive On/Off Delay-Compensated Active Rectifiers for Wireless Power Transfer Systems," *IEEE Journal of Solid-State Circuits*, vol. 51, no. 3, pp. 712–723, 3 2016.

- [18] H. M. Lee and M. Ghovanloo, "An integrated power-efficient active rectifier with offset-controlled high speed comparators for inductively powered applications," *IEEE Transactions on Circuits and Systems I:* Regular Papers, vol. 58, no. 8, pp. 1749–1760, 2011.

- [19] E. Ozalevli, N. Femia, G. Di Capua, R. Subramonian, D. Du, J. Sankman, and M. El Markhi, "A Cost-Effective Adaptive Rectifier for Low Power Loosely Coupled Wireless Power Transfer Systems," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 65, no. 7, pp. 2318–2329, 7 2018. [Online]. Available: https://ieeexplore.ieee.org/document/8241828/

- [20] X. Li, C. Y. Tsui, and W. H. Ki, "A 13.56 MHz Wireless Power Transfer System With Reconfigurable Resonant Regulating Rectifier and Wireless Power Control for Implantable Medical Devices," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 4, pp. 978–989, 4 2015.

- [21] J. Van Mulders, D. Delabie, C. Lecluyse, C. Buyle, G. Callebaut, L. Van der Perre, and L. De Strycker, "Wireless Power Transfer: Systems, Circuits, Standards, and Use Cases," 8 2022.

- [22] S. Pal and W. H. Ki, "40.68 MHz Digital On-Off Delay-Compensated Active Rectifier for WPT of Biomedical Applications," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 67, no. 12, pp. 3307–3311, 12 2020.

- [23] L. Hu, L. Cheng, Y. Yao, T. S. Yim, W. H. Ki, and C. Y. Tsui, "A 40.68MHz Active Rectifier with Hybrid Delay Compensation Scheme," in 2018 IEEE Asia Pacific Conference on Circuits and Systems, APCCAS 2018. Institute of Electrical and Electronics Engineers Inc., 1 2019, pp. 501–504.