# A 6800- $\mu$ m<sup>2</sup> Resistor-Based Temperature Sensor with ±0.35 °c (3 $\sigma$ ) Inaccuracy in 180-nm CMOS

Angevare, Jan A.; Makinwa, Kofi A.A.

DOI

10.1109/JSSC.2019.2921450

**Publication date**

**Document Version** Final published version

Published in

IEEE Journal of Solid-State Circuits

Citation (APA) Angevare, J. A., & Makinwa, K. A. A. (2019). A 6800- $\mu$  m<sup>2</sup> Resistor-Based Temperature Sensor with ±0.35 °c (3 $\sigma$ ) Inaccuracy in 180-nm CMOS. *IEEE Journal of Solid-State Circuits*, *54*(10), 2649-2657. Article 8753607. https://doi.org/10.1109/JSSC.2019.2921450

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A 6800- $\mu$ m<sup>2</sup> Resistor-Based Temperature Sensor With $\pm 0.35$ °C (3 $\sigma$ ) Inaccuracy in 180-nm CMOS

Jan A. Angevare<sup>6</sup>, Student Member, IEEE, and Kofi A. A. Makinwa<sup>6</sup>, Fellow, IEEE

Abstract—This paper describes a compact resistor-based temperature sensor that has been realized in a 180-nm CMOS process. It occupies only 6800  $\mu m^2$ , thanks to the use of a highly digital voltage-controlled oscillator (VCO)-based phase-domain sigma–delta modulator, whose loop filter consists of a compact digital counter. Despite its small size, the sensor achieves  $\pm 0.35~^{\circ}\mathrm{C}~(3\sigma)$  inaccuracy from  $-35~^{\circ}\mathrm{C}$  to 125 °C. Furthermore, it achieves 0.12 °C  $(1\sigma)$  resolution at 2.8 kSa/s, which is mainly limited by the time-domain quantization imposed by the counter.

Index Terms—CMOS temperature sensor, phase-to-digital converter, thermal sensing, voltage-controlled oscillator (VCO)-based phase-domain sigma–delta modulator (PD $\Sigma\Delta M$ ), Wien bridge (WB).

# I. INTRODUCTION

EAT dissipation is a major issue in system-on-chips (SoCs) [1] since cooling techniques have failed to keep up with the growing energy density of modern processes. In consequence, SoCs heat up rapidly and may overheat if their power consumption is not throttled back. Overheating accelerates aging, degrades reliability, and may even cause a system failure. Therefore, modern SoCs usually incorporate thermal management systems, which monitor die temperature and throttle performance when needed either by reducing clock frequencies and/or supply voltages [2], [3].

The key specifications of such temperature sensors are speed, size, accuracy, and supply voltage insensitivity. Thermal transients have time constants in the order of a few milliseconds and, therefore, must be sampled at kSa/s rates. The heat distribution in an SoC will typically be non-uniform, featuring a number of so-called hot-spots whose intensity and location change dynamically as a function of workload. As a result, accurate thermal monitoring often requires the use of several tens of temperature sensors [4], and so each of them should be as small as possible. This makes it easier to include them in the layout of dense digital

Manuscript received January 29, 2019; revised April 24, 2019; accepted May 26, 2019. Date of publication July 2, 2019; date of current version September 24, 2019. This paper was approved by Guest Editor Jae-Yoon Sim. (Corresponding author: Jan A. Angevare.)

The authors are with the Department of Microelectronics, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: j.a.angevare@tudelft.nl; k.a.a.makinwa@tudelft.nl).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2019.2921450

blocks and, therefore, easier to place near potential hotspots. Moderate accuracy is required to reduce the safety margin between the measured and the desired performance throttling temperatures, and thus maximize performance. Finally, such sensors should be insensitive to supply voltage changes since performance throttling will change the latter significantly.

Most temperature sensors proposed for thermal management applications belong to one of the three types, i.e., bipolar junction transistor (BJT), gate-delay, and thermal-diffusivitybased temperature sensors. The most common are BJT-based temperature sensors [5]. In [6], a current-mode readout technique is used to realize a small (3800  $\mu$ m<sup>2</sup>) and moderately accurate (1.8 °C from -20 °C to 130 °C) n-p-n-based temperature sensor. In later work [7], the readout was modified to work with p-n-ps, which are more commonly available. Although BJT-based sensors can be quite accurate, their voltage headroom requirements do not scale with the technology. As a scaling-friendly alternative, sensors that exploit the temperature-dependent delay of CMOS logic gates have been proposed [8], [9]. Although they can be quite small, they are inherently sensitive to supply voltage variations and MOSFET aging. The third type of sensor exploits the temperature-dependent rate at which heat diffuses through silicon. Such thermal diffusivity (TD) sensors are as accurate as BJT-based sensors, can be quite compact (1650  $\mu$ m<sup>2</sup> [10]), and scale well with the technology. However, they are comparatively power hungry [10]–[13].

Recently, temperature sensors based on silicided polysilicon resistors have been shown to be both stable, accurate, and energy efficient [14], [15]. The voltage insensitivity and large temperature coefficient (0.3%/°C) of this type of resistors make the resulting sensors well suited for use in thermal monitoring applications. However, only two resistor-based temperature sensor designs with areas less than  $10\,000~\mu\text{m}^2$  have been reported so far [15], [16]. Of these, only [15] achieves good accuracy, but its output is a temperature-dependent frequency, and, therefore additional circuitry is required to generate a digital output.

This paper, an expanded version of [17], proposes ways of reducing the area of resistor-based temperature sensors while also maintaining their advantages: voltage insensitivity, accuracy, and energy efficiency. The result is a temperature sensor that achieves both small area (6800  $\mu$ m<sup>2</sup>) and good accuracy [ $\pm 0.35$  °C ( $3\sigma$ ) after a two-point trim].

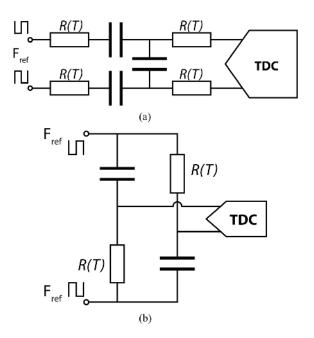

Fig. 1. (a) Differential WB. (b) PPF.

#### II. RESISTOR-BASED TEMPERATURE SENSORS

# A. Sensor Topologies

There are two ways of using a temperature-dependent resistor R(T) to generate a digital representation of temperature. The first involves the use of a Wheatstone bridge (WhB) to compare the value of R(T) with that of a stable resistor, or to one with a different temperature dependence. The output of the bridge can then be digitized by an ADC [18]. The second involves the combination of R(T) with a stable capacitor to realize a temperature-dependent RC filter, whose phase shift can then be digitized using a stable time reference [14]–[16].

On-chip resistors also suffer from process spread. This is particularly problematic in a WhB, which employs two different types of resistors, and, therefore, suffers from two different sources of spread [18]. Although on-chip capacitors also suffer from the spread, they are comparatively stable over temperature and so contribute much less temperature-sensing error. Furthermore, SoCs are usually clocked by sufficiently accurate time references. For example, for a Wienbridge (WB) filter realized with 0.3%/K resistors, the 100-ppm frequency error of a typical low-cost crystal oscillator will only result in 0.025 °C temperature-sensing error.

#### B. Filter Choice

As shown in Fig. 1, two types of RC filters have been used in resistor-based temperature sensors: the WB [14] and the polyphase filter (PPF) [15]. Both combine first order low- and high-pass filters to achieve double the phase sensitivity of a first-order filter. However, a PPF requires fewer components than a WB filter. It also has slightly more phase sensitivity, at the expense of a slightly more non-linear resistance-to-phase characteristic. However, when driven by a rail-to-rail square wave, the output of a PPF will exceed the supply rails, which complicates the design of its readout circuitry. Although this

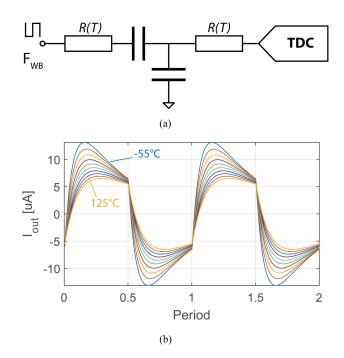

Fig. 2. (a) Single-ended WB. (b) Output waveform of a single-ended WB at different temperatures.

is not the case for a WB, the resulting output voltage swing will still exceed the linear range of a simple differential pair. For this reason, WB sensors are usually read out in current-mode [Fig. 1(a)], by connecting the resistors in their output branches to a virtual ground [14] or to a current buffer [19].

In this work, a single-ended WB is used, which has the same number of components and occupies the same area as a PPF [Fig. 2(a)]. It is realized with silicided p-poly resistors ( $R_{\rm WB}=28~k\Omega$ ) and MIM capacitors ( $C_{\rm WB}=1.84~\rm pF$ ), resulting in a center frequency  $F_{\rm WB}=3~\rm MHz$  at room temperature. In the chosen 180-nm process, it occupies only 3700  $\mu \rm m^2$ . When driven by a 1.8-V square wave at  $F_{\rm WB}$ , its output current is as shown in Fig. 2(b). It can be seen that both its shape (phase) and amplitude vary significantly over temperature.

# III. SYSTEM-LEVEL OVERVIEW

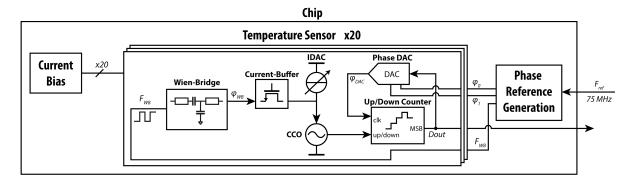

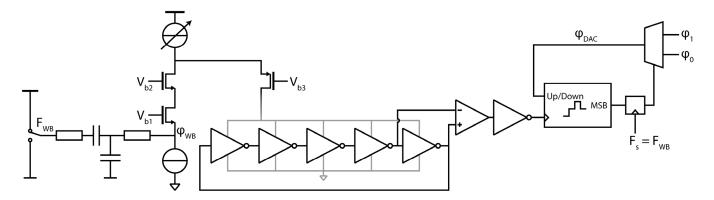

Fig. 3 shows a simplified block diagram of the proposed system. It consists of 20 compact temperature sensors, together with shared bias current and phase reference generator, the latter being driven by an external frequency reference  $F_{\rm REF}(=75 \text{ MHz})$ . Each sensor consists of a single-ended WB, whose phase-shifted output current is digitized by a phase-domain sigma-delta modulator (PD $\Sigma \Delta M$ ) [12]. Instead of using an analog integrator based on large capacitors [12], the modulator's loop filter uses a compact discrete-time integrator based on a counter, which is driven by a currentcontrolled oscillator (CCO) [11]. In turn, the CCO is driven by a current buffer, whose low input impedance facilitates the current readout of the WB. To provide robustness against process spread, the center frequency of the CCO can be trimmed via a current DAC (IDAC). In Section IV, the design of each of these sub-blocks and their impact on sensor performance will be discussed in more detail.

Fig. 3. System-level block diagram.

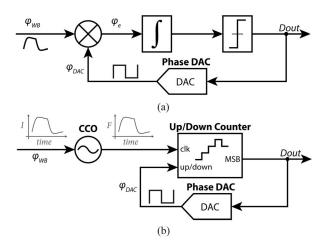

Fig. 4. (a) Block diagram of the phase-domain delta-sigma modulator [12]. (b) CCO-based phase-domain delta-sigma modulator [11].

## IV. PHASE-DOMAIN DELTA-SIGMA MODULATOR

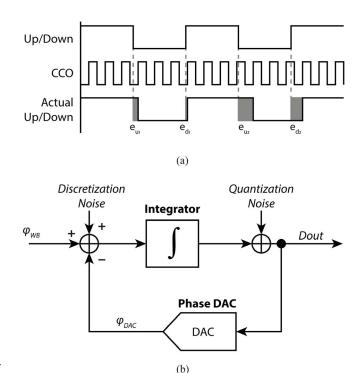

Fig. 4(a) shows a simplified block diagram of a PD $\Sigma\Delta M$  [12]. An input phase ( $\varphi_{WB}$ , at a frequency of  $F_{WB}$ ) is first multiplied by a feedback phase ( $\varphi_{DAC}$ , also at a frequency of  $F_{WB}$ ). For sinusoidal signals, this results in a signal  $\varphi_e$  whose dc component is proportional to  $\cos(\varphi_{WB}-\varphi_{DAC})$ . For phase differences close to 90° P,  $\cos(\varphi_{WB}-\varphi_{DAC}-90^\circ)\sim\varphi_{WB}-\varphi_{DAC}$  and so the demodulator effectively performs a phase-domain subtraction. In practice, the higher harmonics present in the WB output and the square wave of the phase DAC output also contribute to  $\varphi_e$  but the error is less than 5° P. The dc component of  $\varphi_e$  and the harmonics are integrated and then digitized by a 1-bit quantizer whose output is fed back to the phase DAC. This drives the multiplier's dc output to zero such that the average feedback phase  $\varphi_{DAC}$  is equal to  $\varphi_{WB}+90^\circ P$ .

In this work, as shown in Fig. 4(b), the modulator's loop filter consists of a digital counter, which is driven by a CCO [11]. The latter converts the input signal from the current domain to the frequency domain, allowing the counter to be used as an integrator. By toggling the counter's up/down signal, the polarity of this integration can also be toggled, thus effectively multiplying the input signal with the up/down signal. The modulator's 1-bit quantizer can then be realized by simply

Fig. 5. (a) Timing diagram of the up/down and CCO signals. (b) Linear model of the voltage-controlled oscillator (VCO)-based phase-domain sigma-delta modulator.

sampling and evaluating the counter's MSB. The result is a highly digital PD $\Sigma \Delta M$  [11], which can be easily scaled.

#### A. Counter Time-Discretization Noise

The downside of using a counter as an integrator is that it quantizes the phase of the CCO and, therefore, introduces time-domain discretization noise. Fig. 5(a) illustrates this: at the moment the up/down signal toggles, the CCO phase, and therefore the integrator's state, is quantized. In the example shown, the CCO goes through approximately 3.15 cycles in the first "up" counting period. However, the counter truncates this to 3 cycles, creating an error in the integrator state, and also creating an error at the start of the next "down" counting period, since it already starts at the truncated value. As shown in Fig. 5(b), this *discretization* noise can be modeled as an additive white-noise source at the input of the integrator [20] and, therefore, does not benefit from noise shaping.

Assuming that the transitions of the up/down signal are random with respect to the CCO phase, which is the case if the CCO frequency  $F_{\rm CCO}$  is asynchronous with respect to the demodulating frequency  $F_{\rm WB}$ , and/or if  $F_{\rm CCO}$  is dithered by thermal noise, the counter's rounding error will have a uniform distribution. With this assumption, the total in-band phase noise (in radians) is given by [20]

$$\sigma_{\rm P} = \sqrt{\frac{2}{3 \cdot \rm OSR}} \cdot \frac{\pi \, F_{\rm WB}}{F_{\rm CCO, pp}} \tag{1}$$

where  $F_{\text{CCO,pp}}$  is the peak-to-peak variation of  $F_{\text{CCO}}$  and over-sampling ratio (OSR) is the PD $\Sigma \Delta M$ 's OSR. It can be seen that the discretization noise can be minimized either by decreasing  $F_{WB}$ , increasing the modulator's OSR, or increasing the CCO's frequency swing. In this design,  $F_{WB} = 3 \text{ MHz}$ , which in turn limits the modulator's sampling frequency to 3 MHz, since  $F_s \leq F_{WB}$  in a PD $\Sigma \Delta M$ . The OSR is then set by the signal bandwidth, which is defined by the desired conversion rate (3 kSa/s) and the choice of a simple sinc<sup>1</sup> decimation filter. On the other hand, increasing the CCO's frequency swing requires higher CCO frequencies, and hence higher power consumption. In this design,  $F_{CCO,pp}$  is set to 600 MHz, which results in a resolution of 0.12 °C (rms). Although this is much worse than the mK-level resolution of the WB itself [19], it is good enough for thermal monitoring applications.

#### B. Up/Down Counter

Unlike an analog integrator, a counter does not clip. Instead, it wraps around. This corrupts the counter's state and, therefore, must be prevented. After one period of the sampling clock, the number of counts accumulated by the counter is given by [20]

$$C_{\Delta} = \frac{F_{\text{CCO,pp}}}{\pi F_{\text{WB}}} \cdot (\varphi_{\text{WB}} - \varphi_{\text{DAC}}). \tag{2}$$

In a PD $\Sigma\Delta M$ , the counter's state oscillates around its mid-code; therefore, to prevent wrap-around,  $C_{\Delta}$  should never exceed half the counter length.

From simulations,  $\varphi_{WB}$  varies by about 23° P over the targeted temperature range (-35 °C to 125 °C). With  $\pm 40\%$  spread in RC, this results in a worst case phase difference  $\varphi_{WB} - \varphi_{DAC}$  of about 40°. Given  $F_{CCO,pp} = 600$  MHz and  $F_{WB} = 3$  MHz, (2) indicates that the maximum value of  $C_{\Delta}$  is 44. A 7-bit counter is thus required to prevent wrap-around.

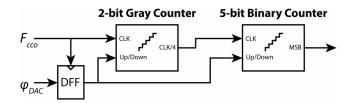

To guarantee a 600 MHz (pp) frequency swing even in the presence of process variations, both the CCO and the counter are designed to operate up to 800 MHz over process, voltage and temperature (PVT). To achieve this, the counter is split up into two parts: a fine two-bit counter and a coarse 5-bit counter (Fig. 6) [13]. This reduces its power consumption since clock gating can be used to ensure that the coarse counter only operates at one quarter the frequency of the fine counter. The fine counter is a gray code counter, resulting in a faster and simpler implementation. To limit meta-stability issues to a single D flip-flop (D-FF) rather than to the entire counter, the up/down signal  $\varphi_{\rm DAC}$  is re-clocked by  $F_{\rm CCO}$ , before being applied to the counter.

Fig. 6. 7-bit counter/integrator that splits into a 2-bit gray-code counter and a coarse 5-bit binary counter [13].

Fig. 7. 5-stage ring oscillator with a differential pair to level-shift the CCO swing to the full digital waveform.

The counter was synthesized using the normal digital design flow of the 180-nm CMOS process used. Operating at 800 MHz, it consumes 1 mW from a 1.8-V power supply, making it the most power-hungry sub-block of each sensor. However, in a more advanced process, its power consumption will scale dramatically, e.g., to about 130  $\mu$ W in a 65-nm process.

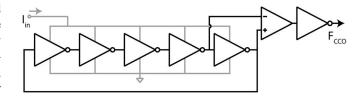

# C. CCO

The CCO consists of a five-stage chain of inverters, which converts the output current of the WB (30  $\mu$ A pp) into the desired 600-MHz frequency swing. To mitigate the CCO center frequency's sensitivity to PVT, a 6-bit IDAC (~30-MHz LSB) is used to trim the CCO's center frequency to ~400 MHz at room temperature. Since this frequency is too high to be readily measured off-chip, the up/down counter is used as a divide-by-128 counter during trimming.

The inverter stages of the CCO do not output logic-compatible signals. Therefore, their outputs are amplified and level-shifted by a differential-pair (Fig. 7). After this, a simple inverter is enough to generate a rail-to-rail logic swing.

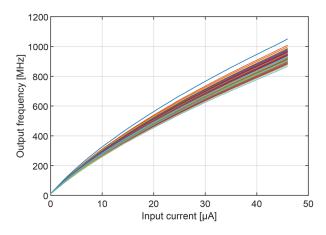

# D. CCO Nonlinearity

As shown in Fig. 8, the CCO's current-to-frequency characteristic is quite non-linear. Since its output is multiplied by the square-wave output of the phase DAC, distortion components at odd harmonics of  $F_{WB}$  will fold back to baseband. In other words, any CCO non-linearity will cause errors in the error signal  $\varphi_e$  of the PD $\Sigma$   $\Delta$ M. Although the CCO frequency swing could be limited to improve linearity, this would increase the discretization noise. Fortunately, any systematic errors will be accounted for during the sensor's calibration, while any spread can be mitigated by trimming.

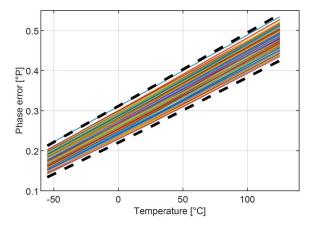

Monte-Carlo simulations results are plotted in Fig. 9 and show the additional phase shift resulting from CCO nonlinearity. Although this is significant (ranging from  $0.2^{\circ}$  P to  $0.5^{\circ}$  P), its spread (mainly offset) is relatively small and

Fig. 8. Monte-Carlo (process + mismatch) simulation of the CCO current-to-frequency transfer.

Fig. 9. Simulated additional phase shift due to the CCO non-linearity at -55 °C, 25 °C, and 125 °C (Monte-Carlo process + mismatch). Dashed line:  $3\sigma$  values.

can be reduced to less than 80 mK  $(3\sigma)$  after a one-point trim.

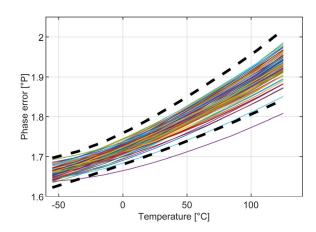

Variations in the WB's output current swing will also vary the CCO's effective non-linearity, which, in turn, will cause variations in the detected WB phase. This may be due to power supply variations and/or the spread ( $\pm 20\%$ ) of the WB resistors. The former will result in a finite power supply sensitivity, which is simulated to be 5.3 °C/V, close to the measured supply sensitivity of 4.6 °C/V. The latter will cause variations in the measured phase (Fig. 10) and therefore increase inaccuracy. This can only be somewhat mitigated by trimming: to 1.2 °C ( $3\sigma$ ) after a one-point trim, and to 0.13 °C ( $3\sigma$ ) after a two-point trim.

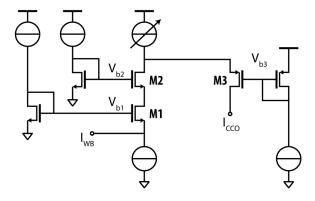

# E. Current Buffer

As seen from its supply terminals, the impedance of the CCO is quite significant compared to that of the WB resistors. Therefore, to avoid altering its phase response, a current buffer is inserted between the WB and the CCO. As shown in Fig. 11, the current buffer consists of a common-gate amplifier (M1), with an input impedance  $(1/\text{gm} \sim 600 \,\Omega) \ll R_{\text{WB}}$  at  $F_{\text{WB}}$ , and a folded-cascode output that drives the CCO. Since they are both small (for speed and area) and the CCO input has a large

Fig. 10. Simulated Monte-Carlo (process + mismatch) spread due to amplitude variations in the WB output current.

Fig. 11. Cascodes in the current-buffer reduce the input impedance as seen from the WB side.

Fig. 12. Simulated Monte-Carlo (process + mismatch) spread due to current buffer and bias spread.

voltage swing, two cascodes (M2, M3) are used to prevent the voltage swing across the CCO from entering the WB. The required bias voltages are generated by diode-connected MOSFETs, each of which is biased with a nominal 5.6  $\mu$ A.

Fig. 12 shows the simulated phase shift spread due to the spread of the current buffer and its bias current. Once more, there is a relatively large average shift ( $\sim$ 1.8° P) and a nonlinear temperature dependence, both of which will be corrected during the sensor's calibration. Simulations show that the

Fig. 13. Complete sensor overview.

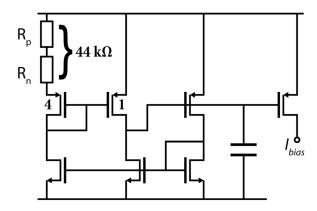

Fig. 14. Circuit diagram of the bias source.

resulting temperature error is less than 0.6 °C after a one-point and less than 0.1 °C after a two-point trim.

# F. Shared Bias and Phase Reference Generation

Fig. 13 shows the complete system, in which the WB is driven by a square-wave signal at  $F_{\rm WB}$ , which then generates an output current with a phase shift  $\varphi_{\rm WB}$ . This is then fed to the current buffer and used to drive the CCO, which, in turn, drives the PD $\Sigma$   $\Delta$ M. A phase generator provides the required reference signals ( $F_{\rm WB}=0^{\circ}$ ,  $\varphi_0=90^{\circ}$  P  $-20^{\circ}$  P, and  $\varphi_1=90^{\circ}$  P  $+20^{\circ}$  P).

The phase reference generator is driven by an external 75-MHz clock. It consists of a programmable divide-by-2N counter, whose output is a square wave with a frequency of  $F_{WB}$  and a 50% duty cycle. This is then used to drive the WB, as well as a programmable delay chain, which generates the phase references used by the phase DAC. As shown in Fig. 3, the phase generator is shared by all 20 temperature sensors on the same chip. It occupies 1200  $\mu$ m² and dissipates less than 0.1 mW (simulated). It should be noted that a non-programmable generator would only occupy 430  $\mu$ m².

The bias current generator (Fig. 14) operates by forcing a proportional to absolute temperature voltage across a resistor. A composite resistor, made by combining two resistors with opposite temperature coefficients, ensures that the resulting current is relatively flat over temperature. This current is then

Fig. 15. Chip photograph.

mirrored out to all 20 sensors. The residual curvature is less than 10%, which means that a single trim is sufficient to ensure that the CCO operates properly over the military temperature range. The bias current generator dissipates about 33  $\mu$ W and occupies 2500  $\mu$ m<sup>2</sup>.

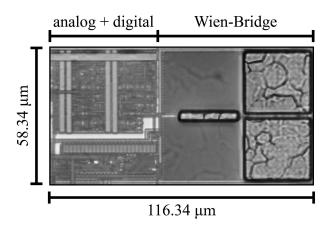

#### V. MEASUREMENTS

The system was realized in a standard 180-nm CMOS technology (Fig. 15). Each chip contains 20 temperature sensors, which each occupies  $6800~\mu\text{m}^2$ , as well as a shared bias current and a phase reference generator. The system operates from a 1.8-V supply voltage and dissipates 1.6 mW (60% is consumed by the counter, 39% by the current buffer and CCO, and 1% by the WB).

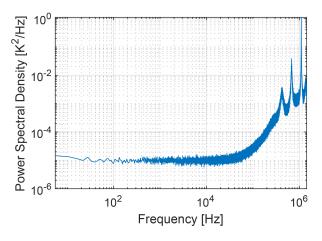

Due to the finite input impedance of the current buffer, and the spread and parasitic capacitances of the WB resistors, the average center frequency of the implemented WB filters is a bit lower than 3 MHz. To accommodate this, all the sensors were driven at  $F_{\rm WB} \approx 2.9$  MHz(= 75 MHz/2·13). A fast Fourier transform (FFT) of the PD $\Sigma$   $\Delta$ M's bitstream output (Fig. 16) confirms that the sensor's noise floor is indeed dominated by the counter's discretization noise. After decimation by an off-chip 1024-tap sinc<sup>1</sup> filter, the sensor achieves a resolution of 0.12 °C (1 $\sigma$ ) at a conversion rate of 2.8 kSa/s, which is in good agreement with the discretization noise levels predicted by (2).

Fig. 16. PSD of  $2^{19}$  bit-stream samples (with the mean value removed to better observe LF noise), averaged  $100\times$ .

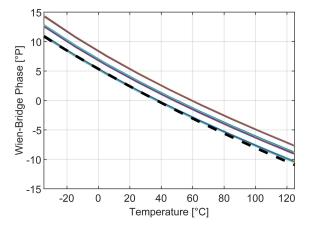

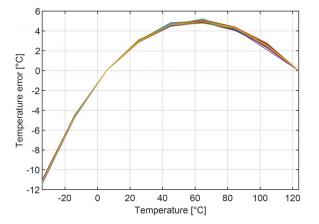

Fig. 17. Measured phase of 160 samples from 8 chips compared to the simulated phase (dashed line).

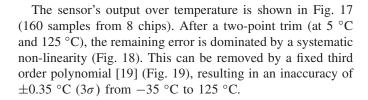

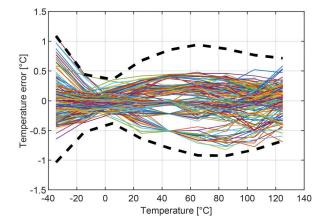

Fig. 18. Temperature error of 160 samples from 8 chips after two-point trim but before systematic non-linearity correction.

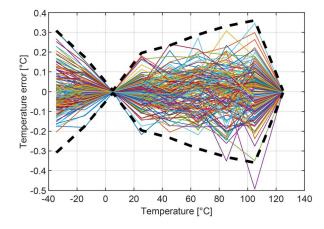

Fig. 19. Measured inaccuracy of 160 samples from 8 chips after a two-point temperature trim. Dashed line:  $3\sigma$  error.

Fig. 20. Measured inaccuracy of 160 samples from 8 chips after a one-point temperature trim. Dashed line:  $3\sigma$  error.

Fig. 21. Measured inaccuracy of 160 samples from 8 chips after a correlated one-point temperature trim. Dashed line:  $3\sigma$  error.

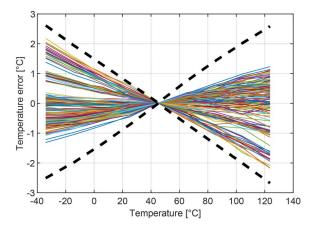

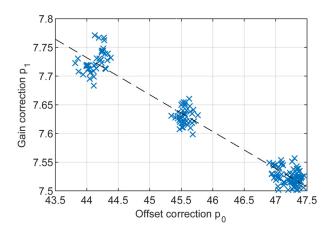

After a 1-point offset trim, the sensor achieves an inaccuracy of  $\pm 2.7$  °C ( $3\sigma$ ) (Fig. 20). This can be improved to  $\pm 1.2$  °C (Fig. 21) by applying a correlated one-point trim [14]. This trim relies on the correlation of offset and gain errors of individual sensors with respect to their average master curve (Fig. 22), and so the gain error can be estimated from the offset

| Publication                             | This Work  | U. Sonmez [10]    | S. Pan [14] | W. Choi [15] | Y-C Hsu [21] | M. Eberlein<br>[6] |

|-----------------------------------------|------------|-------------------|-------------|--------------|--------------|--------------------|

| Year                                    | 2018       | 2016              | 2018        | 2018         | 2017         | 2016               |

| Туре                                    | Resistor   | TD                | Resistor    | Resistor     | PNP          | NPN                |

| Technology                              | 180nm      | 40nm              | 180nm       | 65nm         | 28nm         | 28nm               |

| Area (μm²)                              | 6800¹      | 1650 <sup>1</sup> | 720000¹     | 7000¹        | 9461         | 3800               |

| Inaccuracy (3σ, °C)                     | -          | 1.4               | -           | -            | 0.87         | 1.8                |

| Inaccuracy, 1-pt trim (3σ, °C)          | -          | 0.75              | 0.2         | 2.47         | -            | -                  |

| Inaccuracy, 2-pt trim (3 $\sigma$ , °C) | 0.35       | -                 | 0.03        | 0.12         | -            | -                  |

| Temperature Range (°C)                  | -35 to 125 | -40 to 125        | -40 to 85   | -40 to 85    | 0 to 125     | -20 to 130         |

| Resolution (°C)                         | 0.12       | 0.36              | 0.00041     | 0.0025       | 0.15         | 0.5                |

| Speed (kSa/s)                           | 3          | 1                 | 0.2         | 1            | 0.12         | 31.25              |

| Supply Voltage (V)                      | 1.8        | 0.9-1.2           | 1.6-2.0     | 0.85-1.05    | 1.8          | 1.1-2.0            |

| Supply Sensitivity (°C/V)               | 4.6        | 2.8               | 0.17        | 0.5          | -            | $0.1^{2}$          |

| Power (mW)                              | 1.61       | 2.51              | $0.16^{1}$  | $0.068^{1}$  | 0.01875      | 0.0176             |

${\bf TABLE~I}$  Performance Summary and Comparison With the State of the Art

<sup>&</sup>lt;sup>1</sup> Additional circuitry required (e.g. bias current and phase reference generators (this work), decimation filters (this work, [10, 13] or frequency-to-digital converters [14]). <sup>2</sup> Simulated, measured <0.5LSB~0.33°C/V.

Fig. 22. Correlation between offset correction p<sub>0</sub> and gain correction p<sub>1</sub>.

at 45 °C. Simulations show that this correlation is mainly due to the phase errors caused by CCO non-linearity. In Table I, the sensor's performance is compared to other state-of-the-art temperature sensors. The area and power of the bias and phase generators are not included, since these are both negligible compared to that of the 20 sensors.

As stated before, the CCO center frequency will spread over PVT and so must be trimmed to about 400 MHz. Since the intra-batch CCO spread is small and the same bias current generator is used, the same trim code can be used for all the CCOs on one die. This means that in practice, only one CCO (of the 20) needs to be trimmed, which considerably reduces the required effort.

### VI. CONCLUSION

A compact and accurate resistor-based temperature sensor has been proposed. Compared to other resistor-based temperature sensors aimed at thermal management, this design achieves competitive area and accuracy despite being realized in a mature 180-nm process. Its low area is mainly due to the use of a highly digital CCO-based ADC. This design scales well with technology and its performance is expected to improve when ported to more advanced processes.

#### REFERENCES

- [1] M. Horowitz, "1.1 computing's energy problem (and what we can do about it)," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2014, pp. 10–14.

- [2] D. Brooks and M. Martonosi, "Dynamic thermal management for high-performance microprocessors," in *Proc. HPCA 7th Int. Symp. High-Perform. Comput. Archit.*, Jan. 2001, pp. 171–182.

- [3] E. Rotem, J. Hermerding, C. Aviad, and C. Harel, "Temperature measurement in the Intel Core duo processor," *Proc. 12th Int. Workshop Therm. Invest. Therminic*. New York, NY, USA: Nice, Sep. 2006, pp. 23–27.

- [4] M. Ware et al., "Architecting for power management: The IBM POWER7 approach," in Proc. 16th Int. Symp. High-Perform. Comput. Archit., Bengaluru, India, Jan. 2010, pp. 1–11.

- [5] J. S. Shor and K. Luria, "Miniaturized BJT-based thermal sensor for microprocessors in 32- and 22-nm technologies," *IEEE J. Solid-State Circuits*, vol. 48, no. 11, pp. 2860–2867, Nov. 2013.

- [6] M. Eberlein and I. Yahav, "A 28 nm CMOS ultra-compact thermal sensor in current-mode technique," in *Proc. IEEE Symp. VLSI Circuits (VLSI-Circuits)*, Jun. 2016, pp. 1–2.

- [7] C. Lu, S. Ravikumar, A. D. Sali, M. Eberlein, and H. Lee, "An 8b subthreshold hybrid thermal sensor with ±1.07 °C inaccuracy and single-element remote-sensing technique in 22 nm FinFET," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2018, pp. 318–320.

- [8] M. Cochet et al., "A 225 μm<sup>2</sup> probe single-point calibration digital temperature sensor using body-bias adjustment in 28 nm FD-SOI CMOS," *IEEE Solid-State Circuits Lett.*, vol. 1, no. 1, pp. 14–17, Jan. 2018.

- [9] K. Yang et al., "9.2 A 0.6nJ–0.22/+0.19 °C inaccuracy temperature sensor using exponential subthreshold oscillation dependence," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 160–161.

- [10] U. Sönmez, F. Sebastiano, and K. A. A. Makinwa, "Compact thermal-diffusivity-based temperature sensors in 40-nm CMOS for SoC thermal monitoring," *IEEE J. Solid-State Circuits*, vol. 52, no. 3, pp. 834–843, Mar. 2017.

- [11] R. Quan et al., "27.8 A 4600 μm<sup>2</sup> 1.5°C (3s) 0.9kS/s thermal-diffusivity temperature sensor with VCO-based readout," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2015, pp. 1–3.

- [12] C. P. L. van Vroonhoven, and K. A. A. Makinwa, "A CMOS temperature-to-digital converter with an inaccuracy of  $\pm 0.5$  °C ( $3\sigma$ ) from -55 to 125 °C," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2008, pp. 576–577.

- [13] J. Angevare, L. Pedalà, U. Sönmez, F. Sebastiano, and K. A. A. Makinwa, "A 2800-μm<sup>2</sup> thermal-diffusivity temperature sensor with VCO-based readout in 160-nm CMOS," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Nov. 2015, pp. 1–4.

- [14] S. Pan, Y. Luo, S. H. Shalmany, and K. A. A. Makinwa, "A resistor-based temperature sensor with a 0.13 pJ · K2 resolution FoM," *IEEE J. Solid-State Circuits*, vol. 53, no. 1, pp. 164–173, Jan. 2018.

- [15] W. Choi et al., "A compact resistor-based CMOS temperature sensor with an inaccuracy of 0.12 °C (3σ) and a resolution FoM of 0.43 pJ K<sup>2</sup> in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3356–3367, Dec. 2018.

- [16] A. Mordakhay and J. Shor, "Miniaturized, 0.01 mm<sup>2</sup>, Resistor-based thermal sensor with an energy consumption of 0.9 nJ and a conversion time of 80μs for processor applications," *IEEE J. Solid-State Circuits*, vol. 53, no. 10, pp. 2958–2969, Oct. 2018.

- [17] J. Angevare and K. A. A. Makinwa, "A 6800-μm<sup>2</sup> resistor-based temperature sensor in 180-nm CMOS," in *Proc. A-SSCC*, Nov. 2018, pp. 43–46.

- [18] J. Angevare and K. A. A. Makinwa, "A 0.25 mm<sup>2</sup>-resistor-based temperature sensor with an inaccuracy of 0.12 °C (3σ) from -55 °C to 125 °C," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3347–3355, Dec. 2018.

- [19] M. Shahmohammadi, K. Souri, and K. A. A. Makinwa, "A resistor-based temperature sensor for MEMS frequency references," in *Proc. ESSCIRC*, Sep. 2013, pp. 225–228.

- [20] U. Sönmez, F. Sebastiano, and K. A. A. Makinwa, "Analysis and design of VCO-based phase-domain ΣΔ modulators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 5, pp. 1075–1084, May 2017.

- [21] Y.-C. Hsu, C.-L. Tai, M.-C. Chuang, A. Roth, and E. Soenen, "5.9 An 18.75 μW dynamic-distributing-bias temperature sensor with 0.87 °C (3σ) untrimmed inaccuracy and 0.00946 mm² area," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2017, pp. 102–103.

**Jan A. Angevare** (S'15) was born in Leiden, The Netherlands, in 1990. He received the B.Sc. and M.Sc. degrees in electrical engineering from the Delft University of Technology, Delft, The Netherlands, in 2012 and 2015, respectively, where he is currently pursuing the Ph.D. degree.

His current research interests include mixed-signal design and smart sensors.

Kofi A. A. Makinwa (M'97–SM'05–F'11) received the B.Sc. and M.Sc. degrees from Obafemi Awolowo University, Ife, Nigeria, in 1985 and 1988, respectively, the M.E.E. degree from the Philips International Institute, Eindhoven, The Netherlands, in 1989, and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2004.

From 1989 to 1999, he was a Research Scientist with the Philips Research Laboratories, Eindhoven, where he worked on interactive displays and digital recording systems. In 1999, he joined the Delft

University of Technology, where he is currently an Antoni van Leeuwenhoek Professor and the Head of the Microelectronics Department. He has coauthored or edited 15 books, more than 250 technical papers. He holds 30 patents. His research interests include the design of mixed-signal circuits, sensor interfaces, and smart sensors.

Dr. Makinwa is a member of the Royal Netherlands Academy of Arts and Sciences and the Editorial Board of the PROCEEDINGS OF THE IEEE. He was a recipient of the 2005 Simon Stevin Gezel Award from the Dutch Technology Foundation. He was a co-recipient of the 15 best paper awards from the IEEE JOURNAL OF SOLID-STATE CIRCUITS (JSSC), ISSCC, the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, European Solid-State Circuits Conference (ESSCIRC), and Transducers. He is the Analog Subcommittee Chair of the International Solid-State Circuits Conference (ISSCC). He has served as a Distinguished Lecturer and an Elected AdCom Member for the IEEE Solid-State Circuits Society. He has been a Guest Editor of the IEEE JSSC. He serves on the program committees of the VLSI Symposium, ESSCIRC, and the Advances in Analog Circuit Design (AACD) workshop. At the 60th anniversary of ISSCC, he was recognized as a top-10 contributor.