# Library Characterization for Cell-Aware Test

Santosh S. Malagi

## CE-MS-2018-27

#### Abstract

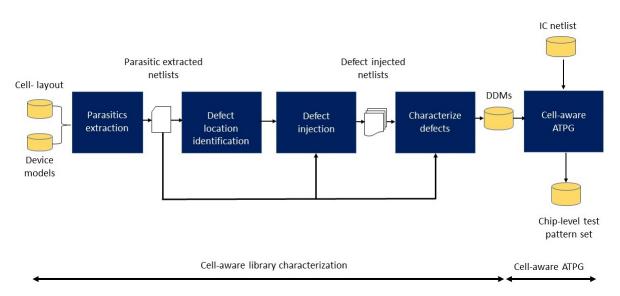

Due to their large number of high-precision, defect-prone manufacturing steps, integrated circuits (ICs) are susceptible to manufacturing defects and hence need to undergo electrical tests to weed out the defective parts and guarantee sufficient outgoing product quality to the customer. A key step in test development for digital logic ICs is automatic test pattern generation (ATPG). Cell-aware test (CAT) is a next-generation test pattern generation approach; its novel feature is that it explicitly addresses cell-internal defects (as opposed to relying on serendipitous coverage by traditional ATPG). CAT consists of two stages - cell-aware library characterization (CA-LC) and cell-aware ATPG. Library characterization uses parasitics-extracted transistor-level netlists to model open and short defects candidates, which are then simulated with an exhaustive set of cell-level test patterns. The results are encoded in the form of defect detection matrices (DDMs). Cell-aware ATPG uses this information to determine a set of test patterns such that, as many as possible cell-internal defects in the circuit are covered.

As an industrial standard-cell library contains hundreds of cells, library characterization is a time consuming task. The target defect set must be realistic and complete, but not unnecessarily large. The objective of this thesis is to improve the library characterization stage of the Cadence CAT flow by effectively and efficiently modelling realistic defects, while trying to minimize the time required for characterization. To achieve this, several improvements to the existing flow are proposed. (1) defining a set of customized settings for the parasitics extraction tool for generating transistor-level netlists, which are well-suited for cell-aware defect modelling (2) elimination of potential defects, which were superfluous elements being inserted into the netlist (3) using superhard defect resistance values for modelling opens and shorts (4) reduction in simulation time by modifying the software flow and, (5) inserting a single short defect between two net pairs to reduce the size of the target defect set. For the 45nm generic library (GPDK045) from Cadence, these modifications resulted in an improvement in test quality by uncovering as many as 1114 false detections and a reduction of 6% in the characterization time. The number of short defects to be simulated reduced by 97.7%. This work was carried out as a part of a joint project on cellaware test between Cadence (supplier of electronic design automation software), IMEC (research organization), and Eindhoven University of Technology.

cādence universiteit **TU/e** Technische Universiteit Eindhoven University of Technology

# **LIBRARY CHARACTERIZATION FOR CELL-AWARE TEST**

by

## Santosh S Malagi

in partial fulfillment of the requirements for the degree of

**Master of Science** in Computer Engineering

at the Delft University of Technology, to be defended publicly on Tuesday September 18, 2018 at 1:00 PM.

Student number: 4602420

Supervisor: Prof. dr. ir. Said Hamdioui, Thesis committee: Dr. ir. Rene van Leuken, Ir. Erik Jan Marinissen,

TU Delft IMEC

An electronic version of this thesis is available at http://repository.tudelft.nl/.

Dedicated to the worldwide community of DfT and EDA engineers, who strive to make the world a better place, one chip at a time!

# **CONTENTS**

| List of Figures  | vii  |

|------------------|------|

| List of Tables   | ix   |

| List of Acronyms | xi   |

| Acknowledgements | xiii |

| 1 | Introduction                                           |     | 1  |

|---|--------------------------------------------------------|-----|----|

|   | 1.1 Motivation behind IC Manufacturing Test            |     | 1  |

|   | 1.2 Cell-Aware Test                                    |     |    |

|   | 1.3 Contribution of the Thesis                         |     | 2  |

|   | 1.4 Thesis Organization.                               |     | 3  |

| 2 | Background Knowledge                                   |     | 5  |

|   | 2.1 Introduction to IC Testing.                        |     | 5  |

|   | 2.1.1 Fault modelling                                  |     | 6  |

|   | 2.1.2 Fault simulation                                 |     | 7  |

|   | 2.1.3 Automatic test pattern generation                |     | 8  |

|   | 2.2 Standard-cell based Design Flow                    |     | 9  |

|   | 2.3 Parasitics Extraction                              |     | 11 |

|   | 2.4 Quantus QRC based Parasitic Extraction Flow.       |     | 13 |

|   | 2.5 Summary                                            |     | 14 |

| 3 | Cell-Aware Test                                        |     | 15 |

| 3 | 3.1 The Evolution of Cell-Aware Test                   |     |    |

|   | 3.2 Library Characterization                           |     |    |

|   | 3.3 Cell-Aware ATPG                                    |     |    |

|   | 3.4 Industrial Applications of Cell-Aware Test.        |     |    |

|   | 3.5 Summary                                            |     |    |

|   |                                                        | ••• |    |

| 4 | Original Cell-Aware Flow by Cadence                    |     | 21 |

|   | 4.1 Overview of Cadence Cell-Aware Test Flow           |     |    |

|   | 4.2 Issues with Cadence Library Characterization Flow  |     |    |

|   | 4.2.1 Parasitic extraction settings                    |     |    |

|   | 4.2.2 Arbitrary thresholds for defect insertion        |     |    |

|   | 4.2.3 Potential defects                                |     |    |

|   | 4.2.4 Resistance values for modelling opens and shorts |     |    |

|   | 4.2.5 Simulation of $ D  + 1$ defect injected netlists |     |    |

|   | 4.2.6 Spectre netlist format                           |     |    |

|   | 4.2.7 Reversal of transistor source-drain terminals    |     |    |

|   | 4.3 Summary                                            | ••• | 28 |

| 5 | Improvements to The Cell-Aware Test Flow               |     | 29 |

|   | 5.1 Related Prior Work                                 |     |    |

|   | 5.2 Parasitic Extraction Settings for Cell-Aware Test. |     |    |

|   | 5.3 Threshold Values for Defect Insertion              |     |    |

|   | 5.4 Elimination of Potential Defects                   |     |    |

|   | 5.5 Insertion of Super-Hard Defects                    |     |    |

|   | 5.6 Reduction in Run-Time by Modifying Software Flow   |     | 37 |

|    | 5.7   | Inserting a Single Short between Net Pairs           | 37 |

|----|-------|------------------------------------------------------|----|

|    | 5.8   | Summary                                              | 38 |

| 6  | Exp   | erimental Results                                    | 41 |

|    | 6.1   | Improvements due to elimination of potential defects | 41 |

|    |       | Improvements due to insertion of super-hard defects. |    |

|    |       | Effect on simulation time                            |    |

|    |       | Reduction in number of shorts                        |    |

|    |       | Analysis for the GPDK045 Library                     |    |

|    | 6.6   | Summary                                              | 47 |

| 7  | Con   | clusion and Future Scope                             | 49 |

| Bi | bliog | raphy                                                | 51 |

| A  | Cod   | e Listings                                           | 53 |

| B  | Cad   | ence Cell Aware Test - RAK directory structure       | 57 |

| С  | Cad   | ence Library Characterization - Software Execution   | 59 |

|    |       |                                                      |    |

# **LIST OF FIGURES**

| 1.1        | Three nested loops in library characterization.                                             | 2      |

|------------|---------------------------------------------------------------------------------------------|--------|

| 2.1<br>2.2 | Concept of IC manufacturing test                                                            | 5<br>6 |

| 2.3        | Circuit to illustrate concept of fault sites.                                               | 7      |

| 2.4        | Illustration of unknown and high-impedance states.                                          | 8      |

| 2.5        | Fault sensitization and propagation.                                                        | 9      |

| 2.6        | Standard-cell based design flow.                                                            | 10     |

| 2.7        | 2-input AND cell from GPDK045 library.                                                      | 11     |

| 2.8        | Quantus parasitic extraction flow.                                                          | 13     |

| 3.1        | Cell-aware test flow.                                                                       | 16     |

| 3.2        | Defect Detection Matrix (DDM).                                                              |        |

| 3.3        | Cell-Aware Automatic Test Pattern Generation.                                               |        |

| 3.4        | ATPG for stuck-at fault model.                                                              | 18     |

| 3.5        | ATPG for cell-aware defect model.                                                           | 18     |

| 4.1        | Cadence cell-aware (a) library characterization (b) ATPG.                                   | 21     |

| 4.2        | Open defect insertion and concept of potential defects.                                     | 22     |

| 4.3        | Short defect insertion and concept of potential defects.                                    | 22     |

| 4.4        | An example of a faults list file.                                                           | <br>24 |

| 4.5        | Example defect detection file for 2-input AND cell.                                         | 24     |

| 4.6        | Original parasitic extracted Spectre netlist.                                               | 26     |

| 4.7        | Additional steps required for generating Spectre netlists.                                  |        |

| 4.8        | (a) Software bug causing reversal of transistor source-drain terminals (b) fix added        |        |

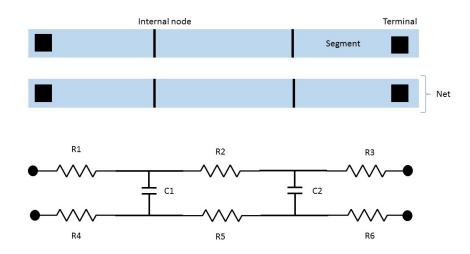

| 5.1        | Terminals, segments, nets and nodes.                                                        | 33     |

| 5.2        | Quantus parasitics-extracted cell model.                                                    | 34     |

| 5.3        | AND2X1 layout to illustrate heuristics for choosing $C_{th}$                                | 34     |

| 5.4        | Opens (a) based on potential defects (b) without potential defects                          | 35     |

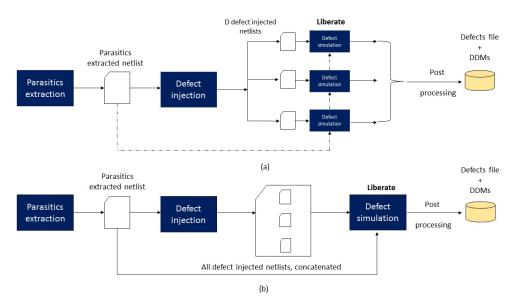

| 5.5        | Defect simulation (a) using $D + 1$ netlists vs. (b) combining all defect injected netlists | 37     |

| 5.6        | Shorts between nodes of a net-pair are equivalent                                           | 38     |

| 5.7        | Algorithm for inserting a single short between two net pairs.                               | 38     |

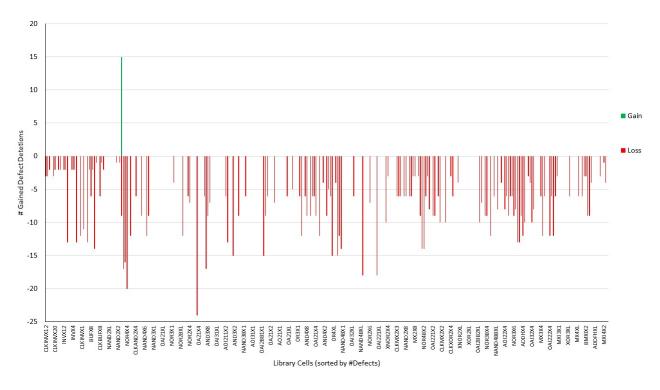

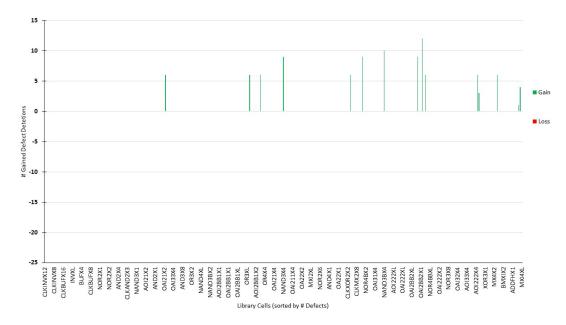

| 6.1        | Defect detections gained or lost per-cell after eliminating potential defects               | 42     |

|            | Defect detections with potential defects and without potential defects                      | 42     |

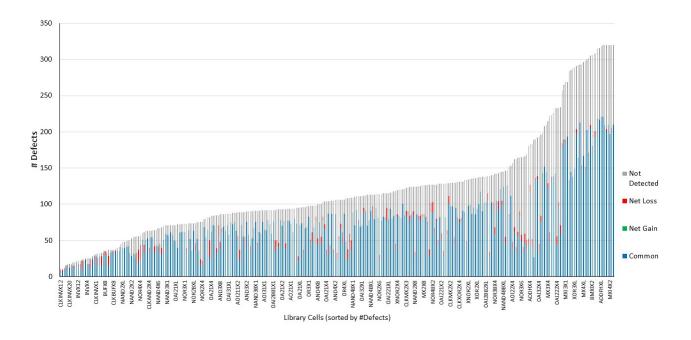

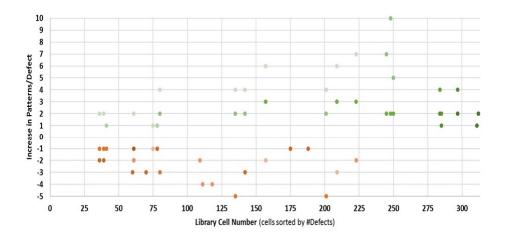

|            | Defect detections gained or lost per-cell after inserting super-hard defects                | 43     |

| 6.4        | Increase or decrease in number of test patterns upon inserting super-hard defects           | 43     |

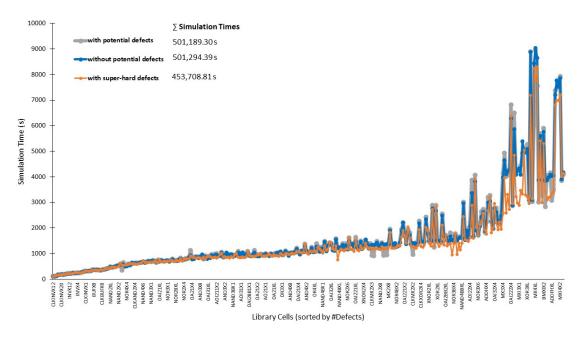

| 6.5        | Comparison of simulation times.                                                             | 44     |

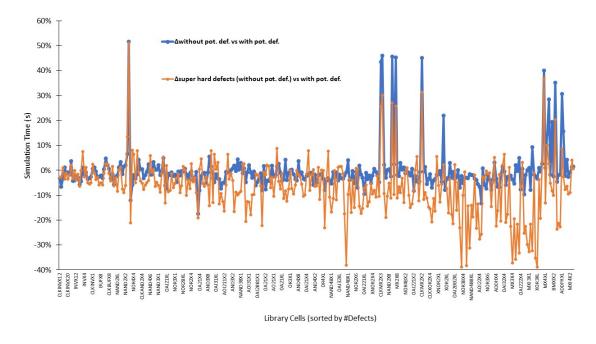

| 6.6        | $\Delta$ simulation times                                                                   | 44     |

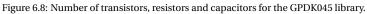

| 6.7        | Inserting a single short defect per net-pair for all cells.                                 | 45     |

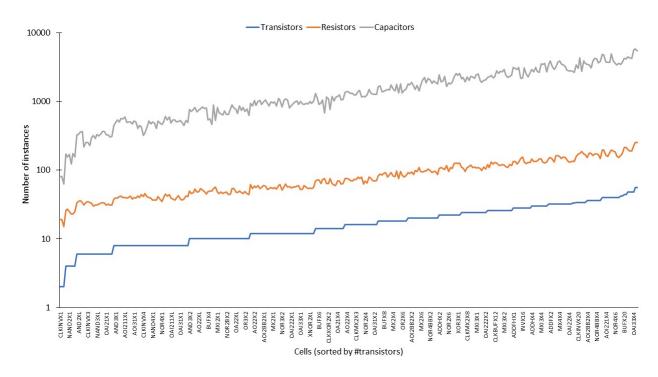

| 6.8        |                                                                                             | 46     |

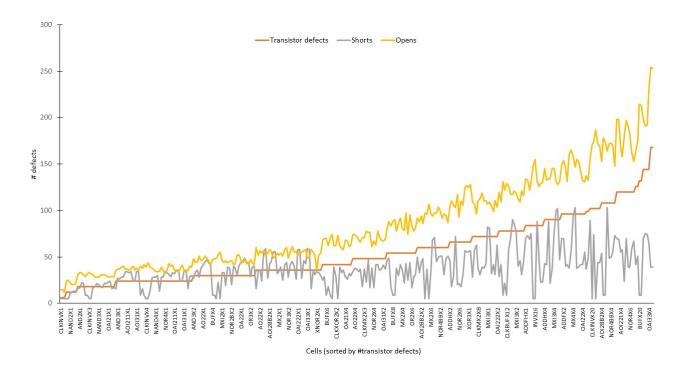

| 6.9        | Number of transistor, open and short defects.                                               | 47     |

| 7.1        | Improved flow for cell-aware library characterization                                       | 50     |

# LIST OF TABLES

| 2.1 | Logic operations on 0,1, and X.                                               | 8  |

|-----|-------------------------------------------------------------------------------|----|

| 4.1 | Various EDA tools being used in library characterization flow.                | 25 |

| 5.1 | Speedup - defective netlists combined as sub-circuits within a large netlist. | 37 |

| 6.1 | Number of transistors, resistors and capacitors extracted for few cells       | 46 |

| B.1 | The cell-aware flow RAK directory structure.                                  | 57 |

## LIST OF ACRONYMS

ATPG Automatic Test Pattern Generation

CAT Cell-Aware Test

CA-ATPG Cell-Aware Automatic Test Pattern Generation

CA-LC Cell-Aware Library Characterization

CUT Circuit Under Test

DfT Design for Test

DDM Defect Detection Matrix

EDA Electronic Design Automation

IC Integrated Circuits

PEX Parasitics Extraction

PVS Physical Verification System

QRC Quantus RC extraction tool

RAK Rapid Adoption Kit

## ACKNOWLEDGEMENTS

This thesis is a result of the support and the guidance I received from several people, and I am forever indebted to them. I consider myself to be fortunate to be associated with such individuals and organizations. Foremost, I would like to express my sincere gratitude's to my thesis advisor Prof. Said Hamdioui, who initiated me into the world of VLSI Testing and DfT with his inspiring lectures and magnetic personality. Without him, I don't think I would have ventured into this discipline or thought of making a career as a DfT engineer. If Prof. Hamdioui showed me the way my daily supervisor at IMEC, Erik Jan Marinissen taught me how to walk on this path. Erik Jan refined my style of working, corrected me when I was wrong, and showed me the importance of writing correctly and making effective technical presentations. The lessons I learned from him during this short tenure at IMEC will go a long way in shaping my professional career. My sincere thanks to my colleague Zhan Gao, for her untiring support and interesting discussions. I am sure, Zhan will make a good researcher and I wish her the very best in her future endeavors.

Next I would like to extend my acknowledgements to Kristof Croes who not only funded my project but taught me that respect has to be earned, and it takes time and effort to reach great heights. Prof. Ingrid De Wolf from KU Leuven, was an able mentor during this journey. Without the cooperation of IT support staff at IMEC, especially my Linux Guy - Ibrahim Tatar my software would never have worked. Thank you Linda Vanmeerbeek, for providing a nice office working space and the colourful marker pens!

Joe Swenton, Principal Software Architect, and Carl Wisnesky, Product Manager, from the Test Solutions Group at Cadence were my software gurus. This was my first real world software development experience both Joe and Carl took keen interest in me, and mentored me. Anton Klotz, University Program Manager at Cadence EMEA sent me a powerful laptop to work on, took care of all the administrative formalities and was kind enough to extend his professional network for my advantage. A special mention of Michel Montanuy - Staff Application Engineer from Cadence France, who taught me two industry leading software tools - Quantus QRC and PVS. As an organization, Cadence was instrumental in providing me with all the tools necessary to find the answers I needed during the course of this project. Not to forget, Vivek Chickermane and Louis Milano at Cadence, for offering me a suitable position to continue my journey with Cadence after my graduation!

The Delft University of Technology, and the people there especially my master coordinator, Prof. Arjan van Genderen, CE group secretaries, Joyce van Velzen and Lidwina Tromp. Prof. Rene van Leuken for consenting to being a part of my thesis exam committee. My fellow batch-mates from TU Delft Aritra Sarkar, Prashanth G L, Sarthak Sharma, Manoj Payani, Srinidhi Ramdas, and Sunil Suresh, many cheers to our friendship! The international student community at the Wisteria Student Residence in Leuven, for all the fun during the thesis period.

None of this would ever have been possible if not for my family, my father for believing in me and giving away his life's fortune for my education, my mom for letting me go, and my sister for her sacrifices.

Santosh S Malagi Leuven, September 2018

# 1

## **INTRODUCTION**

As Integrated Circuits (ICs) become pervasive in all walks of life, it is necessary to ensure they meet high quality standards and are reliable. Section 1.1 begins by discussing the motivation behind IC manufacturing test and its importance in electronic product development life-cycle. This is followed by a discussion about the traditional approaches to manufacturing test pattern generation and their inability to model realistic defects based on actual physical layouts. Cell-Aware Test (CAT) is a next generation test pattern generation technique which can address these shortcomings. Section 1.2 provides an overview of the cell-aware test methodology and it's associated challenges. Section 1.3 highlights the major contributions of this thesis, followed by the organization of the rest of the report in Section 1.4.

## **1.1. MOTIVATION BEHIND IC MANUFACTURING TEST**

ICs are omnipresent today; not only in computers, consumer electronics, and smartphones, but increasingly also in the Internet of Things (IoT), automotive and healthcare. Due to their large number of high-precision, defect-prone manufacturing steps, ICs are susceptible to manufacturing defects and hence need to undergo electrical tests to weed out the defective parts and guarantee sufficient outgoing product quality to the customer. High product quality and reliability become an absolute necessity, especially for applications such as automotive and medical which cannot tolerate any defective chips. However, as every IC is individually tested (typically even twice - once at the wafer level and once more after packaging), the tests also need to be very efficient with respect to the execution time. If the cost of identifying a defective chip is \$1, it costs about \$10 to detect the same defective chip when mounted on a PCB. The penalty rises to \$100 when the chip becomes a part of a bigger electronic system. Therefore, the goal of IC testing is to weed out defective chips in the supply chain as early as possible. No amount of testing can guarantee a 100% defect free product, but what testing does for us is, it increases our confidence in the correct and reliable operation of the Circuit Under Test (CUT). In volume production only those chips which pass the test are shipped to the customer and the rest are discarded.

#### **1.2. CELL-AWARE TEST**

A key step in the test development for digital logic ICs is automatic test pattern generation (ATPG). ATPG determines the content of the IC test. The quality of the generated test patterns significantly affects the test effectiveness. For scan-testable digital logic, manufacturing test patterns can be automatically generated by ATPG software tools. Conventional ATPG tools operate under the assumption that defects can only occur at the periphery of standard-cell instances, I/O ports or between interconnect lines. Any defect occurring within a standard-cell is completely disregarded during test pattern generation. As semiconductor technology scales further and newer transistor architectures are introduced, it is expected that the percentage of defects which occur within the standard cells i.e cell-internal defects will increase considerably [1–3]. Therefore, test patterns must be capable of detecting such cell-internal defects. Cell-aware test is a next-generation test pattern generation methodology. Its novel feature is that it explicitly addresses cell-internal defects as opposed to relying on serendipitous defect coverage reported by traditional ATPG tools. Cell-aware test is expected to significantly improve the test quality, and hence reduce the test escape rate for a relatively small increase in test execution cost. Test generation in cell-aware test flow consists of two distinct stages:

- 1. *Cell-aware library characterization (CA-LC):* Library characterization begins with the extraction of transistorlevel netlists along with the parasitic resistors and capacitors from the standard-cell layouts. Parasitic resistors and capacitors form the basis for identifying possible locations for open and short defects. This is followed by detailed simulations to determine the cell-level test patterns which can detect such intra-cell defects. The results are finally encoded in the form of a defect detection matrix (DDM).

- 2. *Cell-aware automatic test pattern generation (CA-ATPG):* Based on the generated DDM's, cell-aware ATPG generates minimum chip level test pattern set, which can cover as many as possible cell-internal defects.

#### Challenges in Cell-Aware Test

As an industrial standard-cell technology library easily contains about 1,500 cells, library characterization is a challenging task. For every cell with *n*-inputs all possible defect locations within the cell must be identified and simulated with  $2^n$  input test patterns, resulting in a nested loop as illustrated in Figure 1.1. The characterization process therefore is both resource and compute time intensive. Fortunately, it has to be done once per every standard-cell library and the results of this step can be re-used multiple times for all designs based on the same technology library.

```

for all cells \epsilon listofCells do {

RC parasitics extraction;

defect candidate identification;

for all defect candidates d do {

for all input patterns p do {

if Simulation(c,p) \neq Simulation (c+d,p):

DDM_c(d,p) = "1" //defect is detected

else:

DDM_c(d,p) = 0 //defect is not detected

}

}

```

Figure 1.1: Three nested loops in library characterization.

The cell-aware test flow uses parasitic resistors and capacitors to model possible locations for open and short defects. If all extracted resistors and capacitors are modelled as defect candidates, then the target defect set becomes very large. The parasitic resistors and capacitors to be chosen for cell-aware defect modeling must be such that the defect locations are realistic. Too few implies the risk of missing defects, and too many means expensive simulations and execution time. Since cell-aware test is a non-standard application of parasitic extraction (PEX) tools, conventional approaches of using PEX tools may not be well-suited for cell-aware test. Therefore, an investigation is needed for defining the suitable settings to be used by a PEX tool for generating transistor-level netlists appropriate for cell-aware defect modelling.

#### **1.3.** CONTRIBUTION OF THE THESIS

The objective of this thesis is to improve the library characterization stage of the CAT flow based on Cadence EDA tools. It proposes several approaches to effectively and efficiently model realistic physical defects based on standard-cell layouts, while trying to minimize the time required for characterizing standard-cell libraries. The main contributions of this thesis are the following:

- Proposing a set of customized settings for the Quantus parasitics extraction tool. These settings are effective in generating transistor-level netlists which are well-suited for cell-aware defect modelling.

- A heuristics based approach for defining the threshold values for parasitic resistors and capacitors to decide whether they are to be considered as possible defect candidates.

- Eliminating potential defects, which were superfluous elements being introduced in the netlist as a part of the original flow. Due to this change, 1114 false detections were uncovered leading to an improvement in the quality of the defect simulation results for the 45nm library (GPDK045) from Cadence.

- Using super-hard defect resistance values for modelling opens and shorts resulted in an additional 99 defect detections. The simulation time required for characterizing the library cells dropped by 6%.

- Concatenating the defect-injected netlists into one large file and avoiding repeated execution of background software tasks results in a speedup of upto 12 times in simulation time.

- Modifying the short-defect insertion strategy to insert a single short between two net pairs. Consequently simulation of equivalent defects exhibiting the same defect behavior is avoided. This reduces the number of short defect candidates for the GPDK045 library by 97.7%. Once incorporated in the software flow, this change is expected to translate to a significant savings in simulation time.

## **1.4. THESIS ORGANIZATION**

The remainder of the thesis is organized as follows. Chapter 2 provides a background on the essentials of IC testing, standard-cell based design flow, operation of parasitic extraction tools and Quantus QRC based parasitics extraction flow. This sets the tone for rest of the thesis. Chapter 3 presents a detailed discussion on cell-aware test and it's two stages. Chapter 4 talks about the shortcomings in the existing Cadence cell-aware flow and how it affects the quality of defect simulation results. Chapter 5 suggests various modifications to address these issues. Chapter 6 talks about the expected improvements and experimental results obtained by applying these changes to the the existing Cadence cell-aware flow. Finally, Chapter 7 concludes the thesis.

# 2

## **BACKGROUND KNOWLEDGE**

This chapter equips the reader with the necessary background required to understand the rest of the thesis. Section 2.1 introduces the essentials of IC testing. Section 2.2 touches upon the various aspects of the standardcell based design flow, which has become the de-facto standard for digital ICs. Parasitics extraction generates a transistor-level netlist which is to used for cell-aware defect modelling. An overview of parasitic extraction is covered in Section 2.3, followed by the specific details of the Quantus QRC parasitics-extraction tool in Section 2.4.

### **2.1. INTRODUCTION TO IC TESTING**

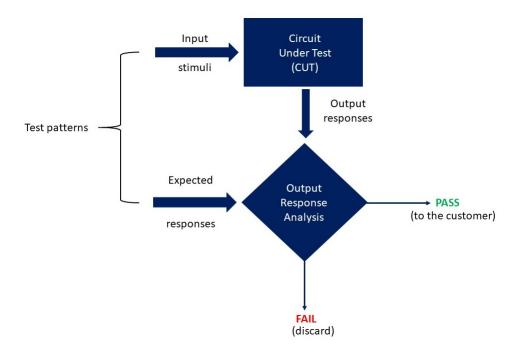

The last 40 years have been exciting times for the semiconductor industry, starting from a single transistor we have reached a stage where billions of transistors are packed in a tiny chip. This has been possible due to the steady decrease in the feature size of transistors and interconnect dimensions. Manufacturing chips at such a level of complexity involves hundreds of process steps, this increases the possibilities of a small error to result in a defective chip. The objective of IC testing is to separate the defective chips from good ones and ensure sufficient outgoing product quality to the customer. This basic philosophy behind IC manufacturing test is depicted in Figure 2.1.

Figure 2.1: Concept of IC manufacturing test.

Input stimuli are applied to the *circuit under test (CUT)* during manufacturing test. If the output response matches the expected response, the circuit (chip) passes the test and is considered to be *fault-free*. Those chips which do not produce the expected response are considered to be *faulty*, and discarded. A *defect* is defined as a physical imperfection or anomaly which results in a faulty behaviour. Some of the common examples of manufacturing defects include: resistive bridges and opens, partially filled vias, missing contacts, process variations, and impurity induced defects. Manufacturing tests can be executed based on two paradigms - functional testing and structural testing. In functional testing, an n-input circuit under test is subjected to all possible (2<sup>*n*</sup>) input combinations to verify it's functionality. Such an approach is not feasible because of the explosion in the number of test patterns required and prohibitive test application times. A more practical approach is *structural testing*. The structural testing approach does not attempt to verify the functionality of the circuit, rather it tries to ascertain whether the circuit has been assembled correctly using low-level building blocks and they have been connected as expected. The quality of the manufactured chips is measured in terms of the Defective parts per million (DPPM) i.e the number of defective chips per million manufactured chips. Certain applications such as automotive target zero DPPM. Manufacturing *yield* is defined as that percentage of chips which pass the manufacturing test and are acceptable, out of the total lot of manufactured chips. Yield-loss is that fraction of good chips which are erroneously flagged to be defective. Yield loss occurs because of over testing or badly designed test strategy. The defective chips which are passed to the customer as good ones are known as test-escapes.

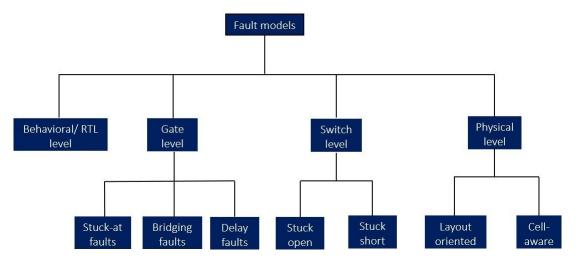

#### 2.1.1. FAULT MODELLING

Due to the infinite possibilities in which manufacturing defects can manifest themselves, it is highly impossible to test for each one of them individually. Rather we abstract the defects in terms of their faulty behaviour and generate test patterns to detect them. A *fault model* can be defined as a behavioural representation of the actual physical defect. A variety of fault models, each targeting a particular class of defects have been proposed. A good fault model must not only mimic the behaviour of the actual physical defect, but must be computationally efficient and lend itself for test pattern generation. In most cases a single fault model may not be sufficient to meet the targeted test quality. Therefore, a combination of two or more fault models are often used for generating tests. Figure 2.2 depicts some examples of fault models defined at various levels of abstraction.

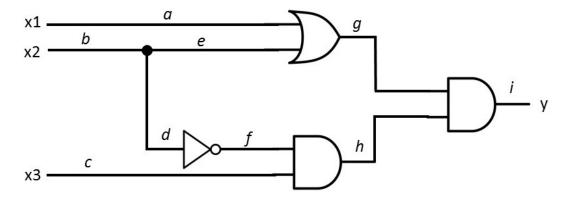

Figure 2.2: Examples of fault models at various levels of abstraction.

Most ATPG tools are based on the use of gate-level fault models such as stuck-at, bridging, and delay faults for generating test patterns. A stuck-at fault model operates on the principle that any interconnect line, *primary input* or *primary output* could be permanently set to a logic-1 value (*stuck-at 1*) or a logic-0 (*stuck-at 0*). In Figure 2.3 there are nine possible fault sites and each fault site could be stuck-at 0 or stuck-at 1. For single stuck-at fault model based test generation, if two or more faults exhibit the same fault behaviour they are said to be *equivalent*. Rather than testing for all faults in the equivalent set, it suffices to test for only one fault and all other cases are automatically covered. In the above example, for a two-input AND gate a stuck-at 0 fault at the input is same as a stuck-at 0 fault at the output. Similarly, for a two-input OR gate a stuck-at 1 fault at the

output is equivalent to stuck-at 1 fault at one of the input lines. The process of substituting several faults with one equivalent fault is known as *fault collapsing*. Fault collapsing helps reduce the length of the test pattern set and time required for fault simulation. *Fault coverage* is a measure of test effectiveness, and is defined as the percentage of faults which are detected by applying test patterns. A bridging fault is used to model the case of two signal nets being shorted with each other. A delay fault models a defect which does not change the value of signal, but causes a circuit to produce the correct output at slower clock speeds. A high-to-low or a low-to-high transition is required to activate the fault effect and hence a pair of test vectors are necessary to detect delay faults.

Figure 2.3: Circuit to illustrate concept of fault sites.

A switch level fault model targets transistor faults wherein a transistor could be permanently turned ON - stuck-short (stuck-ON), or turned OFF - stuck-open (stuck-OFF). For detecting stuck-open faults a pair of test vectors are necessary, whereas to detect stuck-short faults the power supply current at steady state is monitored using  $I_{ddq}$  testing. Gate-level fault models lie at the intersection of logic and physical implementation and they have been widely used for generating manufacturing test patterns. Unfortunately, such fault models may not be sufficient to address the testing challenges posed by today's state of the art deep sub-micron technologies [1, 4]. Generating test patterns by considering the actual physical layouts to target realistic defects is becoming increasingly important. One such example is the cell-aware model which forms the basis of this thesis work.

#### 2.1.2. FAULT SIMULATION

A circuit simulation is used to predict the behaviour of a circuit. A distinction between functional simulation and fault simulation is necessary at this point. In functional simulation the main intent is design verification. Functional simulation identifies design errors by comparing the circuit responses with specifications or requirements of the design. Functional simulation can take place at various levels of abstraction. For example, a simulation to verify behaviour of the gate-level netlists is often known as logic simulation. At the switch level, analog simulations on SPICE netlists can be carried out to verify the values of functional parameters of the circuit such as output voltage and currents. Carrying out detailed analog simulations of the circuit is usually time consuming, gate-level or logic simulations are much faster. Fault simulation on the other hand characterizes the circuit behaviour in the presence of faulty circuit elements. The goal is to identify a set of test vectors which can detect these faults. It helps estimate the quality of the test pattern set in terms of the targeted fault coverage. Fault simulation results also play a major role in fault diagnosis. Before discussing fault simulation techniques, it is necessary to develop an appreciation of the various logic symbols used in fault simulation. Most fault simulation methods are derivatives of logic simulation techniques and hence use a similar etymology.

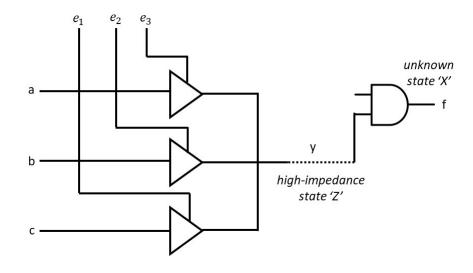

#### Logic Symbols - 0, 1, X, and Z

Boolean algebra uses two logic symbols - 0 and 1 to represent false and true values respectively. In CMOS technology a 0 corresponds to voltage level  $V_{ss}$  and 1 represents the  $V_{dd}$  value. In addition two more logic symbols X (unknown state) and Z (high-impedance) are used. The symbol X is used to represent unknown logic values on a signal net, when it is not clear whether the value is a logic 0 or logic 1. The outcomes of

performing fundamental boolean operations on 0,1 and *X* are depicted in Table 2.1. It can be seen that during a logical AND operation, 0 is the dominant value, whereas 1 is dominant during a logical OR.

| NOT | 0 | 1 | X | OR | 0 | 1 | x | AND | 0 | 1 | x |

|-----|---|---|---|----|---|---|---|-----|---|---|---|

|     | 1 | 0 | х | 0  | 0 | 1 | х | 0   | 0 | 0 | 0 |

|     |   |   |   | 1  | 1 | 1 | 1 | 1   | 0 | 1 | X |

|     |   |   |   | х  | х | 1 | х | x   | 0 | x | X |

Table 2.1: Logic operations on 0,1, and X.

The logic symbol Z means a high-impedance state, it represents a node which is floating i.e. it is neither being driven by a logic 1 nor logic 0 value. Consider the example circuit shown in Figure 2.4. If because of a certain fault, all the drivers are disconnected from the node y, it is said to be in the high-impedance or Zstate. Since the internal node y is in high impedance state, the final output f is unknown, it can either take a logic-1 or logic-0 value and is represented using an X symbol.

Figure 2.4: Illustration of unknown and high-impedance states.

Various techniques to improve the performance of fault simulation have been proposed in literature [1, 5], and are widely used in practice. The simplest of all the fault simulation techniques is serial fault simulation. A target set of faults is identified and faulty circuit elements are injected in the fault-free circuit netlist. Each of these fault-injected netlists are subject to fault simulation by applying input test vectors. The responses of the fault injected netlists are compared with the expected responses, in case of a mismatch the fault is considered detected. Serial fault simulation is very intuitive and simple to implement. A major drawback however is its slow speed. Parallel fault simulation exploits the bit wise parallelism in boolean operations to reduce the simulation time. Faulty circuits can be simulated in parallel and their responses are compared with that of the fault free circuit. Concurrent fault simulation or event driven simulation only simulates that region of the circuit which is in the immediate vicinity of the fault, thereby reducing the fault simulation time, available compute resources, ability to handle unknown or high-impedance states and the structure of the circuit netlist itself [1].

#### 2.1.3. AUTOMATIC TEST PATTERN GENERATION

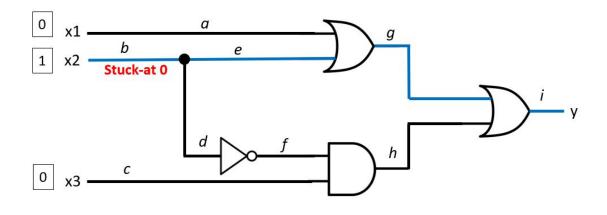

Given a set of faults F and a set of test patterns T, the objective of ATPG is to determine an optimum subset of test patterns V which can either detect all faults in F, or pre-determined fraction of the faults (i.e. targeted fault coverage). ATPG is a well-known NP-complete problem [6]. ATPG is regarded as a huge binary decision tree, which could have an exponential search space with single, many or no solutions at all [1, 6]. The usual approach to test pattern generation is to first start by generating random test patterns and then apply deterministic test patterns to improve the fault coverage. Many easy to detect faults can be detected using random test pattern generation. After subsequent iterations when fault coverage using random test pattern generation finally saturates, test patterns are generated using deterministic algorithms such as D [7, 8], PO-DEM [9] and FAN [10]. ATPG algorithms operate on the principles of sensitizing (activating) the fault effect, propagating the fault effect to the primary outputs, and finally justifying all input signals by setting them to non-controlling states so that they do not change the faulty logic values. Fault activation sets the signal driving the fault site to a logic value which is opposite to that of the faulty value. For example, to test for a stuck-at 1 fault, the fault site is set to a logic-0 value to activate the fault. Fault propagation selects a path from the fault site to the primary output, where the fault effect can be observed. Fault justification sets the internal nets or primary inputs to non-controlling values so that they do not negate the fault effect. Conflicts are possible between the propagation and justification tasks, in such a scenario a new alternative path must be selected. Consider a simple logic circuit illustrated in Figure 2.5 which has a stuck-at 0 fault at b. Let e-g-i be the chosen path for propagating the fault effect to the output *i*. To sensitize the fault effect, *b* is set to logic-1. *a and c* must be justified by setting them to non-controlling values of 0. After completion of the activate, propagate and justify tasks the test pattern becomes x1 = 0, x2 = 1, and x3 = 0.

Figure 2.5: Fault sensitization and propagation.

#### **2.2. STANDARD-CELL BASED DESIGN FLOW**

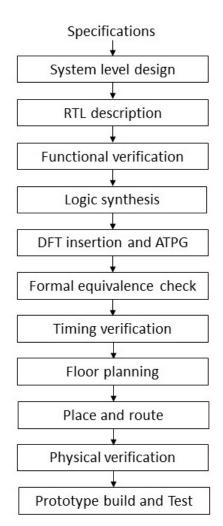

A design flow can be defined as set of well-defined steps which allows a chip design team to realize a successful implementation of chip starting from it's specifications. The standard-cell based design flow is widely used for designing Application Specific Integrated Circuits (ASIC's) with substantial digital and memory content. A standard-cell is a complete logical and physical implementation of most commonly used logic or storage function such as AND, OR, NOT gates, multiplexers, adders, flip-flop, register etc. These functions are verified, designed and laid out in a particular technology node and the logical, timing, physical, and electrical models are made available. A collection of such standard-cells in a particular technology node is called as a standard-cell library. A highly simplified version of standard-cell based design flow is illustrated in Figure 2.6. In practice the design flow is not very straight forward and consists of several design iterations and back-tracking steps to resolve design errors. The design flow starts with the system-level design. The detailed behavioural specifications of the chip are captured using a high-level modelling language such as SystemC. RTL designers then use hardware description languages such as VHDL or Verilog to achieve the desired functionality in terms of memory elements (registers) and logical/arithmetic operations performed on them. Functional verification confirms that the developed RTL code matches the design specifications. During the logic synthesis phase, the RTL description is transformed to a technology dependent gate-level netlist. This is done by mapping the logic functions to their respective standard-cell instances in the chosen technology library. This marks the end of front-end design or logic design phase. Additional logic is inserted to improve the testability of design. DFT features make it easy to develop and apply test patterns to detect any defects

during manufacturing. Manufacturing test patterns are generated using ATPG tools.

Figure 2.6: Standard-cell based design flow.

The gate-level netlist from the logic synthesis step is modified during DFT insertion. To verify that such a netlist does not violate the initial specifications a formal equivalence check is necessary. The goal of functional verification is to check for functional correctness, where as formal verification checks whether two gate-level implementations of the circuit represent the same boolean equations or not. During pre-layout Static Timing Analysis (STA), the design is checked for setup and hold violations before being handed over to physical design implementation. The idea is to check whether the design can operate at the designated clock frequency. The floor planning stage decides the I/O structure of the chip, placement of standard cell instances and macro blocks, and the design of power-ground networks. The actual placement of standardcell instances and other blocks happens during placement. For digital designs this step is largely automated and determines the quality of routing. This is a key step in the physical design implementation phase as placement of blocks directly impacts the quality of routing. The clock network is designed during the clocktree insertion phase. This is followed by routing of signal nets. Global routing determines the 2D map of how standard-cell instances must be interconnected. Detailed routing stage determines the exact interconnection path through different metal layers and vias. The physical verification phase consists of many steps. Design Rule Check (DRC) ensures that the layout does not violate any design rules set by the fabrication house and hence can be manufactured. Layout vs Schematic (LVS) ensures that post layout the structure of the chip has not been modified and matches the circuit schematic. This is followed by circuit extraction step which extracts the designed and parasitic devices (RLC) from the layout. The design is then verified in the presence of actual parasitic elements and wire delays for timing correctness during post-layout STA. Once the back-end flow is complete, the GDSII output is generated and sent for fabrication. An initial batch of chips is subjected to post-silicon validation to ensure all the specifications are satisfied. Any anomaly detected in this stage may lead to back-tracking and corrections in the earlier steps. A chip design project reaches a logical conclusion when the design is cleared for volume production. Every chip is then subjected to manufacturing test by applying test patterns. Only those chips which qualify the tests are shipped to the customer and the rest are discarded.

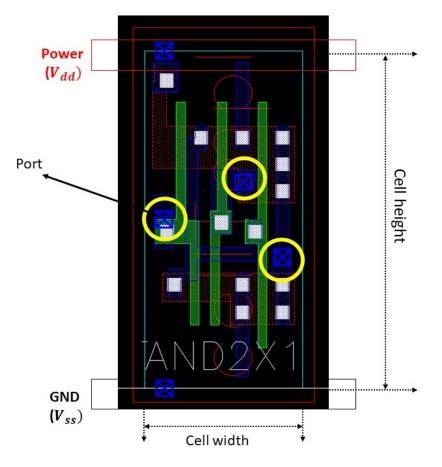

Figure 2.7: 2-input AND cell from GPDK045 library.

The biggest advantage of standard-cell based design flow is that it enables design re-use and shortens the time to market. It makes it possible to massively scale the design while most of the synthesis and implementation details are taken care of by state of the art EDA tools. This also reduces human effort and possibility of errors during the design cycle. The present work is based on the generic 45nm standard-cell library from Cadence (GPDK045). Figure 2.7 illustrates a 2-input AND cell from the the GPDK045 standard-cell library. The height of the standard-cells in a library is maintained as a constant, this makes it possible to align the standard cells in a single row. The width of a cell varies depending on the complexity of the cell, number of transistors, and their drive strength.

#### **2.3. PARASITICS EXTRACTION**

Parasitics extraction generates a transistor-level netlist which is to used for cell-aware defect modelling. This section provides a brief overview of the operation of parasitics extraction tools. The process of converting the layout view of a design to a transistor-level netlist is known as layout extraction. It serves various purposes - estimating the timing behaviour, noise characterization, power analysis, layout vs schematic comparison, and identifying parasitic elements. Extracting a transistor-level netlist for identifying parasitic elements is known as *parasitic-extraction*. The generated circuit level netlist contains two types of devices - designed devices and parasitic devices. Designed devices are created by the designer, parasitic devices (R),

capacitors (C), and inductors(L)) are a result of material properties. They were not explicitly designed but they exist in the fabricated hardware. As circuits become more complex and interconnect structures shrink further, the effect of parasitic devices on circuit performance becomes an important concern [4]. Most parasitics-extraction tools started out as derivatives of Design Rule Check (DRC) programs, later branching out to evolve as specialized tools [4]. A generic parasitics-extraction flow involves the extraction of designed devices, inter-connect and parasitic device extraction (R, L and C), and network simplification tasks as explained in [4]. The behaviour of the extraction tool is customized by the user. These settings not only determine the quality of extraction, but also the suitability of the extracted circuit netlist for the target application.

- 1. *Determine the nature of extraction:* Identify the target design analog, digital, mixed signal, Radio Frequency (RF) etc. Zero in on the accepted input database and required output format of the netlist to be generated. Interoperability of EDA tools might also be worth a consideration. Finally, decide whether the extraction would be flat, cell-level or hierarchical in nature. In the flat extraction technique entire design is simplified to a single level of hierarchy. A cell-level extraction system performs parasitic extraction on each individual cell, while only considering the the inter-cell relationships for connectivity. A truly hierarchical system also allows for extracting inter-cell parasitic device. Because of the high sophistication involved in a truly hierarchical system most layout extraction happens at the flat or cell level.

- 2. Correlate designed layout dimensions with actual silicon geometries: A circuit designer builds an ideal view of the different layers of a circuit in terms of polygons which appear as perfect shapes in the software model. The practical limitations posed by lithography and chemical mechanical polishing processes (CMP) result in differences between the layout in a CAD tool vs what is actually achieved. For accurate parasitic estimation an extraction tool must account for these differences. The shape and size of the drawn geometries might be different from what is actually patterned on a silicon substrate. Also the designer has not specified the thickness of the different layers. Empirically these details can be determined by using the available information such as width, spacing between neighbours, density, material properties etc. All of these dimensions are specified in a technology file and provided as input to the extraction tool.

- 3. *Extraction of designed devices:* The designed device extraction identifies the location of devices such as MOS transistors which have been explicitly designed in the circuit. For example in a typical CMOS design flow a transistor is defined whenever a poly overlaps a diffusion region. A poly-silicon area forms the gate, whereas the drain and source terminals are located in the diffusion regions. An additional step might involve measuring the device parameters such as gate length or width. At this stage the tool might also validate whether the device has been correctly identified or not. For example, a transistor with three source-drain terminals is invalid unless the process architecture allows for such a configuration. The extraction tool recognizes such instances, assigns a unique identifier to each device, makes a note of the terminal connections, device location and parameters and stores this information in a database.

- 4. *Interconnect or connectivity extraction:* The first step in interconnect extraction is to remove the designed devices, then construct monolithic net structures integrating vias and connections on different layers. Using the information generated in earlier step the device terminals must be located. This helps in assigning unique labels to nets and later to net segments after the parasitic resistance extraction step is complete.

- 5. *Parasitic device extraction:* After connectivity extraction is complete, each net is broken down into simpler, smaller parts known as segments and the resistance of each sub-part is estimated. The resistance value is estimated using the dimensions(shape), it's nature such as being a linear resistor, contact resistor, bend, junction etc. and a resistance coefficient value defined in the process technology files. Some of the challenges in parasitic R extraction include treatment of copper interconnects which are not homogeneous, accurate estimation of contact resistors and handling of resistive via-arrays. Specialized techniques have been developed to address these issues and most industrial grade parasitic extraction tool provides options to handle such situations. Capacitance extraction uses the area and the perimeter information of the interconnects and routing layers to obtain the capacitance values. In 2D capacitance extraction the lateral or surface capacitance of different layers is also taken into account. In 2.5D extraction two 2D structures are combined to improve the accuracy of parasitic extraction. A 3D

capacitance extractor provides the highest level of sophistication and accuracy. It operates by breaking the cross section into thousands of smaller units and simulating them with field solvers. The generated data is co-related to fit an empirical formula and then estimate the C value between any two segments. Inductance extraction is performed only when required. Since detailed discussion of algorithms involved in parasitic extraction is out of the scope of this thesis, the reader is advised to consult other sources such as [3, 4] for a comprehensive treatment of parasitic extraction techniques.

6. *Circuit reduction:* Parasitic extraction can generate a large number of resistors and capacitors. In most use case scenarios all the extracted R and C elements, internal nodes and net segments might not be required. A simplified version of the netlist obtained by replacing the original R and C elements with the lumped or equivalent values is sufficient. It not only reduces the size of the netlist, but also optimizes the computation requirements of the EDA tools which might operate on these generated netlists.

## 2.4. QUANTUS QRC BASED PARASITIC EXTRACTION FLOW

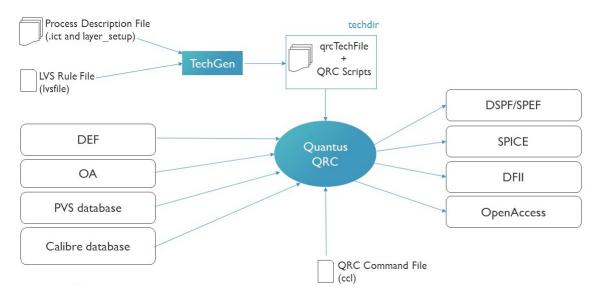

Quantus is a parasitics extraction tool offering from Cadence. It supports R,L and C extraction from both celllevel and transistor level designs and is suitable for analog, digital and mixed-signal circuits. Quantus can perform parasitic extraction from multiple process technology nodes, and has built-in support for 3D capacitance extraction using field-solvers. Figure 2.8 illustrates the parasitic extraction flow using Quantus. Quantus can accept various input formats such as DEF, OA (Open Access Database), PVS database (PVS- Physical Verification System) or Calibre (physical verification tool from Mentor Graphics) as inputs. In the Cadence cell-ware flow, PVS database is used as input to generate parasitic extracted netlists in the SPICE format. PVS is a suite of physical verification tools from Cadence which can perform DRC (Design Rule Check), IVL (Layout vs Layout), ERC (Electrical Rule Check), LVS (Layout vs Schematic) and SVS (Schematic vs Schematic). Prior to performing parasitics extraction using Quantus, PVS must be invoked to perform LVS. Firstly, the design flow requires checking the reliability of the layout database. Secondly, PVS generates several input files which are used during RC extraction. For example, Quantus requires information regarding port names, layers, connectivity and device information which is generated by PVS.

Figure 2.8: Quantus parasitic extraction flow.

Quantus accepts the files produced during PVS to perform RC extraction. The settings for extraction process are specified by the user in the form of an ASCI file known as QRC Command File (.ccl file). The CAD engineer invokes a command line utility known as TechGen to generate the start-up scripts and files containing information about resistance (layer + via) and capacitance (interconnect) models to be used for RC extraction. This is used as an input during the extraction process. Finally, Quantus generates a parasitics-extracted SPICE netlist.

#### 2.5. SUMMARY

This chapter provides an overview of IC testing and it's various building blocks - fault modelling, fault simulation and ATPG. Fault modelling abstracts the actual physical defects in terms of their logical behaviour and therefore enables test pattern generation using ATPG. Fault simulation identifies which test patterns detect which faults. ATPG uses this information to generate test patterns for the entire design. Standard-cell based design flow is most widely used ASIC design methodology. Parasitics extraction generates an accurate simulation model of the circuit by extracting both designed devices and parasitic elements from physical layouts. Quantus QRC is one such parasitic extraction tool which is used in the context of this thesis for generating transistor-level netlists.

# 3

## **CELL-AWARE TEST**

Related prior work leading to the evolution of cell-aware test is discussed in Section 3.1. Library characterization and cell-aware ATPG, the two stages of cell-aware test are discussed in Section 3.2 and Section 3.3 respectively. Cell-aware test has been successfully applied for testing complex circuit designs ranging from automotive chips to 32-bit microprocessor designs. Some of these example use cases are reviewed in Section 3.4.

## **3.1.** THE EVOLUTION OF CELL-AWARE TEST

Manufacturing tests have largely relied on the use of gate-level fault models such as stuck-at, delay, and bridging fault models [1]. Most of them operate under the assumption that a defect can only take place on the interconnects or I/O ports of gate-level instances [11]. Though this assumption has worked quite well in the past, with the advent of deep sub-micron technologies this is no longer the case [1]. Numerous approaches have been suggested to improve the defect detection capabilities of ATPG-based logic tests. In *n-detect* testing [12, 13] a given stuck-at fault is targeted multiple times by applying *n* different test patterns. New (different) test patterns are generated in the hope that these patterns will improve the defect coverage. This leads to a corresponding increase in the test pattern set making it expensive to apply on large designs. Embedded Multidetect [14] tries a different approach by making use of don't-care bits to detect stuck-at faults. Though, this does not lead to expensive test pattern count increase it prohibits the use of don't care bits for compression and low power testing [15]. The effectiveness of *n*-detect and EMD approaches depends on the characteristics of the original test pattern set, which makes the improvement in test quality largely probabilistic [11]. In gate-exhaustive testing [16], all possible input test patterns are applied at the library cell-level to guarantee full coverage of all cell-internal defects. For large complex designs having millions of gates, often with multiple inputs this might lead to an explosion of test patterns. Use of SPICE netlists and analog simulations to target transistor level defects, albeit without parasitic elements was proposed in [17]. The cell-aware test methodology evolved as an extension of these ideas and was first introduced in [11]. The objective of cellaware test is to explicitly target cell-internal defects and improve the defect coverage rather than relying on serendipitous coverage of defects as reported by conventional ATPG [11, 18, 19]. This is achieved by modelling realistic physical defects based on actual standard-cell layouts, and simulating them with an exhaustive set of  $2^n$  inputs (where n is the number of cell-inputs). Cell-aware test methodology consists of two stages - library characterization and cell-aware ATPG as illustrated in Figure 3.1. During the library characterization stage the cell-level test patterns which can detect the cell-internal defects are determined. The results are then used during the subsequent cell-aware ATPG stage to generate compact set of test patterns at the chip level. Cell-aware test is expected to provide gate exhaustive test quality at a small increase in test cost. Prior research has already proven the usefulness of cell-aware test over n-detect [20], EMD [21], and gate-exhaustive [22] based approaches. The subsequent sections discuss the library characterization and cell-aware ATPG in greater details.

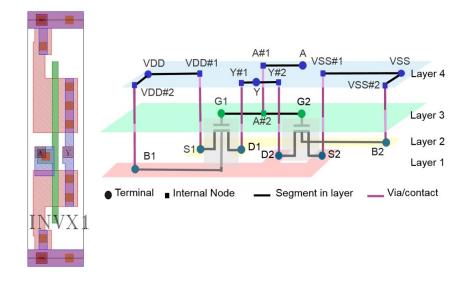

## **3.2. LIBRARY CHARACTERIZATION**

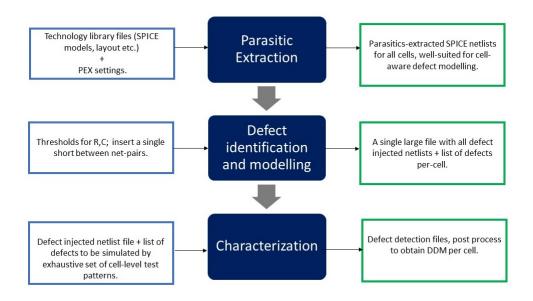

Library characterization stage consists of parasitic extraction, defect location identification, defect injection, and defect simulation as illustrated in Figure 3.1. It starts by extracting transistor-level netlists along with parasitic elements from the physical layouts of standard-cells. Parasitic resistors and capacitors form the

Figure 3.1: Cell-aware test flow.

basis for identifying possible open and short defect sites. A high parasitic resistance (R) is indicative of a long and thin wire and is therefore a potential candidate for an open defect. A large parasitic capacitance (C) between two nets implies they are very close to each other and run in parallel for long distances. This makes them highly susceptible to shorts during manufacturing. Parasitic Rs and Cs above a user defined threshold are considered as target defect candidates. To simulate the defect behaviour, a parasitic resistor is replaced with a hard-open (very high resistance), and a capacitor is replaced with a hard-short (very weak resistance in parallel with the capacitor). Choosing a large threshold value reduces the number of opens and shorts in the target defect set, but might lead to the skipping of some possible defect scenarios. On the other hand, a very low threshold could lead to the modelling of unrealistic defect free and |D| defect injected netlists for |D| defects ). Once the defect extraction process is completed, these netlists are subjected to detailed simulations by using an exhaustive set of  $2^n$  patterns, where *n* represents the number of cell-inputs. This defect characterization process must be repeated for every cell in the library, for all possible defect locations. If the output response is different from the defect free case, then the pattern is considered to detect the defect. The target defect set can be summarized as follows:

- *Candidate open defects:* (1) opens on long and thin wires (2) opens at the transistor source and drain terminals.

- *Candidate short defects:* (1) shorts between two wires which are very close to each other (2) short between transistor drain and source terminals.

| Sum | Pattern | d1 | d2 | d3 | d4 | d5 | d6 | d7 | d8 | d9 | d10 | d11 | d12 | d13 | d14 | d15 | d16 | d17 | d18 | d19 | d20 | d21 | d22 | d23 | d24 | d25 |

|-----|---------|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 9   | p0=00/L | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 1   | 1   | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 0   | 0   | 0   | 0   | 0   | 0   |

| 17  | p1=01/L | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 1   | 1   | 0   | 0   | 0   | 1   | 0   | 1   | 1   | 1   | 0   | 0   | 1   | 1   | 0   | 1   |

| 10  | p2=10/L | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 1   | 1   | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 0   | 1   | 0   | 0   | 0   | 0   |

| 10  | p3=11/H | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1   | 1   | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 0   | 0   | 0   | 0   | 0   | 1   |

|     | Sum     | 1  | 3  | 1  | 1  | 3  | 0  | 2  | 4  | 2  | 4   | 4   | 0   | 0   | 0   | 1   | 4   | 4   | 4   | 4   | 0   | 1   | 1   | 1   | 0   | 2   |

Figure 3.2: Defect Detection Matrix (DDM).

The results of this step are then encoded in the form of a Defect Detection Matrix (DDM) which is illustrated in Figure 3.2. A DDM records which cell-level test patterns can detect which cell-internal defect candidates. The number of rows in a DDM are equal to the number of patterns (i.e.  $2^n$  for *n*-input cell) and each column corresponds to a defect candidate. A 1 indicates that the particular defect d is detected by cell-level test pattern p, 0 means it is not detected. The sum of the rows of the matrix gives the total number of cell-internal defects which can be detected by a particular test pattern. The total number of simulations to be carried out for a cell i in the library is given by:

Number of simulations for the

$$i^{th}$$

cell =  $2^{n_i} \cdot d_i$  (3.1)

where  $n_i$  is the number of inputs for the  $i^{th}$  cell and  $d_i$  is the number of defects for cell *i*. If the entire standard-cell library has *c* cells, the total number of simulations to be performed are:

Total number of simulations for the entire library =

$$\sum_{i=1}^{c} 2^{n_i} \cdot d_i$$

(3.2)

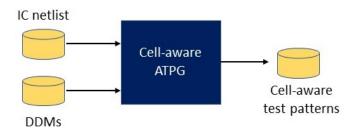

#### **3.3. CELL-AWARE ATPG**

The inputs to the cell-aware ATPG step are the DDMs for all the library cells and the circuit level netlist as illustrated in Figure 3.3. A DDM records which cell-level test patterns can detect which cell-internal defect candidates. This information is used by the cell-aware ATPG engine to identify a compact test pattern set at the circuit-level which can cover the maximum number of cell-internal defect candidates.

Figure 3.3: Cell-Aware Automatic Test Pattern Generation.

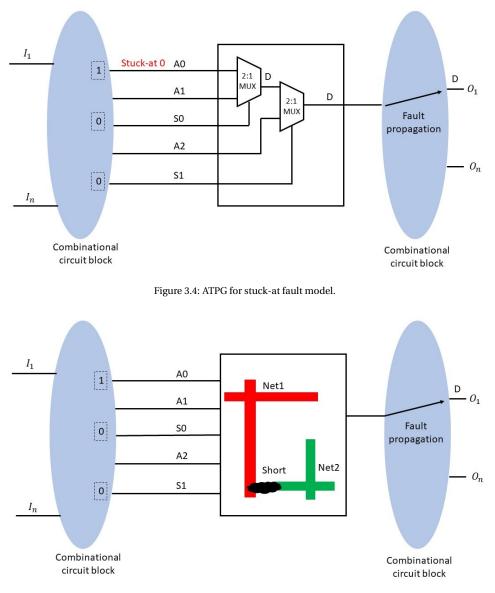

A conventional ATPG engine based on stuck-at faults modelling tries to detect a fault at the cell boundary, i.e. it has to perform a single justification and propagation activity. Cell-aware ATPG on the other hand may have to satisfy several justification targets for a single propagation task. This is best illustrated by an example. Consider a stuck-at 0 fault on the line A0 of the circuit shown in Figure 3.4. The fault effect is justified by making A0 = 1. S0 = 0 and S1 = 0. The other inputs A1 and A2 are don't care bits. The justification and propagation for an example cell-internal defect of the same circuit is shown in Figure 3.5. The required conditions in this case are A2 = 0, A0 = 1, S1 = 0 and S0 = 0. An additional bit A2 must be justified in order to propagate the fault effect. Consequently, compared to stuck-at faults based ATPG, CA-ATPG requires more logic signal values to be justified [19].

#### **3.4.** INDUSTRIAL APPLICATIONS OF CELL-AWARE TEST

The cell-aware test methodology has been applied in practice to several multi-million transistor designs laid out in 65, 55, 32 and 28 nm process technology nodes. The results of generating static and transition test patterns for 10 such industrial designs based on the CAT fault model have been reported in [19]. On an average each design had 2.9 million transistors, leading to about 20 million stuck-at faults and 60 million possible CAT defects. The number of potential defect candidates based on CAT model was always significantly higher than static stuck-at faults. The improvement in test quality is attributed to the ability of cell-aware fault model to explicitly target cell-internal defects which otherwise were not detected by conventional fault models. However, this comes at the cost of additional test-patterns. If the improvement in defect coverage is taken into consideration then this increase is marginal. For instance, with 25% increase in test pattern count, the defect coverage for most designs went up by 4%. Production test results of applying CAT to a 32nm notebook processor design from AMD (Advanced Micro Devices) have been presented in [23]. The library characterization

Figure 3.5: ATPG for cell-aware defect model.

was carried out on about 1900 cells. It is reported that an additional 699 failing parts were identified by applying cell-aware patterns which had escaped stuck-at and transition patterns. These statistics were further confirmed by applying system level tests to the failing chips. In [24] production test results of a 130 nm automotive chip from Infineon Technologies based on 216 standard-cell instances are presented. Even on mature technology nodes CAT has effectively improved test quality for mission critical electronic chips which target zero test escapes.

#### **3.5. SUMMARY**

Conventional ATPG tools have relied on serendipitous coverage of faults, which can no longer be the case with deep sub-micron technologies. Some of the notable approaches to improving the test quality and increasing the defect coverage include - *n-detect, Embedded Multi-Detect (EMD) and Gate-Exhaustive (GE) testing.* In most cases, either the test application is very expensive, making it highly impractical for actual designs or the improvement in test quality is probabilistic. The cell-aware test methodology has emerged as a promising alternative which uses the actual physical layout as blueprint to identify cell-internal defects. This is done in two stages - cell-aware library characterization and cell-aware ATPG. In cell-aware library characterization a standard-cell library is characterized to generate a set of cell-level test patterns which can detect the targeted

cell-internal defects. These are represented in the form of a Defect Detection Matrix (DDM). The cell-aware ATPG stage, uses the DDMs and the circuit netlist to generate a compact set of test patterns for the whole design. Cell-aware test is expected to significantly improve test quality and reduce test escapes at marginal increase in test generation cost. Cell-aware test has been used for the production testing of several multi-million transistor based designs such as microprocessors and automotive chips.

## 4

### **ORIGINAL CELL-AWARE FLOW BY CADENCE**

Section 4.1 presents an overview of the Cadence cell-aware test flow and it's two stages. Section 4.2 discusses the various shortcomings identified in the library characterization stage and how it affects the overall test quality.

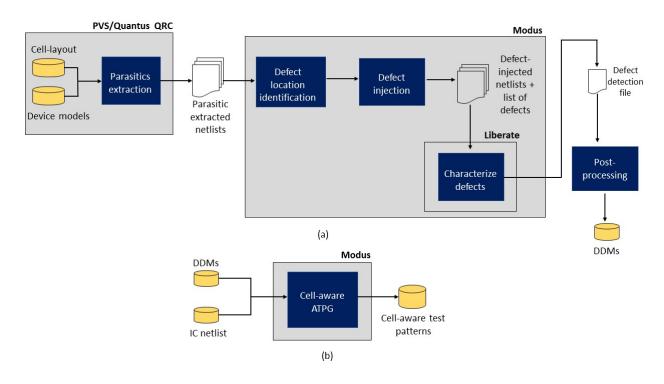

#### 4.1. OVERVIEW OF CADENCE CELL-AWARE TEST FLOW

The Cadence cell-aware test flow is illustrated in Figure 4.1 and is executed in two stages. During the first stage of the cell-aware test flow i.e. the library characterization stage, the cell-level test patterns which can detect the cell-internal defects are determined. The results are stored in the form of a Defect Detection Matrix (DDM), which are then used during the subsequent cell-aware automatic test pattern generation stage to generate a chip level test pattern set.

Figure 4.1: Cadence cell-aware (a) library characterization (b) ATPG.

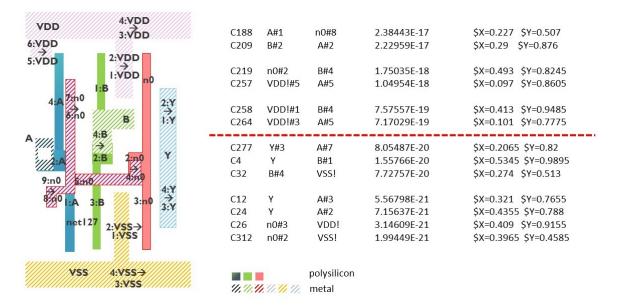

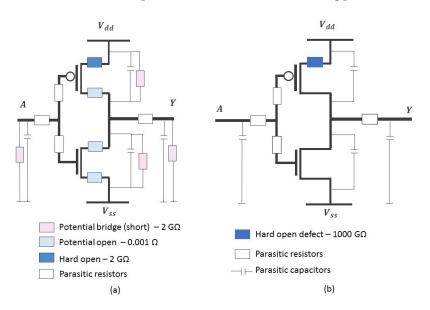

The objective of the library characterization stage is to generate a DDM per library cell. Cadence Quantus QRC is used to generate parasitics extracted transistor-level netlists for all library cells. Using inputs from the technology library, the tool calculates a parasitic resistance for every net segment and a parasitic capacitance between internal nodes. A segment with a large parasitic resistance indicates a long and thin wire which has

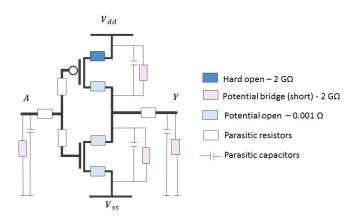

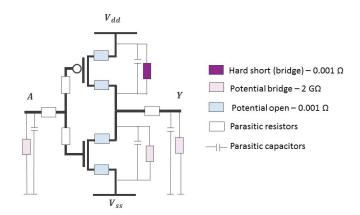

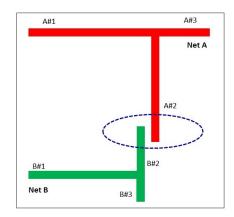

a higher chances of having an open defect. Parasitic capacitance can be extracted between nodes belonging to different nets (inter-net) or between nodes of the same net (intra-net or self-capacitance). A large capacitance indicates the corresponding nets between which the capacitor is located are close to each other and run in parallel for long distances. Therefore, they have a high chance of being shorted. Based on a user-defined threshold value, a defect location identification script is executed within the Modus software environment which determines the parasitic resistors and capacitors to be considered as opens and shorts in the target defect set. A parasitic resistor above user-defined threshold resistance is modeled as an open by replacing it with a high resistance of 2  $G\Omega$  in the transistor-level netlist. A parasitic capacitor above a threshold is modelled as a short by inserting a low-resistance value of 0.001  $\Omega$  in parallel with the capacitor. A high threshold value reduces the number of opens and shorts in the target defect set but might lead to the skipping of some possible defect cases. On the other hand, a very low threshold could mean modelling of unrealistic defect scenarios. In case of transistors, three defects - source-open, drain-open and source-drain short are modeled. Modus generates a separate defect injected netlist for every identified candidate defect. While generating a defect injected netlist the defect extraction scripts inserts place holder values to negate the effect of all other defect candidates other than the one, for which a netlist is being generated. Figure 4.2 illustrates the defect insertion for an open defect on the PMOS transistor source terminal. A hard open of 2  $G\Omega$ , is injected on the PMOS source terminal, whereas *potential opens* of 0.001  $\Omega$  at the transistor source and drain terminals are inserted at remaining source/drain terminals. A parasitic capacitor is shorted with a high resistance of 2  $G\Omega$  (potential bridges). Similar concept is illustrated for inserting a source-drain short in Figure 4.3. Parasitic resistors and capacitors less than the thresholds are not propagated as defect candidates but remain as a part of the netlist.

Figure 4.2: Open defect insertion and concept of potential defects.

Figure 4.3: Short defect insertion and concept of potential defects.

#------# Defect insertion based on potential defects

**‡**.....

for cell in listofCells do {

```

read RES_THRESH, CAP_THRESH;

read R_POTENTIAL_BRIDGE, R_POTENTIAL_OPEN

read R_OPEN, R_BRIDGE;

```

# parse parasitics-extracted Spectre netlists and store netlist contents cellContents = readLines(cell.sp);

```

# identify resistors, capacitors and transistor instances in the cell

mos_primitives = findMosModels(cell, cellContents);

listofResistor = PATTERN.MATCH('R');

listofCapacitors = PATTERN.MATCH('C');

```

```

# define lists to hold short, open and transistor defects

mos_defects = [];

shorts = [];

opens = [];

```

```

for capacitor in listofCapacitors

if capacitor > CAP_THRESH:

shorts.append(capacitor = R_BRIDGE);

identify capacitor nodes ----- > (n1,n2)

bridgeInstance = R_POTENTIAL_BRIDGE across (n1,n2);

bridgeLines.append(bridgeInstance);

```

```

for resistor in listofResistors

if resistor > RES_THRESH:

opens.append(resistor = R_OPEN);

```

```

# identify MOS defects

for transistor in mos_primitives:

drain, gate, source, bulk = identifyMosTerminals

# drain-open defect

mos_defects.append(drain = R_OPEN)

identify segment ----- > (d1,d2)

drainPotentialOpen = R POTENTIAL OPEN between (d1, d2);

drainPotentialOpenLines.append(drainPotentialOpen);

# source-open defect

mos_defects.append(source = R OPEN)

identify segment ----- > (s1,s2)

sourcePotentialOpen = R_POTENTIAL OPEN between (s1,s2);

sourcePotentialOpenLines.append(sourcePotentialOpen);

# source-drain short

mos_defects.append(sourcedrain = R_BRIDGE)

identify source-drain node pair----- > (sd1,sd2)

sourceDrainPotentialBridge = R_POTENTIAL_BRIDGE between (sd1,sd2);

sourceDrainPotentialBridgeLines.append(sourceDrainPotentialBridge);

for defect in opens:

write defect injected netlists;

for defect in shorts:

```

```

write defect injected netlists;

```

```

for defect in mos_defects:

```

```

write defect injected netlists;

```

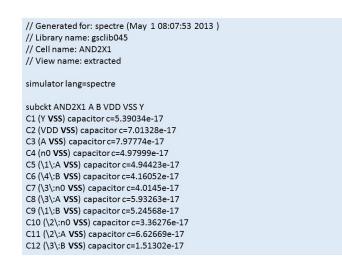

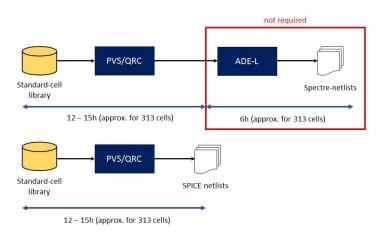

After the completion of the defect extraction step, for *D* identified defects in the target defect set, |D| + 1 netlists per cell are obtained (one defect free and |D| defect injected). The list of defects along with a short description are recorded in a faults list file per cell as illustrated in Figure 4.4. This completes the defect extraction step. From within the Modus environment, Liberate is invoked to perform a static simulation on each of these defect injected netlists using an exhaustive set *P* of cell-level test patterns (where  $P = 2^n$  for a cell with *n* inputs). If the target defect set is *D*, defect *d*  $\epsilon$  *D* is considered detected by applying an input pattern  $p \epsilon P$  if the output response for this case, differs from the defect-free output. For every defect *d*, all the cell-level test patterns *p* which can detect the defect are recorded in a defect detection file as illustrated in Figure 4.5. The defect detection file is generated per-cell and contains the following information:

- fault number and the description of the defect such as defect location and the nature of the defect (open/short).

- · input test-patterns which can detect the defect.

- · output response of the defect-free and defective netlist.

fault:0 description: bridge source-drain mp1 (\8\:n0 \4\:B \5\:VDD VDD) g45p1svt fault:1 description: bridge source-drain mp0 (\8\:n0 \1\:A \1\:VDD VDD) g45p1svt fault:2 description: bridge source-drain mp2 (\1\:Y s0 \3\:n0 \3\:Y VS) g45n1svt fault:3 description: bridge source-drain mp2 (\1\:Y n0 \1\:VDD VDD) g45p1svt fault:3 description: open drain mp1 (\8\:n0 \4\:B \5\:VDD VDD) g45p1svt fault:4 description: open source mp1 (\8\:n0 \4\:B \5\:VDD VDD) g45p1svt fault:5 description: open source mp1 (\8\:n0 \4\:B \5\:VDD VDD) g45p1svt fault:6 description: open drain mp0 (\8\:n0 \1\:A \1\:VDD VDD) g45p1svt fault:7 description: open source mp0 (\8\:n0 \1\:A \1\:VDD VDD) g45p1svt fault:9 description: open Rk14 (\4\:VSS VS) resistor r=0.1503 fault:9 description: open Rk13 (\2\:VSS \4\:VS) resistor r=0.001776 fault:10 description: open Rk2 (B \7\:B) resistor r=0.003546

Figure 4.4: An example of a faults list file.

| CELL=AND2X1                                                                      |

|----------------------------------------------------------------------------------|

| IN_PIN=A,B                                                                       |

| OUT_PIN=Y;                                                                       |

| FAULT=_fault0_DESC="bridge_source-drain_mp1 (\8\:n0 \4\:B \5\:VDD VDD) g45p1svt" |

| IN=1,1 OUT=1/0;                                                                  |

| FAULT=_fault3_DESC="bridge_C2 (VDD_VSS) capacitor c=7.01328e-17"                 |

| IN=1,0 OUT=0/1                                                                   |

| IN=0,0 OUT=0/1                                                                   |

| IN=0,1 OUT=0/1;                                                                  |

| FAULT=_fault5 DESC="bridge C4 (n0 VSS) capacitor c=4.97999e-17"                  |

| IN=1,0 OUT=0/1                                                                   |

| IN=0,0 OUT=0/1                                                                   |

| IN=0,1 OUT=0/1;                                                                  |

| FAULT=_fault6 DESC="bridge C5 (\1\:A VSS) capacitor c=4.94423e-17"               |

| IN=1,1 OUT=1/0;                                                                  |

| FAULT=_fault7_DESC="bridge_C6 (\4\:B_VSS) capacitor c=4.16052e-17"               |

| IN=1,1 OUT=1/0;                                                                  |

| FAULT=_fault9 DESC="bridge C8 (\3\:A VSS) capacitor c=5.93263e-17"               |

| IN=1,1 OUT=1/0;                                                                  |

Figure 4.5: Example defect detection file for 2-input AND cell.