**Delft University of Technology**

### Electromagnetic Design of High Frequency PFC Boost Converters using Gallium Nitride Devices

Wang, Wenbo

DOI

10.4233/uuid:fafbbfcb-9ed1-4920-8b9b-e4e64d143daf

**Publication date** 2017 **Document Version**

Final published version

#### Citation (APA)

Wang, W. (2017). Electromagnetic Design of High Frequency PFC Boost Converters using Gallium Nitride Devices. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:fafbbfcb-9ed1-4920-8b9b-e4e64d143daf

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy** Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# Electromagnetic Design of High Frequency PFC Boost Converters using Gallium Nitride Devices

Wenbo Wang 王文博

# Electromagnetic Design of High Frequency PFC Boost Converters using Gallium Nitride Devices

# Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir.K.C.A.M.Luyben; voorzitter van het College voor Promoties, in het openbaar te verdedigen op donderdag 19 oktober 2017 om 10:00 uur

Door

# Wenbo WANG

Master of Engineering, Northwestern Polytechnical University, China geboren te Shandong, China

## This dissertation has been approved by the

promotor: Prof. dr. J.A.Ferreira

## Composition of the doctoral committee:

| Rector Magnificus       | Chairman                                    |

|-------------------------|---------------------------------------------|

| Prof. dr. J.A.Ferreira, | Delft University of Technology, promotor    |

| Dr. J. Popovic,         | Delft University of Technology, co-promotor |

# Independent members:

| Prof. dr. G.Q.Zhang  | Delft University of Technology |

|----------------------|--------------------------------|

| Prof. dr. J.J. Smit  | Delft University of Technology |

| Prof.dr. L. Wang     | Xi'an Jiaotong University      |

| Prof.dr. N. Kaminski | University of Bremen           |

|                      |                                |

# Other member:

Ir. F. Pansier Delft University of Technology, advisor

Printed by Ipskamp Printing, 7500 AH Enschede, the Netherlands ISBN: 978-94-028-0825-4 Copyright © 2017 by Wenbo Wang

All rights reserved.

To my parents

献给我的父母

# Acknowledgement

People may be born equal overall, but not so in every single measure. There are people with better intuitive feelings over one particular subject than others, the ones naturally have stronger curiosity compared to the rest, those who are inherently more patient, etc. When I began my Ph.D, I felt like I have got nothing. Power electronics was more of one course to me rather than something I had great interests in. With the starting project of passive integration, I did not have much motivation and enthusiasm in asking why and finding out reasons behind. Moreover, I showed a lack of patience in adjusting myself to be initiative and to work in a systematic way. Needless to say, I had a really bad start and never pictured what it would be like when I finish. Now, I managed to translate the research work conducted in the past few years into this thesis. There have been many people who helped, encouraged, supported and accompanied me through these years and thus contributed to my work and this thesis either directly or indirectly. I would like to take this opportunity to express my gratitude and appreciation to them.

First of all, I would like to express my deepest gratitude to Ir. Frans Pansier, my daily supervisor and friend. He is the person from whom I learnt almost everything about power electronics. I was lucky to have him and have stimulate a lot from his sharp mind, critical thinking as well as his broad and profound knowledge, not only in power electronics but in other topics too. Throughout these years, apart from work, we also developed close personal relations. He helped me in difficult times through talks about life and religion, opened his home to me and introduced his family, shared his personal experiences and views. With this thesis, he spent as much time as I did, especially in the last two chapters. Without him, the finishing of my Ph.D, and also this thesis, would not be possible.

I am very grateful to my promoter Prof. Braham Ferreira. for giving me the opportunity to pursue Ph.D. degrees in his group and for granting me a second chance when I failed my first evaluation. Besides, I am also grateful for his broad vision and insightful guidance that inspired my research work. Moreover, I would like to thank him for the opportunity to continue working with him after my Ph.D in Beijng. I am sure I will benefit more from his brilliant ideas and his passion in the field of power electronics.

I would like to express my sincere thanks to my daily supervisor Dr.Jelena Popovic for her guidance and support. The questions she asked in each of our weekly meeting stimulated me to think independently and be more critical with mine and other people's work. I am very grateful for all the time and efforts she put in my reading and commenting my papers and

chapters. I am also thankful for her kind character, which makes our discussions rewarding and pleasant

My thanks also go to Ir. Sjoerd de Haan for being my daily supervisor in the first three years. Thanks for his guidance and patience.

I would like to acknowledge my doctoral examination committee, Prof. G.Q.Zhang, Prof. N.Kaminski, Prof. L. Wang and Prof. J.J. Smit for the valuable time they spent on reading my draft thesis and giving comments and suggestions.

In the course of my research work, I met great colleagues in our research group. Thanks to all the past and present colleagues for their help, accompany and sharing of knowledge. In particular, I would like to thank Yeh Ting for all the discussions and talks we had on power electronics, Ivan Josifovic and Milos Acanski for their advices on experimental work, Marcelo Gutierrez-Alcaraz for his tips on how to carry out research, Emile Brink for his suggestions on inductance calculation, Johan Wolmarans for his humour, Tsegay Hailu and Aniel Shri for being nice officemates, Todor Todorčević for sharing his opinions on electronic products. I would also like to than the Chinese Ph.Ds and Postdocs, Yi Wang, Dongsheng Zhao, Xun Gong, Xuezhou Wang, Dong Liu, Junyin Gu and Kewei Huang for the help they gave and the time we spent together. Besides, I would like to thank Rob Schoevaars, Bart Roodenburg, Kasper Zwetsloot and Harrie Olsthoorn for their help with the practical work in lab. Also, I would like to express my appreciation the secretaries in our group, Laura, Sharmila and Ellen for helping me with all kinds of matters.

Special thanks go to Jianing Wang and Ilija Pecelj. The help and encouragement from Jianing was much appreciated and I really enjoyed our walks in the late afternoons and meals we had together. Thank Ilija for being sarcastic in a funny way and for his friendship. It was nice talking, laughing and having dinners together, even in hard times.

Life would have been much more difficult without the support from my friends both in Delft and around the world. I would like to acknowledge Le Li, Ziwei Ouyang, Jinku Hu, Ziliang Qiao, Xiaoshan Liu, Chao Wang, Guanshan Liu, Hao Cheng, Yuankang Cheng, Jing Han, Daniel Yi for their friendship and the regular or unregular phone calls we had. In particular, I would like to express my gratitude to Jianfei Yang, Zhang Li, Yan Ren, Changlin Chen, Ting Hao, Hongling Wang and Shaoying Wang for keeping me accompanied through these years and for all the nice meals we had and poker games we played. I am also sincerely grateful to Yanyan Li for her kindness, understanding and support.

Above all, my deepest thanks to my parents, to whom this thesis is dedicated and my sincere gratitude to my young brother, for their unconditional love and support. I love you.

# **Table of Contents**

| Chapte                       | r 1. Introduction ······ 1                                                   |

|------------------------------|------------------------------------------------------------------------------|

| 1.1                          | Thesis Background1                                                           |

| 1.1.<br>1.1.<br>1.1.<br>of p | 2 Developments of power semiconductor technologies- Technology push          |

| 1.2                          | Problem description9                                                         |

| 1.3                          | Thesis objectives11                                                          |

| 1.4                          | Thesis layout12                                                              |

| 1.5                          | Reference14                                                                  |

| Chapte                       | r 2. Overview of GaN Devices and Converters19                                |

| 2.1                          | Introduction19                                                               |

| 2.2                          | GaN material properties and device potentials20                              |

| 2.3                          | Emerging GaN transistors22                                                   |

|                              | 1 Introduction22                                                             |

| 2.3.<br><b>2.4</b>           | 22 Lateral GaN transistors ······ 23 High frequency GaN converters ······ 28 |

| 2.4.                         | 1 Single-die GaN HEMT based high frequency converters                        |

| 2.4.                         | 2 GaN GIT based high frequency converters                                    |

| 2.5                          | Challenges of GaN transistors and converters                                 |

| 2.6                          | Discussion46                                                                 |

| 2.7                          | Summary48                                                                    |

| 2.8                          | References······49                                                           |

| Chapte                       | r 3. Overview on PFC converters61                                            |

| 3.1                          | Introduction61                                                               |

| Power factor correction<br>Types of PFC technique<br><b>Overview of PFC converters</b><br>Common properties of DC-DC converters for implementing PFC<br>Step-up DC-DC converters as PFC preregulators<br>Step-down DC-DC converters as PFC preregulators                                                                              |                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overview of PFC converters                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                           |

| Common properties of DC-DC converters for implementing PFC<br>Step-up DC-DC converters as PFC preregulators<br>Step-down DC-DC converters as PFC preregulators                                                                                                                                                                        |                                                                                                                                                                                                           |

| Step-up DC-DC converters as PFC preregulators                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                           |

| Step-down DC-DC converters as PFC preregulators                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                           |

| Step-up/Step-down PFC topologies                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                           |

| Discussion                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                           |

| Interactions between PFC stage and DC-DC stage                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                           |

| Qualitative comparisons of PFC topologies                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                           |

| High frequency operation of PFC topologies                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                           |

| Boost converter used for exploring potentials of GaN devices                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                           |

| Summary                                                                                                                                                                                                                                                                                                                               | •••••                                                                                                                                                                                                     |

| References                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                           |

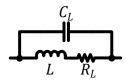

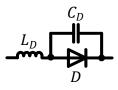

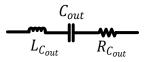

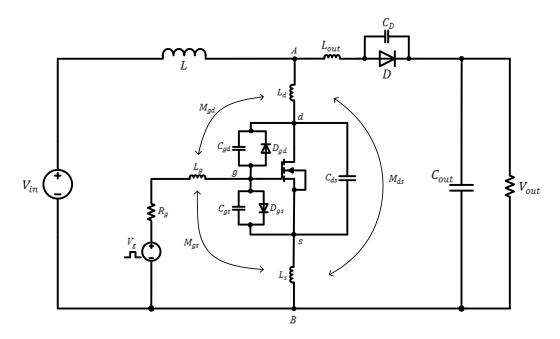

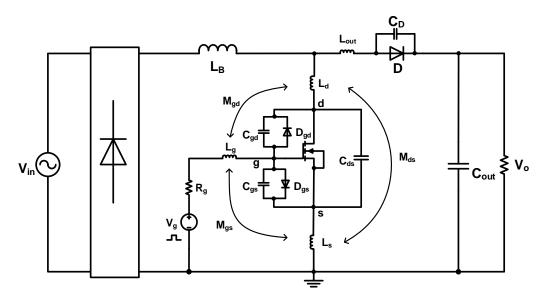

| Equivalent circuit of a GaN based boost converter                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                           |

| Equivalent circuit of a GaN based boost converter                                                                                                                                                                                                                                                                                     | ••••••                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                           |

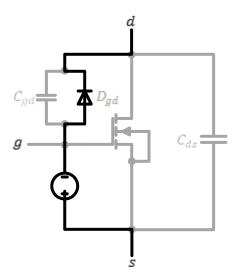

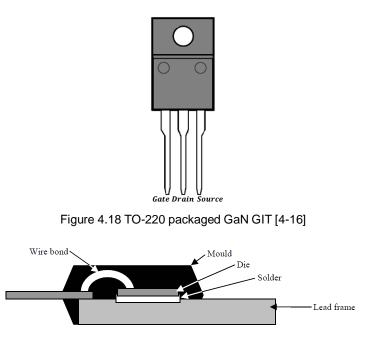

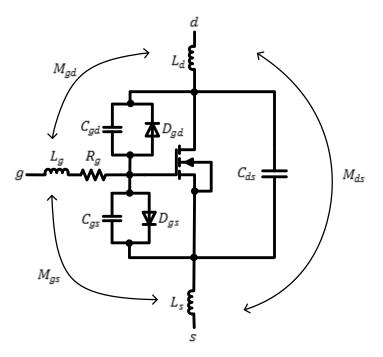

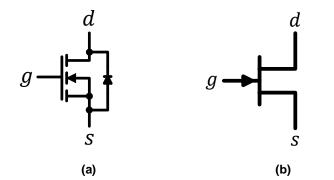

| A general circuit model for normally-off GaN HEMT and GaN GIT                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                           |

| A general circuit model for normally-off GaN HEMT and GaN GIT                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                           |

| A general circuit model for normally-off GaN HEMT and GaN GIT<br>Equivalent circuit of a GaN based boost converter<br>Analytical loss modelling of GaN transistors in a boost converter                                                                                                                                               |                                                                                                                                                                                                           |

| A general circuit model for normally-off GaN HEMT and GaN GIT<br>Equivalent circuit of a GaN based boost converter<br>Analytical loss modelling of GaN transistors in a boost converter<br>Loss modelling of GaN transistors in a boost converter                                                                                     |                                                                                                                                                                                                           |

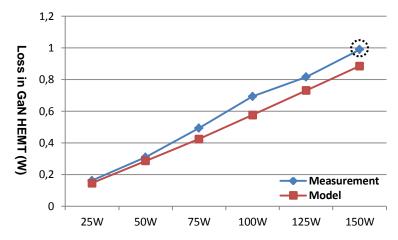

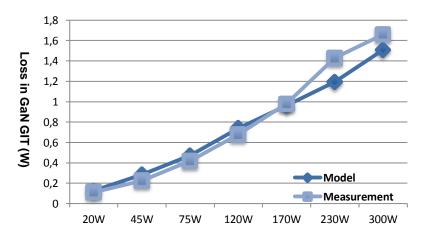

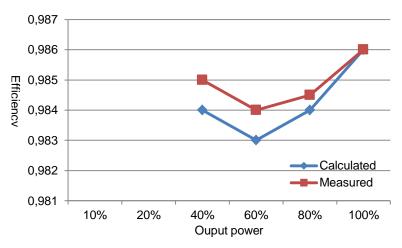

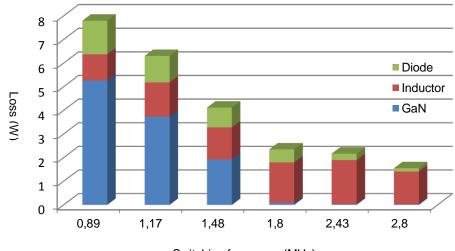

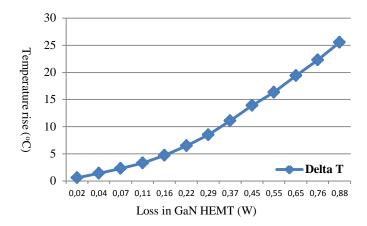

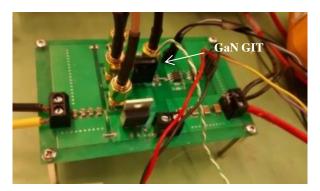

| A general circuit model for normally-off GaN HEMT and GaN GIT<br>Equivalent circuit of a GaN based boost converter<br>Analytical loss modelling of GaN transistors in a boost converter<br>Loss modelling of GaN transistors in a boost converter<br>Validation of the developed loss model in a boost converter                      |                                                                                                                                                                                                           |

| A general circuit model for normally-off GaN HEMT and GaN GIT<br>Equivalent circuit of a GaN based boost converter<br><b>Analytical loss modelling of GaN transistors in a boost converter</b><br>Loss modelling of GaN transistors in a boost converter<br>Validation of the developed loss model in a boost converter<br>Discussion |                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                       | Interactions between PFC stage and DC-DC stage<br>Qualitative comparisons of PFC topologies<br>High frequency operation of PFC topologies<br>Boost converter used for exploring potentials of GaN devices |

| 5.2                               | 2 Loss analysis of GaN transistors in boost converters                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 149                                                                                          |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

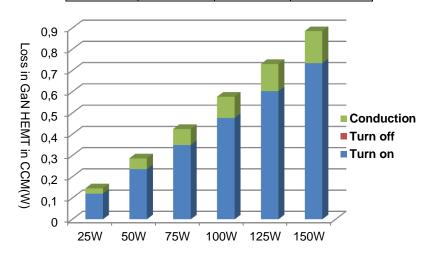

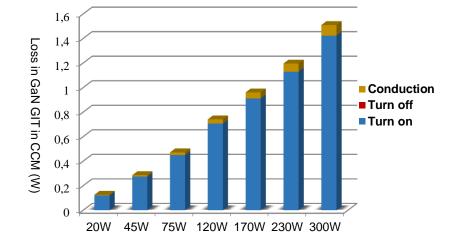

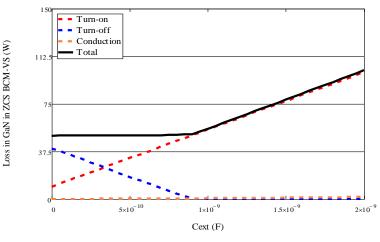

| :                                 | 5.2.1 Loss characteristics of GaN transistors in boost converters in CCM                                                                                                                                                                                                                                                                                                                                                                                                                                           | 150                                                                                          |

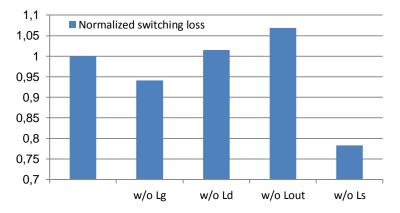

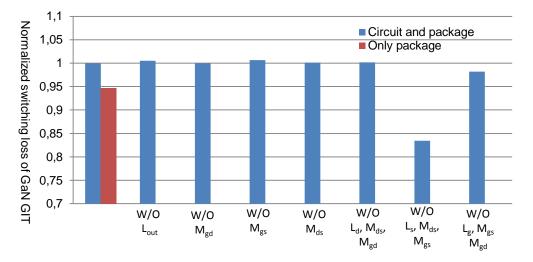

| :                                 | 5.2.2 Desirable switching conditions of GaN transistors for high frequency applica                                                                                                                                                                                                                                                                                                                                                                                                                                 | ations 154                                                                                   |

| 5.3                               | 3 Application of GaN transistors in high frequency boost converte                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ers in BCM-VS                                                                                |

|                                   | 156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

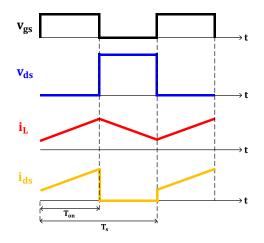

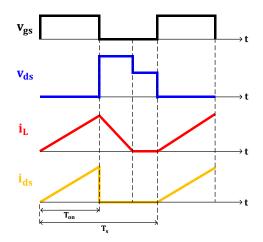

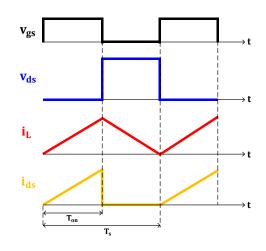

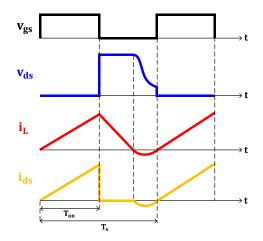

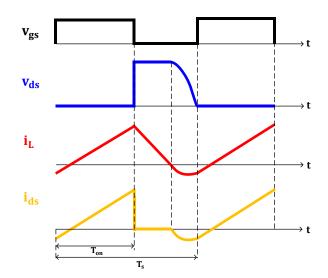

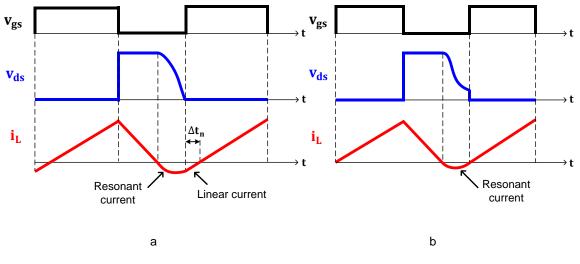

| :                                 | 5.3.1 Operation modes in a boost converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 156                                                                                          |

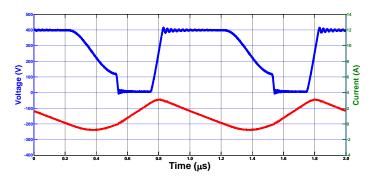

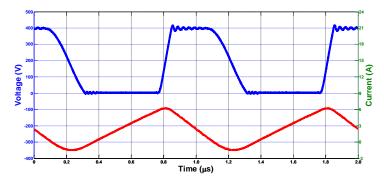

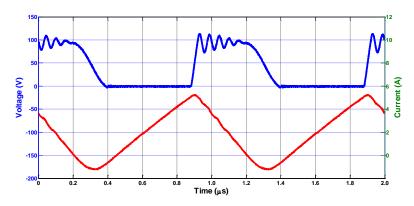

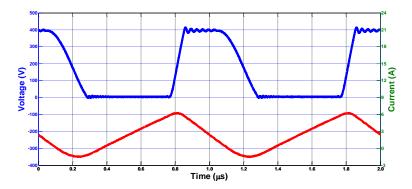

| :                                 | 5.3.2 Application of GaN transistors in BCM-VS                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 161                                                                                          |

| 5.4                               | 4 Optimal utilization of GaN transistors in high frequency boost co                                                                                                                                                                                                                                                                                                                                                                                                                                                | onverters in                                                                                 |

| BC                                | CM-VS······                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 165                                                                                          |

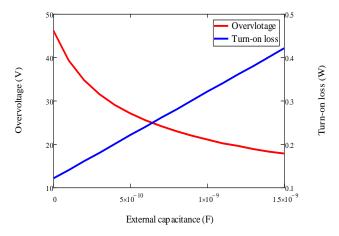

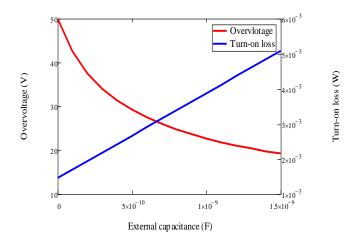

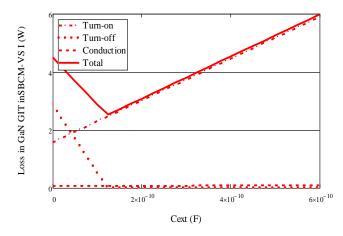

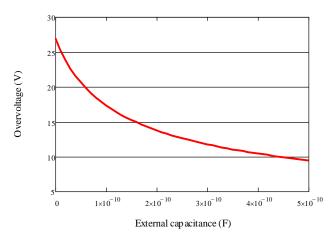

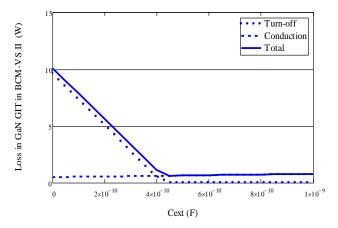

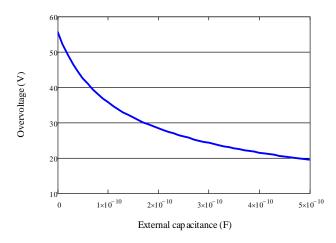

| :                                 | 5.4.1 Trade-off between switching loss minimization and overvoltage suppression                                                                                                                                                                                                                                                                                                                                                                                                                                    | ۱····· 165                                                                                   |

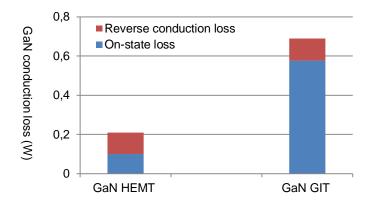

| :                                 | 5.4.2 Reverse conduction loss reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 172                                                                                          |

| 5.5                               | 5 Boundaries and limitations of using GaN devices in BCM-VS for                                                                                                                                                                                                                                                                                                                                                                                                                                                    | high                                                                                         |

| fre                               | equency operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 176                                                                                          |

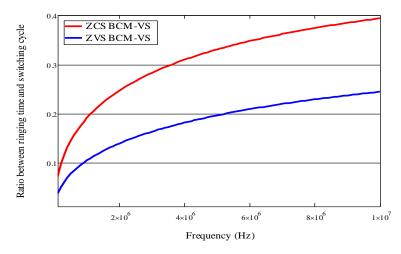

| :                                 | 5.5.1 Influence of high frequency operation of BCM-VS on GaN transistor                                                                                                                                                                                                                                                                                                                                                                                                                                            | 176                                                                                          |

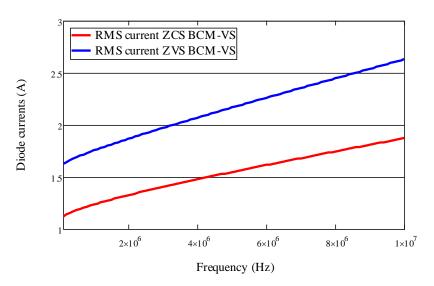

| :                                 | 5.5.2 Influence of high frequency operation of BCM-VS on freewheeling diode                                                                                                                                                                                                                                                                                                                                                                                                                                        | 183                                                                                          |

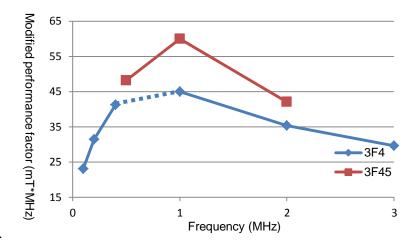

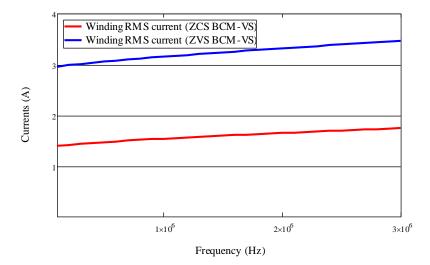

| :                                 | 5.5.3 Influence of high frequency operation of BCM-VS on boost inductor                                                                                                                                                                                                                                                                                                                                                                                                                                            | 184                                                                                          |

| 5.6                               | 6 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 187                                                                                          |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| 5.7                               | 7 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 187                                                                                          |

|                                   | 7 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

| Chaj                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ency PFC                                                                                     |

| Chaj                              | pter 6. Design and optimization of a GaN GIT based high freque st converter                                                                                                                                                                                                                                                                                                                                                                                                                                        | ency PFC<br>189                                                                              |

| Chaj<br>boos                      | pter 6. Design and optimization of a GaN GIT based high freque<br>st converter                                                                                                                                                                                                                                                                                                                                                                                                                                     | ency PFC<br>189<br>189                                                                       |

| Chaj<br>boos<br>6.1<br>6.2        | pter 6. Design and optimization of a GaN GIT based high freque<br>st converter                                                                                                                                                                                                                                                                                                                                                                                                                                     | ency PFC<br>189<br>189<br>189                                                                |

| Chaj<br>boos<br>6.1<br>6.2        | pter 6. Design and optimization of a GaN GIT based high freque<br>st converter<br>Introduction<br>Loss modeling of a GaN GIT based PFC boost converter                                                                                                                                                                                                                                                                                                                                                             | ency PFC<br>189<br>189<br>189<br>189                                                         |

| Chaj<br>boos<br>6.1<br>6.2        | pter 6. Design and optimization of a GaN GIT based high freque         st converter         1       Introduction         2       Loss modeling of a GaN GIT based PFC boost converter         6.2.1 Analytical loss modeling of inductor and diode         6.2.2 Loss modeling of a GaN based PFC boost converter in BCM-VS                                                                                                                                                                                        | ency PFC<br>189<br>189<br>189<br>189<br>190<br>194                                           |

| Chaj<br>boos<br>6.1<br>6.2        | pter 6. Design and optimization of a GaN GIT based high freque         st converter         1       Introduction         2       Loss modeling of a GaN GIT based PFC boost converter         6.2.1 Analytical loss modeling of inductor and diode         6.2.2 Loss modeling of a GaN based PFC boost converter in BCM-VS                                                                                                                                                                                        | ency PFC<br>189<br>189<br>189<br>189<br>190<br>194<br>194<br>196                             |

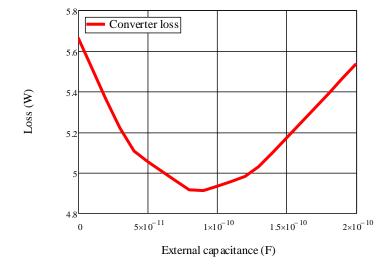

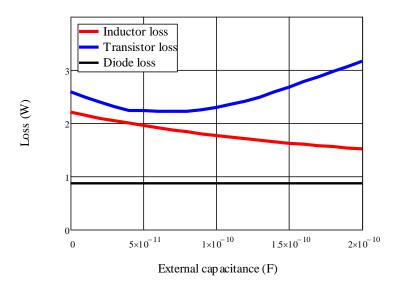

| Chaj<br>boos<br>6.1<br>6.2        | <ul> <li>pter 6. Design and optimization of a GaN GIT based high frequest converter</li> <li>Introduction</li> <li>Loss modeling of a GaN GIT based PFC boost converter</li> <li>6.2.1 Analytical loss modeling of inductor and diode</li> <li>6.2.2 Loss modeling of a GaN based PFC boost converter in BCM-VS</li> <li>Besign of a high frequency GaN GIT based PFC boost converter</li> </ul>                                                                                                                   | ency PFC<br>189<br>189<br>189<br>189<br>190<br>194<br>194<br>196                             |

| Chaj<br>boos<br>6.1<br>6.2        | <ul> <li>pter 6. Design and optimization of a GaN GIT based high frequest converter</li> <li>Introduction</li> <li>Loss modeling of a GaN GIT based PFC boost converter</li> <li>6.2.1 Analytical loss modeling of inductor and diode</li> <li>6.2.2 Loss modeling of a GaN based PFC boost converter in BCM-VS</li> <li>Design of a high frequency GaN GIT based PFC boost converter</li> <li>6.3.1 Design of a BCM-VS PFC boost converter</li> </ul>                                                             | ency PFC<br>189<br>189<br>189<br>189<br>190<br>194<br>194<br>196<br>201                      |

| Chaj<br>boos<br>6.1<br>6.2        | <ul> <li>pter 6. Design and optimization of a GaN GIT based high frequest converter</li> <li>Introduction</li> <li>Loss modeling of a GaN GIT based PFC boost converter</li> <li>6.2.1 Analytical loss modeling of inductor and diode</li> <li>6.2.2 Loss modeling of a GaN based PFC boost converter in BCM-VS</li> <li>Design of a high frequency GaN GIT based PFC boost converter</li> <li>6.3.1 Design of a BCM-VS PFC boost converter</li> <li>6.3.2 Optimization of a BCM-VS PFC boost converter</li> </ul> | ency PFC<br>189<br>189<br>189<br>189<br>190<br>194<br>194<br>196<br>201<br>207               |

| Chaj<br>boos<br>6.1<br>6.2<br>6.3 | <ul> <li>pter 6. Design and optimization of a GaN GIT based high frequest converter</li> <li>Introduction</li> <li>Loss modeling of a GaN GIT based PFC boost converter</li> <li>6.2.1 Analytical loss modeling of inductor and diode</li> <li>6.2.2 Loss modeling of a GaN based PFC boost converter in BCM-VS</li> <li>Design of a high frequency GaN GIT based PFC boost converter</li> <li>6.3.1 Design of a BCM-VS PFC boost converter</li> <li>6.3.2 Optimization of a BCM-VS PFC boost converter</li> </ul> | ency PFC<br>189<br>189<br>189<br>189<br>190<br>194<br>194<br>194<br>196<br>201<br>207<br>207 |

| 6.5     | Summary211                             |

|---------|----------------------------------------|

| 6.6     | References······212                    |

| Chapte  | 7. Conclusions and recommendations 215 |

| 7.1     | Conclusions216                         |

| 7.2     | Thesis contributions218                |

| 7.3     | Recommendations for future research219 |

| Append  | lix A. Loss model validation 221       |

| Summa   | ry                                     |

| Samen   | vatting ······ 231                     |

| Publica | tions and Award ······ 235             |

| Curricu | lum Vitae 237                          |

## **Chapter 1. Introduction**

#### 1.1 Thesis Background

Power Electronics, in general, is an enabling technology that facilitates efficient conversion, control and conditioning of electric power from power sources to loads [1-1]-[1-4]. Nowadays, almost all kinds of electrical energy processing in industrial, commercial, residential, utility, transportation, aerospace and military applications benefit from employments of power electronics systems [1-1] [1-3]-[1-5]. The development of power electronics, therefore, is driven by both the push from innovations in the technology itself and the pull from requirements of the applications it is used in [1-6].

#### 1.1.1 Demands on performance of power electronics systems- Application pull

Power electronics systems are spreading into every corner of transportation, industry, lighting, consumer, communication and energy generation, transmission and distribution applications [1-2]. Within each section of application category, power electronics systems are facing different energy sources, diversity in the loads, wide power level span, etc. And therefore, demands on performance measures of power electronics system can diverse a lot depending on environmental conditions and regulatory requirements of the specific application. Many different kinds of application requirements have been identified and categorized, such as high efficiency, high power density and low cost.

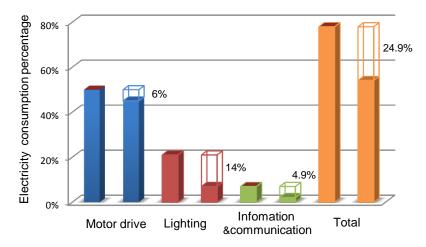

**High efficiency** is a crucial demand of power electronics systems driven mainly by regulations originated from purpose of energy-saving. Since most of electrical energy now flows through power electronics systems, slight efficiency increase in power electronics systems would lead to great energy savings worldwide [1-5]. In European Union (EU), for instance, electric energy consumption was reported occupying 20% of total final energy consumption in 2009 and will be growing much faster than any other energy sources in the following few decades. It was predicted that by implementing power electronics systems in three key application groups as listed in Figure 1.1, which contribute to 78% of electric energy consumption in total, about 25% of EU electricity consumption can be saved [1-7]. Efficiency improvements in these power electronics systems would result in further great energy consumption reduction across EU. Moreover, current trend of ever-increasing demand for energy, pressing dwindling of fossil fuels and urgent need to mitigate environmental pollution and climate change problems has resulted in tightened regulatory requirements and increased energy price. Increasing efficiency of power electronics systems will therefore directly bring financial benefits and indirectly help to save energy and ease environmental problems. In the past few decades, efficiency increase in power electronics systems is made possible mainly by progress in power semiconductor devices. Development of traditionally used Si devices, as will be elaborated further in 1.1.2, is entering into maturing stage after the uninterrupted improvements of the technology for three decades. Further performance improvements of power semiconductors are still needed as Si devices usually account for an important share of power loss and have noticeable effects on overall efficiency in today's power converters, especially the hard-switching [1-8] [1-9]. The dilemma cannot be overcome without a radical change in power semiconductor technology.

Figure 1.1. Electric energy saving potentials by application of power electronics in EU [1-7]

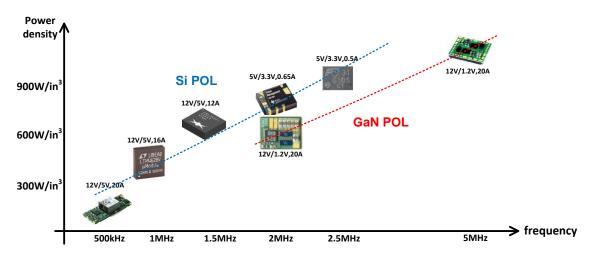

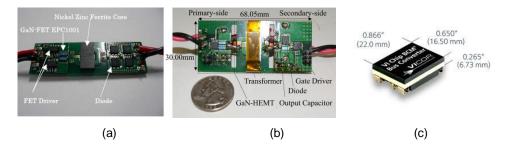

High power density is required in applications where space and/or weight is limited such as portable devices, automotive, lighting aerospace and telecom facilities. In applications with relatively less strict demand on volume reduction, power electronics systems and their associated thermal management can take large part of the whole system footprint and it is favourable to push power density of these systems to higher level as well. Increase of power density has traditionally been achieved by pushing up operation frequencies of power converters utilizing faster-switching Si power semiconductors to reduce size of bulky passives components while keeping switching loss of the semiconductors, and the volume of cooling system thereof, low. Take Si transistor based POL converters as an example, as illustrated in Figure 1.2, the increase of power density is made possible through both increase in operation frequency to reduce size of passive components and decline in power handling to keep size of the thermal management parts small. Adoption of this approach to achieve higher level power density is being challenged by the fact that, with operation frequency being pushed up, volume distribution within a power electronics system is changing i.e. the size-dominating part is shifting from passives to cooling constructions [1-10]. As size of the cooling construction is determined mostly by both the amount of loss in power semiconductors and high temperature operation capability of the device, better device is needed. Consequently, to further increase power density of a power electronics system, transistors more suitable for operating in elevated frequencies than state-of-art Si devices have to be applied. In fact, application of low voltage GaN devices in the conventionally Si device based POL converters to further increase power density of the converters has already been performed, as can be seen in Figure 1.2. Due to the lack of suitable high voltage devices, further increase of power density in line-voltage power converters e.g. PFC boost converter, unfortunately, has not been accomplished.

Figure 1.2 Power density increase by pushing up operation frequency in POL converters [1-11] - [1-13]

#### (Specification: input voltage/output voltage, output current)

Low Cost has always been and will continue to be one important measure that is common to all power electronics systems. A typical power electronics system usually is assembled with power devices mounted on heatsinks while the passives, control circuits, protection circuits etc. implemented on PCBs [1-14]. Cost in a power electronics system, accordingly, includes component cost (passive and active components), mechanical parts (PCBs, connectors, etc.) and thermal parts (heatsinks) cost, assembly cost (labor), etc. Currently, there's a trend of rising cost of copper and magnetic material and falling cost of Si based semiconductor products, which makes size and volume reduction of magnetic parts critical to further compress cost of components [1-15]. As PCB construction technology is maturing, room for cost reduction of PCB per unit area is limited. Since the size and volume of heatsink needed depends greatly on the amount of loss in a power device and the maximum temperature the device can work at, cost of the thermal parts can be lowered if thermal burden is relieved i.e. loss in power devices are reduced or the device can handle higher thermal stress. Assembly of power electronics products is labor-intensive as different kinds of assembling technology are demanded, ranging from electric parts to mechanical parts, from through hole technology to surface mount technology, and so on. Although there are efforts to reduce assembling cost, development of standardized components for instance, the most common practice taken by power electronics product manufacturers is to have the assembly processed in low labor cost countries like China [1-2]. In fact, the manufacturing now is moving to countries like India and Vietnam where labor is even cheaper to minimize assembling cost. Given current status and future trend on costs of different sectors in a power electronics system, there's still room for cost reduction if size of both magnetic components and heatsinks can be reduced. To fulfill this further cost reduction need, power semiconductor devices that are capable of operating at high operation frequency with low loss need to be developed.

There are also other performance measures, such as high reliability, long lifetime, high modularity, high maintainability etc. [1-8]. However, in one way or another, they all couple with at least one of the three factors discussed above. For example, as losses will be dissipated in the form of heat in a power electronics system, increasing efficiency i.e. reducing loss would decrease temperature of components and mechanical parts like wire/connectors leading to prolonged lifetime and enhanced reliability of the system as a whole in the long run. On the other hand, with sufficient loss reduction, heatsinks maybe exempted from a power electronics system, resulting in more compact design and thus ease the task of modularity.

#### 1.1.2 Developments of power semiconductor technologies- Technology push

It is well acknowledged that power semiconductor is the heart of a power electronics system, and performance improvements of the system depends, to great extent, on innovations of the switching device [1-1]. Improvements in circuits or topologies, control, passive components and packaging techniques, etc. also contribute to the development of power electronics. However, these technologies generally follow the development of power semiconductors to best accommodate the semiconductors in different applications [1-16].

There are different opinions on which event marks the beginning of power electronics, e.g. Bimal K. Bose considered the appearance of glass-bulb mercury-arc rectifier in 1901, while Thomas G. Wilson preferred the invention of magnetic amplifier in 1912 [1-1] [1-17] [1-19]. There is, however, no dispute over the fact that revolutionary development of power electronics technology did not start until controllable solid-state electronic devices appeared. Commercial availability of thyristor or SCR (silicon controlled rectifier) and bipolar junction transistors (BJT) in the 1950's stimulated rapid expansion of power electronics in conversion and control of electric power. With the help of continuous improvements on characteristics and reliability of the devices, in particular the disclose of Gate Turn Off thyristor (GTO), thyristors dominated in high power applications for almost two decades. In fact, thyristors are still active today in high power, low frequency applications. Meanwhile, BJTs were favored in low and medium power applications. Although there have been great efforts to increase the ratings of BJTs e.g. the introduction of Darlington structure, due to inherent demerit of current-control technology and limited switching speed, the BJTs were gradually replaced by MOS (Metal-Oxide-Semiconductor) gated, voltage-controlled transistors from late 1970's [1-17] [1-18]. The advent of insulated-gate power devices, in particular MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) in the 1970's and IGBT

(Insulated Gate Bipolar Transistor) in the 1980's, are significant milestones in the history of power semiconductors as these devices have been shaping the industry of power electronics ever since.

Although there were innovations and applications of many different types of power semiconductor technologies, such as MCT (MOS gate controlled Thyristor) and IGCT (Insulated Gatecommutated Thyristor), MOSFET and IGBT have been the most popular devices in the past three decades. Due to trade-offs among different characteristics of power transistors e.g. off-state voltage blocking capability, on-state current carrying ability, time needed for transitions between on and off state, etc. MOSFET is the dominating device in low power/voltage, high frequency applications like PFC (Power factor correction) and DPS (Distributed Power Systems); while IGBT reign in medium and high power/voltage, low frequency applications such as UPS (uninterruptable power supplies) and Photovoltaic (PV) inverters. After 30 years' successive technological innovations, characteristics of MOSFETs and IGBTs have improved dramatically and have entered into maturing stage. In fact, as manufacturing technologies has evolved to such advanced stage, physical limits of the traditionally used Silicon (Si) material, such as breakdown field and thermal conductivity, are being approached. Further performance improvements in one of the important characteristics may not practically possible without the degradation of the other(s). Take power MOSFETs that can be used in PFC boost converter ( $\geq 600V$ ) as an example, the on-state resistance can be as low as 0.015  $\Omega$  in a 650V superjunction MOSFET with a package of so-called Max 247. This MOSFET, however, has a large input capacitance of 18.5 nF that leads to very slow switching speed [1-20]. On the other hand, several MOSEFT products with a maximum blocking voltage of up to 1.5kV are available from the market, among which the one with smallest on-state resistance is the product packaged in TO247 with a R<sub>dson</sub> value of up to 1.8  $\Omega$  [1-21]. In addition, maximum junction temperature of today's Si MOSFETs is confined to 200 °C [1-22].

Attempts to develop Si transistors, especially the ESBT (Emitter-Switched Bipolar Transistor), that can stretch theoretical limits of the material had been performed. ESBT has a cascode configuration combining a high voltage, high current BJT and a low voltage, fast switching MOSFET, packaged either as a single monolithic chip or in a hybrid way [1-23]. The particular structure allows achievement of high voltage, small resistance and fast switching speed simultaneously. Today, maximum blocking voltage of commercial ESBT products is up to 1.7kV, packaged in TO247 with on-state resistance of 0.07  $\Omega$  [1-24]. The ESBTs, however, requires complex driving and control to achieve optimal functionality, resulting from the fact that the switching of both the BJT (the current of which affects not only the static but also dynamic behavior) and the MOSFET needs to be handled in an intelligent way [1-25]. In a PFC boost converter where the current through the transistor varies, for instance, a driving scheme of adjusting the voltage and current in the base of ESBT according to the instantaneous value of the

current is required [1-26]. Although there has been lots of efforts to provide suitable driving solutions, ESBT is not widely preferred in today's industrial applications [1-23] [1-26].

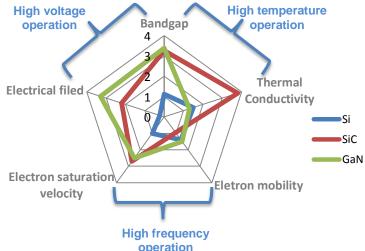

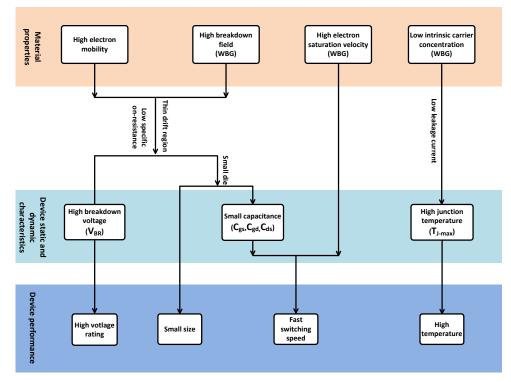

Wide bandgap (WBG) materials, such as Gallium Arsenide (GaAs), Silicon Carbide (SiC), Gallium Nitride (GaN), diamond, etc. offer significantly better electrical and thermal properties over Si. And thus, theoretically, performance of WBG power semiconductors would be superior to Si counterparts. Research on developing WBG devices has been going on for many years and focuses have gradually been given to SiC and GaN devices as they showed the best tradeoffs among material properties, commercial availability of starting material and relatively maturity of their technological processes [1-27]. Compared with Si technology, as illustrated in Figure 1.3, SiC and GaN semiconductors are capable of operating at higher temperature, higher voltage and higher frequency conditions [1-28] [1-30].

Figure. 1.3 Comparisons on material properties of Si, SiC and GaN

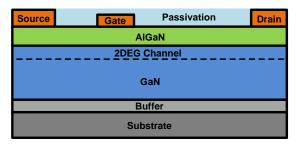

With recent availability of qualified products from multiple suppliers, discussions on SiC and GaN technology is shifting from theoretical analysis and speculations to practical solutions to best accommodate the devices in various applications. Currently, a variety of SiC products are available including MOSEFT, diode, JFET, IGBT, BJT, which are mostly tailored for high voltage (>900V), high power applications; GaN products, on the other hand, are also available in the form of different types of transistors and diodes. The major family of GaN transistors is high electron mobility transistors (HEMTs) and HEMT-derivatives, which are suitable for low voltage (<900V), high frequency applications [1-29]. Results from evaluations and applications of the emerging new devices showed that performances of traditional power electronics systems can be elevated in terms of efficiency, power density, etc. Moreover, WGB devices are also capable of initiating new applications that are beyond the reach of Si technology.

High efficiency power converter prototypes were successfully implemented using GaN transistors [1-30] [1-31]. For instance, efficiency of a 300V/50V, 200W synchronous buck converter operating at 500kHz can be pushed up to more than 92% in hard switching and over 99% in soft switching using a 600V, 0.25  $\Omega$  GaN transistors [1-32].

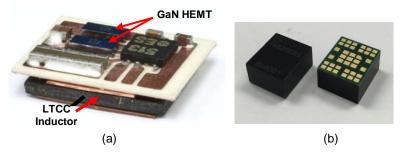

- High power density power electronics systems facilitated by GaN transistors have already been demonstrated [1-11] [1-34] [1-35]. Power density of a low voltage GaN HEMT based 12–1.2V POL (point of load) converter, for example, can be pushed up to 1100 W/in<sup>3</sup> when it operates at 5MHz with a maximum output current of 20A [1-11].

- New applications potentials of WBG transistors have been well promoted and, with availability of qualified products, realizations of the potentials can be expected [1-36]. It was predicted that with the availability of SiC or GaN devices, which have a high temperature operation ability up to 250 °C, a loosened requirement on heat exchanger of power electronics systems in space exploration is possible, which could lead to new design of the thrust engine suitable for deeper space missions [1-37] [1-38].

As performances of WBG devices do live up to expectations, with wider adoption of the devices i.e. increased production and decreased cost, they are believed to be able to replace Si devices and reshape the industry power electronics in near future [1-29].

# 1.1.3 Applications of GaN semiconductors in power electronics systems -Development trend of power electronics

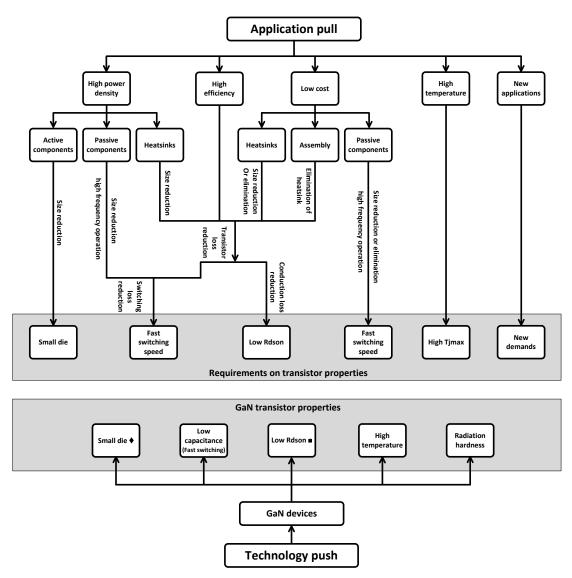

As the high efficiency, high power density and low cost requirements of power electronics systems can all be translated into the need of suitable power semiconductors for high frequency operation, with the advent of GaN devices that are superior to state-of-art Si devices in terms of switching speed, a trend of high frequency operation with GaN semiconductors to satisfy the demands is appearing. In fact, application of GaN devices in high frequency power electronics systems will bring benefits more than expected especially in hard switching systems, as illustrated in Figure 1.4.

GaN devices have much faster switching speed than Si counterparts, resulting in great switching loss reduction in many power electronics applications even at high frequencies. Material properties of GaN device also promise lower on-resistance of the device compared with Si counterparts with the same voltage blocking capability and die size, leading to reduced conduction loss in the device. Size as well as cost reduction of both passive components and heatsinks can be achieved simultaneously by pushing up operation frequency while having low loss in switching devices. Besides, when GaN operates at sufficient high frequencies that permit the usage of air core magnetics or/and when losses in GaN is low that elimination of heatsinks is possible, assembly cost can also be reduced. Furthermore, when the same voltage and on resistance characteristics are maintained, GaN devices would need much smaller die (and smaller package) than corresponding Si devices. And thus, the effect of GaN device on system

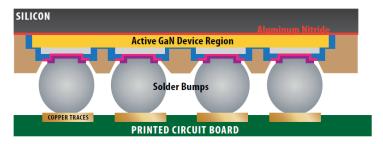

miniaturization starts already from size reduction of the component itself. Moreover, in GaN products, a thin GaN epi-layer usually grows on a Si substrate and the manufacturing process is compatible with conventional fabrication equipment for Si devices [1-39]. Given the fact that GaN device requires smaller die size than Si device with similar ratings, GaN products may even be cheaper than Si products in future.

GaN devices are, in theory, capable of surviving high temperature operations thanks to low intrinsic carrier concentrations of the material, which will not affect carrier conductivity and functioning of the devices thereof up to 600°C [1-40]. At this moment, maximum junction temperature of GaN products is confined to 175 °C, limited mainly by a lack of suitable packaging technologies [1-41] [1-42]. Research on developing better packaging techniques for both discrete GaN devices and GaN power modules has already started and noticeable progress has been made recently. The X-6 low-profile package from APEI, for example, is developed to accommodate discrete GaN HEMT up to 225°C [1-43]. With more advanced packaging technology, wider temperature span of GaN devices can be expected. As no high temperature GaN product is commercially available, with which the potentials of GaN devices could have been explored in this thesis, the high temperature capability of GaN devices is not considered in this work.

GaN devices also hold the potentials for enabling new applications. Although emerging GaN products already perform better than Si counterparts in measures of efficiency and power density, more advanced characteristics as promised by basic material properties can be expected from future GaN devices. For instance, most GaN transistors available now are heterojunction devices in lateral structure as they grow on non-GaN substrates like Si, SiC and Sapphire. And therefore, the transistors are regarded as low voltage devices. In fact, high voltage GaN transistors of both lateral structure and vertical structure are appearing: a 1700V cascode-configured GaN-on-Si HEMT was reported by Transphorm while a 1200V enhancement mode vertical JFET was already developed by Avogy [1-29] [1-44]. With performance of GaN devices be promoted further, various new applications which are beyond the capabilities of Si devices could be enabled. Among many others, wireless power transfer, RF envelope tracking, rad-hard satellite and avionics power supplies are some of the predicted applications that will be initiated by GaN devices. Wireless power transmission and RF envelope tracking systems utilizes a blend of highfrequency operation with high-power and high-voltage capabilities. Power systems for satellite and avionics applications, on the other hand, take advantage of GaN transistors' high frequency, high temperature capabilities as well as the ability to operate in high radiation conditions [1-45].

- For the same blocking voltage and die size

- For the same blocking voltage and on-resistance

Figure 1.4. Trend of high frequency operation with GaN devices

#### 1.2 Problem description

#### Losses in GaN devices and the effects of parasitics on losses

Emerging GaN semiconductors, judging from their wide bandgap material properties, are good candidates to replace Si devices and enable power converter to operate at increased switching frequencies. In theory, GaN devices have much improved FOM (Figure-of-Merit) than Si counterparts, and thus the new devices have the potential of boosting the performances of existing power electronics systems and sparking new applications [1-10] [1-45]. Characteristics of

actual GaN devices, however, are determined by more than just the properties of the material. Issues such as die design and fabrication approach, device packaging technology, the way they are used in circuits etc., also contribute to what GaN transistors can achieve, especially in high switching frequency applications [1-35] [1-46]. Available low voltage GaN transistors come with extremely small die size and package compared to Si MOSEFT with similar electric ratings [1-45]; while newly developed high voltage GaN transistors have comparable die size and package as Si counterparts with the same ratings [1-32] [1-48]. And thus, for the purpose of exploring potentials of GaN devices, it is essential to evaluate and analyze losses in the devices to reveal benefits and limitations of applying them in high frequency power converters.

It is a natural approach to execute loss assessments of GaN transistors in existing power converters where the transistors are used as direct replacement of Si MOSFETs. As GaN devices have high current slew rate (di/dt) during switching transients, high voltage drop across parasitic inductances will occur in a fixed converter setup. And therefore, in addition to the characterization of package parasitics, the electromagnetic environment surrounding the transistors i.e. circuit parasitic elements also have to be defined and specified. In particular, the electromagnetic volume of low voltage GaN transistor is negligible compared to the rest parts of the power converter circuit, the environment has profound influence on switching characteristics and losses of the transistor and must be well accounted for [1-10].

#### Optimal usage of GaN transistors and limitations in high frequency applications

Optimal usage of GaN devices, however, may not be achieved if they are used simply as a dropin replacement of Si devices in existing power converters. The available converter architectures are mostly designed to suit Si devices, and whether full benefits of GaN transistors can be achieved in these concepts are questionable. To fully exploit the potentials of GaN devices for high frequency operations and, more importantly, to find applications in which benefits of GaN devices could be maximized, optimal topologies and operation modes that accommodate GaN transistors best needs to be identified. Moreover, challenges and design trade-offs other than suitable topologies and operation modes also presents in a GaN converter, such as thermal management, voltage stress, etc. Heat removal approach for GaN devices, especially for low voltage GaN HEMTs, could be challenging as the new devices have different packaging technologies, electrical and thermal properties, etc. compared to Si devices. Thermal management approach taken should be an optimal solution, as a trade-off exists between thermal management and high frequency performance in a GaN converter [1-10]. To successfully take advantage of GaN technology, the GaN based power electronics system as a whole needs to be optimized. Besides, limitations of the optimal conditions in which GaN transistors will be applied needs to be clarified to guide proper design and implementation of GaN based applications.

#### 1.3 Thesis objectives

With the purpose of overcoming challenges introduced in Section 1.2, the main goal of this thesis is to *explore potentials of GaN devices for high frequency applications*. Objectives of the thesis, accordingly, can be summarized as:

I. Investigate limitations of GaN devices for high frequency applications

As performance of emerging GaN transistors is unknown, evaluation of their capabilities in certain applications, PFC converters in this work, needs to be carried out. The evaluation should reveal how GaN devices perform in existing systems where they are used directly as replacement of Si devices; whether they can outperform Si counterparts in existing systems; what kind of benefits the new technology brings compared to Si devices in these systems; what are the influences of circuit and package parasitic elements on performance of GaN devices (issues, such as circuit/package parasitic inductances, that hinder realization of fast switching and problems, like device parasitic capacitance, that affects suitable switching conditions); what are the limitations in applying GaN transistors in high frequency operations.

II. Explore topologies and operation modes that accommodate GaN devices and clarify limitations of the topologies and modes for high frequency operations

To fully explore the potentials of GaN devices, optimal topologies and operation modes where benefits of GaN technology can be fully exploited should be identified. The optimal topologies and operation modes, which could be widely-adopted conventional schemes, unpopular existing systems or even new technologies, should overcome or even take advantage of the spotted limitations. For instance, in active PFC solutions, traditionally a boost converter, mainly because of its simplicity, is popular rather than choices like buckboost, Sepic, etc. Whether the boost will remain the preferred solution or one of the alternative circuits will be made more attractive with the advent of GaN devices needs to be verified. Furthermore, new PFC topologies might even be needed when all the existing options fails to well accommodate GaN devices. In addition, new challenges, design trade-offs and limitations that arise when applying GaN devices in the identified topologies and operation modes should be taken care of.

III. Demonstrate benefits of GaN technology in high frequency power conversion applications

Demonstration on benefits of GaN technology in real applications, PFC converter in this thesis, should be conducted. Optimal usage of GaN devices in an application that

embodies both optimal topology and operation mode so as to maximize the benefits of the devices should be carried out as a case study.

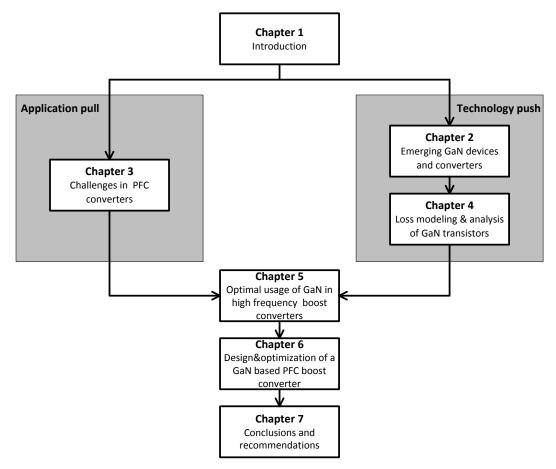

#### 1.4 Thesis layout

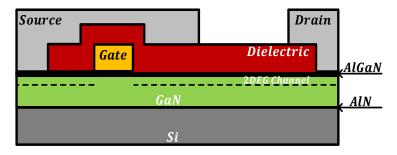

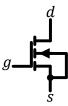

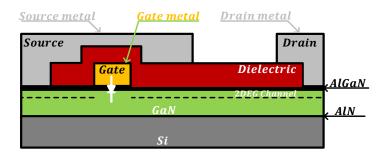

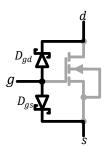

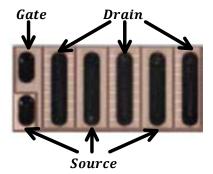

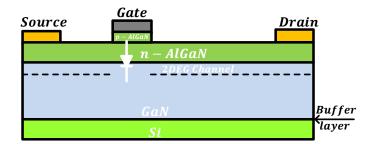

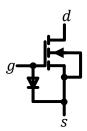

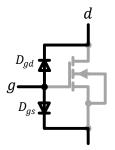

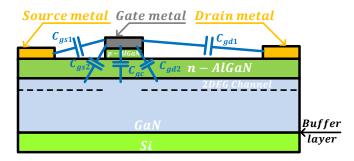

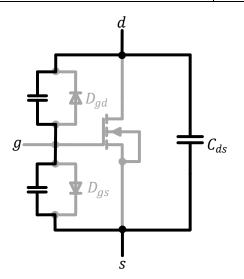

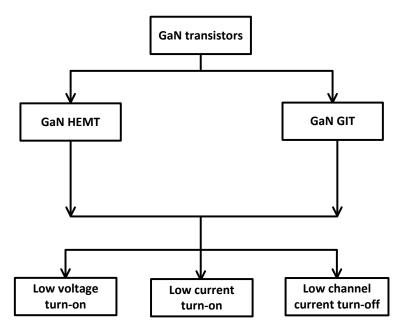

**Chapter 2** presents an overview on GaN devices and converters. Both the evolution of different types of GaN semiconductors and performance of converters employing the newly appeared devices will be reviewed. Special attention will be paid to two different kinds of GaN transistors, low voltage GaN HEMT (High Electron Mobility Transistor) and High voltage GaN GIT (Gate Injection Transistor), and their applications in converters. The goal of this chapter is to demonstrate the potential of GaN technology on development of power electronics from the perspective of technology push.

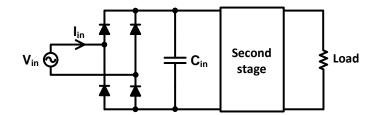

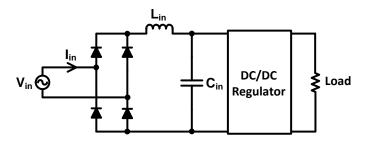

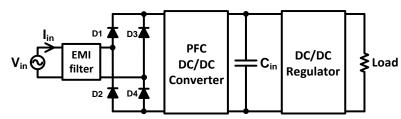

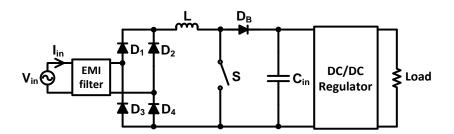

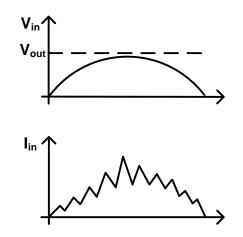

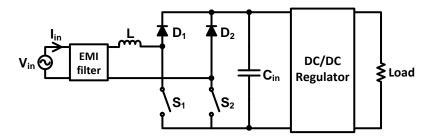

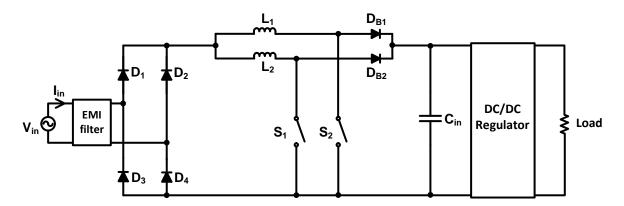

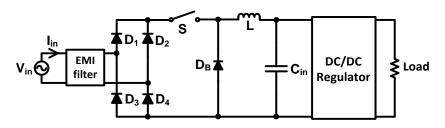

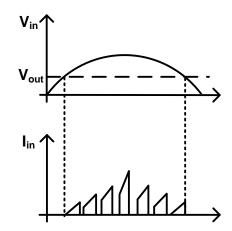

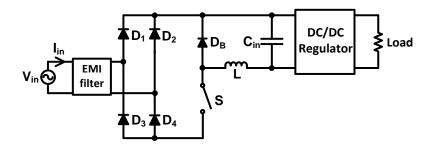

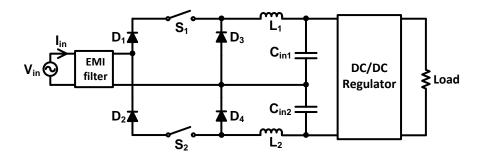

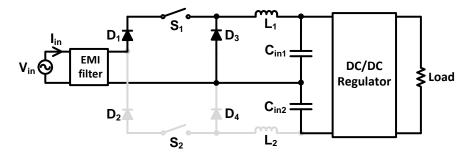

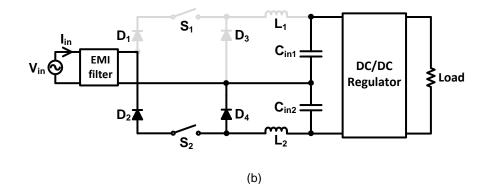

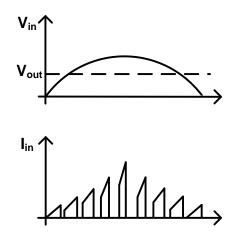

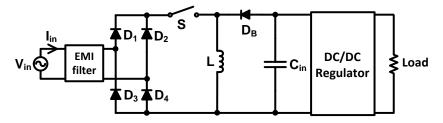

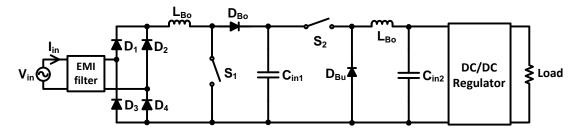

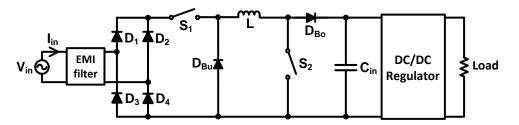

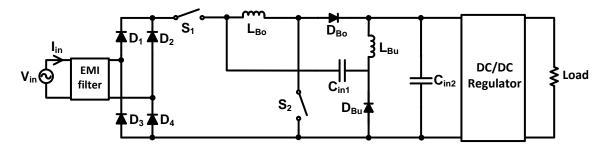

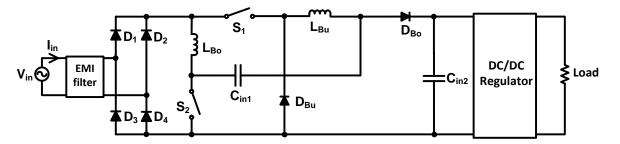

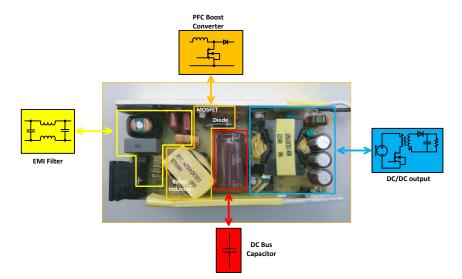

**Chapter 3** covers developments of PFC converters and investigation of preferred topology for pushing up frequency of the PFC stage. The concept of PFC technique and approaches to realize the technique is introduced first. Possible topologies such as boost, buck, buck-boost, etc. to implement PFC are then compared and summarized with both their advantages and disadvantages. An investigation on whether pushing up operation frequency will make one or more topologies better options for PFC than traditionally used boost converter i.e. whether GaN devices could combat the disadvantages while retaining or even enhancing their advantages of these topologies is carried out afterwards. After the confirmation that boost converter will remain as a preferred choice for implementing high frequency PFC, it is chosen as the platform for evaluating and demonstrating potentials and benefits of GaN devices. The purpose of this chapter is to illustrate application pull of current and future power electronics systems using PFC converters as an example.

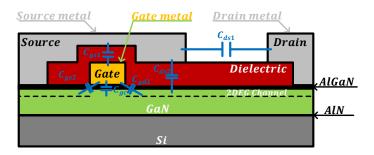

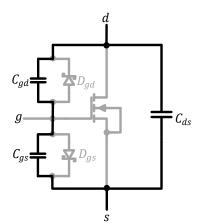

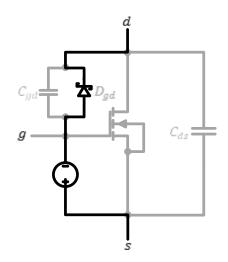

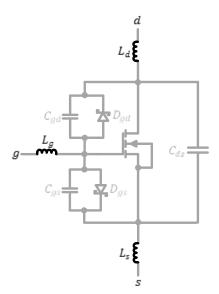

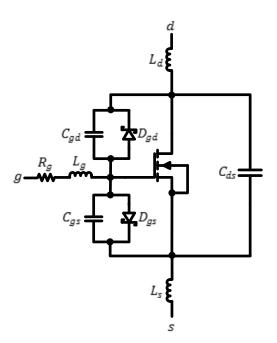

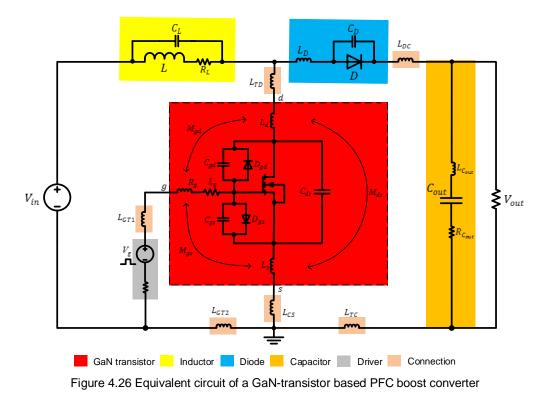

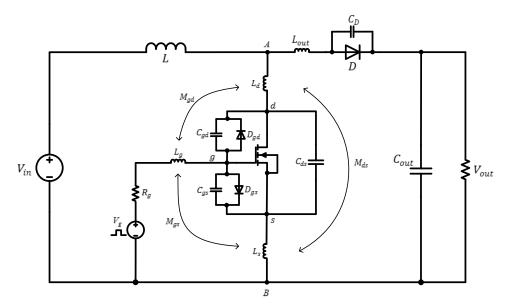

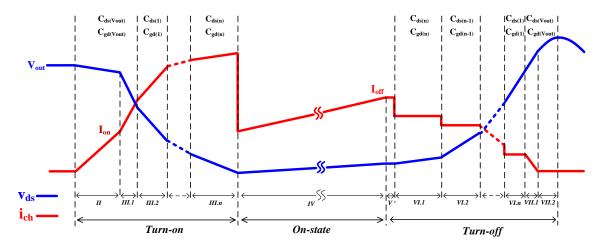

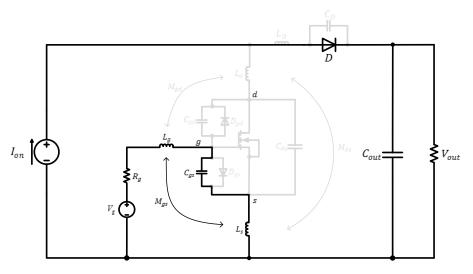

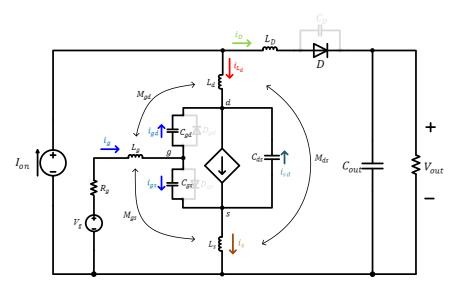

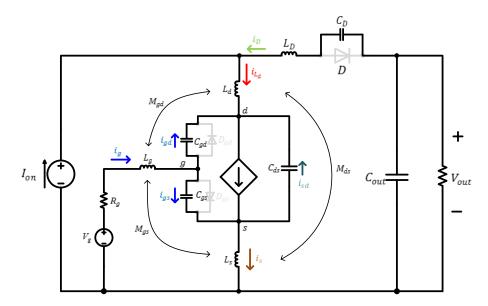

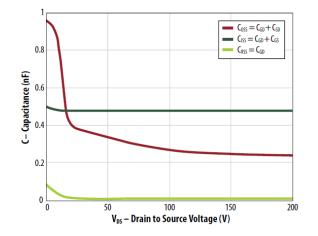

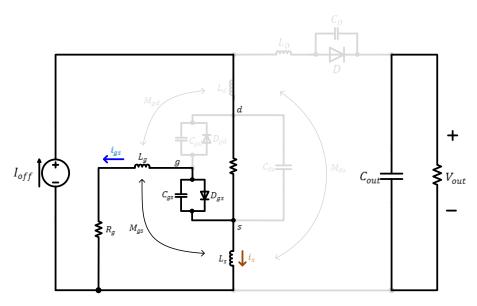

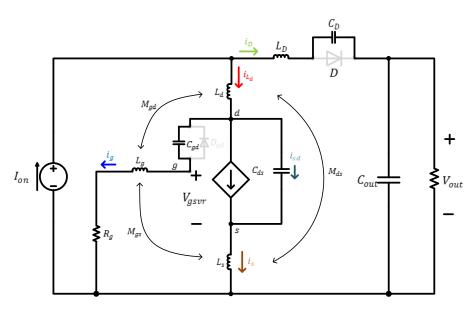

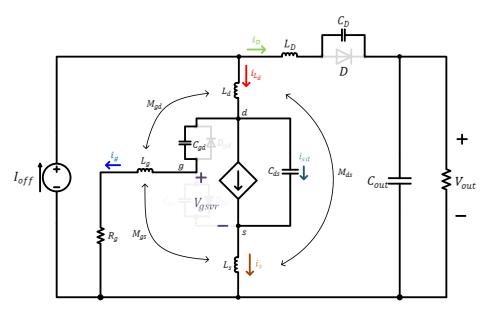

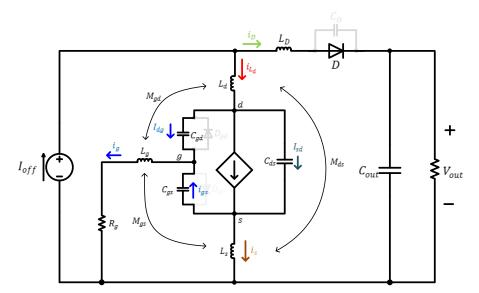

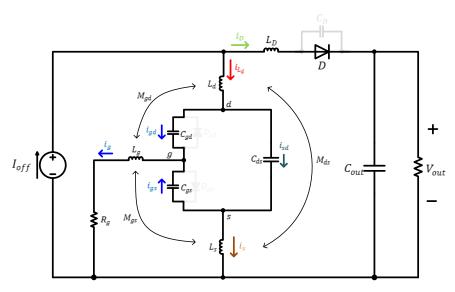

**Chapter 4** performs loss modeling and analysis of GaN devices in a high frequency boost converter. With the assistance of a generalized equivalent circuit which is derived based on their physical structures and basic operation principles of low voltage GaN HEMT and high voltage GIT, analytical loss model of GaN devices that accounts for influences of circuit and package parasitics, is developed. The model is employed to analyze losses in both GaN HEMT and GaN GIT and to disclose the critical parasitic elements in a GaN boost converter in CCM (Continuous Conduction Mode). The goal of this chapter is to uncover the benefits and limitations of GaN devices in high frequency operation when the devices are simply used as a drop-in replacement of Si device in existing power electronics systems, using hard-switched boost converter as a platform.

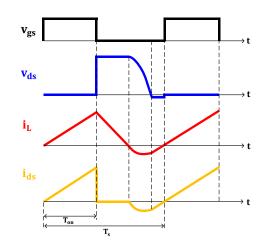

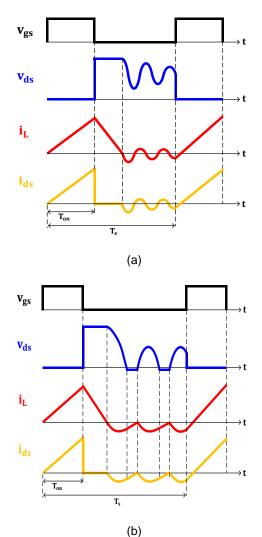

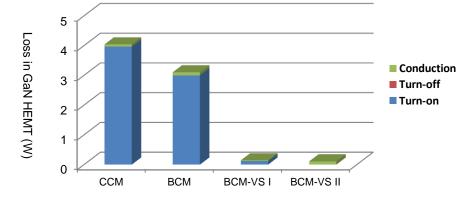

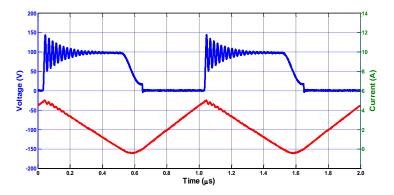

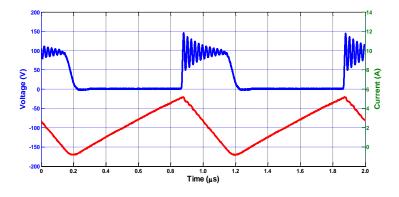

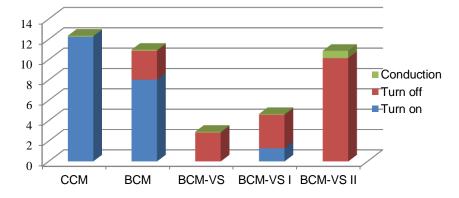

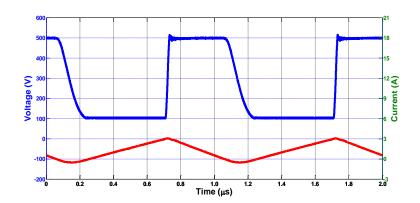

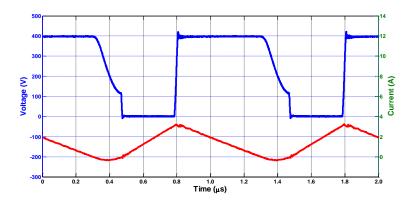

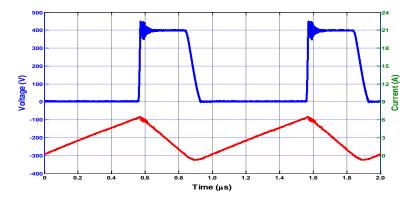

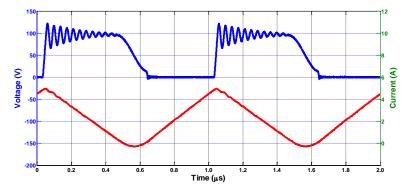

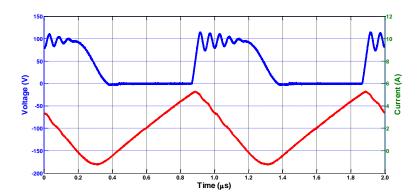

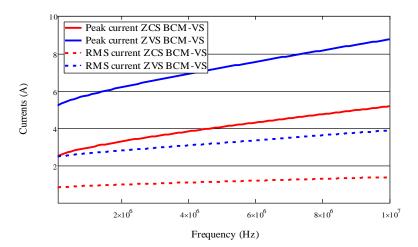

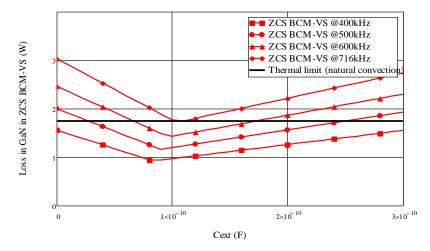

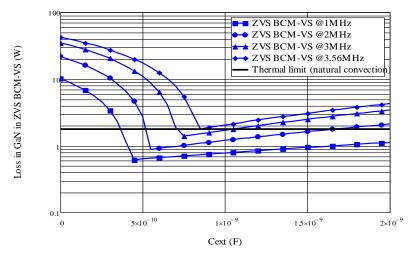

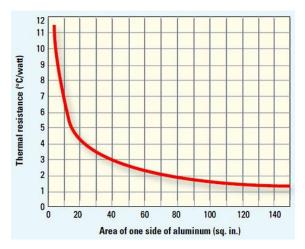

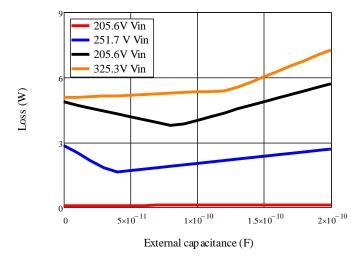

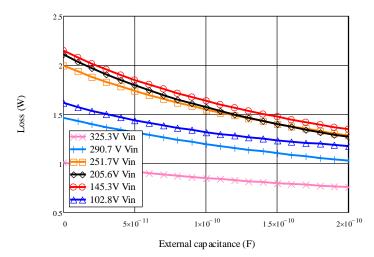

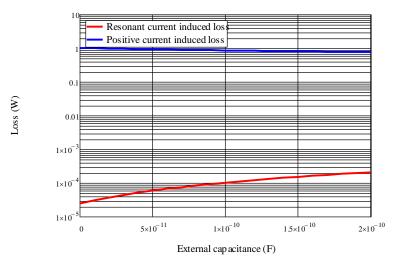

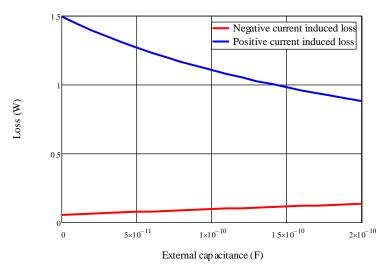

**Chapter 5** explores optimal operation modes and the limitations of the modes in a PFC converter that can suit GaN device best so that full advantage of GaN can be taken of. Losses in GaN transistors in CCM are analyzed firstly through the help of loss model developed in chapter 4 to