#### Pitch-Matched Integrated Transceiver Circuits for High-Resolution 3-D Neonatal Brain Monitoring

Guo, P.

DOI

10.4233/uuid:a356d348-add2-4995-9392-1b16daa8dbfa

**Publication date**

**Document Version**

Final published version

Citation (APA)

Guo, P. (2023). *Pitch-Matched Integrated Transceiver Circuits for High-Resolution 3-D Neonatal Brain Monitoring*. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:a356d348-add2-4995-9392-1b16daa8dbfa

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# PITCH-MATCHED INTEGRATED TRANSCEIVER CIRCUITS FOR HIGH-RESOLUTION 3-D NEONATAL BRAIN MONITORING

# PITCH-MATCHED INTEGRATED TRANSCEIVER CIRCUITS FOR HIGH-RESOLUTION 3-D NEONATAL BRAIN MONITORING

#### Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus, prof. dr. ir. T.H.J.J. van der Hagen chair of the Board for Doctorates to be defended publicly on Wednesday 27 September 2023 at 12:30 o'clock

by

#### **Peng GUO**

Master of Science in Electronics Science and Technology, Zhejiang University, China born in Huzhou, China This dissertation has been approved by the promotors.

#### Composition of the doctoral committee:

Rector Magnificus, chairperson

Dr. ir. M. A. P. Pertijs Delft University of Technology, promotor

Prof. dr. ir. N. de Jong Delft University of Technology, promotor

Independent members:

Prof. dr. P. Tortoli University of Florence, Italy

Prof. dr. K. A. A. Makinwa Delft University of Technology

Prof. dr. L. C. N. de Vreede Delft University of Technology

Dr. ir. P. J. A. Harpe Eindhoven University of Technology, The Netherlands

Dr. ir. H. J. Vos Erasmus University Medical Center, The Netherlands

Prof. dr. P. French Delft University of Technology, reserve member

This research is part of the project MIFFY with project number 15293 of the Open Technology Programme, which is financed by the Dutch Research Council (NWO).

ISBN: 978-94-6469-514-4

Copyright © 2023 by Peng GUO

All rights reserved. No part of this publication may be reproduced, or distributed in any form or by any other means, or stored in a database or retrieval system, without the prior written permission of the author.

Printed by Proefschrift Maken | www.proefschriftmaken.nl

To my parents and my family (MinWen, QingYan)

### **CONTENTS**

| 1 | Intr | oduction                                                                   | 1  |  |  |  |

|---|------|----------------------------------------------------------------------------|----|--|--|--|

|   | 1.1  | Motivation                                                                 | 1  |  |  |  |

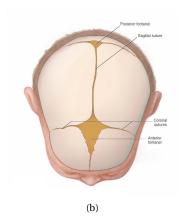

|   | 1.2  | Transfontenelle Ultrasonography Overview                                   | 2  |  |  |  |

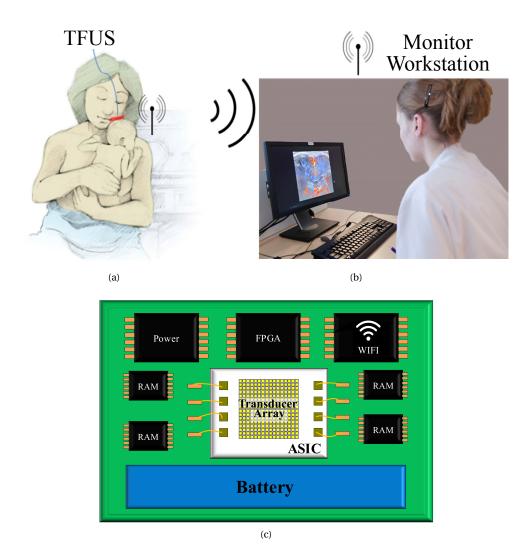

|   | 1.3  | Wearable TFUS Device                                                       | 3  |  |  |  |

|   | 1.4  | Design Challenges                                                          | 3  |  |  |  |

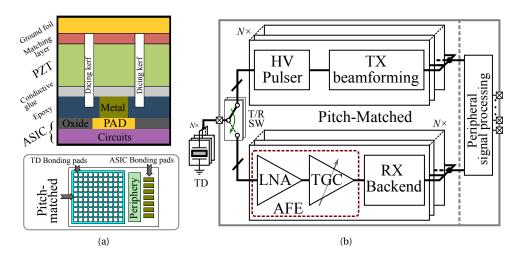

|   |      | 1.4.1 3-D TFUS Design Requirements                                         | 3  |  |  |  |

|   |      | 1.4.2 Transducer-ASIC Process Integration                                  | 5  |  |  |  |

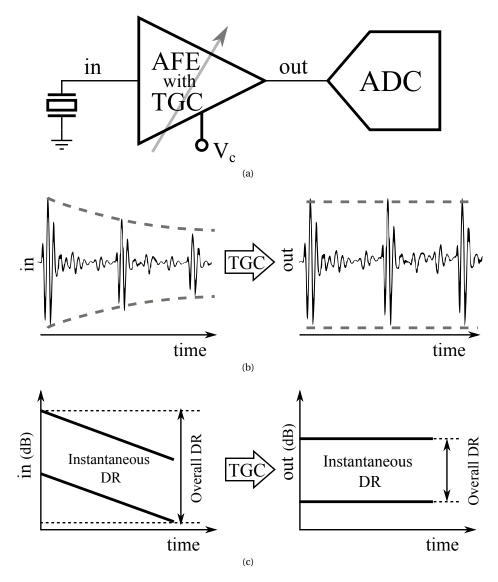

|   |      | 1.4.3 Transceiver ASIC Design Considerations                               | 7  |  |  |  |

|   |      | 1.4.4 Conclusion                                                           | 8  |  |  |  |

|   | 1.5  | Thesis Organization                                                        | 9  |  |  |  |

| 2 | A Pi | itch-Matched Low-Noise AFE With Accurate TGC for High-Density Ultrasound   |    |  |  |  |

|   |      |                                                                            | 17 |  |  |  |

|   | 2.1  | Introduction                                                               | 17 |  |  |  |

|   |      |                                                                            | 19 |  |  |  |

|   | 2.3  | Architecture design                                                        | 21 |  |  |  |

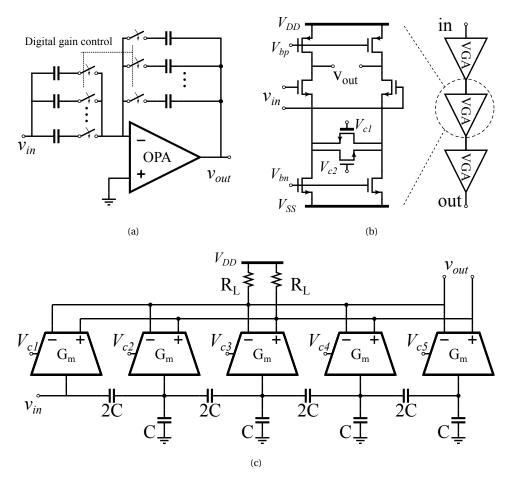

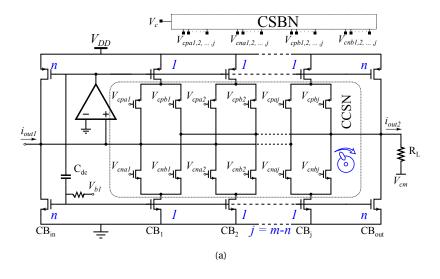

|   |      | 2.3.1 Two-Stage Interpolating VGA                                          | 21 |  |  |  |

|   |      |                                                                            | 22 |  |  |  |

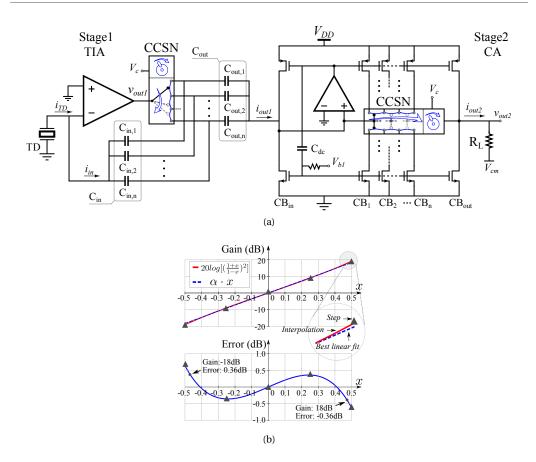

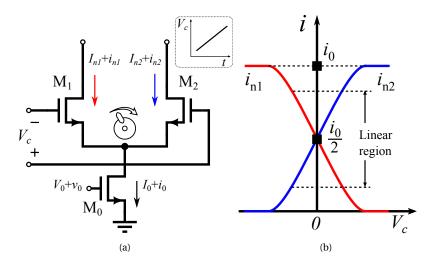

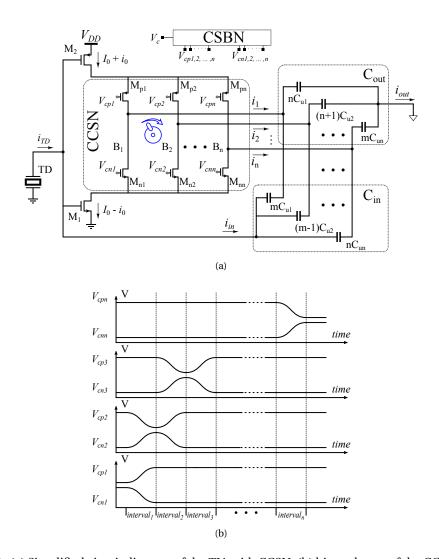

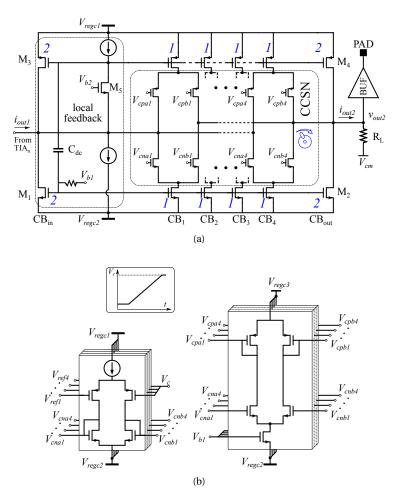

|   |      | 2.3.3 Transimpedance Amplifier with Complementary Current-Steering Network | 23 |  |  |  |

|   |      | 2.3.4 Current Amplifier with Complementary Current-Steering Network        | 25 |  |  |  |

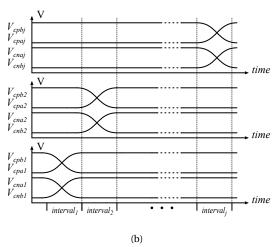

|   | 2.4  | Circuit design                                                             | 26 |  |  |  |

|   |      | 2.4.1 Hardware Sharing TIA                                                 | 26 |  |  |  |

|   |      | 2.4.2 Bandwidth-Control Circuit                                            | 28 |  |  |  |

|   |      | 2.4.3 Class-AB Current Amplifier                                           | 29 |  |  |  |

|   |      | 2.4.4 Noise Analysis                                                       | 30 |  |  |  |

|   | 2.5  | Experimental results                                                       | 31 |  |  |  |

|   |      | J 1                                                                        | 31 |  |  |  |

|   |      |                                                                            | 31 |  |  |  |

|   |      |                                                                            | 35 |  |  |  |

|   | 2.6  | Conclusion                                                                 | 37 |  |  |  |

| 3 | A    | 1.2mW/Channel Pitch-Matched Transceiver ASIC Employing a                   |    |  |  |  |

|   | Box  | ccar-Integration-Based RX Micro-Beamformer for High-Resolution 3-D         |    |  |  |  |

|   | Ultr | Ultrasound Imaging                                                         |    |  |  |  |

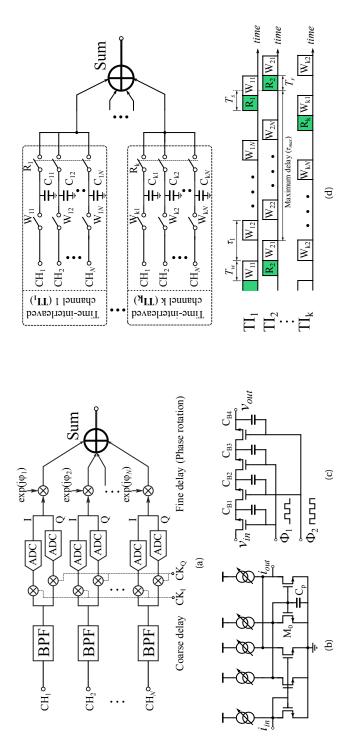

|   | 3.1  |                                                                            | 45 |  |  |  |

|   | 3.2  |                                                                            | 48 |  |  |  |

|   | 3.3  | 8                                                                          | 50 |  |  |  |

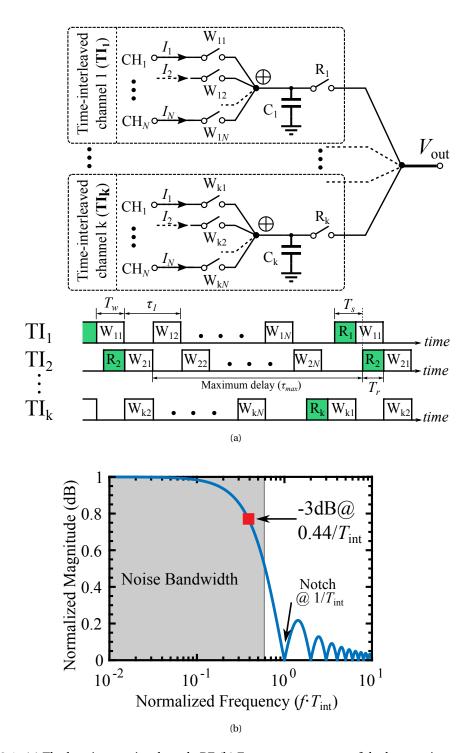

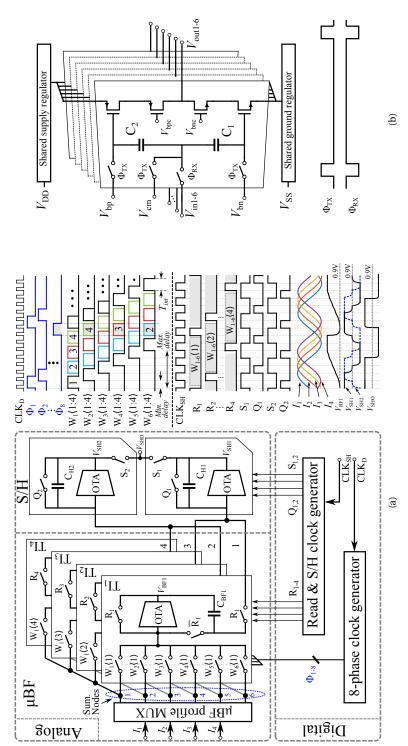

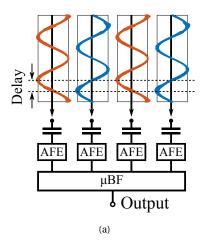

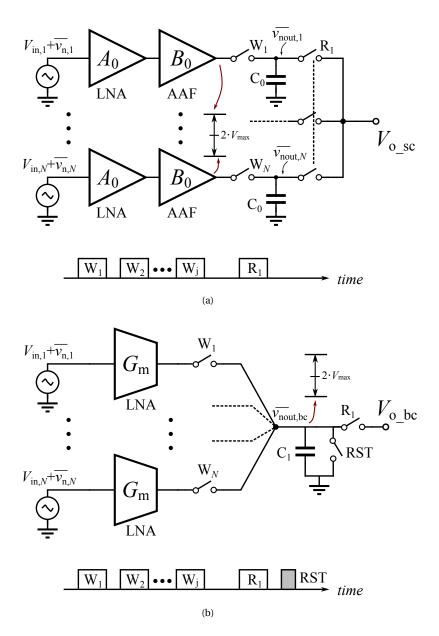

|   |      | 3.3.1 Boxcar-integration-based micro-beamformer                            | 50 |  |  |  |

|   |      | 3.3.2 System overview                                                      | 52 |  |  |  |

VIII CONTENTS

| 3.4.2 Micro-beamformer       54         3.4.3 Output Buffer       57         3.4.4 Transmitter       57         3.5 Experimental results       58         3.5.1 ASIC Prototype       58         3.5.2 Electrical Characterization       59         3.5.3 Acoustical Characterization       62         3.6 Conclusion       63         4 A 125μm-Pitch-Matched Transceiver ASIC with Micro-Beamforming ADC and Multi-Level Signaling for 3-D Transfontanelle Ultrasonography       73         4.1 Introduction       73         4.2 Architecture Design       76         4.2.1 System Overview       76         4.2.2 AFE       76         4.2.3 Passive boxcar-integration-based μBF ADC       78         4.2.4 Data Transmitter (D-TX)       80         4.2.5 TX Architecture       82         4.3 Circuit Design       82         4.3.1 Passive Amplification of the μBF ADC       82         4.3.2 Dynamic Comparator of the SAR ADC       83         4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 3.4 | Circuit design                                                    | 54  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-------------------------------------------------------------------|-----|

| 3.4.3 Output Buffer 3.4.4 Transmitter 3.4.1 Transmitter 3.5 Experimental results 3.5.1 ASIC Prototype 58 3.5.2 Electrical Characterization 59 3.5.3 Acoustical Characterization 62 3.6 Conclusion 63  4 A 125μm-Pitch-Matched Transceiver ASIC with Micro-Beamforming ADC and Multi-Level Signaling for 3-D Transfontanelle Ultrasonography 73 4.1 Introduction 73 4.2 Architecture Design 76 4.2.1 System Overview 76 4.2.2 AFE 76 4.2.3 Passive boxcar-integration-based μBF ADC 78 4.2.4 Data Transmitter (D-TX) 78 4.2 Circuit Design 79 4.3.1 Passive Amplification of the μBF ADC 78 4.3.2 Dynamic Comparator of the SAR ADC 78 4.3.3 Charge-mode Reference Generation 78 4.3.4 Input Common-mode Feedback 78 4.3.5 PAM-16 DAC 78 78 79 79 70 70 71 71 71 71 71 72 72 73 73 74 75 75 75 76 76 77 78 78 79 79 70 70 70 71 71 71 71 75 75 75 76 76 77 78 77 78 78 79 79 70 70 70 71 71 70 70 71 71 70 70 71 71 70 70 71 71 70 70 71 71 71 70 70 71 71 71 71 71 71 71 71 71 71 71 71 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |     | 3.4.1 Analog front-end                                            | 54  |

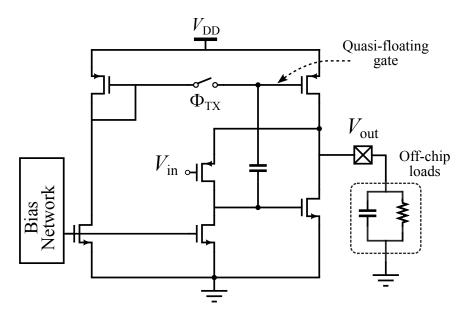

| 3.4.4 Transmitter 57 3.5 Experimental results 58 3.5.1 ASIC Prototype 58 3.5.2 Electrical Characterization 59 3.5.3 Acoustical Characterization 62 3.6 Conclusion 63  4 A 125μm-Pitch-Matched Transceiver ASIC with Micro-Beamforming ADC and Multi-Level Signaling for 3-D Transfontanelle Ultrasonography 73 4.1 Introduction 73 4.2 Architecture Design 76 4.2.1 System Overview 76 4.2.2 AFE 76 4.2.3 Passive boxcar-integration-based μBF ADC 78 4.2.4 Data Transmitter (D-TX) 80 4.2.5 TX Architecture 82 4.3.1 Passive Amplification of the μBF ADC 82 4.3.2 Dynamic Comparator of the SAR ADC 83 4.3.3 Charge-mode Reference Generation 84 4.3.4 Input Common-mode Feedback 86 4.3.5 PAM-16 DAC 87 4.3.6 HV Pulser 88 4.4 Experimental results 88 4.4.1 ASIC Prototype 88 4.4.2 Electrical Characterization 90 4.4.3 RX μBF Characterization 90 4.4.4 Ultrasound B-mode Imaging 95 4.5 Conclusion 97 5 Conclusion 97 5 Conclusion 97 5 Conclusion 97 5 Conclusion 107 5.1 Main Contributions 107 5.2 Original Findings 108 5.3 Future Work 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |     | 3.4.2 Micro-beamformer                                            | 54  |

| 3.5 Experimental results 3.5.1 ASIC Prototype 3.5.2 Electrical Characterization 3.5.3 Acoustical Characterization 3.6 Conclusion 63  4 A 125μm-Pitch-Matched Transceiver ASIC with Micro-Beamforming ADC and Multi-Level Signaling for 3-D Transfontanelle Ultrasonography 73 4.1 Introduction 73 4.2 Architecture Design 76 4.2.1 System Overview 76 4.2.2 AFE 76 4.2.3 Passive boxcar-integration-based μBF ADC 78 4.2.4 Data Transmitter (D-TX) 80 4.2.5 TX Architecture 82 4.3 Circuit Design 82 4.3.1 Passive Amplification of the μBF ADC 83 4.3.2 Dynamic Comparator of the SAR ADC 83 4.3.3 Charge-mode Reference Generation 84 4.3.4 Input Common-mode Feedback 86 4.3.5 PAM-16 DAC 87 4.6 HV Pulser 88 4.7 Experimental results 88 4.8 Experimental results 88 4.9 Experimental results 89 4.1 ASIC Prototype 89 4.1 ASIC Prototype 80 4.2 Electrical Characterization 90 4.3 Ranch All Plans All |   |     | 3.4.3 Output Buffer                                               | 57  |

| 3.5.1 ASIC Prototype 3.5.2 Electrical Characterization 3.5.3 Acoustical Characterization 3.5.3 Acoustical Characterization 3.6 Conclusion 4 A 125μm-Pitch-Matched Transceiver ASIC with Micro-Beamforming ADC and Multi-Level Signaling for 3-D Transfontanelle Ultrasonography 4.1 Introduction 4.2 Architecture Design 4.2.1 System Overview 4.2.2 AFE 4.2.3 Passive boxcar-integration-based μBF ADC 4.2.4 Data Transmitter (D-TX) 80 4.2.5 TX Architecture 82 4.3.1 Passive Amplification of the μBF ADC 83 4.3.2 Dynamic Comparator of the SAR ADC 83 4.3.3 Charge-mode Reference Generation 84 4.3.4 Input Common-mode Feedback 86 4.3.5 PAM-16 DAC 87 4.3.6 HV Pulser 88 4.4 Experimental results 88 4.4 Experimental results 88 4.4.1 ASIC Prototype 4.4.2 Electrical Characterization 90 4.4.3 RX μBF Characterization 91 4.4.4 Ultrasound B-mode Imaging 95 4.5 Conclusion 97 5 Conclusion 97 5 Conclusion 107 5.1 Main Contributions 107 5.2 Original Findings 108 5.3 Future Work 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |     | 3.4.4 Transmitter                                                 | 57  |

| 3.5.1 ASIC Prototype 3.5.2 Electrical Characterization 3.5.3 Acoustical Characterization 3.5.3 Acoustical Characterization 3.6 Conclusion 4 A 125μm-Pitch-Matched Transceiver ASIC with Micro-Beamforming ADC and Multi-Level Signaling for 3-D Transfontanelle Ultrasonography 4.1 Introduction 4.2 Architecture Design 4.2.1 System Overview 4.2.2 AFE 4.2.3 Passive boxcar-integration-based μBF ADC 4.2.4 Data Transmitter (D-TX) 80 4.2.5 TX Architecture 82 4.3.1 Passive Amplification of the μBF ADC 83 4.3.2 Dynamic Comparator of the SAR ADC 83 4.3.3 Charge-mode Reference Generation 84 4.3.4 Input Common-mode Feedback 86 4.3.5 PAM-16 DAC 87 4.3.6 HV Pulser 88 4.4 Experimental results 88 4.4 Experimental results 88 4.4.1 ASIC Prototype 4.4.2 Electrical Characterization 90 4.4.3 RX μBF Characterization 91 4.4.4 Ultrasound B-mode Imaging 95 4.5 Conclusion 97 5 Conclusion 97 5 Conclusion 107 5.1 Main Contributions 107 5.2 Original Findings 108 5.3 Future Work 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 3.5 |                                                                   | 58  |

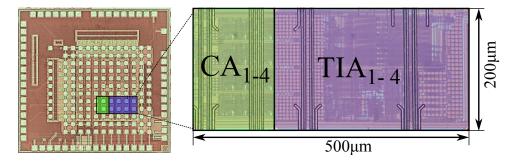

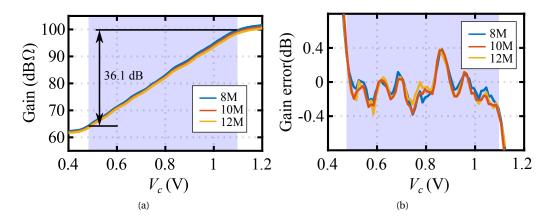

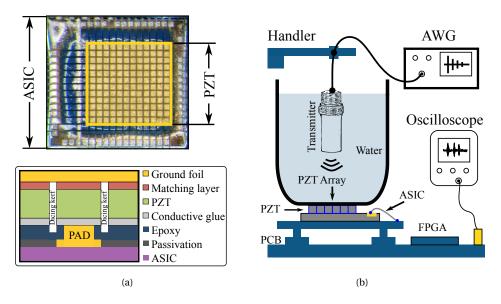

| 3.5.2 Electrical Characterization 59 3.5.3 Acoustical Characterization 62 3.6 Conclusion 63  4 A 125μm-Pitch-Matched Transceiver ASIC with Micro-Beamforming ADC and Multi-Level Signaling for 3-D Transfontanelle Ultrasonography 73 4.1 Introduction 73 4.2 Architecture Design 76 4.2.1 System Overview 76 4.2.2 AFE 76 4.2.3 Passive boxcar-integration-based μBF ADC 78 4.2.4 Data Transmitter (D-TX) 80 4.2.5 TX Architecture 82 4.3 Circuit Design 82 4.3.1 Passive Amplification of the μBF ADC 82 4.3.2 Dynamic Comparator of the SAR ADC 82 4.3.3 Charge-mode Reference Generation 84 4.3.4 Input Common-mode Feedback 86 4.3.5 PAM-16 DAC 87 4.3.6 HV Pulser 88 4.4 Experimental results 88 4.4.1 ASIC Prototype 88 4.4.2 Electrical Characterization 90 4.4.3 RX μBF Characterization 90 4.4.4 Ultrasound B-mode Imaging 95 4.5 Conclusion 97 5 Conclusion 107 5.1 Main Contributions 107 5.2 Original Findings 108 5.3 Future Work 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |     | 3.5.1 ASIC Prototype                                              | 58  |

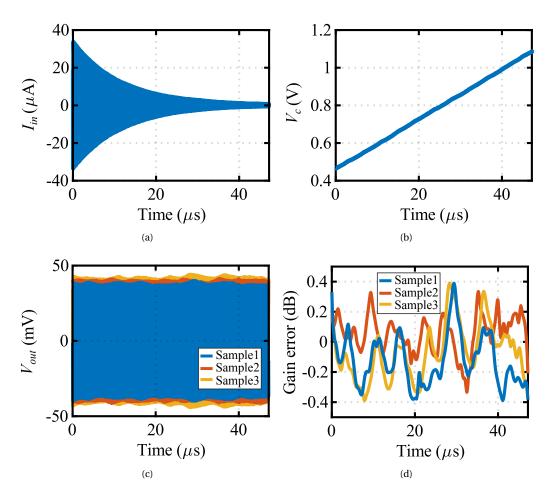

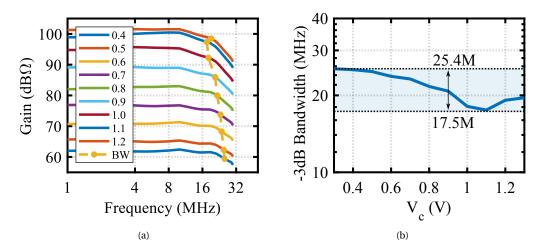

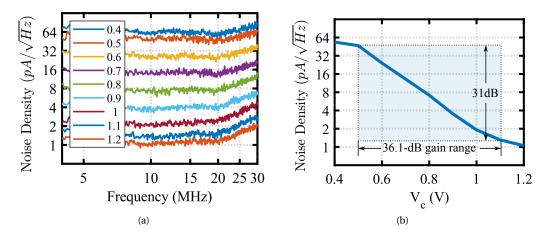

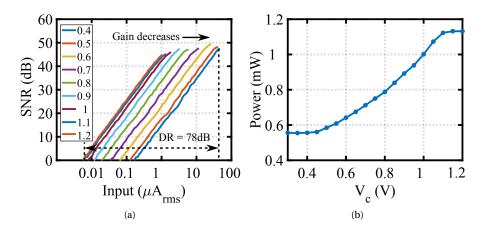

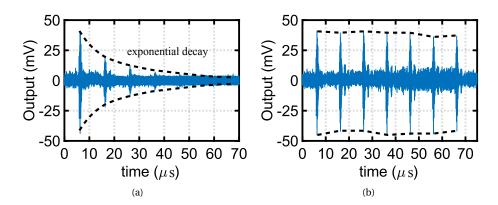

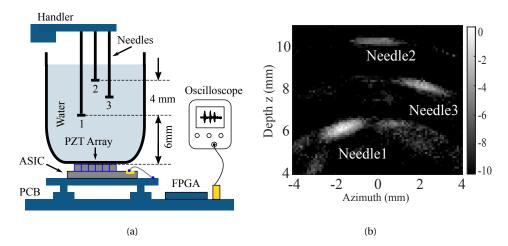

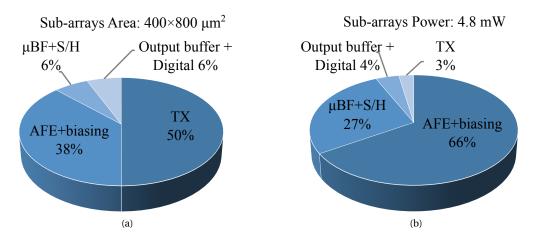

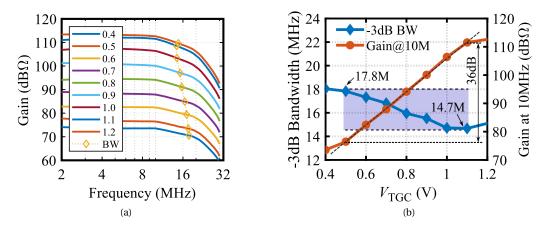

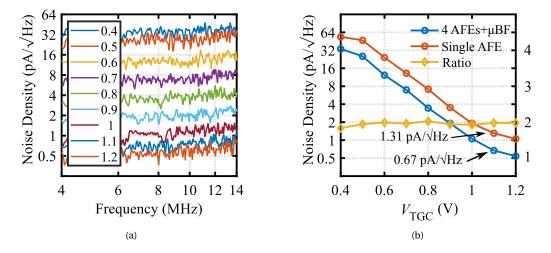

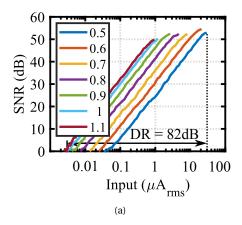

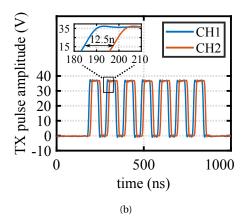

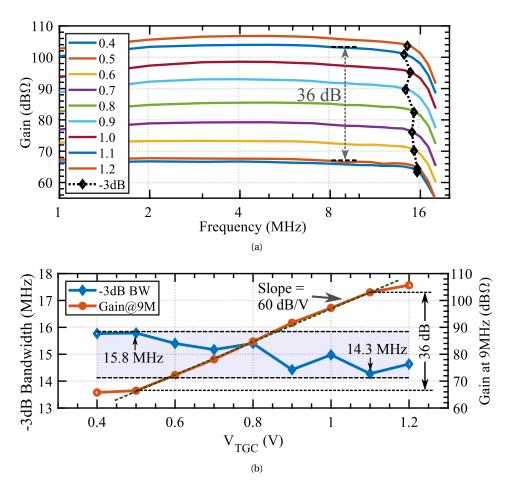

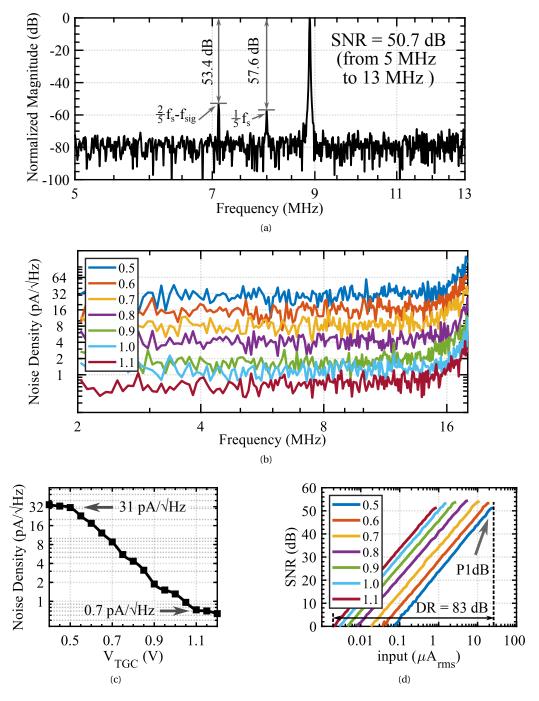

| 3.6 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |     | * *                                                               | 59  |

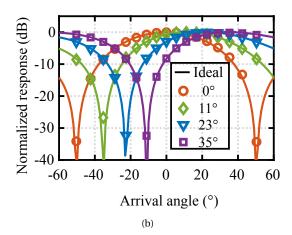

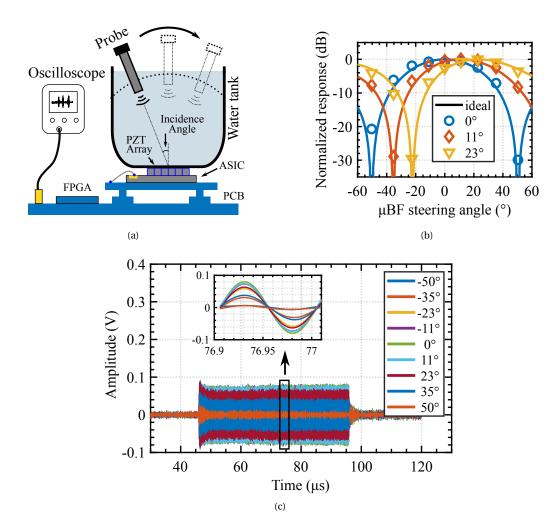

| 3.6 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |     | 3.5.3 Acoustical Characterization                                 | 62  |

| Multi-Level Signaling for 3-D Transfontanelle Ultrasonography       73         4.1 Introduction       73         4.2 Architecture Design       76         4.2.1 System Overview       76         4.2.2 AFE       76         4.2.3 Passive boxcar-integration-based μBF ADC       78         4.2.4 Data Transmitter (D-TX)       80         4.2.5 TX Architecture       82         4.3 Circuit Design       82         4.3.1 Passive Amplification of the μBF ADC       82         4.3.2 Dynamic Comparator of the SAR ADC       83         4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121    <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 3.6 |                                                                   | 63  |

| Multi-Level Signaling for 3-D Transfontanelle Ultrasonography       73         4.1 Introduction       73         4.2 Architecture Design       76         4.2.1 System Overview       76         4.2.2 AFE       76         4.2.3 Passive boxcar-integration-based μBF ADC       78         4.2.4 Data Transmitter (D-TX)       80         4.2.5 TX Architecture       82         4.3 Circuit Design       82         4.3.1 Passive Amplification of the μBF ADC       82         4.3.2 Dynamic Comparator of the SAR ADC       83         4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121    <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4 | A 1 | 5um-Pitch-Matched Transceiver ASIC with Micro-Beamforming ADC and |     |

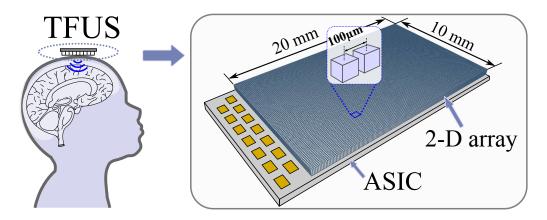

| 4.1 Introduction       73         4.2 Architecture Design       76         4.2.1 System Overview       76         4.2.2 AFE       76         4.2.3 Passive boxcar-integration-based μBF ADC       78         4.2.4 Data Transmitter (D-TX)       80         4.2.5 TX Architecture       82         4.3 Circuit Design       82         4.3.1 Passive Amplification of the μBF ADC       82         4.3.2 Dynamic Comparator of the SAR ADC       83         4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       90         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |     |                                                                   | 73  |

| 4.2 Architecture Design       76         4.2.1 System Overview       76         4.2.2 AFE       76         4.2.3 Passive boxcar-integration-based μBF ADC       78         4.2.4 Data Transmitter (D-TX)       80         4.2.5 TX Architecture       82         4.3 Circuit Design       82         4.3.1 Passive Amplification of the μBF ADC       82         4.3.2 Dynamic Comparator of the SAR ADC       83         4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |     |                                                                   | 73  |

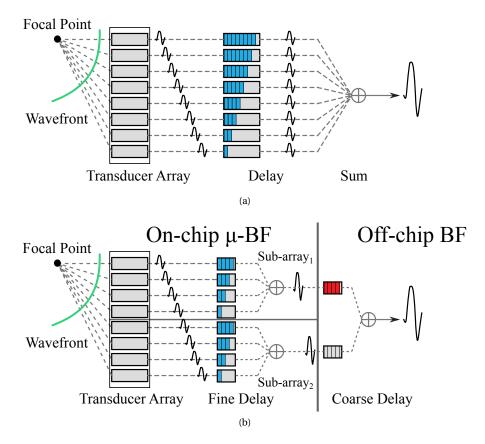

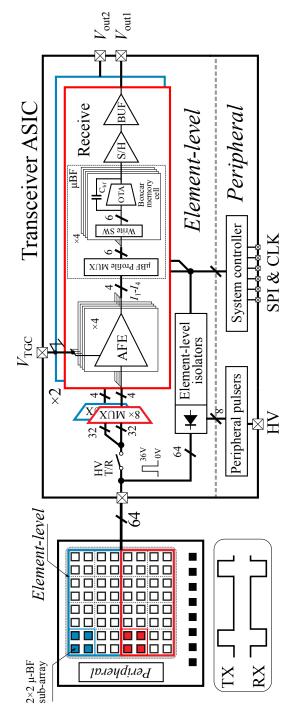

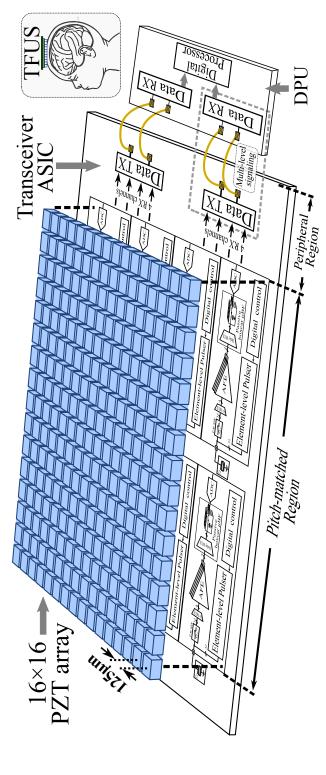

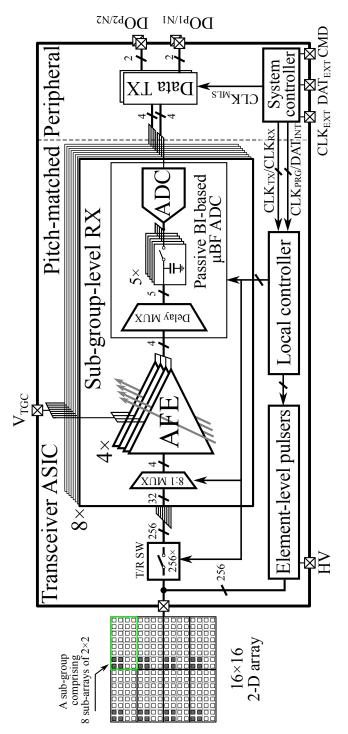

| 4.2.1 System Overview       76         4.2.2 AFE       76         4.2.3 Passive boxcar-integration-based μBF ADC       78         4.2.4 Data Transmitter (D-TX)       80         4.2.5 TX Architecture       82         4.3 Circuit Design       82         4.3.1 Passive Amplification of the μBF ADC       82         4.3.2 Dynamic Comparator of the SAR ADC       83         4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |     |                                                                   | 76  |

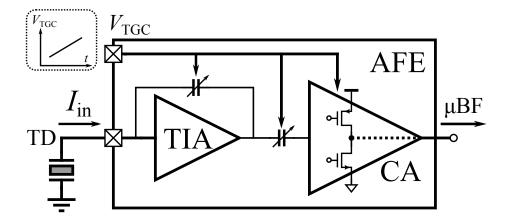

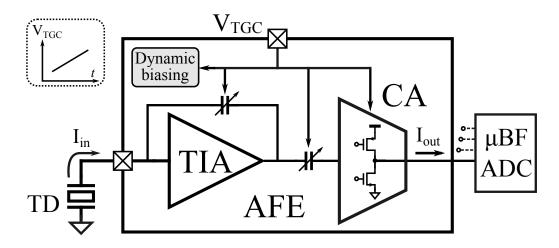

| 4.2.2 AFE       76         4.2.3 Passive boxcar-integration-based μBF ADC       78         4.2.4 Data Transmitter (D-TX)       80         4.2.5 TX Architecture       82         4.3 Circuit Design       82         4.3.1 Passive Amplification of the μBF ADC       82         4.3.2 Dynamic Comparator of the SAR ADC       83         4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |     |                                                                   | 76  |

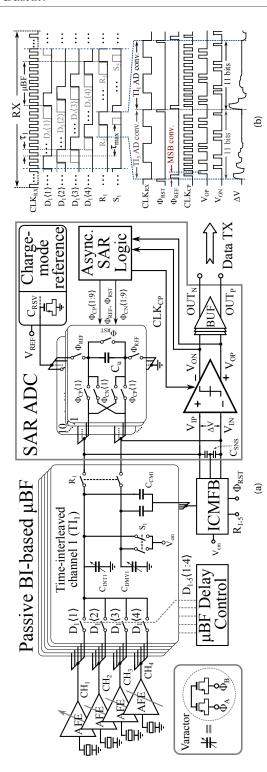

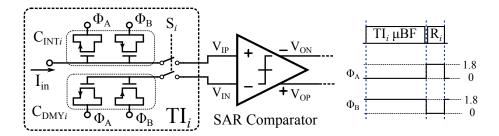

| 4.2.3 Passive boxcar-integration-based μBF ADC       78         4.2.4 Data Transmitter (D-TX)       80         4.2.5 TX Architecture       82         4.3 Circuit Design       82         4.3.1 Passive Amplification of the μBF ADC       82         4.3.2 Dynamic Comparator of the SAR ADC       83         4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |     |                                                                   | 76  |

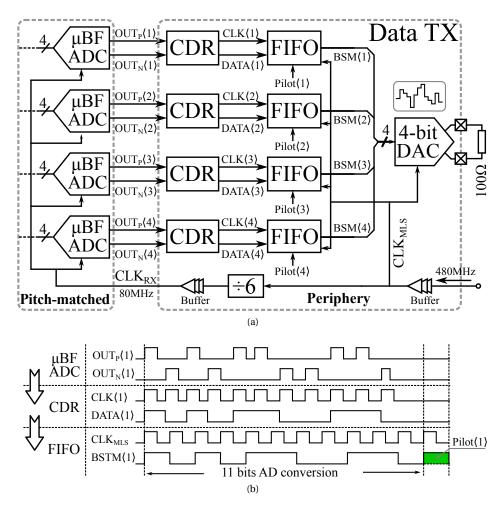

| 4.2.4 Data Transmitter (D-TX)       80         4.2.5 TX Architecture       82         4.3 Circuit Design       82         4.3.1 Passive Amplification of the μBF ADC       82         4.3.2 Dynamic Comparator of the SAR ADC       83         4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |     |                                                                   | 78  |

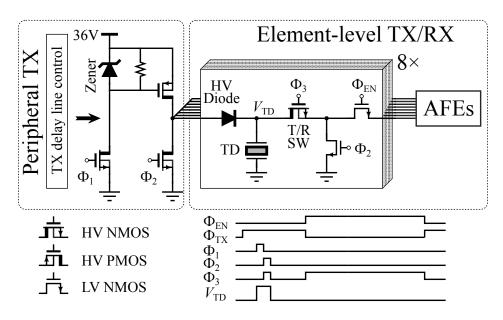

| 4.2.5 TX Architecture       82         4.3 Circuit Design       82         4.3.1 Passive Amplification of the μBF ADC       82         4.3.2 Dynamic Comparator of the SAR ADC       83         4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |     | ě ,                                                               | 80  |

| 4.3 Circuit Design       82         4.3.1 Passive Amplification of the μBF ADC       82         4.3.2 Dynamic Comparator of the SAR ADC       83         4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |     |                                                                   | 82  |

| 4.3.1 Passive Amplification of the μBF ADC       82         4.3.2 Dynamic Comparator of the SAR ADC       83         4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 4.3 |                                                                   | 82  |

| 4.3.2 Dynamic Comparator of the SAR ADC       83         4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |     |                                                                   | 82  |

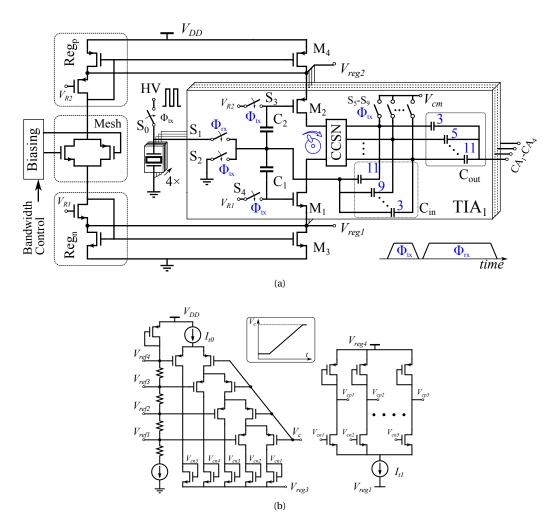

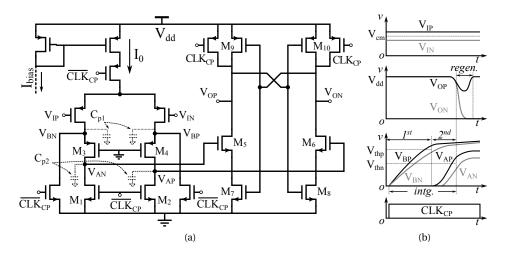

| 4.3.3 Charge-mode Reference Generation       84         4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |     |                                                                   | 83  |

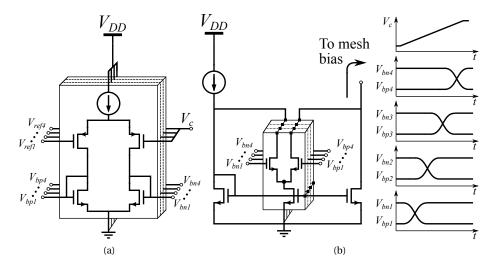

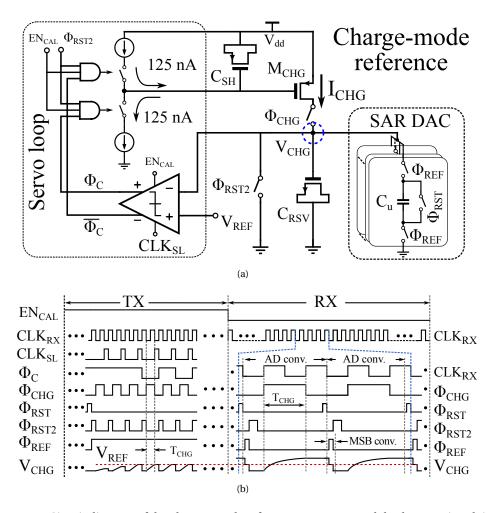

| 4.3.4 Input Common-mode Feedback       86         4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |     |                                                                   | 84  |

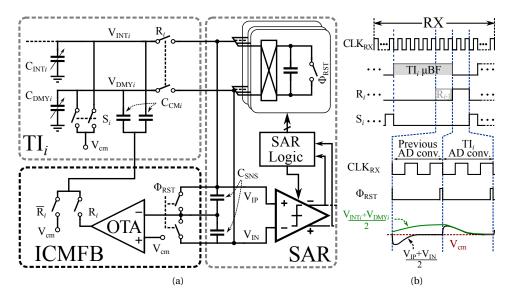

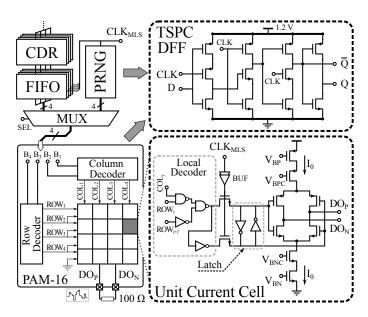

| 4.3.5 PAM-16 DAC       87         4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |     |                                                                   | 86  |

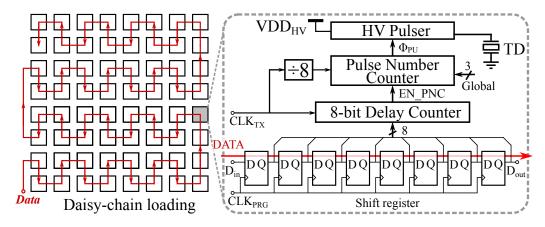

| 4.3.6 HV Pulser       88         4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |     | *                                                                 | 87  |

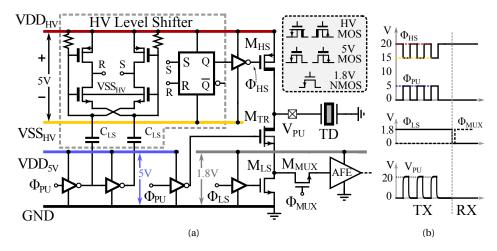

| 4.4 Experimental results       88         4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |     |                                                                   | 88  |

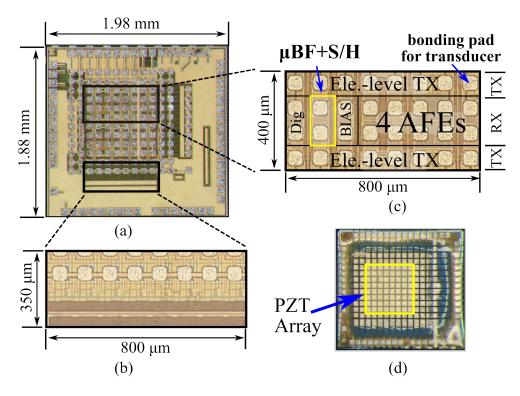

| 4.4.1 ASIC Prototype       88         4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 4.4 |                                                                   | 88  |

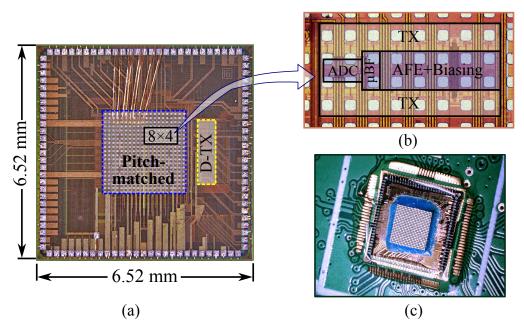

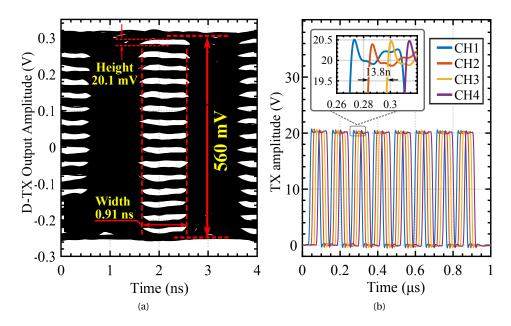

| 4.4.2 Electrical Characterization       90         4.4.3 RX μBF Characterization       94         4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |     |                                                                   | 88  |

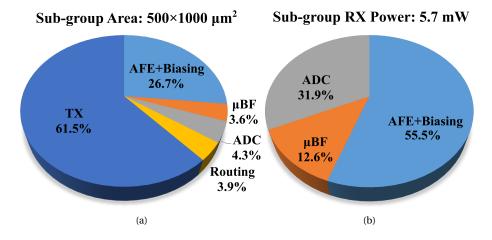

| 4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |     | * *                                                               | 90  |

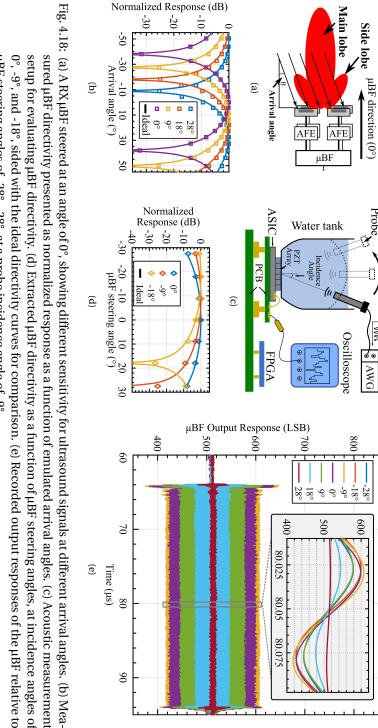

| 4.4.4 Ultrasound B-mode Imaging       95         4.5 Conclusion       97         5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |     | 4.4.3 RX µBF Characterization                                     | 94  |

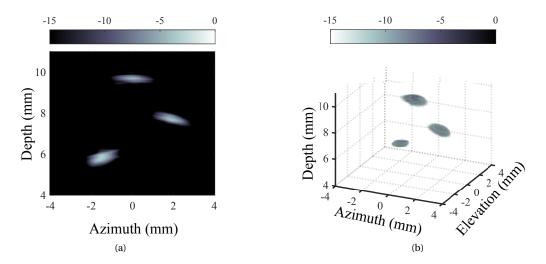

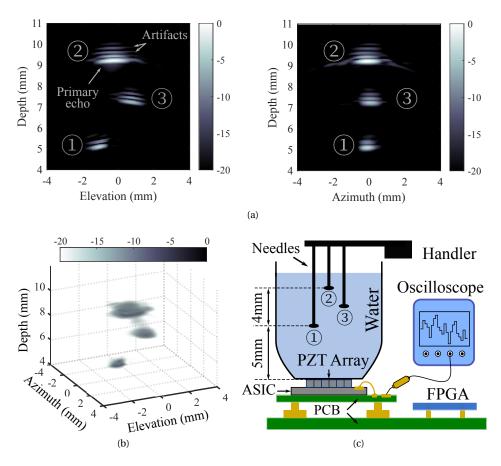

| 5 Conclusion       107         5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |     |                                                                   | 95  |

| 5.1 Main Contributions       107         5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 4.5 | Conclusion                                                        | 97  |

| 5.2 Original Findings       108         5.3 Future Work       110         6 Summary       117         7 Samenvatting       121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 | Con | elusion                                                           | 107 |