Delft University of Technology

## Device Aware Diagnosis for Unique Defects in STT-MRAMs

Aouichi, Ahmed; Yuan, Sicong; Fieback, Moritz; Rao, Siddharth; Kim, Woojin; Marinissen, Erik Jan; Couet, Sebastien; Taouil, Mottagiallah; Hamdioui, Said

DOI 10.1109/ATS59501.2023.10317952

**Publication date** 2023

**Document Version** Final published version

Published in Proceedings of the 2023 IEEE 32nd Asian Test Symposium, ATS 2023

### Citation (APA)

Aouichi, A., Yuan, S., Fieback, M., Rao, S., Kim, W., Marinissen, E. J., Couet, S., Taouil, M., & Hamdioui, S. (2023). Device Aware Diagnosis for Unique Defects in STT-MRAMs. In *Proceedings of the 2023 IEEE 32nd Asian Test Symposium, ATS 2023* (Proceedings of the Asian Test Symposium). IEEE. https://doi.org/10.1109/ATS59501.2023.10317952

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

**Copyright** Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

# 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# Device Aware Diagnosis for Unique Defects in STT-MRAMs

Ahmed Aouichi\* Sicong Yuan\*<sup>‡</sup> Moritz Fieback\* Siddharth Rao<sup>‡</sup> Woojin Kim<sup>‡</sup>

Erik Jan Marinissen<sup>‡</sup> Sebastien Couet<sup>‡</sup> Mottaqiallah Taouil<sup>\*†</sup> Said Hamdioui<sup>\*†</sup>

\*TU Delft, Delft, The Netherlands <sup>†</sup> CognitiveIC, Delft, The Netherlands <sup>‡</sup>IMEC, Leuven, Belgium

{S.Yuan-4, M.C.R.Fieback, M.Taouil, S.Hamdioui}@tudelft.nl {A.Aouichi}@student.tudelft.nl

{Siddharth.Rao, Woojin.Kim, Erik.Jan.Marinissen, Sebastien.Couet}@imec.be

*Abstract*—Spin-Transfer Torque Magnetic RAMs (STT-MRAMs) are on their way to commercialization. However, obtaining high-quality test and diagnosis solutions for STT-MRAMs is challenging due to the existence of unique defects in Magnetic Tunneling Junctions (MTJs). Recently, the Device-Aware Test (DA-Test) method has been put forward as an effective approach mainly for detecting unique defecting STT-MRAMs. In this study, we propose a further advancement based on the DA-Test framework, introducing the Device-Aware Diagnosis (DA-Diagnosis) method. This method comprises two steps: a) defining distinctive features of each unique defect by characterization and physical analysis of defective MTJs, and b) utilizing march algorithms to extract distinctive features. The effectiveness of the proposed approach is validated in an industrial setting with real devices and data measurement.

Index Terms—STT-MRAM, unique defect, test, diagnosis, device-aware method.

#### I. INTRODUCTION

Spin-Transfer Torque Magnetic RAMs (STT-MRAMs) have emerged as a promising technology thanks to their competitive writing performance, low power consumption, retention, and endurance [1]. Since its early commercialization in 2006, world-leading foundries and producers (such as TSMC, Samsung, Intel, and Everspin) have entered the MRAM market, leading to a substantial increase in single-chip storage capacity from 4 MB to 1 GB [1–5]. Further development of such chips requires high-quality testing and diagnosis methods.

Previous works on STT-MRAM testing and diagnosis can be classified into two types: works on conventional defects and works on unique defects in Magnetic Tunneling Junctions (MTJs). Works on conventional defects, such as the interconnect and contact defects, assume that such defects can be modeled as linear resistance; they are mainly based on march algorithms [6-13], similar to what has been done for DRAMs and SRAMs [14,15]. On the other hand, simply modeling unique defects in MTJs with linear resistance results in a low-quality test solution [16-18]; physical mechanism of unique defects involves both the magnetic field impact and the spin-transfer torque (STT) effect. To solve this challenge, the Device-Aware Test (DA-Test) method is introduced [17,18]. The DA-Test approach refers to characterizing unique defects, and designing a specific compact model for the defective MTJ that incorporates the impact of physical defects into

the technology parameters of the device, leading to more accurate test solutions for unique defects [18–20]. However, all these works only focus on detecting unique defects, while no research has been conducted on the diagnosis of these defects. Especially, while the DA-Test method has demonstrated advantages in testing unique defects, it is not well-suited for diagnosing these defects, as its primary optimization lies in fault detection rather than defect recognition. For example, one test solution, such as the one proposed for Pinholes [19], may detect multiple defects at the same time, thus infeasible in diagnosis. Therefore, a dedicated diagnosis approach for unique defects becomes essential to enhance the yield learning of STT-MRAMs.

This work presents the Device-Aware Diagnosis (DA-Diagnosis) framework, which builds upon the structure of DA-Test but takes a further step towards specializing in recognizing defects. In the DA-Diagnosis framework, the diagnosis is achieved by employing a primitive march algorithm to extract distinctive features of each unique defect. Through measurement data in real chips, we demonstrate that the DA-Diagnos approach is cost-effective, flexible, and practical in diagnosing unique defects for STT-MRAMs. Contributions of this work are as follows:

- Present the framework of the DA-Diagnosis method for unique defects in STT-MRAMs.

- Define distinctive features of four unique defects in MTJs.

- Design the primitive march algorithm by extracting distinctive features for each unique defect.

- Prove the effectiveness of the DA-Diagnosis method through measurement data for STT-MRAM chips.

- Evaluate the merits and limitations of the proposed DA-Diagnosis methods.

The rest of this paper is organized as follows. Section II introduces the STT-MRAM basics. Section III introduces the STT-MRAM array used in this work, the set-up of characterization, and the targeted unique defects. Section IV offers the framework of the DA-Diagnosis method for unique defects in STT-MRAMs. Section V applies the proposed DA-Diagnosis framework to the targeted unique defects. Section VI concludes this paper.

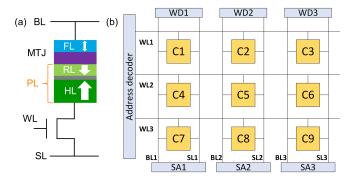

Fig. 1. (a) Simplified MTJ stack and 1T-1M cell, (b) STT-MRAM array.

#### II. BACKGROUND

This section introduces the basic principle of the MTJ device, 1T-1M cell, and the STT-MRAM array.

#### A. MTJ device

The fundamental data storage element in STT-MRAMs is the MTJ; it demonstrates the one-bit data storage by encoding two bi-stable resistance states.

Fig. 1 (a) presents the simplified schematic of an MTJ. Typically, the MTJ consists of an ultra-thin dielectric Tunnel Barrier (TB) sandwiched between a Free Layer (FL) and a Pinned Layer (PL). The FL is a thin ferromagnetic layer, whose magnetization can be switched through write operations. The TB is a thin insulator made of MgO. The PL is a multiple-layer stack composed of Reference Layer (RL), a thin metal spacer, and Hard Layer (HL). The MTJ has two stable resistance states depending on the magnetization direction of FL and RL. If the magnetization of the two layers is in parallel, the MTJ presents low resistance (i.e., P or '0' state); if in anti-parallel, the MTJ presents high resistance (i.e., AP or '1' state). By applying a current through the device, the MTJ state can be switched between 'P' and 'AP' states.

#### B. 1T-1M cell

Fig. 1 (a) illustrates the structure of a 1 Transistor - 1 MTJ (1T-1M) bit cell with three terminals connecting to the Bit Line (BL), Source Line (SL), and Word Line (WL). During write operations, the voltage of WL selects the cell, and the voltage between the BL and SL controls the operation type. For example, the 1w0 operation is performed by connecting the BL to  $V_{\rm DD}$  and the SL to the ground, generating a writing current flowing through the MTJ, and switching the MTJ state from AP to P. In read operations, a small read current  $I_{\rm rd}$  is offered to detect the MTJ resistance while avoiding unwanted state switches.

#### C. STT-MRAM array

Fig. 1 (b) presents a  $3 \times 3$  STT-MRAM array with associated peripheral circuits. In the array, cells in the same row share the same WL, and cells in the same column share the same BL and SL. The peripheral circuit consists of the address decoder, the Write Driver (WD), and the Sense Amplifier (SA). The address decoder selects the device, the WD applies the write and read pulses, and the SA detects the device states.

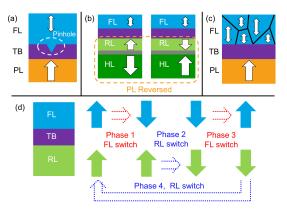

Fig. 2. Mechanisms of defects (a) Pinholes, (b) SAFF, (c) IM, (d) BH.

#### III. EXPERIMENT SET-UP

This section introduces an overview of a) the experiment set-up, and b) the basics of the targeted defects in this work.

#### A. Measurement and test set-up

In this work, we perform measuremens on a 1 Mbit STT-MRAM array (structure same as Fig. 1 (b)). The MTJ Critical Diameter (CD) is 60 nm, and the pitch (distance between neighboring cells) is 200 nm. Additional efforts have been dedicated to circuit design, enabling direct characterization of the 1T-1M cell, which is not typically found in commercial STT-MRAM productions [21]. For example, we are able to extract the resistance of the entire 1T-1M cell ( $R_{cell}$ ) between BL and SL (as in Fig. 1 (a)). This allows us to perform both device-level characterization and circuit-level read/write operations on the same STT-MRAM chip.

#### B. Targeted defects

This study targets diagnosing four unique defects in STT-MRAMs: Pinhole [19,20], Synthetic Anti-Ferromagnet Flip (SAFF) [22], Intermediate-state (IM) [23,24], and Backhopping (BH) [25,26]. These defects are selected because they have been well-studied, and the DA-Test method has been successfully applied to them [18]. Notice that some unique defects are not included here since their mechanism has not been fully understood. The methodology outlined in this work can potentially be applied to them, yet further investigations on the physical mechanisms have to be conducted. To guarantee that each of the four unique defects can also be distinguished from conventional defects, we conduct Spice simulations to observe the STT-MRAM faulty behaviors in the presence of all possible interconnect and contact defects by following the process in [27], which will not be discussed extensively here. The basic of the four unique defects is presented as follows:

1) Pinholes [19,28]: The Pinhole is introduced by the physical imperfection in the MgO or the FL/MgO interface, as presented in Fig.2 (a). This defect has a significant impact on the MTJ tunneling performance, resulting in degradation of MTJ resistance and Tunnel Magneto Resistance (TMR), and further introduces incorrect read destructive faults like < 1r1/0/0 > (i.e., perform the read '1' operation on an MTJ with initial state '1', but the final state becomes '0').

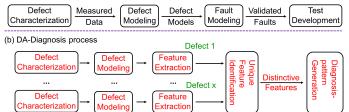

(a) DA-Testing process

Fig. 3. Framework of STT-MRAM test and diagnosis development

2) SAFF [22]: As presented in Fig. 2 (b), the SAFF defect occurs when the PL magnetization gets unexpectedly reversed during manufacturing. This leads to a reversal of the RL magnetization due to the coupling effect [29]. SAFF leads to a high Write Error Rate (WER) depending on the neighbor cell states, and may cause intermittent passive neighborhood pattern sensitive faults [22].

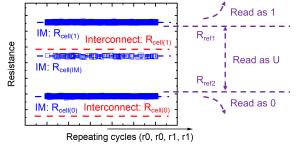

3) IM [23,24]: The IM defect, as shown in Fig. 2 (c), occurs when the FL is not unified. In contrast to the '0' and '1' states, the IM-defective cell may enter a specific stable intermediate state between two regular states when only a portion of the FL gets switched. Therefore, hard-to-detect write faults are observed for IM-defective cells, like < 1w0/U/- > (i.e., perform the write '0' operation on an MTJ with initial state '1', but the final MTJ state becomes an undefined state 'U' between regular '0' and '1' states).

4) BH [25,26]: The BH, as demonstrated in Fig. 2 (d), is caused by the unstable RL. When a write pulse is applied, the RL with low stability undergoes an unexpected switch, subsequently triggers a sequence of FL or RL switches, and forms a four-phase loop (Fig. 5 (a)). The BH-defective device continuously oscillates between the '0' and '1' states during write operations, resulting in a high WER.

#### IV. METHODOLOGY

This section introduces the DA-Test/Diagnosis frameworks.

#### A. Framework of DA-Test

Fig. 3 (a) illustrates the framework of the DA-Test process for STT-MRAMs with four steps [17,18]:

1) Defect Characterization: This step characterizes defect features by measuring defective MTJ performance with electrical and magnetic approaches.

2) Defect Modeling: This step aims to model manufacturing defects. While conventional defects are modeled as resistors [14], unique defects require the DA-Test, which integrates the impact of physical defects into parameters of regular MTJ models, and obtains defective MTJ models.

3) Fault Modeling: This step defines the fault space and validates it through circuit-level (Spice) simulations.

4) *Test Development:* This step generates the test solution for all validated faults through march-based or Design For Test (DFT) approaches.

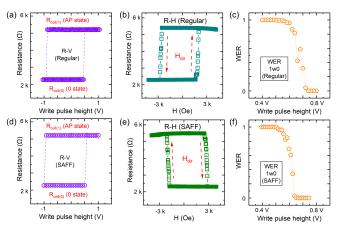

Fig. 4. Characterization of defect-free device: (a) R-V, (b) R-H, (c) WER; Same characterization of SAFF-defective device: (d) R-V, (e) R-H, (f) WER.

#### B. Framework of DA-Diagnosis

The DA-Test is optimized to detect faults, yet does not provide the distinctiveness for defects. For example, the march test algorithm designed for detecting Pinholes in [19] may detect other defects such as BH. In this work, we introduce the DA-Diagnosis process, a new approach that identifies each defect through unique features, and provides marchbased diagnosis solutions. As presented in Fig. 3 (b), the DA-Diagnosis method follows five steps:

1) Defect characterization: This step involves characterizing MTJs. In this work, we apply three common measurement methods: R-V measurement, R-H measurement, and WER extraction. For example, measurement data for defect-free devices are presented in Fig. 4 (a) - (c), compared with those for SAFF-defective devices in Fig. 4 (d) - (f).

2) *Defect modeling:* This step designs models for manufacturing defects. In this work, we directly adopt defect models from previous works [19,23,23,26].

*3) Feature extraction:* This step extracts the features of defective devices based on the characterization and physical analysis. Here, features refer to the electrical or magnetic parameters that can be extracted from the measurement data. All possible features from the three measurement methods are extracted, such as summarized in TABLE I (next section).

4) Unique feature identification: The three steps above will be repeated for the four unique defects (by measurement) and all possible conventional defects (by simulation). This step forms the feature-dictionary by concluding all the features of both conventional and unique defects. Distinctive features are then extracted for each unique defect. Here, a distinctive feature refers to the parameter behaving uniquely to a specific defect, thus allowing for the diagnosis. For example, the reversed R-H hysteresis loop direction (reversed  $H_{dir}$ ) extracted from the R-H measurement is the only distinctive feature of SAFF, as presented in Fig. 4 (b) and (e); while other measurements show the same features for both SAFFdefective and defect-free STT-MRAM cells.

5) Diagnosis pattern generation: This step generates the diagnosis solutions to recognize distinctive features. Here,

we only apply the march-based diagnosis method, which is time-efficient and practical for STT-MRAM arrays. Other methods, like device characterization and Physical Failure Analysis (PFA), are not considered. Characterization methods for prototype MTJs are usually not practical for STT-MRAM arrays, such as the R-V measurement, where it is infeasible to directly extract the MTJ resistance from the structure shown in Fig. 1 (b). PFA methods, like Transmission Electron Microscopes (TEM), are usually costly, time-consuming, and destructive [30]. The final output of the DA-Diagnosis method is the march algorithm for diagnosing each unique defect. If regular march algorithms cannot diagnose certain types of unique defects, additional approaches are applied, like the external magnetic field. For example, the march-based diagnosis for SAFF requires the external magnetic field, which is presented as:  $\{ \ddagger (w0); \ddagger (w0_{Hext}); \ddagger (r0) \}$ . This march algorithm consists of three steps: a) apply w0 to all devices for initialization, b) apply an external magnetic field for the whole chip to perform the w0 operation, c) apply r0 operation to all devices (Details will be discussed later).

Notice that the process variation does not affect unique features of defects, hence no impact on the diagnosis method.

#### V. APPLICATION OF THE METHODS FOR STT-MRAMS

This section applies DA-Diagnosis for four targeted unique defects. The order we present the four unique defects depends on their frequency of occurrence in our measurement/test data (i.e., Pinhole, BH, SAFF, IM).

#### A. Defect characterization

In this step, we first perform the three measurement methods (i.e., R-V, R-H, and WER extraction) on all the devices of 1 MB STT-MRAM cells; an example of results is shown in Fig. 4 for SAFF. To save space, other measurement data is not shown. On the other hand, we extract the MTJ faulty behaviors in the presence of all possible interconnect and contact defects through spice simulations, following the process in [31].

#### B. Defect modeling

As device-aware defect models of the four targeted unique defects are reported in our previous works [19,22,23,26], we therefore make use of them directly.

#### C. Feature extraction

In this step, we summarize all the features we extracted from the R-V, R-H, and WER measurement data for the four unique defects as well as the interconnect & contact defects; the results are reported in TABLE I.

|                          |                                | R-V                            | R-H           | WER       |                                |

|--------------------------|--------------------------------|--------------------------------|---------------|-----------|--------------------------------|

|                          | $R_{cell-0}$                   | $R_{cell-1}$                   | $R_{cell-IM}$ | $H_{dir}$ | WER                            |

| Pinhole                  | $\downarrow$                   | $\downarrow$                   | NA            | NA        | NA                             |

| SAFF                     | NA                             | NA                             | NA            | RD        | \$                             |

| IM                       | NA                             | NA                             | IB            | NA        | <b>†</b>                       |

| BH                       | NA                             | NA                             | NA            | NA        | 1                              |

| Interconnects & contacts | $\downarrow$ , $\uparrow$ , NA | $\downarrow$ , $\uparrow$ , NA | NA            | NA        | $\downarrow$ , $\uparrow$ , NA |

TABLE I. FEATURE-DICTIONARY OF DEFECTS

Where the symbols used in the table are described below:

| $R_{cell-0}$  | Cell resistance in state '0'                   |  |  |  |

|---------------|------------------------------------------------|--|--|--|

| $R_{cell-1}$  | Cell resistance in state '1'                   |  |  |  |

| $R_{cell-IM}$ | Cell resistance in state intermediate state    |  |  |  |

| $H_{dir}$     | R-H hysteresis loop direction                  |  |  |  |

| WER           | Write error rate                               |  |  |  |

| <b>↑</b>      | Increase                                       |  |  |  |

| Ļ             | Decrease                                       |  |  |  |

| RD            | Reversed direction                             |  |  |  |

| NA            | Not affected                                   |  |  |  |

| \$            | Higher or lower depending on neighboring cells |  |  |  |

| IB            | Intermittent behavior                          |  |  |  |

The last row presents all possible situations with the presence of interconnect and contact defects; for instance,  $R_{cell}(0)$  may increase, decrease, or stay constant depending on the nature of the interconnect and contact defects. As an example, Fig. 4 shows the results for SAFF, from which the corresponding features are extracted, and included in TABLE I.

#### D. Distinctive feature identification

This step extracts the distinctive features of each unique defect. A feature is considered distinctive if it behaves uniquely within the column of TABLE I. For example, the intermittent behavior (IB) of the  $R_{cell-IM}$  is identified as the distinctive feature for IM; yet the WER increasing ( $\uparrow$ ) is not a distinctive one, since this behavior is also observed in the presence of BH and conventional defects. Consequently, the distinctive features of SAFF and IM can be directly derived from TABLE.I;  $H_{dir}$  is the distinctive feature of SAFF (i.e. RD), and and the  $R_{cell-IM}$  is the distinctive feature of IM (i.e. IB). However, for Pinhole and BH there is no distinctive feature that can be directly extracted from TABLE.I. Hence, there is a need for 'secondary features' extraction, to ensure distinctive features(s) for each unique defect. Next, we present how we do this for Pinhole and BH:

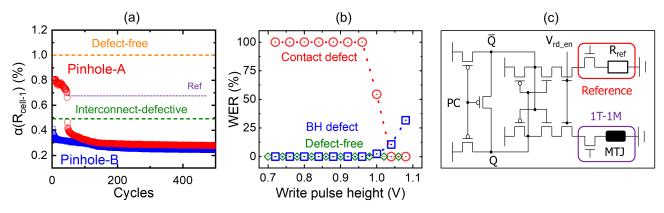

1) Pinholes: As presented in TABLE I, the major feature of Pinhole is the reduced  $R_{cell-0}$  and  $R_{cell-1}$ . However, other defects may also exhibit the same feature, like an interconnect defect between BL and SL of the cell (see Fig. 1). To identify the distinctive feature of Pinhole, we rely on the aid of physical analysis. It has been demonstrated that the MgO of the Pinhole-defective MTJ is vulnerable. When applying the stress test by repeating write operations, the MgO of Pinhole-defective devices experiences further damage, thus further lowering the MTJ resistance [20]. In contrast, the stress test has a negligible impact on the MgO of defect-free MTJs, and on the MTJs with other defects. Therefore, we define the distinctive 'secondary feature' as  $\alpha(R_{cell-1}) = R_{cell(measured)}/R_{cell(defect-free)}$ , being the ratio of the measured  $R_{cell}$  compared with that of a defectfree  $R_{cell}$  when MTJ in the '1' state;  $\alpha$  refers to the ratio. Fig. 5 (a) compares  $\alpha(R_{cell-1})$  behaviors under the stress test for pinhole-defective cells, a defect-free cell, and a cell with an interconnect defect. Clearly  $\alpha(R_{cell-1})$  of the Pinholedefective cell decreases with more write cycles, yet  $\alpha(R_{cell-1})$ of cells with other defects remains constant.

Fig. 5. (a) Unique feature identification for Pinholes, (b) Unique feature identification for BH, (c) SA structure

2) BH: As presented in TABLE I, a high WER is the major irregular feature for BH, yet this is not a distinctive one. Other defects, such as a contact defect between BL and the MTJ, can also cause a high WER. Hence, the 'secondary feature' is necessary. Here, we extract the WER with different write pulse heights. The 'secondary feature' is ' $\alpha(WER)$ ', defined as how WER changes with the write pulse height increasing. For BH-defective MTJs, the range of  $\alpha(WER)$ is limited considering the MTJ state oscillation; when the write pulse height increases, the WER undergoes only slight changes, without exhibiting extremely high or low values. In contrast, the WER of MTJs with other defects will either approach 100% or 0% with the increase of write pulse height. Fig. 5 (b) compares  $\alpha(WER)$  behaviors of a BH-defective cell, a defect-free cell, and a cell with a contact defect. Clearly  $\alpha(R_{cell-1})$  increases a bit for the BH-defective cell, but it decreases dramatically and eventually closes to 0 for the cell with a contact defect. Notice that how WER changes with write pulse depends on various factors like the BH defect strength [26].

#### E. Diagnosis-pattern generation

This step generates the diagnosis patterns. The final output of this step is a set of march algorithms that can be practically performed on industrial STT-MRAM chips. Next, we present how to design the algorithm for each targeted unique defect. TABLE II summarizes the final result of this section.

1) Pinholes: While  $\alpha(R_{cell-1})$  serves as the distinctive feature of Pinhole, the STT-MRAM cell resistance cannot be directly extracted through the STT-MRAM array. For example, we utilize the march algorithm:  $\{ \ddagger (w1, r1)^i \}$  to diagnose Pinhole, indicating repeating w1 and r1 operations for 'i' times, where  $i \geq 30$  according to our measurement. The effectiveness of this march algorithm depends on the SA structure and the defect strength (i.e. Pinhole area [19]). Our work applies the regular SA as given in Fig. 5 (c). If  $R_{cell} \geq R_{ref}$ , then SA gives '1', otherwise '0'. For the two Pinhole-defective devices depicted in Fig. 5 (a), only device-A can be diagnosed; the read operations initially provide correct results, followed by incorrect results, with repeating write operations. Yet, if the Pinhole-defective  $R_{cell}$  is initially lower than  $R_{ref}$  (e.g., device-B), read operations initially provide wrong

Fig. 6. Diagnosing for IM

results, making it impossible to distinguish between Pinholes and other defects. Applying multiple reference resistors in the SA, such as in [20], may diagnose a broader range of Pinholes, but it never guarantees to diagnose all Pinholes.

2) BH:  $\alpha(WER)$  is the distinctive feature of BH, it can be extracted from the STT-MRAM array in three steps: a) Set up the write pulse height  $V_p$  properly (i.e. spec); b) Apply march algorithm { $(w0, r0)^i$ }, where 'i' depends on the targeted WER; c) Repeat steps a) and b) with  $V'_p = 2V_p$ . The BH is diagnosed if read operations provide wrong results in both steps b) and c). Notice that we can also adjust write pulse width rather than pulse height for the BH diagnosis.

3) SAFF:  $H_{dir}$  is recognized as the distinctive feature of SAFF. However, the R-H measurement cannot be applied to regular STT-MRAM arrays, since the STT-MRAM cell resistance cannot be directly extracted. Hence, we apply the following algorithm to observe  $H_{dir}$ : { $( \psi 0)$ ;  $( w0_{Hext})$ ; (r0)}. This march algorithm consists of three steps: a) apply w0 for initialization, b) apply an external magnetic field, and c) apply r0 operation to detect the final state. In the presence of SAFF, the state of the faulty cell will flip to '1'; hence diagnosis is guaranteed.

4) IM:  $R_{cell-IM}$  is recognized as the distinctive feature of IM. However, detecting  $R_{cell-IM}$  is limited by the SA circuit. The SA applied in this work (Fig. 5 (c)) can only detect two states, and  $R_{cell-IM}$  will be read either as '0' or as '1'. Hence, IM can never be detected nor diagnosed. To overcome this limitation, multiple reference resistors are required for the SA. For example, the results presented in Fig. 6 are obtained by such SA utilizing two reference resistors to detect three states: '0', '1', and 'U', representing the intermediate state.

TABLE II. CONCLUSION OF DIAGNOSIS FOR UNIQUE DEFECTS

| Defect   | Mechanism                      | Related steps in<br>STT-MRAM fabrication | Unique feature       | Diagnosis patterns                                                                      | Comments                               |

|----------|--------------------------------|------------------------------------------|----------------------|-----------------------------------------------------------------------------------------|----------------------------------------|

| Pinholes | Physical imperfections in      | MgO or FL deposition,                    | $\alpha(\mathbf{P})$ | $\left\{ \Uparrow \; (w1,r1)^i \right\}$                                                | Higher coverage with                   |

| Plinoles | MgO or FL/MgO interface [32]   | Annealing [32]                           | $\alpha(R_{cell-1})$ |                                                                                         | multiple references                    |

| SAFF     | PL magnetization reversed [22] | Unknown                                  | $H_{dir}$            | $\left\{ \Uparrow (w0); \Uparrow (w0_{Hext}); \Uparrow (r0) \right\}$                   | Require external magnetic field        |

| IM       | Non-unified FL [33]            | Unknown                                  | $P_{IM}$             | $\{ \ (w0, r0, w1, r1)^i \}$                                                            | Require multiple references            |

| BH       | RL instability [25]            | PL deposition [25]                       | $\alpha(WER)$        | 1. { $\pproduct (w0, r0)^i$ }<br>2. adjust write pulse<br>3. { $\pproduct (w0, r0)^i$ } | Require the adjustment of write pulses |

However, it is important to note that other defects, such as the interconnect defect between BL and SL, may also cause the defective STT-MRAM cell state to be located in the 'U' range (see Fig. 6). Therefore, diagnosing IM requires the detection of all three states. To achieve this, we employ the march algorithm:  $\{ \ddagger (w0, r0, w1, r1)^i \}$ , where  $i \ge 10$  according to our measurement. Notice IM has an intermittent behavior. In the presence of contact or interconnect defects, the read operations will result *permanently* in 'U, 1' or in '0, U'. However, in the presence of IM, the read operations will result most of the time in '0, 1', and *intermittently* in 'U, 1' or '0, U'. Hence the difference between read values will distinct contact & interconnect defects from IM.

#### VI. CONCLUSION AND DISCUSSION

This work shows the importance of device-aware defect modeling for defect diagnosis. Understanding how the defects impact the different technology parameters of the device, and hence also the electrical parameters of the device is of great importance. It facilitates the development of diagnosis algorithms that can efficiently distinguish the different unique features of the different defects. We demonstrated the superiority of the approach using industrial STT-MRAM chips.

#### **ACKNOWLEDGEMENTS**

This work is supported by IMEC's Industrial Affiliation Program on STT-MRAM devices.

#### REFERENCES

- L. Wei *et al.*, "13.3 A 7Mb STT-MRAM in 22FFL FinFET Technology with 4ns Read Sensing Time at 0.9V Using Write-Verify-Write Scheme and Offset-Cancellation Sensing Technique," in *ISSCC*, 2019, pp. 214– 216.

- [2] S. Tehrani, "Status and Outlook of MRAM Memory Technology (Invited)," in *IEDM*, 2006, pp. 1–4.

- [3] K. Lee et al., "1Gbit High Density Embedded STT-MRAM in 28nm FDSOI Technology," in IEDM, 2019, pp. 2.2.1–2.2.4.

- [4] W.J. Gallagher *et al.*, "22nm STT-MRAM for Reflow and Automotive Uses with High Yield, Reliability, and Magnetic Immunity and with Performance and Shielding Options," in *IEDM*, 2019, pp. 2.7.1–2.7.4.

- [5] S. Aggarwal *et al.*, "Demonstration of a Reliable 1 Gb Standalone Spin-Transfer Torque MRAM For Industrial Applications," in *IEDM*, 2019, pp. 2.1.1–2.1.4.

- [6] J. Azevedo *et al.*, "A complete resistive-open defect analysis for thermally assisted switching MRAMs," in *VLSI*, vol. 22, no. 11. IEEE, 2014, pp. 2326–2335.

- [7] S.M. Nair *et al.*, "Defect injection, fault modeling and test algorithm generation methodology for STT-MRAM," in *ITC*, 2018, pp. 1–10.

- [8] A. Chintaluri *et al.*, "A model study of defects and faults in embedded spin transfer torque (STT) MRAM arrays," in *ATS*, 2015, pp. 187–192.

- [9] I. Yoon *et al.*, "EMACS: Efficient MBIST architecture for test and characterization of STT-MRAM arrays," in *ITC*, 2016, pp. 1–10.

- [10] I. Yoon *et al.*, "Modeling and analysis of magnetic field induced coupling on embedded STT-MRAM arrays," *IEEE T. COMPUT. AID. D.*, vol. 37, pp. 337–349, 2017.

- [11] S.M. Nair *et al.*, "VAET-STT: Variation aware STT-MRAM analysis and design space exploration tool," *IEEE T. COMPUT. AID. D.*, vol. 37, pp. 1396–1407, 2017.

- [12] W.Y. Lo *et al.*, "Test and diagnosis algorithm generation and evaluation for MRAM write disturbance fault," in *ATS*, 2008, pp. 417–422.

- [13] Z.W. Pan et al., "DFT-Enhanced Test Scheme for Spin-Transfer-Torque (STT) MRAMs," in ITC. IEEE, 2022, pp. 489–493.

- [14] S. Hamdioui *et al.*, "An experimental analysis of spot defects in SRAMs: realistic fault models and tests," in *ATS*, 2000.

- [15] A.J. van de Goor *et al.*, "Disturb neighborhood pattern sensitive fault," in VTS, 1997, pp. 37–45.

- [16] G. Radhakrishnan et al., "Monitoring aging defects in STT-MRAMs," IEEE T. COMPUT. AID. D., vol. 39, pp. 4645–4656, 2020.

- [17] M. Fieback *et al.*, "Device-Aware Test: a New Test Approach Towards DPPB," in *ITC*, 2019, pp. 1–10.

- [18] M. Taouil *et al.*, "Device Aware Test for Memory Units," 2021, in European patent EP4026128A1.

- [19] L. Wu *et al.*, "Electrical Modeling of STT-MRAM Defects," in *ITC*, 2018, pp. 1–10.

- [20] S.B. Mamaghani *et al.*, "Smart Hammering: A practical method of pinhole detection in MRAM memories," in *DATE*, 2023, pp. 1–6.

- [21] S. Rao et al., "STT-MRAM array performance improvement through optimization of Ion Beam Etch and MTJ for Last-Level Cache application," in *IMW*, 2021, pp. 1–4.

- [22] L. Wu *et al.*, "Characterization, Modeling and Test of Synthetic Anti-Ferromagnet Flip Defect in STT-MRAMs," in *ITC*, 2020, pp. 1–10.

- [23] L. Wu *et al.*, "Characterization, Modeling, and Test of Intermediate State Defects in STT-MRAMs," *IEEE Trans. Comput.*, pp. 1–1, 2021.

- [24] X. Yao *et al.*, "Observation of intermediate states in magnetic tunnel junctions with composite free layer," *IEEE Trans. Magn.*, vol. 44, pp. 2496–2499, 2008.

- [25] W. Kim et al., "Experimental Observation of Back-Hopping With Reference Layer Flipping by High-Voltage Pulse in Perpendicular Magnetic Tunnel Junctions," *IEEE Trans. Magn.*, vol. 52, pp. 1–4, 2016.

- [26] S. Yuan et al., "Device-Aware Test for Back-Hopping Defects in STT-MRAMs," in DATE, 2023, pp. 1–6.

- [27] S. Yuan *et al.*, "Magnetic Coupling Based Test Development for Contact and Interconnect Defects in STT-MRAMs (in press)," in *ITC*, 2023.

- [28] B. Oliver et al., "Tunneling criteria and breakdown for low resistive magnetic tunnel junctions," J. Appl. Phys., vol. 94, pp. 1783–1786, 2003.

- [29] J. Nogués et al., "Exchange bias," J. Magn. Magn. Mater., vol. 192, pp. 203–232, 1999.

- [30] S.Y. Liu *et al.*, "Sige profile inspection by using dual beam fib system in physical failure analysis," in *IPFA*. IEEE, 2013, pp. 490–492.

- [31] H. Xun *et al.*, "Data Background-Based Test Development for All Interconnect and Contact Defects in RRAMs (in press)," in *ETS*, 2023, pp. 1–6.

- [32] W. Zhao *et al.*, "Failure analysis in magnetic tunnel junction nanopillar with interfacial perpendicular magnetic anisotropy," *Materials*, vol. 9, p. 41, 2016.

- [33] T. Devolder *et al.*, "Size dependence of nanosecond-scale spin-torque switching in perpendicularly magnetized tunnel junctions," *Phys. Rev. B*, vol. 93, p. 224432, 2016.