### SPAIC: A sub-µW/Channel, 16-Channel General-Purpose Event-Based Analog Front-End with Dual-Mode Encoders

Narayanan, Shyam; Cartiglia, Matteo ; Rubino, Arianna ; Lego, Charles ; Frenkel, Charlotte; Indiveri, Giacomo

DOI

10.1109/BioCAS58349.2023.10388815

Publication date

2023

**Document Version**Final published version

Published in

Proceedings of the 2023 IEEE Biomedical Circuits and Systems Conference (BioCAS)

Citation (APA)

Narayanan, Ś., Cartiglia, M., Rubino, A., Lego, C., Frenkel, C., & Indiveri, G. (2023). SPAIC: A subµW/Channel, 16-Channel General-Purpose Event-Based Analog Front-End with Dual-Mode Encoders. In

Proceedings of the 2023 IEEE Biomedical Circuits and Systems Conference (BioCAS) IEEE.

https://doi.org/10.1109/BioCAS58349.2023.10388815

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# SPAIC: A sub-μW/Channel, 16-Channel General-Purpose Event-Based Analog Front-End with Dual-Mode Encoders

Shyam Narayanan\*, Matteo Cartiglia\* Arianna Rubino\*, Charles Lego \*, Charlotte Frenkel<sup>†</sup>, Giacomo Indiveri\*

\*Institute of Neuroinformatics, University of Zurich and ETH Zurich, Switzerland

† TU Delft, Netherlands

Email: {shyam, camatteo, giacomo}@ini.uzh.ch

Abstract—Low-power event-based analog front-ends (AFE) are a crucial component required to build efficient end-to-end neuromorphic processing systems for edge computing. Although several neuromorphic chips have been developed for implementing spiking neural networks (SNNs) and solving a wide range of sensory processing tasks, there are only a few general-purpose analog front-end devices that can be used to convert analog sensory signals into spikes and interfaced to neuromorphic processors. In this work, we present a novel, highly configurable analog front-end chip, denoted as "SPAIC" (signal-to-spike converter for analog AI computation), that offers a general-purpose dualmode analog signal-to-spike encoding with delta modulation and pulse frequency modulation, with tunable frequency bands. The ASIC is designed in a 180 nm process. It supports and encodes a wide variety of signals spanning 4 orders of magnitude in frequency, and provides an event-based output that is compatible with existing neuromorphic processors. We validated the ASIC for its functions and present initial silicon measurement results characterizing the basic building blocks of the chip.

Index Terms—Neuromorphic, Analog Front-End (AFE), Encoder, Spiking Neural Network (SNN)

#### I. Introduction

Spiking Neural Networks (SNNs) represent a powerful low-power event-based processing computing paradigm for processing streaming data on the edge [1].

To best exploit this novel emerging computing paradigm and build a robust end-to-end SNN sensory processing pipeline, designing efficient event-based analog front-ends is paramount. Fig. 1 illustrates such an end-to-end pipeline. There are various methods of encoding analog signals to spikes [2], [3]. On the hardware front, several analog-to-spike encoders have been developed and demonstrated on silicon, either using Delta Modulation (DM) schemes [4], thereby encoding the temporal changes in the original signal with spike timing, or with Pulse-Frequency Modulation (PFM) schemes [5]–[7], thereby encoding the amplitude of the signal with spike rates. However, these encoders were always optimized for a specific application and for the corresponding frequency bands.

To the best of our knowledge, no general-purpose solution has been proposed to allow exploration and prototyping with existing SNN neuromorphic computing platforms. In this

This work received funding from the European Union's H2020 research and innovation programme under the H2020 BeFerrosynaptic (871737), MeM-Scales (871371) projects.

Fig. 1: Illustration of sensory signal processing pipeline using a general purpose analog front end and SNN.

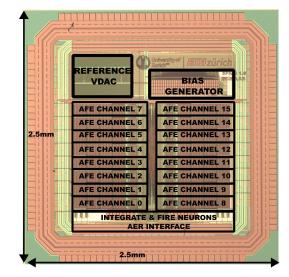

work, we present a highly configurable analog front-end ASIC, denoted as "SPAIC" (signal to spike converter for analog AI computation), which is compatible with existing neuromorphic processors [8]–[12], and which offers a general-purpose dual-mode (DM and PFM) analog-to-spike encoding with tunable frequency bands (see Fig. 2 for the chip micrograph).

#### II. ASIC ARCHITECTURE

SPAIC comprises 16 identical analog channels feeding a common Address Event Representation (AER) interface as shown in Fig. 3. Each channel has four stages: a low noise amplifier section (LNA), a fourth-order flipped voltage follower (FVF) bandpass filter, a programmable gain stage (PGA),

Fig. 2: SPAIC chip micrograph.

#### SPI INTERFACE **AFE CHANNEL 15** AFE CHANNEL 0 NEURON **ENCODERS** $\bigoplus I_{RFR}$ & **ACK AER** INTERFACE 8-BIT CDAC 8-BIT CDAC **PGA** Sigr al path $oldsymbol{v}_{ extbf{RE}^{i}}$ $A_{PGA} = C_{FB}$ DN Tunable ADM seudo Resisto FVF-BPF

Fig. 3: Architecture of SPAIC Analog Front-End ASIC.

and the encoding stage. The LNA amplifies weak signals with tunable gain of 0 to 24dB. The FVF BPF filters the amplified signal with a tunable center frequency and Q [13]. The PGA further amplifies the filtered signal with a tunable gain up to 24dB. The amplified signal is then split in two mutually exclusive paths where either the asynchronous delta modulator encodes the temporal derivative of the amplified signal, or the integrate and fire neuron [14] is enabled and the signal is encoded as a pulse-frequency-modulated spike train. All configurations to the chip are provided in three ways: a configurable on-chip bias generator that generates the necessary bias currents for all circuits in the analog front-end, an 8-bit capacitor DAC (CDAC) to tune the filter parameters and a voltage DAC (VDAC) to set the UP and DN thresholds for the Asynchronous Delta Modulator (ADM). All three of these DACs are configurable via Serial Peripheral Interface (SPI) protocol.

#### III. CIRCUIT IMPLEMENTATION

The SPAIC ASIC was designed and fabricated in a bulk 180 nm technology node. The chip dimensions including the seal ring are 2.5 mm×2.5 mm. The circuit implementation of the major building blocks is described hereafter.

#### A. Low noise amplifiers

For modularity reasons, both amplifiers in the analog frontend (LNA and PGA) are built on the same Operational Tranconductance Amplifier (OTA) core with minor changes adapted for noise and power. The structure of the OTA is based on a well-known wide input range current-mirror-type transconductance amplifier [15]. The primary reason for this design choice was to accommodate for large input changes that may or may not be present depending on the input sensor. The amplifiers are operated in a closed loop as capacitive feedback amplifiers with a DC-Servo loop (DSL) implemented with tunable pseudo resistors as shown in Fig. 3. The capacitance ratio of the feedback to input capacitance determines the overall closed-loop gain. This gain configuration is implemented as a 4-bit binary weighted capacitance DAC, leading to 16 distinct gain values. The gains as well as the noise performance were validated on silicon and are described in Section IV.

#### B. Flipped Voltage Follower-based bandpass filter

Every AFE channel has a 4th-order BPF with tunable center frequency and Q. The FVF-based filter topology shown in Fig. 3 helps achieve better noise performance due to the inherent current reuse present in the architecture.

The filter's center frequency ( $\omega_0$ ) is tunable with the on-chip bias generator. The capacitors of this filter are implemented as an 8-bit CDAC. By configuring  $C_1$  and  $C_2$ , the Q and the center frequency can be adjusted in a precise manner with a resolution of  $C_{1,2}/256$  steps, as described in Eq. (1).

$$\omega_0 = \sqrt{\frac{gm_1 \cdot gm_2}{C_1 \cdot C_2}}, Q = \sqrt{\frac{gm_2 \cdot C_2}{gm_1 \cdot C_1}}$$

(1)

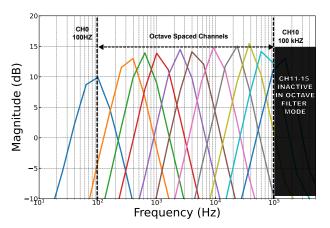

As each filter's center frequency and Q are programmable, they can be configured as a parallel filter bank or as identical parallel electrode interface channels. The frequency response, when configured as a filter bank, measured from the functional silicon is shown in Fig. 6, Section IV.

#### C. Asynchronous Delta Modulation encoder

The ADM is designed based on the foundation of a level-crossing ADC. The amplified and conditioned signal is

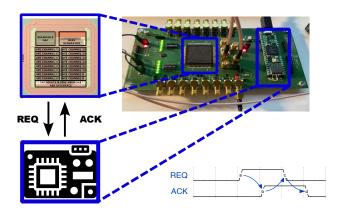

Fig. 4: Measurement setup of the ASIC with a Teensy microcontroller, communicating via a 4-phase asynchronous handshaking protocol.

compared with two known voltage thresholds (an up threshold and a down threshold) set by an on-chip voltage DAC. When the signal crosses the up threshold, an "UP" spike is generated and similarly, in the other direction a "DOWN" spike is generated when the signal goes below the set down threshold. The DACs were simulated running Monte Carlo analysis and the absolute accuracy  $(3\sigma)$  of the voltage thresholds was found to be  $\approx \pm 900~\mu V$ . The comparator used in this ADM was designed with hysteresis [16], [17] to avoid false triggering due to fluctuations in the signal path arriving at the input of the comparator.

#### D. Pulse Frequency Modulation encoder

The PFM encoder was designed using a leaky integrate and fire neuron (LIF) circuit [14] which inherently encodes the amplitude of the input current into pulse frequency. Therefore, before being encoded into spikes, the input signal is half-wave rectified and converted into current by a wide-range transconductance amplifier. The output current of this amplifier flows into the input of the neuron which generates a spike when the input current crosses an externally set spiking threshold of the neuron.

#### IV. SILICON VALIDATION AND MEASUREMENT RESULTS

A custom evaluation board with a Teensy microcontroller was designed to evaluate the functionality of the ASIC. The setup is shown in Fig. 4. The microcontroller communicates with the ASIC and programs its internal registers via an SPI communication protocol. The two separate encoding paths are fully independent of each other and have their own AER circuitry. The AER circuitry operates based on a well-established four-phase hand-shaking mechanism described in Fig. 4 [18]. The asynchronous nature of the AER interface ensures sparse event-driven communication with other asynchronous devices.

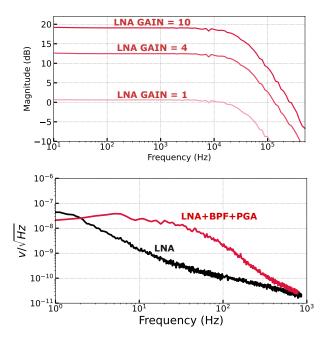

The frequency response of the amplifiers and the noise power spectral density (Noise-PSD) measurement of the AFE are shown in Fig. 5. The plots show the noise PSD in the 1 Hz-1 kHz band, which is mainly dominated by flicker noise. The input-referred noise is  $1.4\,\mu V$  measured at the output of the first

Fig. 5: Frequency Response of LNA (top) noise power spectral density (PSD) measurement (bottom).

Fig. 6: Frequency Response of the bandpass filter bank

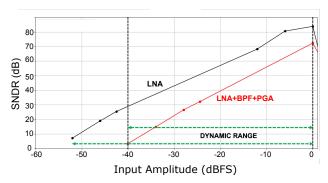

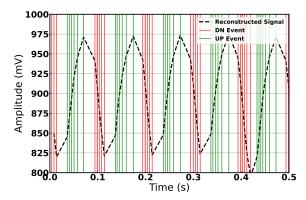

LNA. Fig 6 shows a measurement where the bias currents were programmed in octaves to obtain center frequencies spaced in octaves. When the filter channels are octave-spaced, 11 channels can cover a range of 100 Hz-100 kHz. When used as identical channels, all 16 curves roughly overlap each other. The filter has a dynamic range superior to 40dB, however, reducing the gain of the first amplification stage helps to avoid distortion in the filtering stage. The silicon measurement of signal-to-noise and distortion ratio (SNDR) of a single AFE channel reveals a dynamic range of 42dB at the output of PGA as shown in Fig. 7. The encoding functionality of both ADM and PFM were measured on the silicon. A 100 Hz pure tone was encoded with ADM and the UP and DOWN events were recorded. To validate the encoding, the signal was reconstructed from the spikes and is shown in Fig. 8. A finer or coarser signal reconstruction can

Fig. 7: SNDR Measurement of an AFE Channel.

Fig. 8: ADM spiking response to a 100Hz signal and reconstruction of the signal from spikes.

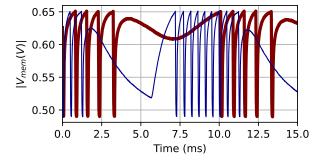

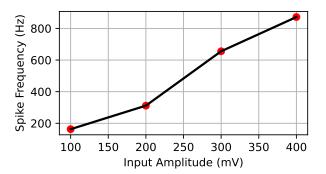

be achieved depending on the configured voltage thresholds. The final encoding accuracy is further determined by the input referred offset of the comparators. Similarly, the functionality of the neuron as a PFM encoder was validated by physical measurement of its membrane potential in response to a 100Hz pure tone as shown in Fig. 9. The red trace in Fig. 9 shows the response to a 100mV input and blue trace to a 400mV input. The almost linear relationship of the spiking frequency to input amplitude shown in Fig. 10 confirms the intended functionality of the block.

Fig. 9: Neuron's membrane potential response for different amplitudes of the input signal of the AFE. Red (100mV), Blue (400mV).

Fig. 10: Spike frequency response to different input amplitudes.

Table I compares the performance of this work with similar event-based analog front-ends. This design can cover a programmable range from 100 Hz to 100 KHz. The AFE

TABLE I: Comparision with prior work

|                                      | This Work    | <b>[6</b> ] | <b>[4</b> ] | [ <mark>7</mark> ] |

|--------------------------------------|--------------|-------------|-------------|--------------------|

| Technology [nm]                      | 180          | 180         | 180         | 90                 |

| Feature                              | Analog to    | Analog to   | Analog to   | Analog to          |

|                                      | Events       | Events      | Events      | Events             |

| Channels                             | 16           | 16          | 64x2        | 16                 |

| Bandwidth [Hz]                       | <100-100K    | 100-5K      | 8-20K       | 75-5K              |

| Power/Channel [nW]                   | <800@100KHz  | 24          | 430         | 380                |

| Normalized Power <sup>1</sup> [nW]   | 532          | 88          | 821         | 1500               |

| Input Referred Noise $[\mu V_{rms}]$ | 1.4@LNA      | 8.3         | 30          | 32.5               |

| Dynamic Range [dB]                   | 55@LNA       | 40@İAF      | 55@BPF      | 45@LNA             |

|                                      | 40@PGA       |             |             |                    |

| Area/Channel [mm <sup>2</sup> ]      | 0.09         | 0.1         | 0.26        | 0.13               |

| Functional Building                  | LNA          | LNA         | LNA         | LNA                |

| Blocks                               | BPF          | BPF         | BPF         | BPF                |

|                                      | PGA          | FWR         | PGA         | FWR                |

|                                      | ADM          | IAF         | ADM         | LPF                |

|                                      | OTA+AdExpI&F |             |             |                    |

Normalized to 5kHz using equation (8) in reference [4]

consumes about 800 nW with the channel processing at the highest frequency (100 kHz) enabled. All other lower-frequency channels consume proportionally lower power. The power consumption was normalized to 5kHz and the normalized power for SPAIC AFE is about 532 nW.

#### V. Conclusions

In this paper, we proposed a highly configurable generalpurpose signal-to-spike encoding ASIC with a dual-mode encoding scheme, designed and fabricated in 180 nm technology.

We demonstrated a generic signal conditioning and dualway encoding scheme that one can pair with a spiking neural network to build an event-based neuromorphic sensing system. The design is comparable to the state-of-the-art in terms of dynamic range and silicon area and is better in terms of the operating range across a larger frequency range and noise performance.

Future work includes quantitatively benchmarking the encoding schemes with a few selected applications such as low-frequency biomedical signals to auditory signals and high-frequency ultrasonic signals and quantifying the normalized power consumption for any selected application.

This work represents a key enabler for building an end-toend signal acquisition pipeline for edge computing nodes with spiking neural networks.

#### REFERENCES

- [1] C. Bartolozzi, G. Indiveri, and E. Donati, "Embodied neuromorphic intelligence," *Nature Communications*, vol. 13, no. 1024, pp. 1–14, 2022.

- [2] W. Guo, M. E. Fouda, and N. Eltawil Ahmed M.and Salama Khaled, "Neural coding in spiking neural networks: A comparative study for robust neuromorphic systems," *Frontiers in Neuroscience*, vol. 15, 2021.

- [3] E. Forno, V. Fra, R. Pignari, E. Macii, and G. Urgese, "Spike encoding techniques for iot time-varying signals benchmarked on a neuromorphic classification task," *Frontiers in Neuroscience*, vol. 16, 2022.

- [4] M. Yang, C.-H. Chien, T. Delbruck, and S.-C. Liu, "A 0.5v 55μw 64×2-channel binaural silicon cochlea for event-driven stereo-audio sensing," in 2016 IEEE International Solid-State Circuits Conference (ISSCC), 2016, pp. 388–389.

- [5] F. Corradi and G. Indiveri, "A neuromorphic event-based neural recording system for smart brain-machine-interfaces," *Biomedical Circuits and Systems, IEEE Transactions on*, vol. 9, no. 5, pp. 699–709, 2015.

- [6] M. Yang, C.-H. Yeh, Y. Zhou, et al., "A 1μw voice activity detector using analog feature extraction and digital deep neural network," in 2018 IEEE International Solid - State Circuits Conference - (ISSCC), 2018, pp. 346–348.

- [7] K. Badami, S. Lauwereins, W. Meert, and M. Verhelst, "24.2 context-aware hierarchical information-sensing in a 6μw 90nm cmos voice activity detector," in 2015 IEEE International Solid-State Circuits Conference - (ISSCC) Digest of Technical Papers, 2015, pp. 1–3.

- [8] S. Moradi, N. Qiao, F. Stefanini, and G. Indiveri, "A scalable multicore architecture with heterogeneous memory structures for dynamic neuromorphic asynchronous processors (dynaps)," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 12, no. 1, pp. 106–122, 2018.

- [9] M. Davies, N. Srinivasa, T.-H. Lin, *et al.*, "Loihi: A neuromorphic manycore processor with on-chip learning," *IEEE Micro*, vol. 38, no. 1, pp. 82–99, 2018.

- [10] C. Frenkel and G. Indiveri, "ReckOn: A 28 nm sub-mm² task-agnostic spiking recurrent neural network processor enabling on-chip learning over second-long timescales," in 2022 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), IEEE, 2022, pp. 468–470.

- [11] C. Mayr, S. Hoeppner, and S. Furber, "Spinnaker 2: A 10 million core processor system for brain simulation and machine learning," *arXiv preprint arXiv:1911.02385*, 2019.

- [12] C. Frenkel, M. Lefebvre, J.-D. Legat, and D. Bol, "A 0.086-mm2 12.7-pj/SOP 64k-synapse 256-neuron onlinelearning digital spiking neuromorphic processor in 28nm CMOS," *IEEE Transactions on Biomedical Circuits* and Systems, vol. 13, no. 1, pp. 145–158, 2019.

- [13] Y. Xu, J. Muhlestein, and U.-K. Moon, "A 0.65mw 20mhz 5th-order low-pass filter with +28.8dbm iip3 using source follower coupling," in 2017 IEEE Custom Integrated Circuits Conference (CICC), 2017, pp. 1–4.

- [14] A. Rubino, C. Livanelioglu, N. Qiao, M. Payvand, and G. Indiveri, "Ultra-low-power fdsoi neural circuits for extreme-edge neuromorphic intelligence," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 68, no. 1, pp. 45–56, 2021.

- [15] R. Harrison, "A low-power, low-noise cmos amplifier for neural recording applications," in 2002 IEEE International Symposium on Circuits and Systems. Proceedings (Cat. No.02CH37353), vol. 5, 2002, pp. V–V.

- [16] D. Allstot, "A precision variable-supply cmos comparator," *IEEE Journal of Solid-State Circuits*, vol. 17, no. 6, pp. 1080–1087, 1982.

- [17] P. Allen and D. Holberg, *CMOS Analog Circuit Design* (The Oxford Series in Electrical and Computer Engineering). OUP USA, 2011, ISBN: 9780199765072.

- [18] J. Lazzaro, J. Wawrzynek, M. Mahowald, M. Sivilotti, and D. Gillespie, "Silicon auditory processors as computer peripherals," *IEEE Transactions on Neural Networks*, vol. 4, pp. 523–528, 1993.