Delft University of Technology

### On the real-world security of cryptographic primitives From theory to practice

Najm, Z.

DOI 10.4233/uuid:b0adc65b-301a-49dc-aac5-03f3c55f7f2a

**Publication date** 2023

**Document Version** Final published version

Citation (APA)

Najm, Z. (2023). On the real-world security of cryptographic primitives: From theory to practice. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:b0adc65b-301a-49dc-aac5-03f3c55f7f2a

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

#### Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# On the real-world security of cryptographic primitives

From theory to practice

### Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.dr.ir T.H.J.J. van der Hagen, voorzitter van het College voor Promoties, in het openbaar te verdedigen op dinsdag 17 oktober 2023 om 12:30 uur.

door

### Zakaria NAJM

Master of Science in Mathematics and Computer Science, University of Grenoble,

geboren te Bourgoin-Jallieu, France.

Dit proefschrift is goedgekeurd door de promotoren.

Samenstelling promotiecommissie bestaat uit: Rector magnificus, voorzitter Prof. dr. P. Hartel Technische Universiteit Delft, promotor Dr. S. Picek, Technische Universiteit Delft, copromotor Onafhankelijke leden: Prof.dr. P.R. Schaumont Worcester Polytechnic Inst., USA Prof.dr.ir. N. Mentens U. Leiden, NL Prof.dr. G. Smaragdakis Technische Universiteit Delft Prof.dr. M. Conti TUD/ U. Padua, Italy EEMCS Prof.dr.ir. R.L. Lagendijk Technische Universiteit Delft, reservelid

*Keywords:* Cyber Security, Information Security, Side Channel Attack, Cryptography, Implementations

Printed by: Ipskamp Printing, Enschede

Front & Back: Zakaria Najm

Copyright © 2021 by Z. Najm

TU Delft PhD Series, Delft 2021

ISBN 978-94-6384-497-0

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

## Contents

| Ι  | Int  | roduc                                    | tion                                                        | 1  |  |

|----|------|------------------------------------------|-------------------------------------------------------------|----|--|

| 1  | Intr | oductio                                  | on                                                          | 3  |  |

|    | 1.1  | Backg                                    | ground                                                      | 3  |  |

|    | 1.2  | Problem statement and Research questions |                                                             |    |  |

|    |      | 1.2.1                                    | Scope                                                       | 11 |  |

|    |      | 1.2.2                                    | The Practical Cryptanalysis (Part II)                       | 12 |  |

|    |      | 1.2.3                                    | Passive Side-Channel Attacks and Countermeasures (Part III) | 13 |  |

|    |      | 1.2.4                                    | Active Side-Channel Attacks and Countermeasures (Part IV)   | 13 |  |

|    |      | 1.2.5                                    | Design considerations and guidelines (Part V)               | 15 |  |

|    |      | 1.2.6                                    | Application of design guidelines: Lightweight cipher secure |    |  |

|    |      |                                          | implementations (Part VI)                                   | 16 |  |

|    |      | 1.2.7                                    | Research questions summary                                  | 18 |  |

|    | 1.3  | Outlin                                   | ne and Contributions                                        | 18 |  |

|    |      | 1.3.1                                    | Part II: The Practical Cryptanalysis                        | 18 |  |

|    |      | 1.3.2                                    | Part III: Passive Side-Channel Attacks and Countermeasures  | 20 |  |

|    |      | 1.3.3                                    | Part IV : Active Side-Channel Attacks and Countermeasures   | 21 |  |

|    |      | 1.3.4                                    | Part V: Design considerations and guidelines                | 23 |  |

|    |      | 1.3.5                                    | Part VI: Application of design guidelines: Lightweight ci-  |    |  |

|    |      |                                          | pher secure implementations                                 | 24 |  |

| II | Tł   | ne Pra                                   | ctical Cryptanalysis                                        | 25 |  |

| 2  | Har  | dware A                                  | Acceleration Bridging the Gap between Practical and Theo-   |    |  |

|    | reti | cal Cry                                  | ptanalysis                                                  | 29 |  |

|    | 2.1  | 2.1 Introduction                         |                                                             |    |  |

|    | 2.2  | Crypt                                    | analytic Attacks with Tight Hardware Requirements           | 31 |  |

|    |      | 2.2.1                                    | Brute-Force Attacks                                         | 31 |  |

|    |      | 2.2.2                                    | Time-Memory-Data Trade-off Attacks                          | 32 |  |

|    |      | 2.2.3                                    | Parallel Birthday Search Algorithms                         | 34 |  |

|    | 2.3  | Hardy                                    | ware Machines for Breaking Ciphers                          | 36 |  |

|    |      | 2.3.1                                    | Brute Force Machines                                        | 36 |  |

|   |      | 2.3.1   | Brute Force Machines                                     | 36 |

|---|------|---------|----------------------------------------------------------|----|

|   |      | 2.3.2   | Acceleration of Collision Attacks on Hash Functions      | 37 |

|   |      | 2.3.3   | The Factoring Machine                                    | 38 |

|   |      | 2.3.4   | Molecular Computers                                      | 38 |

|   |      | 2.3.5   | Blockchain Mining                                        | 38 |

|   | 2.4  | Ouan    | tum Computers                                            | 39 |

|   | 2.5  |         | lusion                                                   | 40 |

| 3 | On 7 | The Co  | st of ASIC Hardware Crackers: A SHA-1 Case Study         | 41 |

|   | 3.1  | Intro   | duction                                                  | 42 |

|   | 3.2  | Hash    | Functions and Cryptanalysis                              | 45 |

|   |      | 3.2.1   | SHA-1 and Related Attacks                                | 45 |

|   |      | 3.2.2   | Birthday Search in Practice                              | 46 |

|   |      | 3.2.3   | Differential Cryptanalysis.                              | 47 |

|   | 3.3  | Hard    | ware Birthday Cluster                                    | 49 |

|   |      | 3.3.1   | Cluster Nodes                                            | 49 |

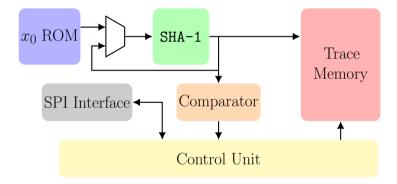

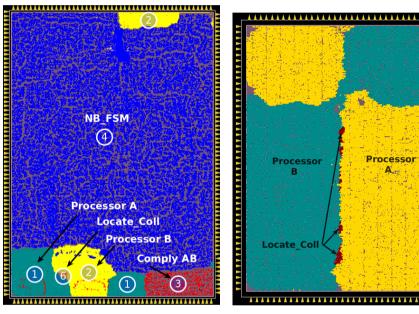

|   |      | 3.3.2   | Hardware Design of Birthday Slaves                       | 50 |

|   | 3.4  | Verifi  | cation                                                   | 51 |

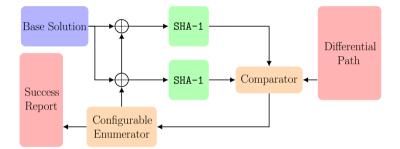

|   | 3.5  | Hard    | ware Differential Attack Cluster Design                  | 51 |

|   |      | 3.5.1   | Neutral Bits                                             | 51 |

|   |      | 3.5.2   | Storage                                                  | 52 |

|   |      | 3.5.3   | Architecture                                             | 53 |

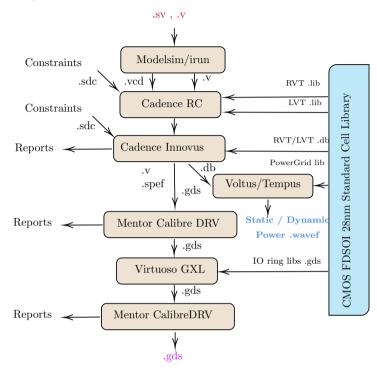

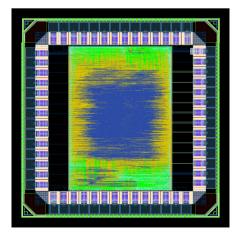

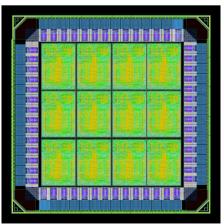

|   | 3.6  | Chip    | Design                                                   | 53 |

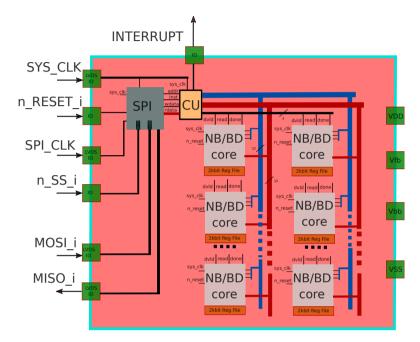

|   |      | 3.6.1   | Chip Architecture                                        | 53 |

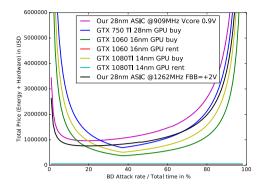

|   |      | 3.6.2   | ASIC Fabrication and Running Cost                        | 54 |

|   | 3.7  | Chip    | layout                                                   | 57 |

|   | 3.8  |         | cation                                                   | 58 |

|   |      | 3.8.1   | Results                                                  | 59 |

|   |      | 3.8.2   | Attack Rates and Execution Time                          | 61 |

|   | 3.9  | Cost    | Analysis and Comparisons                                 | 64 |

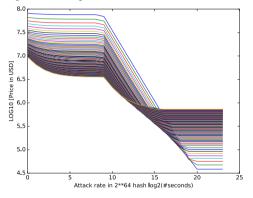

|   |      | 3.9.1   | 2 <sup>64</sup> Birthday Attack                          | 64 |

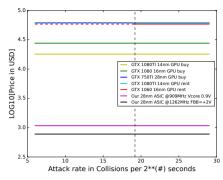

|   |      | 3.9.2   | 2 <sup>80</sup> Birthday Attack                          | 66 |

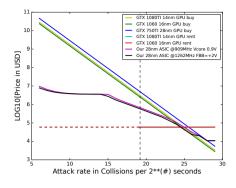

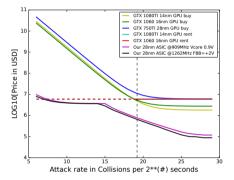

|   |      | 3.9.3   | Chosen Prefix Differential Collision Attack              | 67 |

|   |      | 3.9.4   | Limitations                                              | 69 |

|   | 3.10 | Conc    | lusion                                                   | 69 |

|   |      |         |                                                          |    |

| Π | I Pa | assive  | e Side-Channel Attacks on implementations                | 71 |

| 4 | On   | Compa   | aring Side-channel Properties of AES and ChaCha20 on Mi- |    |

| • |      | ontroll |                                                          | 75 |

|   |      |         | duction                                                  | 75 |

|   | 4.2 | Backg    | ground                                                  | 76  |

|---|-----|----------|---------------------------------------------------------|-----|

|   |     | 4.2.1    | Target Algorithms                                       | 76  |

|   |     | 4.2.2    | Side-Channel Attacks and Metrics                        | 77  |

|   | 4.3 | Side-c   | channel Analysis of Target Algorithms                   | 79  |

|   | 4.4 |          | rds Side-channel Protection                             | 81  |

|   |     | 4.4.1    | Preventing Timing Side-channels                         | 81  |

|   |     | 4.4.2    | Preventing Power Side-channels                          | 82  |

|   | 4.5 | Concl    | lusions                                                 | 83  |

| 5 | Mul | ti-Varia | ate High-Order Attacks of Shuffled Tables Recomputation | 85  |

| 0 | 5.1 |          | luction                                                 | 86  |

|   | 5.2 |          | ninary and notations                                    | 88  |

|   | 5.3 |          | ing scheme with table recomputation                     | 89  |

|   | 0.0 | 5.3.1    | Algorithm                                               | 89  |

|   |     | 5.3.2    | Classical attacks                                       | 89  |

|   |     | 5.3.3    | Classical countermeasure                                | 90  |

|   | 5.4 |          | y random permutation and attack                         | 90  |

|   | 0.1 | 5.4.1    | Defeating the countermeasure                            | 91  |

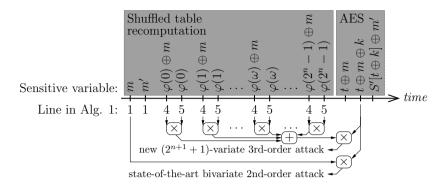

|   |     | 5.4.2    | Multivariate attacks against table recomputation        | 92  |

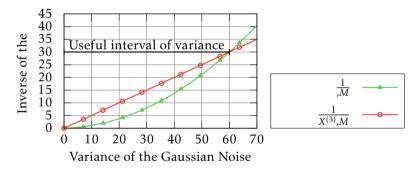

|   |     | 5.4.3    | Leakage analysis                                        | 95  |

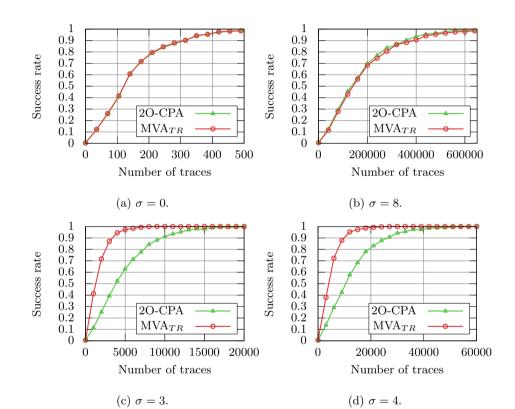

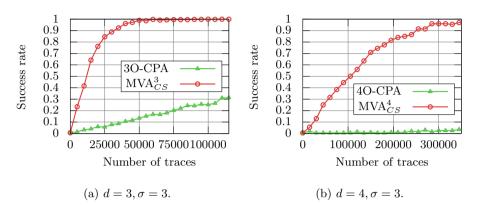

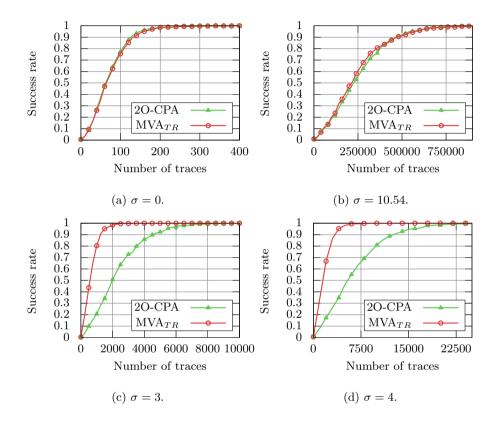

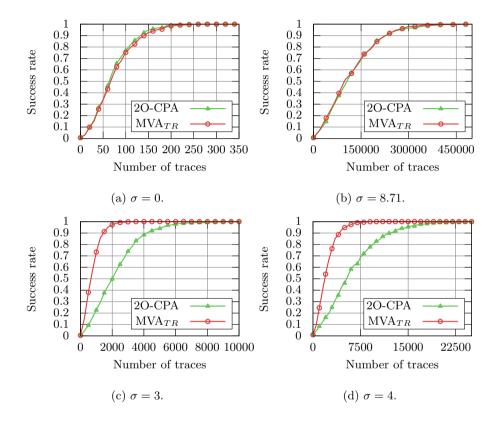

|   |     | 5.4.4    | Simulation results                                      | 96  |

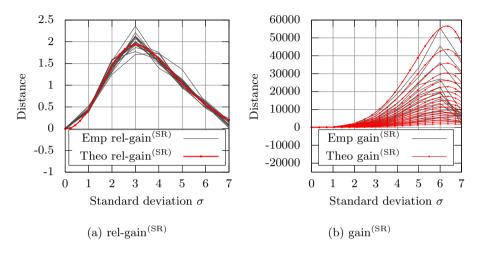

|   |     | 5.4.5    | Theoretical analysis of the Success Rate                | 97  |

|   | 5.5 |          | ample on a high-order countermeasure                    |     |

|   |     | 5.5.1    | Coron masking scheme attack and countermeasure          | 101 |

|   |     | 5.5.2    | Attack on the countermeasure                            |     |

|   |     | 5.5.3    | Leakage analysis                                        |     |

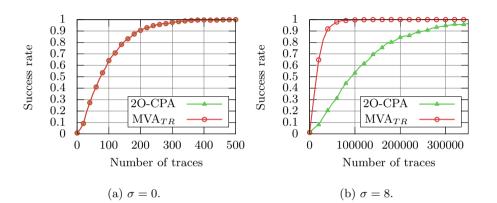

|   |     | 5.5.4    | Simulation results on Coron masking Scheme              |     |

|   | 5.6 | A not    | e on affine model                                       | 108 |

|   |     | 5.6.1    | Properties of the affine model                          |     |

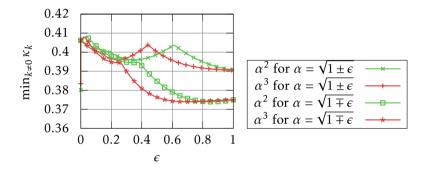

|   |     | 5.6.2    | Impact of the model on the confusion coefficient        |     |

|   |     | 5.6.3    | Theoretical analysis                                    |     |

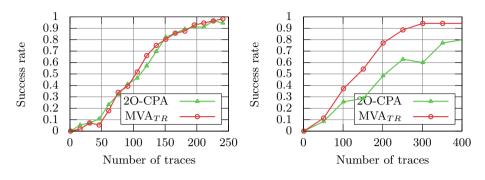

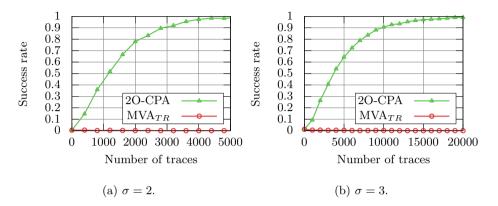

|   |     | 5.6.4    | Simulation results                                      |     |

|   | 5.7 | Practi   | ical validation                                         |     |

|   |     |          | Experimental Setup                                      |     |

|   |     | 5.7.2    | Experimental results                                    |     |

|   | 5.8 | Count    | termeasure                                              | 118 |

|   |     | 5.8.1    | Countermeasure Principle                                | 118 |

|   |     | 5.8.2    | Implementations                                         | 119 |

|   |     | 5.8.3    | Security Analysis                                       | 120 |

|   |     | 5.8.4    | Implementation analysis                                 | 120 |

|   | 5.9 | Concl    | usions and Perspectives                                 | 122 |

|   |     |          |                                                         |     |

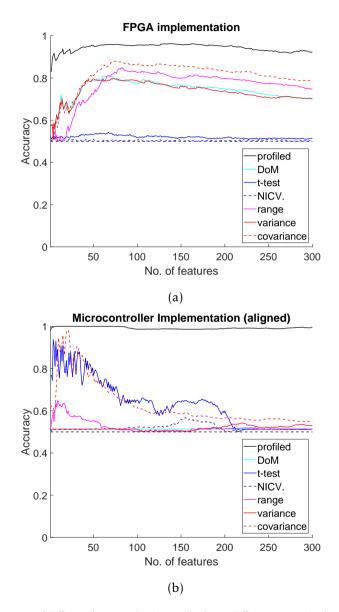

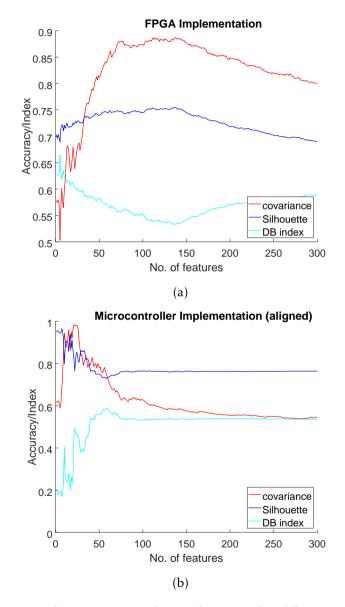

| 6  | Feat<br>ECC | re Selection Methods for Non-Profiled Side-Channel Attacks                     | on<br>125 |

|----|-------------|--------------------------------------------------------------------------------|-----------|

|    | 6.1         | Introduction                                                                   |           |

|    |             | Related Work                                                                   |           |

|    | 6.3         | Methodology                                                                    |           |

|    | 0.5         | 5.3.1 Trace Characterization                                                   |           |

|    |             | 5.3.1         Frace Characterization           6.3.2         Feature selection |           |

|    |             | 6.3.3 Classification Phase                                                     |           |

|    | 6.4         | Experiments                                                                    |           |

|    | 0.1         | 6.4.1 Hardware Implementation and Evaluation Setup                             |           |

|    |             | 5.4.2 Software Implementation and Evaluation Setup                             |           |

|    |             | 5.4.3 Experimental Results                                                     |           |

|    |             | 5.4.4 Discussions                                                              |           |

|    | 6.5         | Conclusion                                                                     |           |

|    | 0.0         |                                                                                |           |

| IV | A A         | tive Side-Channel Attacks and countermeasures                                  | 135       |

| 7  | SoK         | On DFA Vulnerabilities of Substitution-Permutation Network                     | ks 139    |

|    | 7.1         | Introduction                                                                   | 140       |

|    | 7.2         | Background                                                                     | 143       |

|    | 7.3         | Information Theoretic DFA Model: Towards a theoretical secur                   |           |

|    |             | metric for DFA                                                                 | 146       |

|    | 7.4         | DFA against the last round of SPN                                              | 148       |

|    |             | 7.4.1 Reduction of the number of faults                                        | 149       |

|    |             | 7.4.2 Joint Difference Distribution Table (JDDT)                               |           |

|    | 7.5         | Three Round DFA Attack on SPNs                                                 | 153       |

|    | 7.6         | Single Fault Attacks against real world SPNs                                   | 155       |

|    |             | 7.6.1 PRESENT-80/128: Finding Optimal Attack                                   | 155       |

|    |             | 7.6.2 AES-128: Matching Best Known DFA Attack                                  |           |

|    |             | 7.6.3 SKINNY: Matching Best Known DFA Attack                                   | 162       |

|    | 7.7         | Conclusion                                                                     | 165       |

| 8  |             | Injection attack on Private Circuit II                                         | 167       |

|    |             | Introduction                                                                   |           |

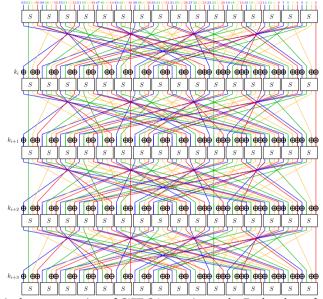

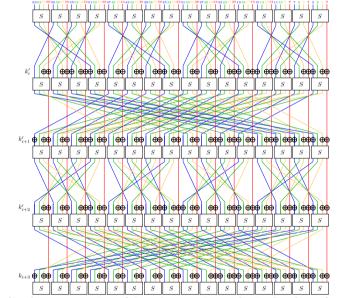

|    | 8.2         | Private Circuits I & II in FPGA                                                |           |

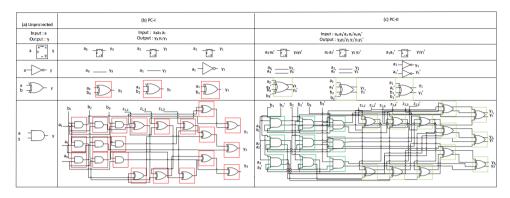

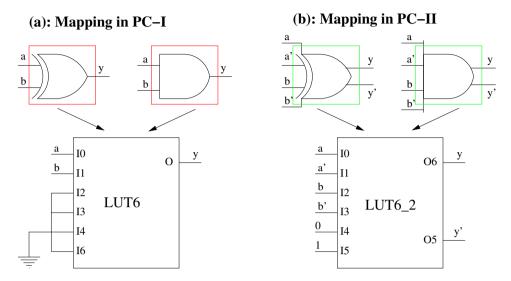

|    |             | 8.2.1 PC-I in FPGA, for $k = 1$                                                |           |

|    |             | 8.2.2 PC-II in FPGA, for $k = t = 1$                                           |           |

|    |             | SIMON 96/96 in Private Circuits II                                             |           |

|    |             | 8.2.4 Synthesis results for PC-I and PC-II in Xilinx Spartan 6.                |           |

|    | 8.3         | Security analysis of PC-II with $k = t = 1$                                    |           |

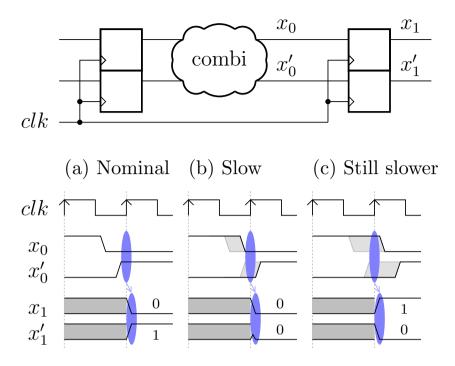

|    |             | 8.3.1 Setup time violations                                                    | 175       |

|    |                                                                    | 8.3.2    | Timing faults on PC-II with $t = 1 \dots \dots \dots \dots \dots$ | 176 |  |  |  |  |

|----|--------------------------------------------------------------------|----------|-------------------------------------------------------------------|-----|--|--|--|--|

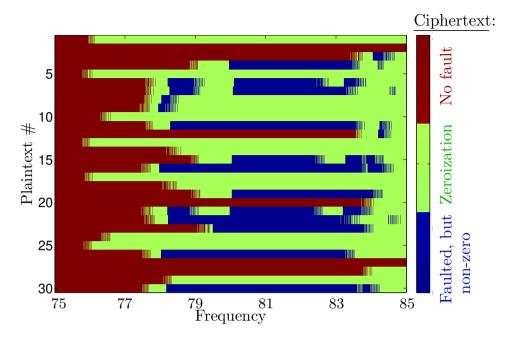

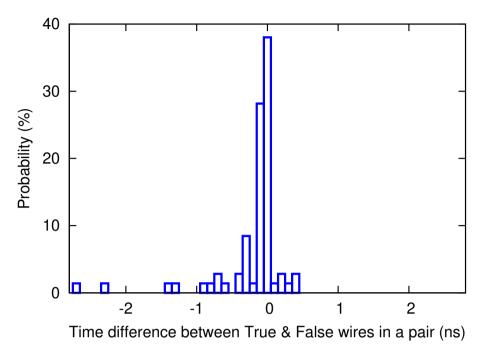

|    | 8.4                                                                | Evalua   | ation using faults                                                | 178 |  |  |  |  |

|    |                                                                    | 8.4.1    | Experiment setup                                                  | 178 |  |  |  |  |

|    |                                                                    | 8.4.2    | Internal and online debug of fault effects                        | 178 |  |  |  |  |

|    |                                                                    | 8.4.3    | Results                                                           | 179 |  |  |  |  |

|    |                                                                    | 8.4.4    | Discussion                                                        | 183 |  |  |  |  |

|    | 8.5                                                                | Concl    | usion and perspectives                                            | 184 |  |  |  |  |

| 9  | Using Modular Extension to Provably Protect Edwards Curves Against |          |                                                                   |     |  |  |  |  |

|    | Faul                                                               | t Attacl | ks                                                                | 187 |  |  |  |  |

|    | 9.1                                                                |          | luction                                                           | 187 |  |  |  |  |

|    | 9.2                                                                | Existi   | ng Countermeasures for ECC                                        | 191 |  |  |  |  |

|    | 9.3                                                                | Securi   | ity Analysis of Modular Extension                                 | 191 |  |  |  |  |

|    | 9.4                                                                | Edwa     | rds Curves over large-characteristic fields                       | 194 |  |  |  |  |

|    |                                                                    | 9.4.1    | Edwards curves                                                    | 194 |  |  |  |  |

|    |                                                                    | 9.4.2    | Twisted Edwards curves                                            | 194 |  |  |  |  |

|    | 9.5                                                                | Practi   | cal Study                                                         | 195 |  |  |  |  |

|    |                                                                    | 9.5.1    | Edwards curves                                                    | 197 |  |  |  |  |

|    |                                                                    | 9.5.2    | Twisted Edwards curves                                            | 198 |  |  |  |  |

|    |                                                                    | 9.5.3    | Discussion                                                        | 199 |  |  |  |  |

|    | 9.6                                                                | Perfor   | mance                                                             | 200 |  |  |  |  |

|    |                                                                    | 9.6.1    | Edwards curve example                                             | 200 |  |  |  |  |

|    |                                                                    | 9.6.2    | Twisted Edwards curve example: Curve25519 / Ed25519               | 201 |  |  |  |  |

|    |                                                                    | 9.6.3    | Comments about results                                            | 202 |  |  |  |  |

|    | 9.7                                                                | Concl    | usions                                                            | 203 |  |  |  |  |

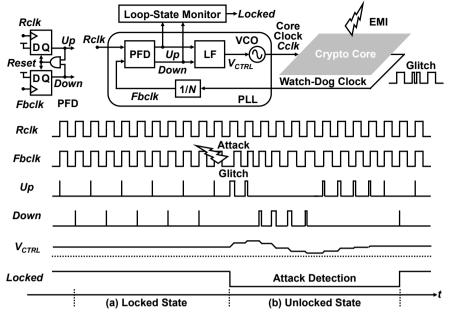

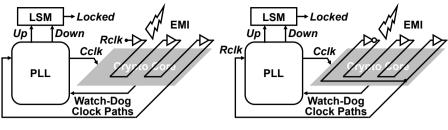

| 10 | A no                                                               | vel phy  | ysical EM Fault coutermeasure                                     | 205 |  |  |  |  |

|    | 10.1                                                               | Introd   | luction                                                           | 205 |  |  |  |  |

|    | 10.2                                                               | PLL-B    | Based EMI Countermeasure                                          | 207 |  |  |  |  |

|    |                                                                    | 10.2.1   | Concept                                                           | 207 |  |  |  |  |

|    |                                                                    | 10.2.2   | Implementation Details                                            | 209 |  |  |  |  |

|    | 10.3                                                               | Desig    | n Automation                                                      | 211 |  |  |  |  |

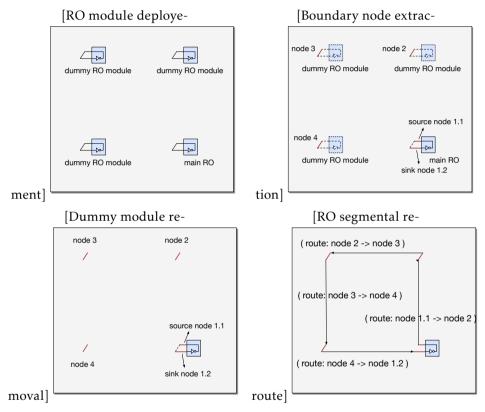

|    |                                                                    | 10.3.1   | Controllable RO Routing Flow                                      | 211 |  |  |  |  |

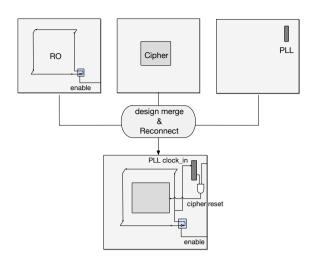

|    |                                                                    |          | Co-Integration Flow of Sensor and Crypto Core                     |     |  |  |  |  |

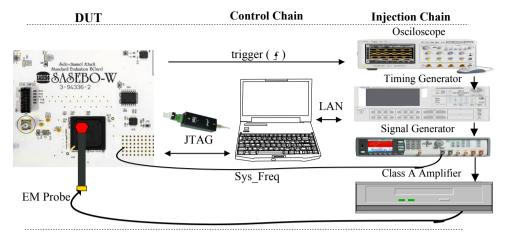

|    | 10.4                                                               | Exper    | imental Evaluation                                                | 215 |  |  |  |  |

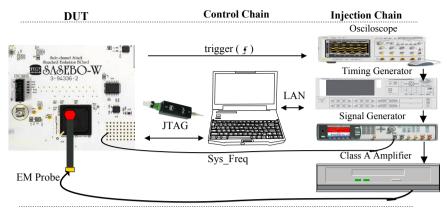

|    |                                                                    | 10.4.1   | Experimental Setup                                                | 215 |  |  |  |  |

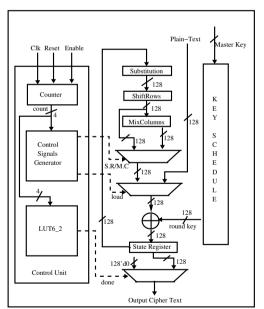

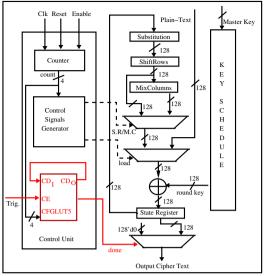

|    |                                                                    | 10.4.2   | Target Circuit                                                    | 215 |  |  |  |  |

|    |                                                                    | 10.4.3   | Experimental Results                                              | 217 |  |  |  |  |

|    |                                                                    | 10.4.4   | Discussion                                                        | 218 |  |  |  |  |

|    | 10.5                                                               | Concl    | usions                                                            | 219 |  |  |  |  |

| 11 | Reconfigurable LUT: A Double Edged Sword for Security-Critical Ap- |                                                            |     |  |  |  |

|----|--------------------------------------------------------------------|------------------------------------------------------------|-----|--|--|--|

|    | plications                                                         |                                                            |     |  |  |  |

|    | 11.1 Introduction                                                  |                                                            |     |  |  |  |

|    | 11.2                                                               | Rationale of the RLUT                                      | 223 |  |  |  |

|    |                                                                    | 11.2.1 Comparison With Dynamic Configuration               | 225 |  |  |  |

|    |                                                                    | 11.2.2 RLUT and Security                                   | 226 |  |  |  |

|    | 11.3                                                               | Destructive Applications of RLUT                           | 226 |  |  |  |

|    |                                                                    | 11.3.1 Adversary Model                                     | 227 |  |  |  |

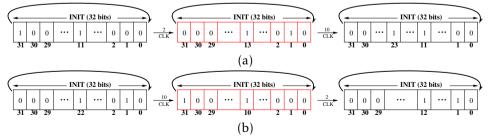

|    |                                                                    | 11.3.2 Trigger Design the Hardware Trojans                 | 229 |  |  |  |

|    |                                                                    | 11.3.3 Trojan Description                                  | 229 |  |  |  |

|    | 11.4                                                               | Constructive Applications for RLUT                         | 235 |  |  |  |

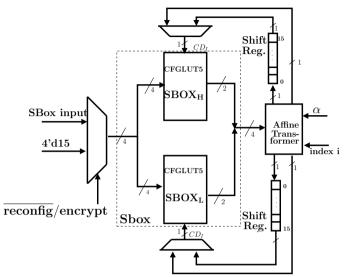

|    |                                                                    | 11.4.1 Customizable Sboxes                                 | 235 |  |  |  |

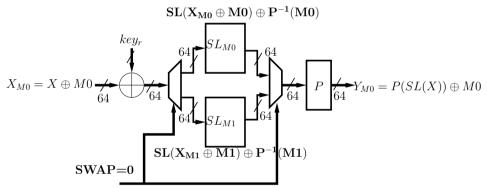

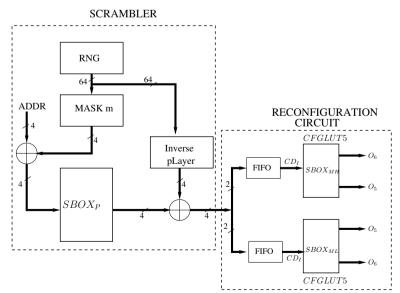

|    |                                                                    | 11.4.2 Sbox Scrambling for DPA Resistance                  | 237 |  |  |  |

|    | 11.5                                                               | Conclusions                                                | 240 |  |  |  |

|    |                                                                    |                                                            |     |  |  |  |

| V  | See                                                                | curity design principles                                   | 241 |  |  |  |

| 12 | Secu                                                               | rity <i>is</i> an Architectural Design Constraint          | 245 |  |  |  |

|    | 12.1                                                               | Introduction                                               | 245 |  |  |  |

|    | 12.2                                                               | Primitive Level                                            |     |  |  |  |

|    |                                                                    | 12.2.1 Public Key Cryptography                             |     |  |  |  |

|    |                                                                    | 12.2.2 Post Quantum Public Key Cryptography                |     |  |  |  |

|    |                                                                    | 12.2.3 Symmetric Key Cryptography                          | 253 |  |  |  |

|    | 12.3                                                               | Protocol Level                                             | 255 |  |  |  |

|    |                                                                    | 12.3.1 Data compression techniques used in TLS protocol    | 255 |  |  |  |

|    |                                                                    | 12.3.2 Attacks on the encryption mode used in TLS protocol | 256 |  |  |  |

|    | 12.4                                                               | System Level                                               | 257 |  |  |  |

|    |                                                                    | 12.4.1 Hardware Security                                   |     |  |  |  |

|    |                                                                    | 12.4.2 Software Security                                   |     |  |  |  |

|    |                                                                    | 12.4.3 Hardware/Software Interface Security                |     |  |  |  |

|    |                                                                    | Proposal for a Security Aware Design Flow                  |     |  |  |  |

|    | 12.6                                                               | Conclusion                                                 | 267 |  |  |  |

| V  | Γ <b>Λ</b>                                                         | pplication of design guidelines: Lightweight ciphers       |     |  |  |  |

|    |                                                                    | implementations                                            | 269 |  |  |  |

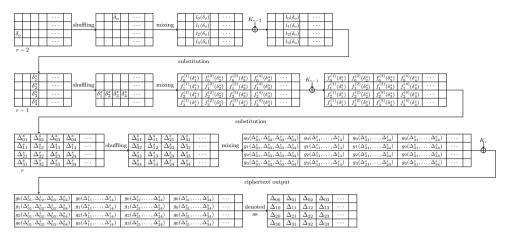

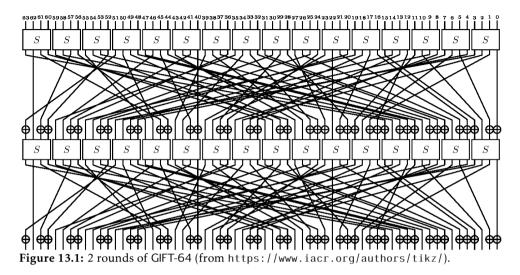

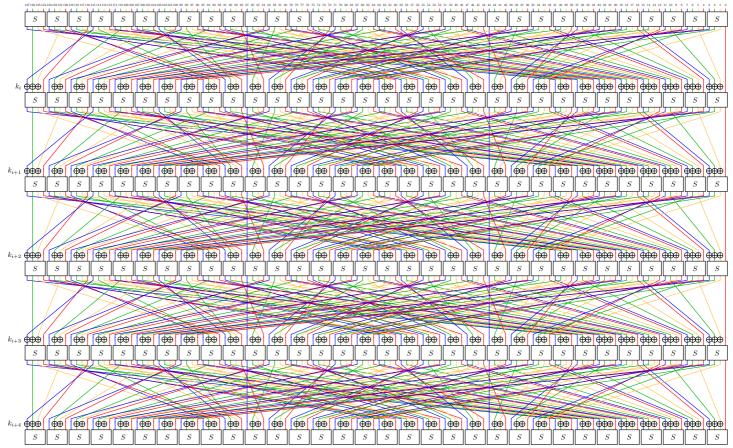

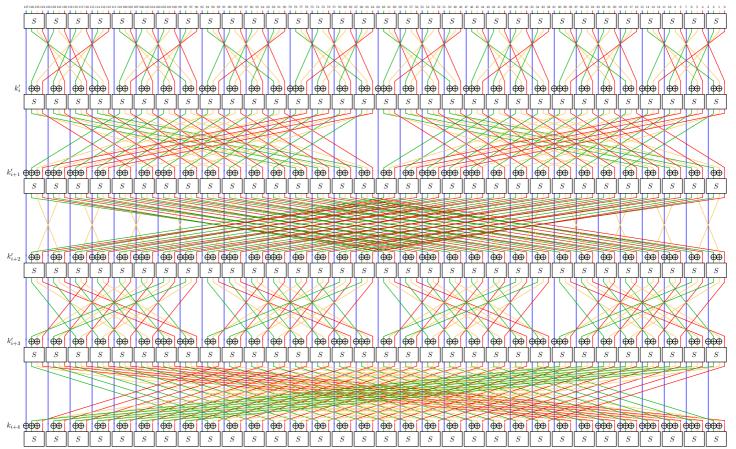

| 13 | Fixsl                                                              | licing: A New GIFT Representation                          | 273 |  |  |  |

|    |                                                                    | Introduction                                               |     |  |  |  |

|    |                                                                    | The GIFT family of block ciphers                           |     |  |  |  |

|    |                                                                    | 13.2.1 Round function                                      |     |  |  |  |

|         | 13.2.2 Key schedule and round constants      | 279 |

|---------|----------------------------------------------|-----|

| 13.     | -                                            | 280 |

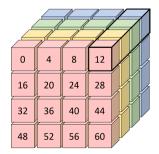

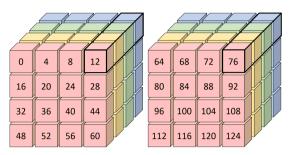

| 13.     | 4 A new GIFT representation                  | 282 |

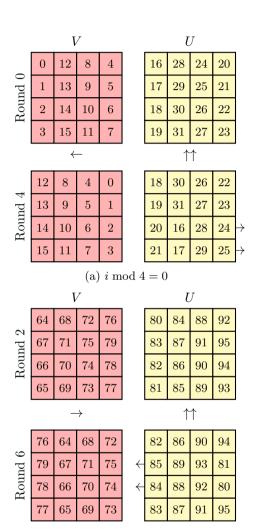

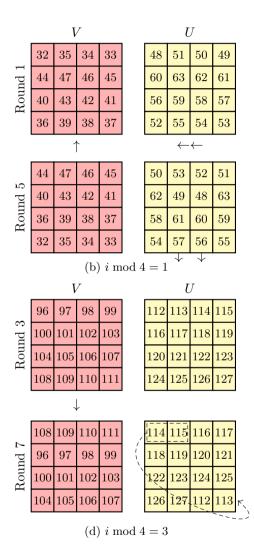

|         | 13.4.1 GIFT-64                               | 282 |

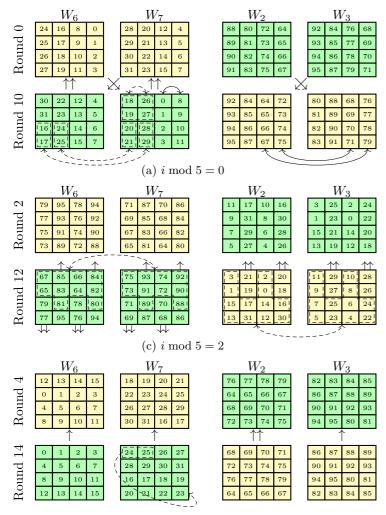

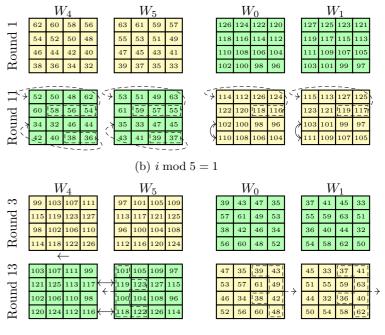

|         | 13.4.2 GIFT-128                              | 285 |

| 13.     | 5 Efficient software implementations of GIFT | 289 |

|         | 13.5.1 GIFT-64                               | 290 |

|         | 13.5.2 GIFT-128                              | 291 |

|         | 13.5.3 Without rotate instruction            | 292 |

| 13.     | 6 Results                                    | 293 |

|         | 1                                            | 293 |

|         | 0                                            | 295 |

|         | 1                                            | 296 |

| 13.     | 7 Conclusion                                 | 296 |

|         |                                              |     |

| VII     | Conclusion                                   | 301 |

|         |                                              |     |

|         |                                              | 303 |

|         |                                              | 303 |

| 14.     | 2 Reflection and future work                 | 311 |

| Ackno   | wledgements                                  | 315 |

|         |                                              |     |

| Biogra  | phy                                          | 317 |

|         |                                              |     |

| List of | Publications                                 | 318 |

| Refere  | n cas                                        | 322 |

| Refere  | inces                                        | 522 |

|         |                                              |     |

| VIII    | Appendix                                     | 355 |

| 15 C    | hapter5                                      | 356 |

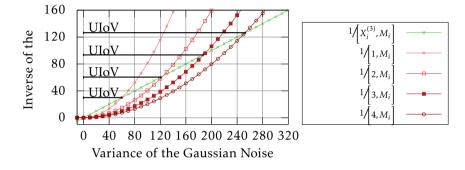

| .1      | *                                            | 356 |

| .2      | Proof of the propositions of Sect. 5.4.5     | 360 |

|         |                                              | 360 |

|         |                                              | 360 |

|         | *                                            | 360 |

| .3      |                                              | 361 |

| .4      | Affine model                                 | 362 |

|         | A Proof of Lemma 5.6.1                       | 362 |

|         |                                              |     |

| В       | Proof of the Theorem 5.6.3                                                                                 | 363                        |

|---------|------------------------------------------------------------------------------------------------------------|----------------------------|

| С       | Proof of Corollary 5.6.3                                                                                   | 364                        |

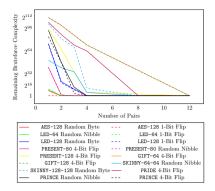

| Chap    | oter7                                                                                                      | 366                        |

| SPN vs  | S DFA: Good Design Practices                                                                               | 366                        |

| More (  | Case Studies to our Techniques                                                                             | 367                        |

| А       | PRESENT-128 and Practical Implementations of PRESENT:                                                      |                            |

|         | Finding Optimal DFA Attack                                                                                 | 367                        |

| В       | GIFT-64: New Results                                                                                       | 368                        |

| С       | GIFT-128: New Results                                                                                      | 370                        |

| D       | PRIDE: Finding Optimal DFA Attack                                                                          | 370                        |

| Proofs  | for Section 7.3                                                                                            | 371                        |

| Chap    | oter11                                                                                                     | 374                        |

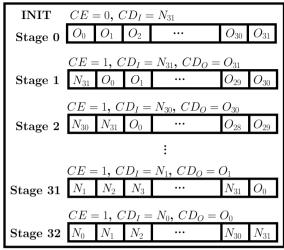

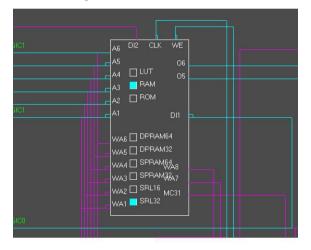

| Trigger | r generation for Hardware Trojans                                                                          | 374                        |

| Chap    | oter13                                                                                                     | 375                        |

| Key sc  | hedule in the fixsliced representation                                                                     | 375                        |

| А       | GIFT-64                                                                                                    | 375                        |

| В       | GIFT-128                                                                                                   | 375                        |

| Additi  | onal illustrations                                                                                         | 379                        |

|         | C<br>Chap<br>SPN vs<br>More C<br>A<br>B<br>C<br>D<br>Proofs<br>Chap<br>Trigget<br>Chap<br>Key sc<br>A<br>B | C Proof of Corollary 5.6.3 |

# Ι

## INTRODUCTION

# 1

## INTRODUCTION

#### **1.1.** BACKGROUND

In today's digital age, data has taken on a new level of significance and has even been referred to as the new gold or new oil [1]. This is due to the increasing value placed on data as an indispensable asset in the digital economy. The ability to store, process, and analyze vast amounts of data has made it possible to gain insights and make informed decisions, creating new opportunities and driving innovation across various industries. However, the abundance of data also creates new challenges, including protecting sensitive information from unauthorized access, theft, and manipulation. Cryptography provides a powerful solution for securing data and ensuring stored and transmitted information's confidentiality, integrity, and authenticity. Cryptographic methods are applied at every data lifecycle stage, from collection and storage to transmission and usage. The demand for cryptography and encryption has risen across various industries, such as finance, healthcare, and government, and is expected to continue growing in the future [2]. The proliferation of communication networks and connected devices, such as the Internet of Things (IoT), has increased the risk of attacks on these systems, which store and handle sensitive information. As such the importance of cryptography in ensuring the security of sensitive information in the digital world cannot be overstated. The fundamental components of cryptography, known as cryptographic algorithms, serve to assure the confidentiality, integrity, and authenticity of stored or communicated data. Key generation primitives, hashing, and encryption primitives make up these algorithms. Key generation primitives generate unique digital keys for encryption and decryption processes, often using a random number generator. Hashing primitives generate a fixed-length hash from a variable-length input, ensuring data integrity by detecting any modifications to the original. Encryption primitives scramble data, rendering it unreadable without the proper decryption key, preserving confidentiality. These primitives provide the secure foundation for cryptography and are utilized in various cryptographic protocols to guard against unauthorized access, tampering, and exposure.

Moreover, cryptographic algorithms were traditionally designed based on the designers' experience and intuition rather than solid mathematical proof. The security of these algorithms was evaluated using generic techniques such as brute force attacks or linear and differential cryptanalysis. However, these techniques may only sometimes give a comprehensive or accurate understanding of an algorithm's security.

The practicality of security is often guided by experience and intuition, while mathematical proofs offer a theoretical sense of security. These two ideas of security can sometimes conflict. For example, two groups emerged with differing approaches to lattice-based schemes during the NIST post-quantum cryptography competition. The first group focused on provably secure schemes that relied on Gaussian sampling. However, these schemes were found to be costly to implement and challenging to protect against side-channel attacks. In contrast, the second group employed uniform sampling-based schemes, which, although lacking provable security, were demonstrated to be less expensive to implement and easier to secure against side-channel attacks [3]. This situation raises a critical question for the field: Should we prioritize the development of systems with ease of security proof, or should we favor schemes that have been empirically shown to be practical and secure?

In the context of cryptographic system design, it is generally preferred to use schemes empirically shown to be secure rather than those with only provable security. However, that is difficult to implement and protect against side-channel attacks. This is because practical security is a critical consideration in real-world applications, and security proof is only one aspect of overall security.

However, using schemes with provable security is still highly valuable in situations where security is paramount, such as in highly sensitive military or government applications. In such cases, the additional security provided by a provably secure scheme may be worth the added implementation complexity and resource usage.

Therefore, the choice of which scheme to use ultimately depends on the application's specific requirements, as well as the available resources and constraints. While schemes with provable security may have their drawbacks, they are still a vital area of research and development in cryptography. An example of empirically secure ciphers widely used in practice is the arithmeticbased non-linear operation ciphers, such as SHA-1 and CHACHA-poly-20. While these schemes have been demonstrated to be secure in practice and highly efficient, they are challenging to formalize. Therefore, they have not received as much attention from researchers as Boolean Pseudo-Random Functions (PRF) based ciphers [4]. However, the attractiveness of PRF-based ciphers has led to extensive research and publication, which ultimately contributes to an additional level of trust in the security of these schemes.

Cryptographic algorithms are mathematical procedures used for the encryption and decryption of data. They form the foundation of secure communication by transforming plaintext data into ciphertext, rendering it unreadable to unauthorized parties. Examples of cryptographic algorithms include symmetric algorithms like Advanced Encryption Standard (AES) and asymmetric algorithms like RSA.

On the other hand, cryptographic protocols are sets of rules and procedures that govern the secure exchange of information between parties using cryptographic algorithms. Protocols define how the algorithms are to be used, including the generation, distribution, and management of cryptographic keys and handling authentication, confidentiality, and integrity of messages. Examples of cryptographic protocols include Secure Sockets Layer (SSL), Transport Layer Security (TLS), and Pretty Good Privacy (PGP).

Cryptographic algorithms provide the mathematical foundation for encryption and decryption, while cryptographic protocols establish a structured framework for secure communication that leverages these algorithms. By introducing both concepts on page three, readers will clearly understand their distinct roles and how they work together to ensure secure data transmission.

The field of cryptography is in a state of constant evolution. As a result, new weaknesses and security breaches are frequently uncovered that can render cryptographic algorithms and protocols vulnerable.

Regular updates, as well as solid underlying infrastructure, are essential to maintain their security. The recent developments in quantum computing have the potential to break many of the encryption algorithms widely used today, making it essential to research and develop post-quantum cryptographic algorithms that are secure against quantum computers. These post-quantum algorithms are expected to be more robust and secure than current algorithms and will be crucial in maintaining the security of digital communication and transactions in the future [5].

The shift to post-quantum cryptography requires a thorough and well-planned approach that involves a range of stakeholders, including researchers, industry leaders, and government agencies. The transition is a complex and multi-faceted pro-

cess that entails updating the cryptographic algorithms and the underlying hardware, software, and communication protocols that support these algorithms. To ensure a smooth and successful transition, it is imperative to take into consideration the far-reaching implications it will have on digital communication and transactions and to implement measures that will minimize any potential risks and disruptions during the process.

As the field of cryptography evolves, and new attacks and vulnerabilities are discovered, security models for cryptographic algorithms and protocols become more complex. Indeed, a security model is a mathematical representation of the cryptographic algorithm or protocol and the environment in which it is used. It describes the assumptions and requirements that must be met for the algorithm or protocol to be considered secure. As the gap between theory and practice is studied, security models for cryptographic algorithms and protocols become more complex and consider a broader range of attack scenarios and potential vulnerabilities. This can make it more challenging to analyze and evaluate the security of a given algorithm or protocol. However, it is necessary to ensure that security is robust against all known and potential attacks.

It is crucial to develop methods to assess security and identify bugs that could affect the security of an implementation. There are several methods that can be used to assess the security of cryptographic algorithms and protocols. These are mathematical analysis, formal verification, and testing. The mathematical analysis involves using mathematical proofs and models to show that an algorithm or protocol is secure under a given set of assumptions. Formal verification uses mathematical proof systems to prove that an algorithm or protocol satisfies specific properties. Testing involves running the algorithm or protocol in a simulated or natural environment to identify bugs or weaknesses.

It is important to note that no single method can guarantee the security of an algorithm or protocol. Instead, a combination of methods is often used to provide a comprehensive assessment of the security of an algorithm or protocol. In addition, it is also essential to conduct regular security audits of the implementation of cryptographic algorithms and protocols to identify any bugs that may affect security. This can include a manual review of the code and automated testing of the implementation to identify any vulnerabilities or weaknesses. In summary, a methodology that combines mathematical analysis, formal verification, testing, and security audits is essential to ensure the security of cryptographic algorithms and protocols. The implementation of a cryptographic primitive may result in the leakage of secret information during computation through side-channels. Side-channels are unintended information channels that can leak sensitive information about the implementation of an algorithm. Examples of side-channels are power consumption, electromagnetic radiation, and timing information. Attackers can use these side-channels to extract secret keys or other sensitive information by measuring the physical characteristics of the implementation. Another way to attack an implementation is the active side-channel attack, where an attacker actively disrupts the computation of the algorithm to leak secrets. With the rapid evolution of technology and advances in cryptanalysis research, older cryptographic primitives such as SHA-1 are showing their limitations. SHA-1 is a cryptographic hash function widely used in the past for digital signatures and other applications requiring data integrity and authenticity. Researchers have discovered new attacks that can effectively break SHA-1 and make the cryptographic hash function vulnerable to collisions. As a result, the use of SHA-1 has been deprecated, and experts recommend using more powerful cryptographic hash functions like SHA-2 or SHA-3. It is important to note that cryptographic primitives have a limited lifetime and must be regularly reviewed and updated to maintain their security. The gap between theory and practice in cryptography can create potential security problems. Researchers focus on theoretical topics, while practitioners focus on providing standards-compliant implementations. This can lead to a situation where disproportionate theoretical security margins are used. In contrast, hackers can, in some situations, easily exploit side-channel weaknesses in the implementation to break the cryptosystem, regardless of the theoretical security margins.

The security margin for a cryptographic algorithm is defined by the difference between the current best-known attack against the algorithm and the theoretical maximum security provided by the algorithm, usually expressed in terms of computational steps or resources required for the attack.

In simpler terms, the security margin is a measure of how resistant an algorithm is to attacks, and it is used to gauge the overall security of a cryptographic system. A larger security margin indicates that an algorithm is more secure, as it would require significantly more time, computational power, or other resources for an attacker to break it.

The security margin depends on various factors, including:

Key size: A larger key typically provides a higher security margin, as it increases the number of possible keys, making it more difficult for an attacker to guess the correct Key through brute force.

Algorithm design: Some cryptographic algorithms are inherently more secure than others due to their design and resistance to known attacks, such as differential or linear cryptanalysis.

Implementation: The security of a cryptographic algorithm can also depend on the quality of its implementation, including how well it resists side-channel attacks or other implementation-specific vulnerabilities.

Attack complexity: The amount of time, computational resources, or other resources required for an attacker to successfully break the algorithm. The higher the complexity, the larger the security margin.

State-of-the-art attacks: The current best-known attacks against a specific cryptographic algorithm. As new attacks are discovered, or existing attacks are improved, the security margin of an algorithm may decrease.

In practice, the security margin is often estimated based on the current state of cryptographic research and attack techniques, and it is subject to change as new attacks are discovered or existing attacks are refined. For bloc cipher, it is referred to as the number of extra computation rounds for which the claimed security bound still holds even if they are removed.

For example, AES has a security margin of three to four rounds in single-key setting, excluding the biclique attack, meaning that if one round is attacked, the attacker would still have to attack two to three rounds and start to erode the security claims. A security margin of three to four rounds in the context of a block cipher refers to the number of additional rounds of encryption that would need to be successfully attacked by an adversary beyond any compromised rounds for the cipher's security to be significantly weakened.

For example, if a block cipher has ten rounds, and an attacker successfully compromises one round, the remaining security margin would be nine rounds. In the case of a security margin of three to four rounds, the attacker would need to compromise an additional two to three rounds (in addition to the one already compromised) before the overall security of the cipher is significantly weakened.

This security margin is a measure of the strength of the block cipher against attacks and is an important consideration in the evaluation of cryptographic algorithms. Generally, a higher security margin provides greater confidence in the cipher's security.

It is important to note that a time-memory trade-off determines the security of a block cipher. As a result, a reduction in time complexity without a corresponding decrease in data or memory complexity may not significantly impact the cipher's overall security claims.

A biclique attack is a type of cryptanalytic attack that targets block ciphers, which are symmetric key cryptographic algorithms operating on fixed-size data blocks. The biclique attack was first introduced by Andrey Bogdanov, Dmitry Khovratovich, and Christian Rechberger in 2011 to improve the known attacks on the Advanced Encryption Standard (AES).

The biclique attack is based on partitioning the cipher into two parts and finding

a so-called "biclique," a set of keys that allows an attacker to bypass some of the intermediate computations in the cipher. By doing this, the attacker can significantly reduce the overall computational complexity of an exhaustive Key search, making the attack more efficient than a brute-force attack.

In the case of AES, the biclique attack reduced the computational complexity of key recovery by a minor factor. However, it is essential to note that the practical impact of the biclique attack on AES is quite limited. The attack still requires enormous computational power to succeed, and more than a reduction in complexity is needed to make AES insecure for most applications. While the biclique attack is a noteworthy development in cryptanalysis, its practical implications are relatively limited for well-designed cryptographic algorithms like AES. As of the time of writing, there are still questions regarding the real-world impact of such attacks in terms of their practical implementation using state-of-the-art technologies.

It is noteworthy that new properties of AES continue to be uncovered. For instance, the novel representations of the AES key schedule by Leurent and Pernot [6] were only recently described, nearly two decades after its initial analysis [7].

The attack serves as a reminder that the cryptographic community must continually research and develop new methods to ensure the long-term security of encryption algorithms ranks depending on the version, and AES 128 requires about  $2^{128}$  evaluations to be attacked under a single key, which is considered infeasible for the foreseeable future. However, a cache-timing attack and other forms of sidechannel attacks can recover the secret Key of a vulnerable AES implementation in just a few minutes [7].

Professionals frequently need to utilize obsolete standards despite the lack of proof concerning any associated risks. Deprecated primitives that are unused but remain in implementations for compatibility purposes can be detected. This practice exposes a vulnerability that hackers could exploit in downgrade attacks, given how algorithm types are used in libraries. Understanding the hazards of using such algorithms is crucial for advancing the field. One way to achieve this is by demonstrating the feasibility and cost of potential attacks. This highlights the importance of bridging the gap between practitioners and theorists of cryptography. Theoretical research needs to be more closely linked to practical implementation, and practitioners need to understand the theoretical underpinnings of cryptography better to ensure secure implementations. One way to bridge this gap is to involve practitioners in developing and analyzing cryptographic algorithms and protocols at an early stage. This will align theoretical research more closely with practical implementation and ensure greater security of applications. Another way to bridge the gap is to include more practical evaluation and testing of cryptographic implementations, including side-channel vulnerability testing, in the development

process. This will ensure that implementations are secure not only in theory but also in practice.

To conclude, bridging the divide between cryptographic practitioners and theorists is crucial to ensure that cryptographic implementations are secure in practice and theory.

This study adopts a practical and pragmatic approach to enhancing the security of real-world systems. By examining the costs associated with various attack types, including the complexity of the attack and the resources required, the study aims to establish a better balance between security, performance, and cost in cryptography. Moreover, the study evaluates several countermeasure schemes designed to enhance the security of embedded systems and connected devices while considering real-world limitations and cost-effectiveness. Additionally, the thesis provides a comprehensive review of the current state of cryptography, including cryptographic primitives, protocols, and the challenges and constraints of existing cryptographic algorithms. We also discuss the post-quantum cryptography topic and its challenges and opportunities, offering recommendations for organizations and individuals in the transition. Overall, this thesis seeks to advance the understanding of practical trade-offs and security margins in cryptographic standards, ultimately contributing to developing robust and secure systems that balance performance and cost.

#### **1.2.** Problem statement and Research questions

This thesis focuses on the gap between cryptography theory and practice. Understanding the differences in how cryptographic algorithms are implemented and executed is critical to designing secure cryptosystems, especially in today's digital age, where the use of technology such as IoT devices, Edge computing, decentralized cloud, and blockchains is widespread. Efficient cryptosystem design is crucial as even small variations at the device or node level can have a significant impact when billions of devices or nodes are connected and exchanging data.

In this thesis, various aspects of Cryptanalysis (in Part II), Passive Side-Channel Attacks and Countermeasures (in Part III), Active Side-Channel Attacks (also known as Fault Attacks) and Countermeasures (in Part IV), and Secure Lightweight Implementations (in Part VI) are examined.

The objective is to address key questions in the field and provide a comprehensive conclusion that takes a broad view of security issues in cryptographic algorithms and suggests a framework for incorporating security into the product design process.

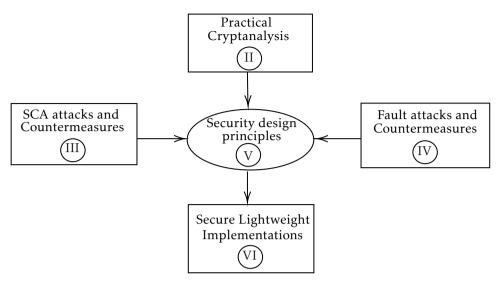

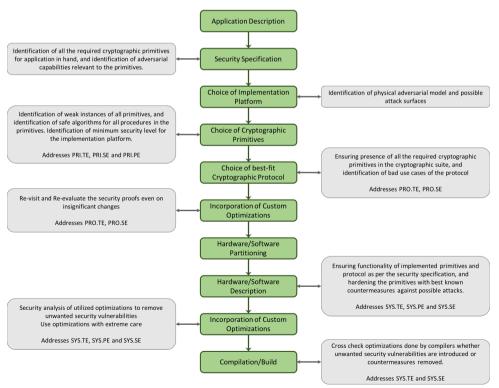

Figure 1.1: Thesis structure chart

The vastness of security means that not all aspects can be covered in this Ph.D. thesis. Nevertheless, we can redefine security from a designer's perspective by studying various topics and evaluating the current state-of-the-art. This can lead to developing a security-aware design flow that designers can utilize to achieve their desired security objectives.

#### **1.2.1.** Scope

The Figure 1.1 illustrates the scope of this Ph.D. thesis. Please note that the ellipse at the center labeled "Security design principles" pertains to establishing a set of guidelines and design principles based on a thorough security analysis from a designer's perspective. The edges of the graph depict the security constraints. The Ph.D. thesis considers three constraints: Cryptanalysis-based attacks, Passive Side-Channel Attacks, and Active Side-Channel Attacks.

In Part II, Part III, Part IV of this doctoral dissertation, a dual approach is taken to scrutinize various attacks and countermeasures from both the attacker and designer perspectives. The investigation assesses the efficacy and constraints of these measures, with particular emphasis on distinguishing between their theoretical and practical implications.

Design guidelines are established based on the three considered constraints and a review of the existing literature. These guidelines form the basis for a proposed security-aware design flow aimed at introducing more rigor in the design process

for applications that require protection against the three attack vectors.

The proposed security-aware design flow is demonstrated in a real-world scenario, specifically implementing and evaluating various contenders in the NIST Lightweight Cipher competition. The methodology was initially applied to the microcontroller implementation of the GIFT family of block ciphers and was later extended to AES [8], demonstrating its genericity.

Having outlined the thesis's scope, we will elaborate on each aspect and present the research questions.

#### **1.2.2.** The Practical Cryptanalysis (Part II)

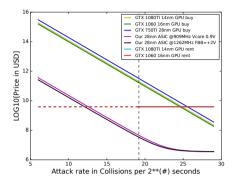

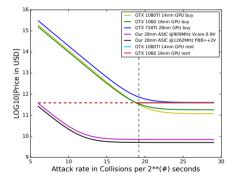

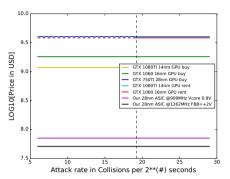

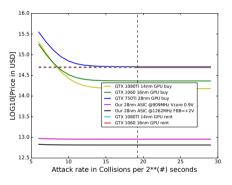

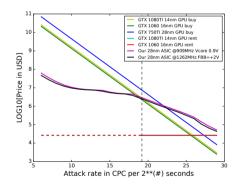

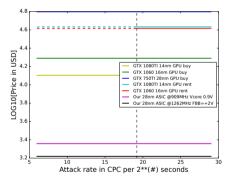

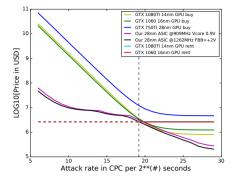

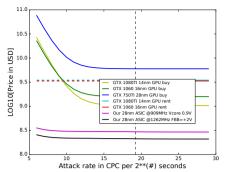

This section explores the practical aspects of differential cryptanalysis attacks. It sheds light on the cost of a differential cryptanalysis attack when the cipher's security is near or below the 80-bit security threshold. We recognize that cryptographic methods are constantly evolving, and determining the level of security provided by encryption is an ever-changing challenge. While 80-bit encryption is generally sufficient for most applications, highly sensitive or critical applications may require higher security, such as a minimum of 128-bit encryption. Despite its claimed security level of 80 bits, the SHA-1 algorithm was still widely used in various applications and website certificates at the start of this Ph.D. thesis. As shown by Leurent et al. (2020), about 30% of the certificates on the internet still supported SHA-1, highlighting the need for regular security assessments and updates to ensure adequate protection. Understanding the cost of a chosen-prefix collision attack on the SHA-1 algorithm through ASICs and GPUs provides insight into the cost of differential cryptanalysis attacks on ciphers with 80-bit security or lower, which are still widely used in low latency and resource-constrained applications such as IoT and sensor networks where side-channel attacks pose a risk. In Chapter chapter 3, we enhance the understanding of the cost of a collision attack on SHA-1 by executing the first chosen-prefix collision on SHA-1 with the use of GPUs and designing the first SHA-1 Chosen-prefix collision ASIC, providing a precise estimate of the attack cost when using ASICs. This knowledge enables more informed choices in selecting secure cryptographic methods and protocols for real-world applications with strict constraints by setting more meaningful security margins. The following research question is addressed in this part:

**RQ1:** What is the actual cost of a differential cryptanalysis attack when the cipher's security is near or below the 80-bit security threshold?

#### **1.2.3.** Passive Side-Channel Attacks and Countermeasures (Part III)

This part explores the practical aspects of preventing side-channel attacks in embedded systems and IoT devices. The security of these devices is not only dependent on their ability to withstand cryptanalysis but also on their resistance to passive and active side-channel attacks. In situations where the device is low on power or requires low latency, side-channel attacks may pose a greater risk than more complex attack methods. Various countermeasures can be employed to prevent passive side-channel attacks, including masking. However, implementing a countermeasure requires balancing execution time and memory usage and preserving the security properties of the masking scheme. The masking order and the signal-to-noise ratio determine a masking scheme's security.

Linear operations in symmetric encryption have been shown to be highly susceptible to side-channel attacks due to their confusion properties, while non-linear operations are fundamental to symmetric encryption. Implementing boolean S-boxes in software can be expensive, and table-based implementations are vulnerable to timing side-channel attacks. Although boolean S-boxes can be naturally masked, arithmetic S-boxes may provide additional security benefits over boolean S-boxes like those used in AES. Masking arithmetic operations such as addition, subtraction, multiplication, and division can be computationally expensive and negatively impact cryptographic implementation performance, particularly for those requiring many arithmetic operations. Masking requires converting arithmetic operations to boolean operations, a resource-intensive process involving performing boolean operations on individual bits of operands and merging the boolean results to produce the masked output.

ChaCha20, an arithmetic addition-based cipher, has emerged as an AES alternative due to its ease of software implementation and ability to deliver constant-time implementation advantages. It would be interesting to explore whether ChaCha20 provides any advantage against side-channel attacks without masking.

Therefore, this part addresses the question:

RQ2: How can we practically prevent side-channel attacks?

#### 1.2.4. Active Side-Channel Attacks and Countermeasures (Part IV)

The Part IV is dedicated to fault injection attacks and their impact on block ciphers and asymmetric cryptography. What methods or techniques can be employed to detect and prevent practical fault attacks? The precision of the attacker plays a crucial role in determining the success of these attacks. The two most common methods for inducing faults on a cryptosystem are using a laser beam or power glitches. However, using lasers may only sometimes be possible due to counter-

measures like light sensors. Power glitches can also be prevented with an on-chip DC-DC converter. Data path and time redundancy, achieved through codes or duplication, is another option, but it has limitations and can be costly. This is why the focus has shifted towards Electromagnetic Fault Injection (EMFI) attacks, which can be carried out with good time-space accuracy without opening the chip, and can induce complex high-order fault models.

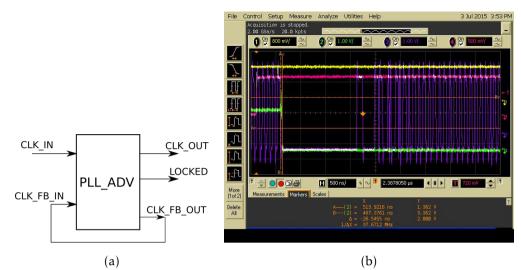

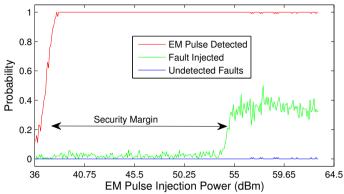

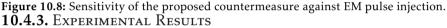

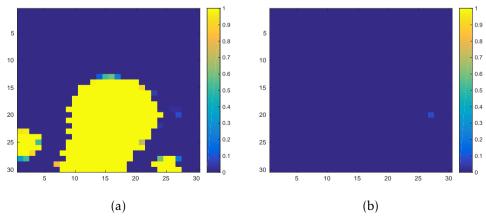

Can electromagnetic fault injection (EMFI) detection and prevention be achieved without data-path time-space redundancy? An unreported behavior of the phaselocked loop (PLL) phase detector sensor exposed to EMFI was discovered through experimentation. A novel countermeasure is examined and assessed based on this behavior against EMFI.

Once a realistic fault model has been established, the identification of potential associated attacks by the cryptographer becomes necessary. These attacks are cipherspecific and are investigated on a case-by-case basis. To the best of our knowledge, no general framework exists to assess a cipher's vulnerability to faults provided a fault model.

A Differential Fault Attack (DFA) is a type of fault injection attack that involves intentionally introducing faults into a cryptographic implementation by altering its input or internal state. The attacker then observes the output of the faulty implementation to infer secret information, such as the secret Key used in a symmetric cipher or the private Key used in a public-key cryptosystem.

Given a fault model, how can we assess the inherent resistance of a block cipher against fault attacks? Understanding the factors that make a cipher more resilient to these attacks is valuable for improving system protection. This thesis seeks to contribute to finding an answer to this question by conducting a case study on DFA.

While physical countermeasures can enhance system security, combining them with logical countermeasures can be even more effective. However, logical countermeasures that are proven based on simple fault models like DFA may not be sufficient in real-world scenarios. Implementing duplication-based countermeasures in Elliptic Curve Cryptography can also be costly.

How effective is a real-world secure, proven implementation of elliptic curve scalar multiplication against electromagnetic fault injection attacks?

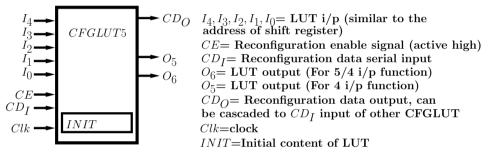

A technology feature developed to mitigate side-channel attacks or enhance system performance may inadvertently create opportunities for other types of attacks. Therefore, a thorough assessment of a system's security and consideration of all possible risk factors before its release to the market is crucial. An example of this is demonstrated by using a reconfigurable lookup table (RLUT) in an FPGA, which can increase a design's resistance against SCA but also offers a potential means for active adversaries to insert trojans into the design.

Therefore, this part addresses the question:

**RQ3:** What methods or techniques, can be employed to detect and prevent practical fault attacks?

#### **1.2.5.** Design considerations and guidelines (Part V)

In Part V, the utilization and selection of security algorithms are discussed. The definition of security from a designer's standpoint can be described as an additional constraint, precisely, as the fourth architectural design constraint, in addition to the three well-known existing ones: Power, Speed, and Price. A proposed security-aware design flow that considers the three security constraints investigated in this thesis, namely Cryptanalysis, Side-Channel Attacks, and Fault Injection Attacks, can be followed to determine the optimal trade-off for different security applications.

In this part (Part V), we will discuss the utilization and selection of security algorithms. From a designer's perspective, security can be considered an additional constraint that must be considered alongside the three well-known architectural design constraints of Power, Speed, and Price. We want to demonstrate that security can be considered the fourth design constraint for any system through the study of state of the art in different security domains, including Cryptanalysis, Side-Channel Attacks, and Fault Injection Attacks.

From our observation in the previous chapters and the study of the state-of-theart, how can we introduce more rigor in the design process of a system subject to different security constraints?

To ensure optimal security, we propose a security-aware design flow that considers the three security constraints studied in this thesis to determine the optimal tradeoff for a targeted application.

The proposed security-aware design flow could include the following high-level steps:

- Threat Model and Risk Assessment: Identify potential threats to the system and evaluate associated risks. This step provides a comprehensive understanding of the system's security requirements.

- Selection of Security Mechanisms: The appropriate security mechanisms can be selected once the security requirements are understood. These mechanisms can be chosen based on their ability to mitigate the identified threats

and reduce the associated risks.

- Algorithm Selection: The appropriate cryptographic algorithms can be chosen after selecting the security mechanisms.

- The selection process should consider the security strengths and weaknesses of the different algorithms and ensure they are suitable for the specific application.

- Implementation and Testing: The selected algorithms should be implemented in the system and thoroughly tested to ensure that they provide the necessary security levels.

- Verification and Validation: The implemented system should be verified and validated to ensure that it meets the specified security requirements.

Overall, in this part, we explore potential guidelines or principles that designers could utilize to enhance the level of rigor in the design process of a security-critical application. We address the following research question: **RQ4:** What potential guidelines or principles could designers utilize to enhance the level of rigor in the design process of a security-critical application?

## **1.2.6.** Application of design guidelines: Lightweight cipher secure implementations (Part VI)

In Part VI, the focus is on implementing the proposed security-aware design flow to address the challenge of creating secure embedded software implementations for lightweight ciphers. The proliferation of IoT devices has increased the use of general-purpose microcontrollers with integrated hardware cryptographic modules and software cryptographic stack implementations. The selection of one of these solutions is primarily influenced by cost considerations, with hardware solutions providing better power performance but being more costly to replace if a vulnerability is identified. FPGA-based solutions can provide the benefits of both approaches but at a higher cost.

In 2021, the NIST launched a competition to select a future lightweight authenticated cipher cryptographic standard. This competition aims to find a cipher that offers a better trade-off than AES, considering the latest advancements in cryptography and hardware security. Designers face a challenge in finding a lightweight cipher that is efficient in software and hardware. Lightweight ciphers with low S-Box gate counts are Side-Channel masking friendly, but their linear parts can be costly to process in software.

The objective is to find an algorithm that surpasses AES regarding gate count

and software cycle count while providing additional security properties suitable for the widespread deployment of IoT and Edge devices.

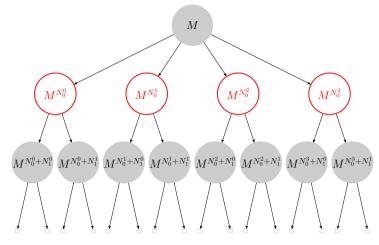

The goal was to assess the performance of NIST lightweight cryptography competition candidates versus AES regarding the hardware-software secure implementation trade-off. The GIFT family of block ciphers utilized by several NIST Lightweight Competition contenders was selected for evaluation due to its advantageous hardware implementation characteristics. Despite the favorable hardware implementation, the software implementation of GIFT is considered complex and inefficient because of the bit permutation in its linear layer. To address this issue, the second chapter of the thesis presents a generic bit-slicing approach for efficient, constant-time software implementation of SPN applied to the GIFT family of block ciphers. This implementation methodology is also adaptable to other ciphers, including AES, and aims to provide a fair basis for comparing secure cipher implementations that are constant in time.

Automated formal proof verification for bit-slice implementations is advantageous when utilizing first and second-order logic proof verifiers. Nevertheless, the proof process generally requires a simplified model and relies on extensive assumptions concerning the executing processor's architecture. Various formally proven implementation methodologies will be examined and validated on real microcontrollers used in the Internet of Things to investigate the disparity between theory and practicality.

#### **1.2.7.** Research questions summary

In summary, here are the questions addressed in this Ph.D. thesis :

#### RQ1

What is the actual cost of a differential cryptanalysis attack when the cipher's security is near or below the 80-bit security threshold?

#### RQ2

How can we practically prevent side-channel attacks?

#### RQ3

What methods or techniques, can be employed to detect and prevent practical fault attacks?

RQ4

What are some potential guidelines or principles that designers could utilize to enhance the level of rigor in the design process of a securitycritical application?

#### **1.3.** Outline and Contributions

The structure of the thesis is as follows:

Each chapter of the thesis includes at least one publication referenced at the end of the chapter. The different chapters of this thesis are integral versions of published papers, and hence, the terminology and notations might vary across chapters.

#### **1.3.1.** Part II: The Practical Cryptanalysis

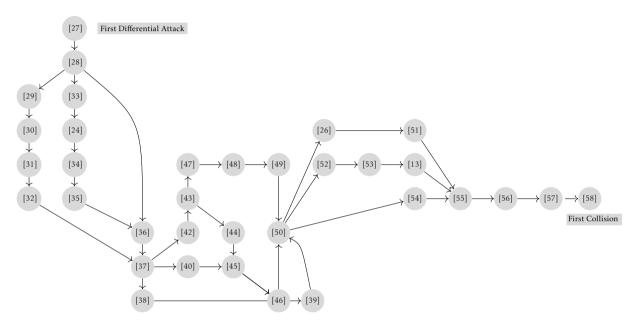

In chapter 2, we provide a preliminary survey on the history of hardware crackers. Cryptanalysis is a crucial aspect of cryptography. It serves the purpose of breaking ciphers for malicious purposes and forming the foundation for constructing secure ones. The most commonly used ciphers are considered secure because they have been continuously tested and not successfully broken by cryptanalysts. Although successful cryptanalysis may prove a cipher's vulnerability, the attack is often only theoretical due to its

difficulty in efficiently executing it. For instance, the vulnerability behind the SHA-1 collision attack discovered in 2017 was already known in 2005. However, due to a lack of resources and algorithms, it took until 2016 for it to be addressed by the Internet and IT industries. Advancements in attack algorithms, implementation techniques, and hardware fabrication have allowed for the practical execution of cryptanalysis. This survey covers these efforts and delves into quantum computers' impact on cryptography and cryptanalysis. The survey is divided into three sections: cryptanalytic attacks with specific implementation needs, previous cryptanalytic machines, and quantum computers.

This chapter is an integral copy of the paper "Crack Me if you can: hardware acceleration bridging the Gap between Practical and theoretical cryptanalysis?: A Survey. SAMOS 2018: 167-172".

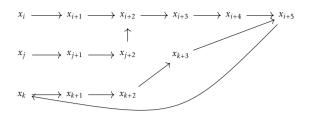

Then in chapter 3, we study the cost of the SHA-2 chosen prefix collision on ASIC. In 2017, the SHA-1 hash algorithm was practically broken using an identical-prefix collision attack implemented on a GPU cluster, and in 2020, a chosen-prefix collision was first computed with practical implications for various security protocols. This raised questions about the cost of performing such attacks and the best software/hardware cryptanalysis technology. This paper addresses these questions by examining the challenges and costs of building an ASIC cluster for attacking a hash function. The study considers different scenarios and includes two cryptanalytic strategies - a classical birthday search and a differential attack using neutral bits for SHA-1.