# An Offset Calibration Technique for CIS Column-Parallel SAR ADCs Using Memory

Lee, Jaekyum; Theuwissen, Albert

10.2352/EI.2022.34.7.ISS-155

**Publication date**

**Document Version** Final published version

Published in

IS and T International Symposium on Electronic Imaging Science and Technology

**Citation (APA)**Lee, J., & Theuwissen, A. (2022). An Offset Calibration Technique for CIS Column-Parallel SAR ADCs Using Memory. *IS and T International Symposium on Electronic Imaging Science and Technology*, *34*(7), Article 155. https://doi.org/10.2352/EI.2022.34.7.ISS-155

# Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# An Offset Calibration Technique for CIS Column-Parallel SAR ADCs Using Memory

Jaekyum Lee<sup>1</sup>, Albert Theuwissen<sup>1,2</sup>;

<sup>1</sup>Electronic Instrumentation Laboratory, Delft University of Technology; Delft/the Netherlands

#### **Abstract**

A column-parallel 10-bit SAR ADC for high-speed image sensors has been implemented. A fast offset calibration technique using memory is proposed to compensate for the offset mismatch, accompanied by an ADC designed for a narrow space the size of a single column pitch. The memory accumulates the variation of the offset to track the offset within two cycles. After applying the offset calibration technique, the offset variation of the ADC measured in each column is improved from 4.27LSB to 0.39LSB. The fixedpattern noise (FPN) is also improved from 4.14LSB to 0.34LSB. This calibration method covers an offset range of ±32LSB. The implemented ADC achieves a maximum speed of 500kS/s. The maximum frame rate of the sensor is 3000fps. The power consumption of the sensor, excluding the LVDS interface, is 71mW. This sensor is designed in a TowerJazz CIS 180nm process with one poly four metal. The supply voltage of the analog and digital domains is 3.3V and 1.8V, respectively.

#### Introduction

Recently, many researchers have performed R&D on high frame rate image sensors. The advent of a wide variety of applications such as machine vision, and the demand for high quality video images strongly justify the research for high frame rate sensors [1-3]. These R&Ds have mainly improved the frame rate of the sensor by increasing the number of ADCs [4-5] or designing a different type of ADC [2-3]. In particular, due to the limitations of the single-slope ADC, such as inefficient data conversion and speed limitation of the counter, SAR ADCs or cyclic ADCs have been designed to overcome these limitations. As a result, research on high frame rate image sensors has achieved a horizontal line time of less than 2µs [2-4]. In most cases, designing a SAR ADC is more beneficial for achieving high-speed data conversion than a cyclic ADC due to its efficient data conversion using a binary search algorithm. However, though the SAR ADC has an efficient algorithm for high-speed data conversion, its designed silicon area and noise performance introduce limitations. In particular, the SAR ADC has many unit capacitors that occupy a relatively large silicon area. As a result, very often, pixels in multiple (neighboring) columns share the same ADC due to lack of space [2], [6-7]. This structural problem leads to channel mismatch, such as offset, so a large bandwidth is required for fast data conversion of the SAR ADC. Furthermore, the offset mismatch impacts the fixed-pattern noise (FPN), and the large bandwidth compromise temporal noise performance.

In this paper, we propose a fast offset calibration technique for the SAR ADC. This offset calibration technique is expected to suppress the offset mismatch which occurs in a SAR ADC designed for a narrow space of a one-pixel pitch. To implement this fast offset calibration, memory designed for each column accumulates the offset variation. This accumulated offset information in turn compensates for the offset during the offset calibration period by controlling the potential level of the capacitor DAC's output. As a result, the image sensor can use the SAR ADC

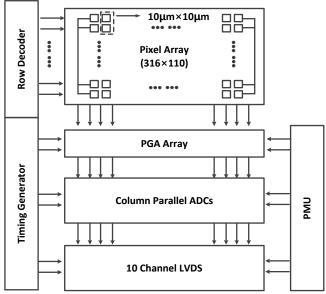

Figure 1. Block diagram of the sensor

in a column-parallel structure to enhance the frame rate while relaxing the specification of the SAR ADC at each column. Therefore, this paper will review the image sensor's readout circuit chain and its operation timing in Section 2. Section 3 will discuss the offset calibration method using memory. Finally, this paper will show the measurement results in Section 4.

#### Readout Architecture with SAR ADC

#### Sensor architecture overview

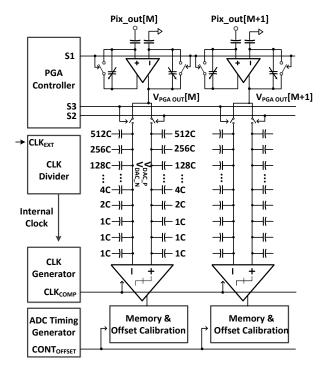

Figure 1 shows a block diagram of the sensor, which has a 316 × 110 pixel array. Since this sensor employs a column-parallel structure, the analog front end consists of 316 ADCs and 316 Programmable Gain Amplifiers (PGAs). Moreover 10 LVDSs are used as an interface to the outside world. An I2C interface defines the register setup for each circuit block. The power management unit (PMU) contains reference generators and a bandgap reference (BGR). The row decoder creates the pixel control signals. Figure 2 depicts the readout circuit chain of this sensor including the SAR ADC and the PGA. The maximum analog gain supported by the PGA is 8x. The SAR ADC has 1026 unit capacitors in the positive and negative parts of the capacitor DAC; the unit capacitor size is 0.56fF. The control logic controls the negative part of the DAC for data conversion while the positive part of the DAC controls the offset calibration. The sensor accepts an external clock, CLKEXT, to control the sensor; this external clock is divided into an internal clock by the clock divider, as shown in Figure 2. In addition, the internal clock is reshaped into a signal CLK<sub>COMP</sub> to control the comparator, as shown in Figure 3.

<sup>&</sup>lt;sup>2</sup>Harvest Imaging; Bree/Belgium

Figure 2. Block diagram of readout chain

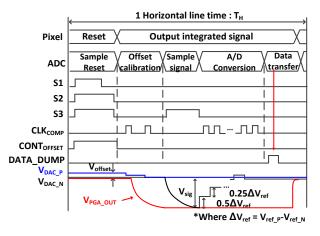

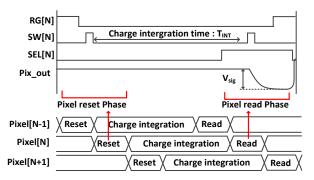

Figure 3. Timing diagram for PGA and ADC in one horizontal line time

Figure 3 shows a timing diagram for controlling the ADCs and the pixels within one horizontal line time. At the beginning of one horizontal line time, the PGA resets itself by turning on S1. At the same time, the ADC samples the reset level of the pixel, VCM, on the capacitor DAC by turning on S2 and S3. The PGA completes the reset operation after turning off S1, while the ADC also finish its sampling by turning off S2 and S3. After sampling, the ADC performs the offset calibration for two cycles, and the pixel starts transmitting the integrated signal to the PGA. In the next phase, the ADC samples the integrated signal from the PGA with S3 turned on. After the sampling is completed by turning off S3, the potential at  $V_{DAC\_N}$  is  $V_{CM} - V_{sig}$ . The  $V_{sig}$  is the signal resulting from charge integration at the pixel. The ADC converts the signal using a binary search method during the subsequent ten cycles starting from the MSB part. After ten cycles, the digital

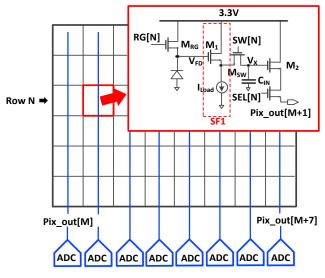

Figure 4. Pixel array and circuit diagram with 3T pixel and sampling net work

Figure 5. Timing diagram example for controlling single pixel

codes are stored in the register array and transmitted to the interface at the rising edge of DUMP DATA shown in Figure 2.

# 3T pixel structure with sampling network

Figure 4 shows a circuit diagram of a single-pixel included in a pixel array. As shown in Figure 4, the sensor generates signals by means of a 3T pixel. The 3T pixel has the advantage in speed compared to a 4T pixel. Specifically, the 3T pixel can output the signal immediately, and the only factor controlling the speed is the current applied in the source follower. All outputs of the pixels located in the single column are connected to a single output line, which enables the sensor to read the pixel sequentially by using the ADC located at each column. Figure 5 illustrates the timing diagram for controlling the pixel array containing this 3T pixel structure. Since the sensor employs a rolling shutter method, the sensor reads out the lines sequentially. In addition, the sensor resets each line sequentially to maintain the same charge integration time. In this work, the ADC calibrates the comparator before the analog-to-digital conversion, the pixel must output reset level first. The sampling network is designed with the 3T pixel to enable this readout sequence.

The pixel control procedure consists of three phases: reset, charge integration, and reading. First, in the reset phase, the row decoder turns on the reset gate,  $M_{RG}$ , to reset the pixel before the

Figure 6. Simplified principle of offset calibration

photodiode starts integrating the charge. After the pixel reset, the row decoder turns off the reset gate, M<sub>RG</sub>, by controlling the signal RG, and then samples the reset level of the pixel on the sampling capacitor  $C_{\rm IN}$  by turning on the switch  $M_{\rm SW}$ . The capacitor  $C_{\rm IN}$ preserves the sampled reset level until the pixel reading phase. In the meantime, the photodiode starts integrating charge generated by incoming light. The holding time of the sampled reset level is equal to the integration time, T<sub>INT</sub>. In the pixel reading phase, the reset level preserved on C<sub>IN</sub> is output to the PGA first through the output of the source follower, VPIX OUT. Next, the signal level is sampled on the C<sub>IN</sub> after the sampling of the reset level of the ADC is completed. This sampled signal level is also output to the PGA during the offset calibration period. The ADC samples this signal level from the PGA after completing the offset calibration. In the pixel reset and reading phase, since the signals from the photodiodes are output through an internal source follower (SF1), as shown in Figure 4, the current sources must be activated. However, enormous power consumption is inevitable when all internal current sources are operating simultaneously. Therefore, only the current sources of the two rows in the pixel reset and the pixel reading phase are working at every horizontal line time to reduce power consumption.

# Offset Calibration Technique and Advantages

# The offset calibration algorithm

In this readout architecture, two factors can introduce FPN. The first factor is the variation of the pixel reset level, and the second factor is the offset inside the ADC. The PGA regulates the pixel reset level difference with the auto-zeroing technique in this work. Previous research has shown that this auto-zeroing technique has already demonstrated the effect on FPN performance [11]. However, this technique cannot compensate for the offset inside an ADC because the ADC samples the signal that the PGA regulates. Therefore, the offset inside the ADC will directly appear in the image as FPN. Figure 6 shows the simplified principle of the offset calibration technique used in this work. Theoretically, the offset is fixed noise. However, any variation occurs in the environment of the ADC could change this offset slightly. The proposed offset calibration algorithm compensates for this offset variation at each horizontal line time by performing background operations.

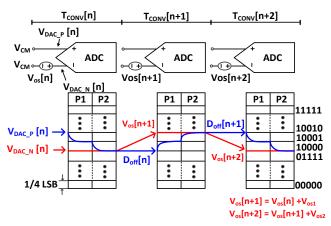

In Figure 6, we assume that the offset, V<sub>off</sub>, is positioned at the top plate of the negative capacitor DAC, V<sub>DAC\_N</sub>, and that this offset varies slightly in each conversion phase. Once the offset

calibration starts, the ADC samples the reset level, V<sub>CM</sub>, at its positive and negative inputs. At n-th horizontal line time, TCONV[n], the potential level V<sub>DAC\_N</sub>[n] including offset variation is V<sub>CM</sub> + Voff[n]. As shown in Figure 6, when the offset calibration algorithm calibrates the offset at T<sub>CONV</sub>[n], the memory stores this offset information as a digital output, Doff[n]. At the next horizontal line time, T<sub>CONV</sub>[n+1], the offset level changes again, and the offset increment Voff[n+1] - Voff[n] is Vos1, as shown in Figure 6. When the ADC starts the offset calibration at  $T_{CONV}[n+1]$ , the ADC loads the previous offset information, Doff[n]. Therefore, the ADC only has the newly added offset Vosl, which the ADC calibrates within two cycles. Therefore, the offset calibration logic easily estimates the offset increment corresponding to  $V_{os1}$ , and the memory accumulates this offset information to generate new offset information as a digital output, Doff[n+1]. At the next horizontal line time, T<sub>CONV</sub>[n+2], if the offset is changed by V<sub>os2</sub> again, the offset calibration starts estimating using the information D<sub>off</sub>[n+1]. In the same way, the offset calibration algorithm continuously compensates for the offset, so the offset information is updated.

This offset calibration algorithm has two critical advantages. The first advantage is that the algorithm calibrates the offset within two cycles. Since this algorithm continuously retrieves the previous offset information from the memory, the offset that is newly added in each conversion phase is relatively small. Therefore, it is possible to compensate the offset within a short amount of time. The second advantage is that this ADC does not need an adder or subtractor. This offset calibration controls the positive part of the capacitor DAC. After two cycles of the offset calibration period, the SAR ADC sets the potential  $V_{\rm DAC\_P}$  as a 0 code level. As a result, the DAC control automatically subtracts the offset level from the signal level.

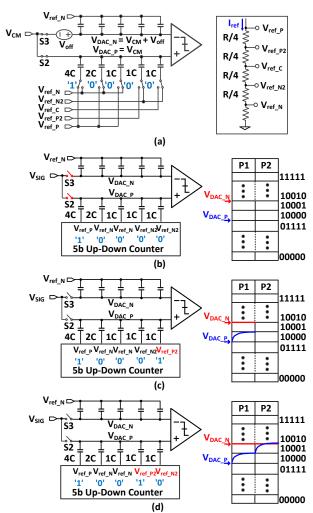

#### The capacitor DAC control for calibration

Figure 7 shows an example of the capacitor DAC control accompanied by a 5b up-down counter for the offset calibration at one horizontal line time. Since two digits in the LSB part of the counter refer to 0.5LSB and 0.25LSB, respectively, the unit capacitors controlled by these LSB parts use the reference voltage V<sub>refP2</sub>, V<sub>refN2</sub> and V<sub>refC</sub>, as shown in Figure 7(a). This offset calibration logic controls the positive part of the capacitor DAC. The signal CONTOFFSET illustrated in Figure 3 controls the switch network of the positive part of capacitor DAC to transfer the offset information from the previous offset calibration period. At the beginning of the horizontal line time, the ADC samples the reset level, while the signal CONT<sub>OFFSET</sub> is in a high state. The switch control logic connects the bottom plate of all capacitors except the 4C to the negative reference, as shown in Figure 7(a). If we assume that the offset exists in the negative part of the DAC, the signals sampled on each DAC are  $V_{CM}$  +  $V_{off}$  and  $V_{CM}$ , respectively. The controller turns off switches S2 and S3 when the ADC completes the sampling of the reset level. After completing the reset sampling, control signal CONT<sub>OFFSET</sub> becomes low-state. At the falling edge of signal CONTOFFSET, the bottom plate of the DAC is connected to the output of the up-down counter, as shown in Figure 7(b). As a result, the mathematical representation of the signal in the positive part of the capacitor DAC is:

$$V_{DAC\ P} = V_{CM} - (D_{INIT} - D_{MEM}) \times V_{1/4LSB}$$

where  $V_{1/4LSB}$  is the analog signal corresponding to 0.25LSB, and  $D_{INIT}$  and  $D_{MEM}$  are the initial values of the counter output and the digital code memorized at the counter, respectively. Therefore,

Figure 7. Switch control method for offset calibration

if the value registered is '10000', the potential at the positive part of the DAC is maintained in the same state as  $V_{CM}$ , as shown in Figure 7(b). In the first comparison phase, in Figure 7(b), the potential at the negative part is higher than that at the positive part. After the comparison, the comparator output becomes low-state, and the counter adds a 1LSB code. As a result, the potential at the output of the positive part of the capacitor DAC adds V<sub>1/4 LSB</sub>, as shown in Figure 7(c). In the second comparison phase, the potential at the negative part is still higher than that in the positive part. When the comparator completes the second comparison, the comparator output becomes low-state again, and the counter adds a 1LSB code again. Consequently, the offset is compensated, as shown in Figure 7(d), and the counter saves the digital outputs generated from the offset calibration until the next offset calibration. Since the counter retains the output until the next offset calibration, the offset can be re-estimated in the next calibration period. We use an 8b up-down counter in this work, with and offset cover range of  $\pm 32$ LSB.

# Measurement result and discussion

## The measurement environment

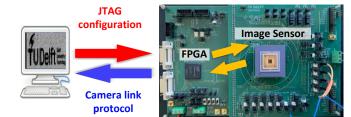

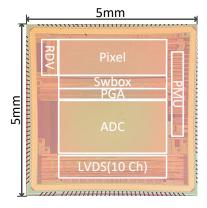

The proposed CMOS image sensor has been fabricated in a Tower-Jazz  $0.18\mu m$  CIS process technology. The chip size is

Figure 8. Test environment setup with a PCB and FPGA

$5.0 \text{mm} \times 5.0 \text{mm}$ , while the core area of the pixel array is  $110 \times 316$ . Within this pixel array, the sensor effectively uses a  $300 \times 90$  pixel array. An Altera Cyclone10 FPGA provides the digital control signals and captures the image sensor's output data. LabVIEW receives the data transmitted through the camera-link interface from the FPGA, and the post-processing is done in MATLAB. Since this system does not output any code below 0, post-processing is performed during the measurement in dark conditions. Figure 8 shows the combination of the test setup with the FPGA.

In this work, the sensor receives a maximum clock of 50MHz from the FPGA. The speed of the clock distributed inside cannot support exceed 50MHz due to a process limitation. Therefore, the maximum speed measured of the ADC is 500kS/s. Since the maximum speed of the LVDS interface is 1Gb/s, the shortest horizontal line time the sensor can support is 4µs, while the maximum frame measured rate is 3000fps. Finally, Table 1 shows a summary of the performance, and Figure 10 shows a microphotograph of the test chip.

**Table 1. Performance summary**

| Pro                      | cess                        | TowerJazz 0.18µm CIS process(1P4M)                        |  |  |

|--------------------------|-----------------------------|-----------------------------------------------------------|--|--|

| Pixel array              |                             | 316(H) × 110(V)<br>Effective pixel array : 300(H) × 90(V) |  |  |

| Pixel size               |                             | 10μm × 10μm                                               |  |  |

| Convers                  | sion gain                   | 58.24μV/e-                                                |  |  |

| Full well capacity (FWC) |                             | 8042e-                                                    |  |  |

| Noise<br>performance     | Read noise                  | 712.8µV(=12.2e-)                                          |  |  |

|                          | VFPN                        | 0.34LSB(with offset calibration)                          |  |  |

|                          | HFPN                        | 0.07LSB                                                   |  |  |

| DR                       |                             | 56.3dB                                                    |  |  |

| Frame rate               |                             | maximum : 3000fps                                         |  |  |

| ADC resolution           |                             | 10                                                        |  |  |

| ADC saturation level     |                             | 500mV                                                     |  |  |

| ADC sampling rate        |                             | maximum : 500kS/s                                         |  |  |

| LVDS speed               |                             | 1Gb/s (10 Channels)                                       |  |  |

| Power consumption        | Analog + Digital +<br>Plxel | 78.5mW @ 3000fps<br>71mW @ 730fps                         |  |  |

|                          | LVDS interface              | 59.4mW(10 Channels)                                       |  |  |

# The measurement result and analysis

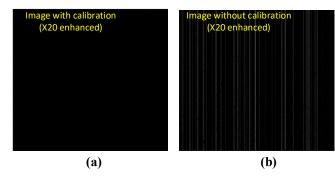

To verify the effect of this offset calibration technique, 100 images are captured in a dark environment. The ADC offset and the vertical fixed pattern noise (VFPN) are characterized after averaging these images. Specifically, the offset calibration logic requires time to set the register value at an appropriate point. Therefore, this algorithm needs a maximum of 128 horizontal line times because cover range of  $\pm 32$ LSB. For this reason, the first frame is excluded from the analysis. Figure 9 shows the impact of this technique on image quality. In this figure, the averaged images

Figure 9. Image taken in a dark environment (a) with offset calibration and (b) without offset calibration

have been enhanced by 20 times. Figure 9(b) shows that the VFPN is observed when the offset calibration is not applied. On the other hand, the offset calibration technique does improve the image quality, as depicted in Figure 9(a).

After post-processing, the data show that the offset calibration improves the ADC offset variation from 4.27LSB to 0.39LSB. In addition, the averaged offset measured of the ADC is -0.6LSB after post-processing. The main reason for the offset is that switch S3 introduces offset due to the coupling effect of the junction capacitor. In the same way, the VFPN is improved from 4.14LSB to 0.34LSB after the offset calibration is applied.

Table 2 shows the impact of this offset calibration on the VFPN performance of this image sensor. As described in the table, the sensor has better VFPN performance when the sensor uses digital CDS because the digital CDS eliminates the error induced by the circuit [9]. However, this CDS inevitably has a long horizontal line time because, in this case, the ADC must convert the data two times. On the other hand, the analog CDS cannot compensate for the offset originating from the readout circuit. Therefore, if the comparator is not calibrated accurately, the sensor's VFPN performance is impacted [6], [8]. If a sufficient comparator offset calibration technique is applied to the sensor, which uses analog CDS, the VFPN performance is substantially improved [10]. In addition, this design requires a smaller area for the offset calibration technique than [10], which is designed with an offset sampling technique, because this calibration circuit consists of a digital circuit, as described in the previous section. Finally, this technique has a robust effect on the offset calibration compared to the offset sampling method [10].

Figure 10. Test micrograph of the fabricated chip

Table 2. Performance comparison

| Year               | 2022                  | 2014                | 2018                 | 2015                 | 2018                  |

|--------------------|-----------------------|---------------------|----------------------|----------------------|-----------------------|

| Ref                | This work             | [8]                 | [6]                  | [9]                  | [10]                  |

| Technology         | 180nm                 | 180nm               | 90nm                 | 180nm                | 180nm                 |

| Pixel array        | 300×90                | 920×256             | 1920×1440            | 256×128              | 190×160               |

| Pixel pitch        | 10 <sub>μ</sub> m     | 1.85 <sub>µ</sub> m | 1.4 <sub>µ</sub> m   | 4.4 <sub>μ</sub> m   | 25 <sub>μ</sub> m     |

| Frame rate         | 3000 fps              | 9 fps               | 50 fps               | 90 fps               | 3000 fps              |

| Power consumption  | 78.5 mW               | 21.2 mW             | 64 mW                | 4.4 mW               | 623 mW                |

| Conversion<br>gain | 58.24 <sub>μ</sub> V  | 70 <sub>µ</sub> V   | N/A                  | 60 <sub>μ</sub> V    | 202.85 <sub>μ</sub> V |

| Analog gain        | ×1 – ×8               | -                   | -                    | ×1 – ×4              | ×1 – ×8               |

| ADC type           | SAR                   | SAR                 | SAR                  | SAR                  | SAR                   |

| ADC resolution     | 10                    | 9                   | 10                   | 12                   | 14                    |

| Temporal           | 710.52 <sub>μ</sub> V | 5.3mV               | 273.6 <sub>u</sub> V | 268.8 <sub>μ</sub> V | 2.3mV                 |

| noise              | (12.2e-)              | (75.7e-)            | 2/3.0μν              | (4.48e-)             | (11.5e-)              |

| Dynamic<br>range   | 56.3 dB               | 50.6 dB             | 66.5 dB              | 68.1 dB              | 68.7 dB               |

| VFPN               | 0.34 LSB<br>(0.03%)   | 0.5%                | 0.23%                | 0.17 LSB             | 0.12%                 |

| CDS type           | Analog                | Mixed               | Analog               | Digital              | Analog                |

| Comparator offset  | Calibrated            | Calibrated          | -                    | -                    | Calibrated            |

# Conclusion

A CMOS image sensor with a column-parallel SAR ADC has been realized. We suggest the application of a fast offset calibration technique to compensate for the offset induced by the ADC, which is designed for a narrow space. Memory enables the implementation of this offset calibration. The memory accumulates the offset variation and compensates the offset within two cycles. As a result, the offset calibration technique improves the VFPN performance of the sensor from 4.14LSB to 0.39LSB. This technique also enables the sensor to be designed with a column-parallel structure that can enhance the frame rate of the sensor. In conclusion, this work suggests that the SAR ADC design in a column-parallel structure can improve an image sensor's frame rate.

### Acknowledgement

This work was supported by the SENSATION project, sponsored by the Dutch government and the EC. The authors would like to thank TowerJazz for their support in fabricating the silicon dies.

# References

- J. O. Vieth, "Image sensors in industrial/machine vision applications," Proceedings Eleventh Annual IEEE International ASIC Conference (Cat. No.98TH8372), 1998, pp. 387-391, doi: 10.1109/ASIC.1998.723045.

- [2] R. Funatsu et al., "6.2 133Mpixel 60fps CMOS image sensor with 32-column shared high-speed column-parallel SAR ADCs," 2015 IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, 2015, pp. 1-3, doi: 10.1109/ISSCC.2015.7062951.

- [3] T. Yasue et al., "A 1.7-in, 33-Mpixel, 120-frames/s CMOS Image Sensor With Depletion-Mode MOS Capacitor-Based 14-b Two-Stage Cyclic A/D Converters," in IEEE Transactions on Electron Devices,

- vol. 63, no. 1, pp. 153-161, Jan. 2016, doi: 10.1109/TED.2015.2451700.

- [4] B. Cremers, "A 5 Megapixel, 1000fps CMOS Image Sensor with High Dynamic Range and 14-bit A/D Converters," IISW, 2013.

- [5] M. Sakakibara et al., "A back-illuminated global-shutter CMOS image sensor with pixel-parallel 14b subthreshold ADC," 2018 IEEE International Solid State Circuits Conference (ISSCC), 2018, pp. 80-82, doi: 10.1109/ISSCC.2018.8310193.

- [6] S. Hwang et al., "A 2.7-M Pixels 64-mW CMOS Image Sensor with Multicolumn-Parallel Noise-Shaping SAR ADCs," in IEEE Transactions on Electron Devices, vol. 65, no. 3, pp. 1119-1126, March 2018, doi: 10.1109/TED.2018.2795005.

- [7] S. Xie, X. Ge and A. Theuwissen, "Temperature Sensors Incorporated into a CMOS Image Sensor with Column Zoom ADCs," 2019 IEEE International Symposium on Circuits and Systems (ISCAS), 2019, pp. 1-5, doi: 10.1109/ISCAS.2019.8702321.

- [8] D. G. Chen, F. Tang, M. Law, X. Zhong and A. Bermak, "A 64 fJ/step 9-bit SAR ADC Array with Forward Error Correction and Mixed-Signal CDS for CMOS Image Sensors," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 61, no. 11, pp. 3085-3093, Nov. 2014, doi: 10.1109/TCSI.2014.2334852.

- [9] M. Kim, S. Hong and O. Kwon, "A Fast Multiple Sampling Method for Low-Noise CMOS Image Sensors with Column-Parallel 12-bit SARADCs," Sensors 16, no. 1:27, https://doi.org/10.3390/s16010027

- [10] X. Zhang, W. Fan, J. Xi and L. He, "14-Bit Fully Differential SAR ADC with PGA Used in Readout Circuit of CMOS Image Sensor", Journal of Sensors, vol. 2021, Article ID 6651642, 17 pages, 2021. https://doi.org/10.1155/2021/6651642

- [11] N. Stevanovic, M. Hillebrand, B. J. Hosticka and A. Teuner, "A CMOS image sensor for high-speed imaging," 2000 IEEE International Solid-State Circuits Conference. Digest of Technical Papers (Cat. No.00CH37056), 2000, pp. 104-105, doi: 10.1109/ISSCC.2000.839710.

# **Author Biography**

Jaekyum Lee received his BSc in microelectronics from Korea University (2011), Seoul, Korea, and his MSc in electrical engineering from KAIST, Daejeon, Korea (2013). Starting in 2013, he worked for Samsung Electronics for five years. While working for the company, he designed CMOS image sensors for mobile phones and automobiles. Since September 2018, Jaekyum has been a Ph.D. candidate in the Electronic Instrumentation Laboratory at TU Delft, where he continues working on CMOS image sensors.

Albert J. P. Theuwissen received his BSc (1977) and Ph.D. (1983) degrees in electrical engineering from the Catholic University of Leuven, Leuven, Belgium. Since 1983 he has worked for several companies, focusing on image sensors. After he left DALSA in 2007, he started Harvest Imaging, Bree, Belgium, where he focuses on consulting, training, and teaching solid-state imaging technology. In 2001 he joined TU Delft as a part-time Professor. Albert is an IEEE Life Fellow.