## **Contactless** Inductive Power and Data Transfer

## For use in E-Texiles

W.P. Lindeman

## Contactless Inductive Power and Data Transfer

For use in E-Texiles

by

## W.P. Lindeman

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Friday September 23th, 2022 at 10:30 AM.

Student number: Project duration: Thesis committee:

4383230 May 1, 2021 – September 23, 2022 Dr. ir. A. Bossche, TU Delft, supervisor Prof. Dr. P. J. French, TU Delft Dr. Ir. J. Dong, TU Delft MSc. A. S. M. Steijlen, TU Delft, daily supervisor

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## Abstract

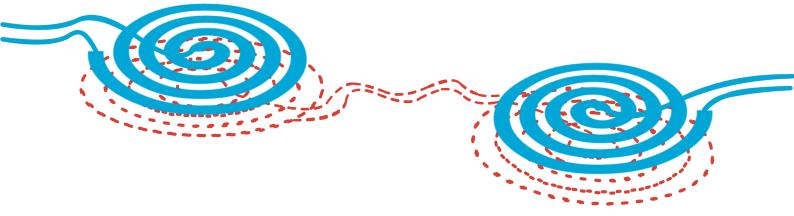

Distributing power and data around a garment is a common problem in sensor enabled e-textiles, as connecting separate electronic subsystems together using connectors and wires has proven to be unreliable and cumbersome. In this work a solution is presented that will eliminate the connectors by using short-range wireless inductive links. This removes mechanical issues caused by wire strain, and will make removing or replacing electronics for washing or maintenance more straight forward. An impression of this system is shown in 1.

The proposed system is able carry power from one node to the next, while at the same time facilitating data transfer between the nodes. The system, as demonstrated in this work, consists of a master and a slave unit, connected via two sets of inductive links. Each inductive link consists of two planar coils placed at a distance of a few millimeters. The master generates a 13.56MHz carrier which is transmitted across the link. The slave uses this signal to extract power for both its own electronics, as well as external devices. Data is sent from the master to the slave by modulating this carrier (on-off keying), while data is sent back to the master using load modulation.

In this work the double inductive link is analysed, and a new compensation topology is presented which allows the system to be easily adapted to variations in coil spacing. A modified version of a class-E amplifier is presented to generate the carrier signal on the master side. A transformer based current sensing network is added to the output of the amplifier, which is used to detect the modulation of the slave input impedance. The slave uses a voltage doubler for harvesting energy from the carrier signal.

A proof of concept is built to demonstrate the working principles of the presented designs, and a basic placeholder data transmission protocol is devised to demonstrate its workings. Using this placeholder data protocol the system is able to transmit 62mW of regulated power to an external load at a total efficiency of 7.3%, while simultaneously transmitting data at a rate of 8.5kbit/s. The system is also shown to be capable of handling a theoretical maximum bitstream of 240kbit/s. Without data transmission it is able to deliver 185mW of DC power at 6.09V unregulated, at an efficiency of 23%. The system as demonstrated allows a sensor to be powered and read out from a central unit, without needing a direct wired connection.

Figure 1: Illustration of what a contactless e-textile sensor network could look like.

## Preface

The idea of harvesting energy from unconventional sources is something that has been chasing me throughout my academic career. I consider it poetic justice that in my final project I finally get the authority to not only harvest the energy, but also create its source, which massively simplifies the whole ordeal. Still, the project was very large in scope, testing my knowledge from amplifier design to data protocols, and from micro controllers to resonant circuits. It encapsulated nearly everything I have learned during my studies, and sometimes even a little more.

I would like to extend my gratitude to those who have kept me sane over the last year or so. This of course includes my supervisors Andre, Annemarijn en Jeroen, who together with my fellow students Adam, Zakaria and Tom, often unknowingly revitalised my enthusiasm for the project with insightful questions and comments during our weekly meetings. I would also like to thank my parents, who although far away supported me throughout the project.

Lastly I would like to thank my girlfriend Nuria. Who, despite not knowing anything about electronics, would insist that I explain her every milestone and roadblock. She even proof read an early version, pointing out several spelling errors. Thank you for always being there for me.

W.P. Lindeman Delft, September 2022

## Contents

| 1 | Intr         | oduction        |                  |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   | 1  |

|---|--------------|-----------------|------------------|----------|---------|-----|-----|-----|-----|-----|-----|---|-----|-----|-----|---|-----|---|----|

|   | 1.1          | Smart Sensor S  | Shorts Project.  |          | <br>    |     |     |     |     |     |     |   |     |     |     |   |     |   | 2  |

|   | 1.2          | Previous Resea  | rch              |          | <br>    |     |     |     |     |     |     |   |     |     |     |   |     |   | 3  |

|   | 1.3          | This Work       |                  |          | <br>    |     |     |     |     |     |     | • |     |     |     |   |     |   | 5  |

| 2 | Ind          | uctive Link     |                  |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   | 7  |

| 2 |              | Analysis of the | Double Induct    | ivo Link |         |     |     |     |     |     |     |   |     |     |     |   |     |   | •  |

|   |              | Link Compens    |                  |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   | 2.2          | -               | of the Compens   |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              | ē               | -                |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              | -               | ncy Characterist |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              | •               | ng the Quality F |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   | 0.0          |                 | ng a Topology.   |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   | 2.3          | •               | ••••••••         |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              |                 | ameters          |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              |                 | ipe              |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              |                 | nensions         |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              |                 | ining Optimal N  |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   | 2.4          | Practical Imple |                  |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              | 1               | nsation Networ   |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              |                 |                  |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   | 2.5          |                 | ılts             |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              |                 | f Inductance .   |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              | 2.5.2 Couplin   | g Factor         |          | <br>    | • • | ••• |     | ••• |     | • • | • | • • |     | • • |   |     | • | 24 |

|   |              | 2.5.3 Coil Res  | istance          |          | <br>    |     | • • |     | ••• | ••• | • • | • | ••• |     | • • |   |     | • | 25 |

|   |              | 2.5.4 Impeda    | nce Mirroring    |          | <br>    | • • |     |     | ••• | ••• |     | • |     |     |     |   |     | • | 27 |

|   |              | 2.5.5 Phase C   | haracteristics   |          | <br>    |     |     |     | ••• | ••• | • • | • | ••• |     |     |   |     | • | 28 |

| 3 | Mas          | ster Design     |                  |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   | 31 |

| 0 | 3.1          | 0               | sign             |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   | -  |

|   | 5.1          | 5               | Generator        |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              |                 | g Estimation .   |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              |                 | emodulation .    |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              |                 | odulation        |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

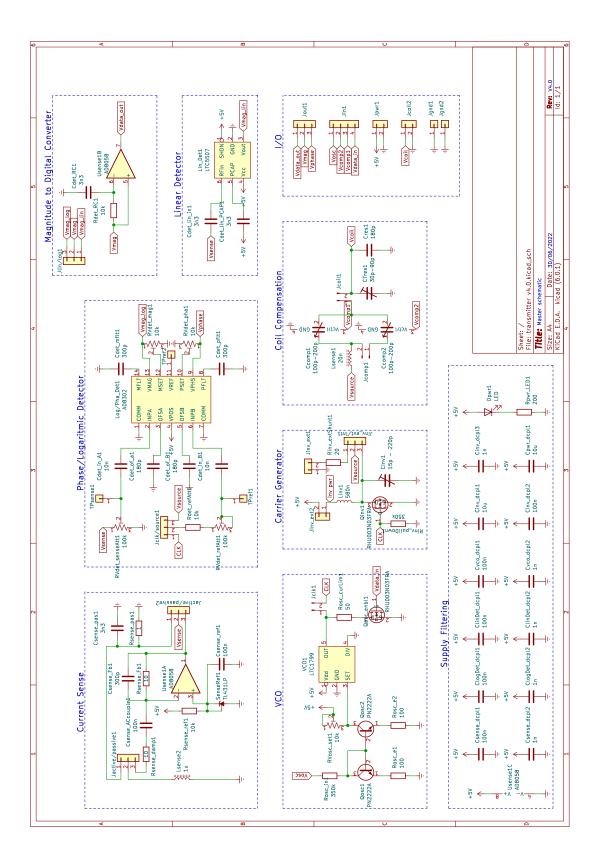

|   | 3.2          | Practical Imple |                  |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

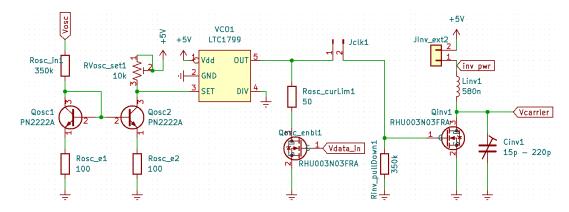

|   | 3.2          | -               | Generator and I  |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

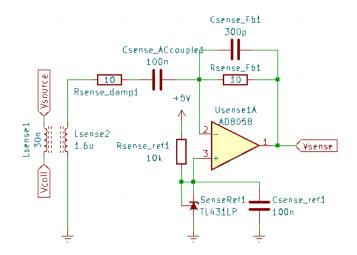

|   |              |                 | Sense Circuit    |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

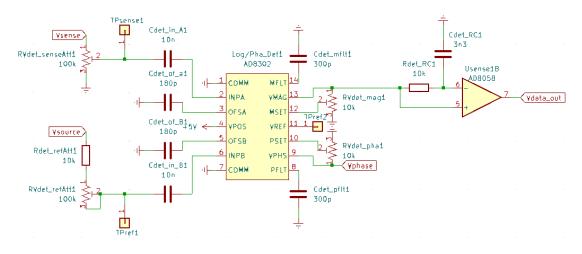

|   |              |                 | etection and M   |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   | <b>•</b> • • |                 |                  | -        |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   | 3.3          |                 | ormance          |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              |                 | Waveforms        |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

|   |              | 3.3.2 Current   | Sense Perform    | ance .   | <br>• • | ••• | ••• | • • | ••• | ••• | • • | • | • • | • • | • • | • | • • | · | 44 |

| 4 | Slav         | ve Design       |                  |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   | 47 |

|   | 4.1          | -               | sign             |          | <br>    |     |     |     |     |     |     |   |     |     |     |   |     |   | 47 |

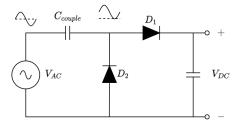

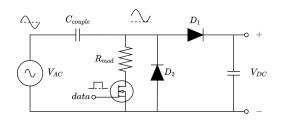

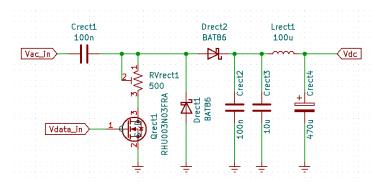

|   |              | 4.1.1 Rectific  | ation            |          | <br>    |     |     |     |     |     |     |   |     |     |     |   |     |   | 47 |

|   |              | 4.1.2 Load M    | odulation        |          | <br>    |     |     |     |     |     |     |   |     |     |     |   |     |   | 48 |

|   |              | 4.1.3 Demod     | ulator           |          | <br>    |     |     |     |     |     |     |   |     |     |     |   |     |   | 48 |

|   |              |                 | nanagement .     |          |         |     |     |     |     |     |     |   |     |     |     |   |     |   |    |

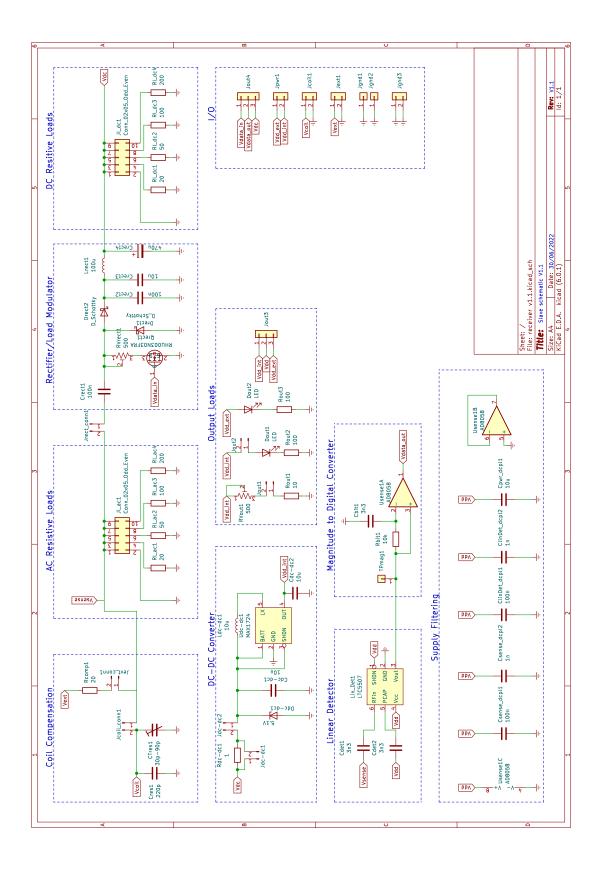

|    | 4.2 Practical Implementation                                         | 49 |

|----|----------------------------------------------------------------------|----|

|    | 4.2.1 Rectifier and Load Modulator                                   |    |

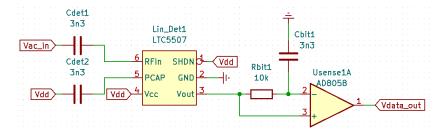

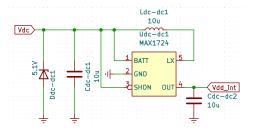

|    | 4.2.2 Demodulator                                                    |    |

|    | 4.2.3 Power Management                                               |    |

|    | 4.3 Measured Results                                                 | 50 |

| 5  | System Implementation                                                | 51 |

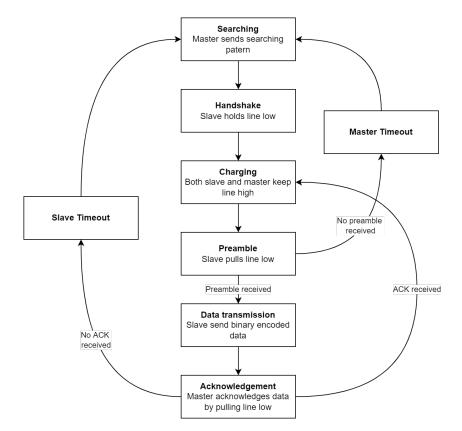

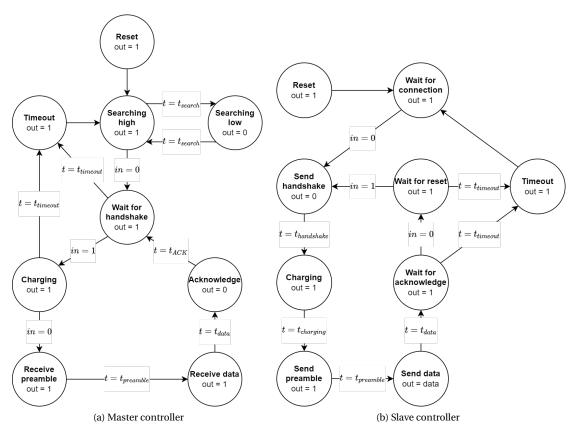

|    | 5.1 Master and Slave Controllers                                     | 51 |

|    | 5.2 Data Communication.                                              |    |

|    | 5.3 Active Coupling Tracking                                         | 54 |

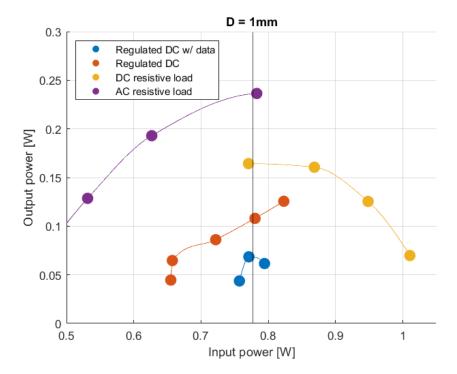

| 6  | Full System Measurements                                             | 55 |

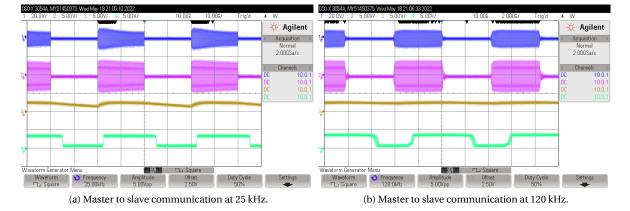

|    | 6.1 Data Transfer Performance                                        | 55 |

|    | 6.1.1 Master to Slave Signal Integrity                               | 55 |

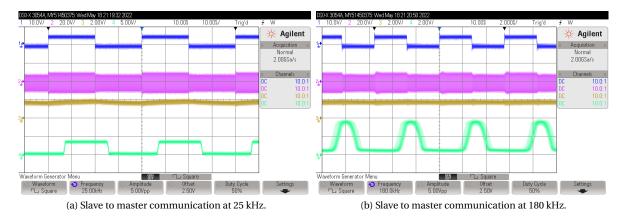

|    | 6.1.2 Slave to Master Signal Integrity                               |    |

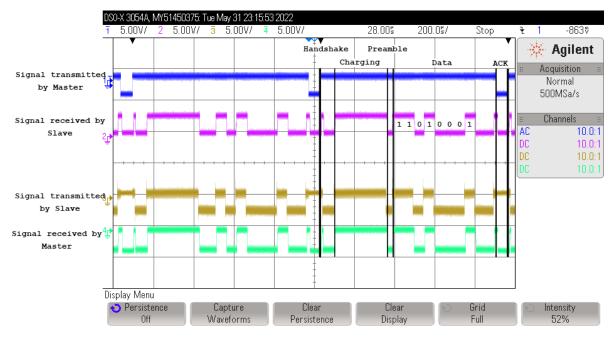

|    | 6.1.3 Performance of the Data Transfer Protocol.                     |    |

|    | 6.2 Power Transfer Efficiency                                        |    |

|    | 6.2.1 Measurement Setup                                              |    |

|    | 6.2.2 Raw Efficiency Measurements                                    |    |

|    | 6.2.3 Subsystem Power Usage                                          |    |

|    | 6.2.4 Efficacy of the Coupling Estimation6.3 Power and Data Transfer |    |

|    |                                                                      | 02 |

| 7  |                                                                      | 65 |

|    | 7.1 Inductive Link                                                   |    |

|    | 7.2 Master Design.                                                   |    |

|    | 7.3 Slave Design                                                     |    |

|    | 7.4 Full System Performance                                          | 67 |

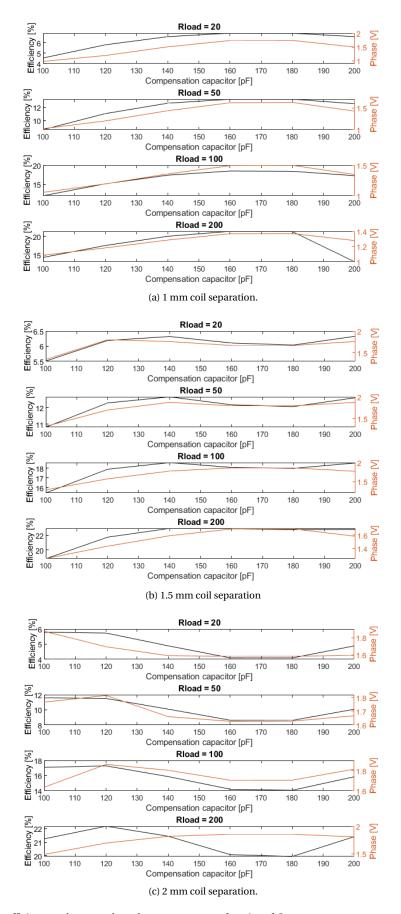

| А  | Additional numeric efficiency and power simulations                  | 69 |

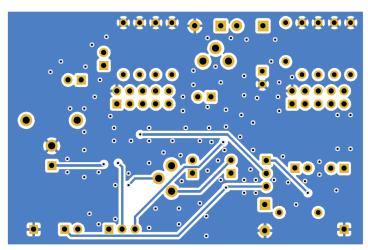

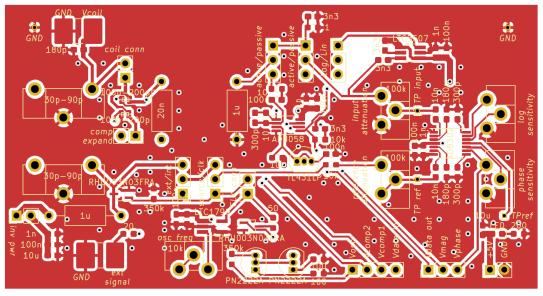

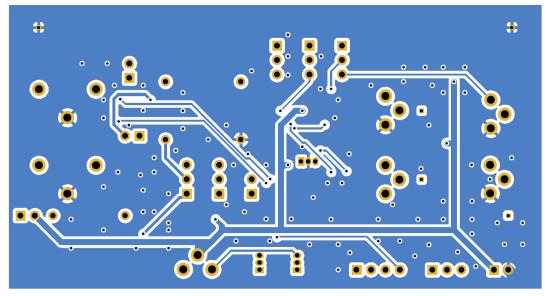

| В  | Full Prototype Schematics                                            | 73 |

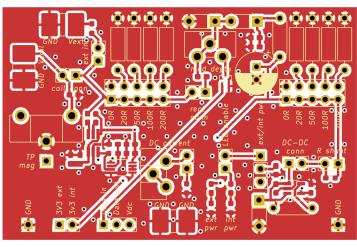

| С  | PCB layouts                                                          | 77 |

| D  | Power Draw Interpolations                                            | 79 |

|    | -                                                                    |    |

| Bı | bliography                                                           | 81 |

# 1

## Introduction

The increasing miniaturisation and power efficiency of integrated circuits has allowed for electronic devices to be more easily integrated into everyday items. The clothing industry has not been blind to this trend and the interest in and market for electronics integrated into clothing, known as e-textiles, is growing [1] [2]. Over the last few years, various companies have released sensor-enabled clothing, in applications ranging from monitoring vital signs [3], to interfacing with smart phones [4], to supporting athletic activities [5] [6].

As the field of e-textiles develops, three generations have been identified.

- First generation: the smart component are largely an add-on to an otherwise normal piece of clothing, and only added after or during the final stage of production.

- Second generation: the smart components are directly integrated into the garment.

- Third generation: the fabric itself forms the smart component, with all the sensing, processing and communication done by structures of the fibres of the garment.

While never reaching main-stream popularity in the consumer market, first generation e-textiles are well developed and commercially available. Second generation products are still a subject of active research, but products in this category are starting to hit the market. A lot of research is currently being done into third generation products [7], but products in this category are yet to leave the research phase.

The most common use of smart clothing is the measurement of certain aspects of the body. For the sensing of certain body-wide metrics, such as body temperature [8], heart-rate [9] [10], breath-rate [11], blood pressure [12], etc. a single node is sufficient. However, the measuring of more complex metrics such as muscle activity [13] or limb movement [14] require a network of sensors distributed around the garment. For reasons of cost, efficiency, and spectral pollution it is not desirable to have each node in such a network wirelessly connected to the outside world. It is preferred to have all the sensor nodes within the garment connected to a central node. This central node will communicate with the outside world, and supply power to all other nodes. This is known as a body area network (BAN).

Most implementations of such a BAN involve connecting the nodes using conductive paths that are directly integrated into the clothing [15] [16]. These interconnecting paths carry data from, and supply power to the sensors, ideally without compromising on the comfortability and wearability of the garment. The use of conductive materials in clothing is traceable back to ancient times, usually in the form of gold or silver coated threads as a decorating feature. These could be manufactured by for example hammering a piece of gold flat, and using it to surround a piece of silk [17]. The same idea is still used for conductive threads today, although the manufacturing techniques are quite different. A common way of creating conductive strands for e-textiles is to take a conventional nylon or silk strand, and coat it in a conductive material [18]. These coatings commonly consist of either an intrinsically conductive polymer (ICP), a carbon-based coating or a metal. The carbon based approaches offer greater strength and durability, while the metal coatings have greater conductivity [18]. These conductive fibres can be woven directly into the textile, or embroidered on to it. Another way of creating conductive paths on a piece of textile is to print a conductive material directly onto the material [19] [20]. This technique better preservers the flexibility and feel of the textile it is printed on, which could result in more comfortable clothing. However, since textiles are generally very porous materials, it can be difficult to maintain a reliable electrical connection as the material stretches. After many years of development, conductive paths in clothing can now be made to withstand the mechanical stresses of everyday wear [21]. However, these conductive paths need to be connected to the (usually rigid) electronics. While extensive research has been done on the conductive paths themselves, the work done in investigating the textile to electronics interface is quite limited. In the world of electronics, connections on printed circuit boards (PCBs) are usually made by soldering. While some success has been had recently using ultrasonic soldering [22], soldering is generally not compatible with textiles, as the high temperatures required for soldering are not compatible with fabrics, and the connections are quite brittle [23]. Other techniques such as crimped connectors and a polymer adhesive have been tested in [24], but showed limited mechanical strength. Success has also been had by embroidering flexible PCBs directly onto the fabric [25], but doubts still exist about the long-term reliability [26].

All of the above mentioned techniques result in permanent bonding of the fabric and the electronics. This presents an additional set of challenges. Firstly, in order for a smart garment to appeal to a wide market, it is important for the garment to be easily machine washed. This is especially important when it comes to smart sportswear. A typical wash cycle will impart very significant mechanical and chemical stresses [27], which puts significant extra constraints on the design of (the casing for) the electronics. The second problem is that textiles and electronics have very different failure modes. It would be a shame to discard a full clothing piece because a sensor contact has corroded. Conversely, it would be wasteful to throw away a working sensor system simply because its host garment has a tear in it. E-textiles are predicted to contribute significantly to global e-waste, and repairability and end-of-life care should not be an afterthought [28].

Some of the above mentioned problems can be solved by using connectors for the sensor nodes. While some connectors especially designed for e-textiles do exist, they have to address the same reliability and washability concerns mentioned before. In certain applications button connectors have been used [23]. Buttons are a proven method for creating connections in the textile industry, and have shown to be very reliable. However, they add a lot of bulk and can only implement a single electrical connection at a time, making them only suitable for certain applications.

In [29] electrical connectors embedded in both button and buckle connections are evaluated for military use. It was concluded that any sufficiently rugged and environmentally sealed connector was too bulky for practical use, although the authors do see some potential for buckle based designs in a civilian setting.

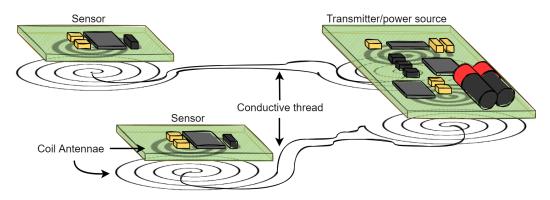

This project aims to find a solution to the reliability, washability and repairability problems. Instead of a galvanic connection between the conductive paths and the electronics, the power and data transfer will occur inductively. The conductors inside the textile terminate on both ends in planar coils embedded directly below pouches holding the electronics. The electronics are also provided with planar coils, which couple to the coils inside the garment as demonstrated in [30]. Across this link both data and power can be transferred. A schematic overview of this is shown in figure 1.1.

#### 1.1. Smart Sensor Shorts Project

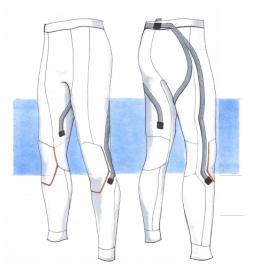

This project is part of the Sensor Shorts project, an initiative of the Citius Altius Sanius program. The goal of the program is make injury free sporting available to everyone. The Sensor Shorts are a sporting garment with embedded sensors which measure the movement of an athletes legs. This data will be used by movement scientists to predict when hamstring injuries are about to happen. In order to achieve this the sensor data must be read out and transmitted in real time, both during training and in matches.

Under the supervision of PhD candidate Annemarijn Steijlen several prototypes have already been made. In these prototypes, off-the-shelf inertial measurement units (IMUs) are mounted on the knees and lower back of a pair of sporting shorts. The IMUs measure the linear acceleration and angular velocity of the limbs. They also contain an electronic compass, to account for gyroscope drift. The data from these sensors is sent via an SPI bus to a central node on the lower back, where it is stored and transmitted. The central node also supplies power to the sensor nodes. The connection between the sensor nodes and the central node is made using off-the-shelf, flexible, embroidered wires. These wires terminate in a small clasp connector, to allow the nodes to be separated from the garment. The intended use for these connectors is to make semipermanent connections within electronic equipment. As a result, they are not designed to withstand many connect/disconnect cycles. The researchers found these connections to be unreliable, and they formed a bottleneck in the user experience. Hence the start of this project.

The sensors used are the ICM-20649 gyroscope and accelerometer, and the AK8963 magnetometer. They are read out at 250 Hz and 100 Hz respectively, resulting in a combined data rate of 28.8 kbit/s. They have a combined power usage of roughly 32 mW. This serves as an outline for the requirements set for this project.

Figure 1.1: Overview of the wireless coupling system.

Figure 1.2: Drawing of the second prototype of the sensor pants [31]. The latest version only contains three sensor nodes, one on the lower back and one per knee.

#### **1.2. Previous Research**

A lot has been written on the broader topic of near-field battery-less sensors [32]. These are commonly referred to as Radio Frequency Identification (RFID) sensors. In an RFID sensor, the sensor does not contain its own power source. Instead, power is transmitted to it via radio waves. This power is used to both readout the sensor, and transmit back the measured data (usually via back-scattering). Since the power contained in a radio wave is inversely proportional to the square of the distance to the source, most RFID sensors operate in the near field. This technology has also been implemented into clothing [33]. However, in most publications, the sensor and the antenna are combined. The sensed quantity alters the reflective properties of the antenna directly, without the need of any traditional readout electronics. This change in antenna properties can be measured from a distance using a readout antenna. Sensors that have been made in this way include, but are not limited to, sweat sensors [34], strain sensors [35], and even very low resolution accelerometers [36]. While the principles behind these types of sensors is similar to the ones used in this work, the techniques are quite different.

Not much has been published on the specific topic of textile-integrated inductive power and data transfer. However, the following papers have been found that are of particular relevance to this project.

In 2016, Saisai Wen et al. developed a battery-less, NFC-based sensor patch for measuring skin temperature, with the aim being to investigate the viability of wearable e-textile sensors for use in health monitoring [37]. The sensor consisted of a MLX90129 chip, mounted on a flexible polyamide substrate. The MLX90129 is a chip developed by Melexis that facilitates the communication and energy harvesting for RFID sensors. It has a temperature sensor built in, and can communicate with external sensors using SPI or I2C. It uses the ISO 15693 NFC protocol to both harvest power and wirelessly transmit the sensor data. In [37] a coil made of a conductive fabric, placed on top of the polyamide substrate, was used as the antenna for the MLX90120 chip. The sensor could be powered and read out from a short distance using an app on an NFC-capable smartphone. The authors do not elaborate on the process used to fabricate, the coil antenna, not do they provide details on its characteristics. They also do not provide any data on the achieved communication speed and power transfer of the inductive link.

Four years later, Rongzhou Lin et al. [38] published a design of a BAN network using inductively coupled sensors for posture and temperature monitoring. Several strain- and temperature sensors were positioned on various points on the body. These sensors would inductively couple to coils embedded into a flexible polyester-spandex shirt. Conductive threads embedded in the garment connected these coils to a central hub, where they would again inductively connect to a smartphone. All power and data transfer to and from these nodes occurred via these coupled inductors. The strain sensors were fabricated within a piece of e-textile, and were read out using a Texas Instruments RF430FRL152H chip, which also facilitated the temperature sensing. This chip is similar to the MLX90129 used in [37], as it also uses the ISO 15693 NFC protocol for wireless power and data transfer. The coils were embroidered directly into the fabric of the garment, using the same conductive threads that were used as interconnects. Further details on the design and characterisation of these coils was published separately [39]. Using an NFC enabled smartphone at the hub node, the researchers reported an 8 Hz sampling rate for one sensor, or a 1.3 Hz sampling rate when all six sensors where used. The sampling resolution was 14-bit, leading to an overall data-rate of 112 bit/s. This is the only publication found that investigates the use of two pairs of coupled coils, as is also used in our work. However, the paper does not elaborate on the challenges this introduces, nor does it attempted to model this arrangement.

The previous publications both rely on the ISO 15693 NFC protocol [40]. This is a protocol originally designed for near field identification of for example library cards. A reader sends out a signal requesting data from a card. The card uses the energy in this signal to send back an identifying code. Devices following this protocol operate at 13.56 MHz, and are theoretically capable of communicating at 26.69 kbit/s in both directions simultaneously. This is slightly less than the 28.8 kbit/s required in this project. They are capable of operating at ranges up to one meter, which is far beyond what this project requires.

In 2020, Ken Takaki et al. also developed an inductively coupled power and data transfer system [41]. This time with the aim of connecting electronics across the hinge of a pair of glasses. The researchers report a power transfer efficiency of 87%, and a communication speed of 50 Mbit/s, with a bit error rate of  $10^{-6}$  at a coil separation of 1.6 mm. These results are however theoretical, based on measured S-parameters and estimated noise figures. As a result they are likely highly optimistic.

The above mentioned systems all rely on a single carrier wave that contains both the power and the data. However, in certain applications it is useful to use separate carriers for the power and data [42] [43] [44] [45]. This is particularly useful for high power applications, where power transfer is prioritized over data speeds, as the modulation required to transmit data will in most cases reduce the overall signal power. Transmitting the data at a higher frequency will allow it to utilize more bandwidth, increasing the data rate. The power electronics tend to operate more efficiently at lower frequencies. A major challenge associated with this technique is that the switch-mode power amplifiers commonly used to generate the power signal tend to produce a lot of high frequency noise, which can interfere with the data signal. Some publications therefore opt to transmit

the data at a lower frequency than the power [42] [45]. This improves reliability at the cost of data rate. A challenge faced with all designs of this nature is that the inductive link needs to be able to efficiently transmit signals at two different frequencies, which is not trivial.

Some publications take this a step further and use separate coils for the power and data transfer [46] [47] [48]. In most cases the power and data coils are aligned on the same axis, but radially or axially displaced from one another. While the design of such a system from a circuit design perspective is relatively straight forward, the design of the coils themselves is quite complex. In order to minimize cross-talk between the data and power coils the coupling between them needs to be minimized, while simultaneously maximizing the coupling to the corresponding coil on the secondary side. This presents significant design challenges, especially when lateral displacement between the primary and secondary side is involved.

#### 1.3. This Work

As mentioned previously, the application requires a system with a data rate of at least 28.8 kbit/s, and a continuous power transfer of at least 32 mW. To leave some margin for error, the specifications for this project are set at 50 kbit/s and 50 mW. No specific requirement is set for the bit error rate, but it should be within the bounds correctable by a simple error correction scheme, although the details of this error correction are beyond the scope of this work. The power flow should not be interrupted under normal conditions. Total power transfer and transfer reliability have been emphasised over transfer efficiency, although the later should still be within reason. The physical size of the inductor should fit within a 5 cm x 5 cm square.

To limit the scope of this project, rigid planar coils are used instead of flexible or integrated coils. A prototype of the system has been built, and serves as a proof of concept. Since this is not intended as a final product, the electronics have been allowed to extend beyond the size limit. This allows the use of off-the-shelf components, instead of requiring all functionality to be housed within a single chip. These requirements are summarised in the list below, in the order of importance.

- Data rate of at least 50 kbit/s

- · Continuous power transfer rate of at least 50 mW

- Stable power connection

- Stable data connection

In order to better understand the challenges in designing such a system, three research questions have been posed:

- 1. Under what conditions will an inductive link behave like a direct connection?

- 2. What techniques should be used to modulate and demodulate the data and power on both sides of the link?

- 3. What data transfer protocol is practical for use in a combined power and data transfer system, and what is the trade-off between power and data rate?

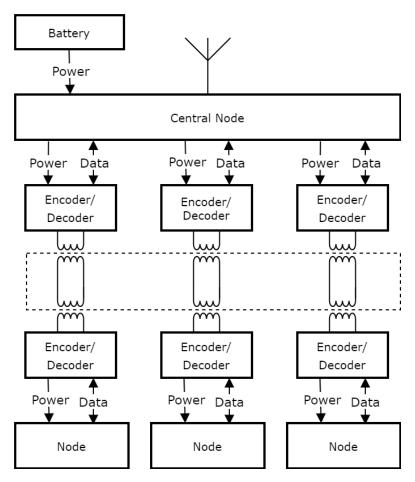

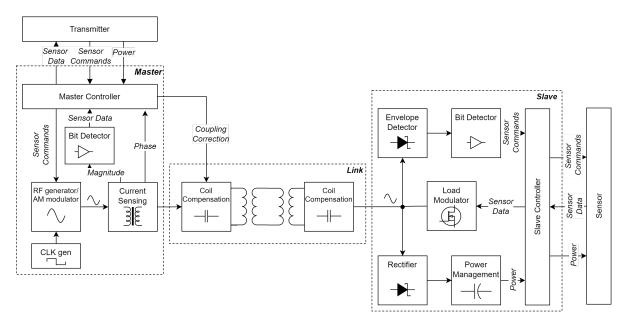

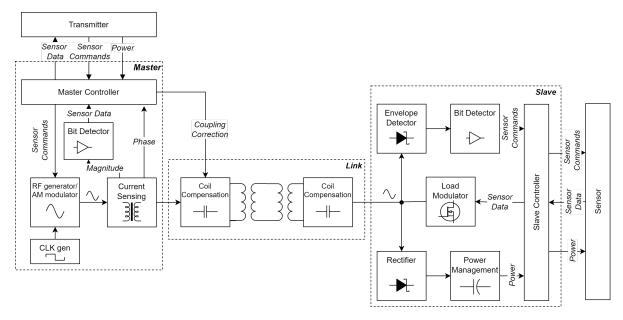

The system is divided into three distinct subsections: the master, the slave, and the link. The master interfaces with the battery and the transmitter on one side, and the link on the other. It is responsible for generating the carrier signal, and modulates this signal to send data and acknowledgements to the slave. It also demodulates the data coming from the slave, and presents this in a usable form to the transmitter. The slave acts as a bridge between the link and the sensor. It harvests energy from the carrier, and performs demodulation. It modulates the data from the sensor onto the carrier by way of load modulation. The link forms the connection between the master and the slave. It consists of four planar coils, forming two pairs, as well as some surrounding capacitors.

A diagram of these subsections, as well as the subsystems within them, is shown in figure 1.3.

Each of these subsystems will be discussed in detail in the thesis, starting with an analysis of the link. This is followed by a discussion of first the master and then the slave. After this the implementation of the controllers and the data protocol is discussed. The thesis concludes with a chapter on the measured results of the full system, followed by a discussion and some recommendations for future work.

Figure 1.3: Block diagram of all the subsystems.

# 2

### Inductive Link

In this chapter the design and characteristics of both the coils forming the inductive link, and the compensation circuits surrounding them will be discussed. As introduced in the previous chapter, the purpose of the link is to provide power to the sensor node, and to allow for bi-directional communication between the central node (master) and the sensor node (slave). In order to effectively do this the link should have the following properties:

- 1. For transmitting to the slave, the transmit voltage of the master should be measurable by the slave.

- 2. For transmitting to the master, the slave side impedance should be measurable by master.

- 3. For high data speeds, the quality factor of the link should be as low as possible.

- 4. For high power transfer efficiency, the link should introduce minimal losses.

- 5. For effective power transfer, the impedance on the master and slave side should be matched to the link impedance.

However, since the signal generator in the slave and the rectifier in the load are non-linear in nature, the exact values of these impedances are ill-defined. Moreover, the input impedance of the slave is dependent on its power draw, which cannot be guaranteed to be constant over time. In order to disconnect the design of the link from that of the slave and master, the link is designed in such a way that the impedance of the slave is mirrored to master. In this way, the inductive link essentially behaves as a direct wired connection. This also guarantees requirements 1 and 2.

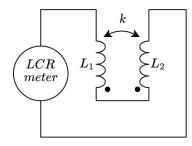

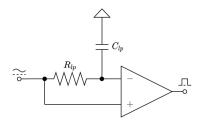

The link can be analyzed as a two-port network with the master attached to port one and the slave to port two. In order to characterise the input-output characteristics of any two-port network, transmission matrices can be used [49]. A transmission matrix defines the input voltage and current ( $V_1$  and  $I_1$ ) in terms of the output voltage and current ( $V_2$  and  $I_2$ ) [49]. This is shown in equation 2.1. The polarities of the voltages and currents are given in figure 2.1.

$$\begin{bmatrix} V_1 \\ I_1 \end{bmatrix} = \begin{bmatrix} A & B \\ C & D \end{bmatrix} \begin{bmatrix} V_2 \\ -I_2 \end{bmatrix}$$

$$\textcircled{(2.1)}$$

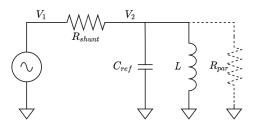

Figure 2.1: Voltage and current definitions of a two-port matrix.

As mentioned earlier, the link is considered optimal when the inductive coupling behaves the same as a physical wired connection. In a direct connection, the output voltage is the same as the input voltage, and

the same is true for the input and output currents. The optimal transmission matrix is therefore given by the identity matrix:

$$\begin{bmatrix} V_1\\ I_1 \end{bmatrix} = \begin{bmatrix} 1 & 0\\ 0 & 1 \end{bmatrix} \begin{bmatrix} V_2\\ -I_2 \end{bmatrix}$$

(2.2)

#### 2.1. Analysis of the Double Inductive Link

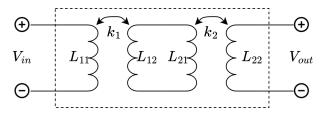

The link consists of a pair of inductively coupled coils at the central node, and a pair at the sensor node. These two pairs are connected using a pair of wires that is integrated into the clothing. This link can be modeled using the circuit shown in 2.2.

Figure 2.2: Simple electrical model of the link.

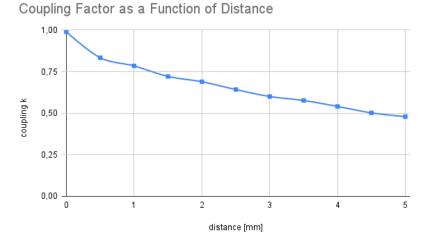

In this model  $L_{11}$  and  $L_{12}$  represent the coils near the central node, while  $L_{21}$  and  $L_{22}$  represent the coils on the sensor node. The coils by the central node and by the sensor node are coupled with coupling factor  $k_1$  and  $k_2$  respectively. Both the inductance L and the coupling k are gravely affected by the physical design of the coil, as well as many environmental factors. Furthermore, neither L nor k can be assumed to remain constant during operation. The coils are preferably made from a flexible material, in order for the clothing to remain comfortable. As the coils bend, both their mutual-inductance and their self-inductance will change.

In order to simplify the analysis in the coming sections, this model is kept quite simple. In reality, there would be many parameters, including the finite resistance of the coils, inter-winding capacitances, as well as non-idealities related to wires mounted in the clothing. The actual implementation of the system inside a garment is considered outside the scope of this work, so the parameters related to this are not further discussed. However, in order to validate this model some measurements on a prototype system using rigid planar coils are presented at the end of this chapter.

In order to analyze the full circuit, it is useful to first consider a single inductive link shown in figure 2.3. By applying Kirchhoffs voltage law equation 2.3 is obtained.

$$\begin{bmatrix} V_{in} \\ V_{out} \end{bmatrix} = \begin{bmatrix} j\omega L_{11} & j\omega k_1 \sqrt{L_{11}L_{12}} \\ j\omega k_1 \sqrt{L_{11}L_{12}} & j\omega L_{12} \end{bmatrix} \begin{bmatrix} I_{in} \\ I_{out} \end{bmatrix}$$

(2.3)

Converting the Z-matrix from equation 2.3 to a transmission matrix gives equation 2.4:

$$\begin{bmatrix} V_{in} \\ I_{in} \end{bmatrix} = \frac{1}{k_1 \sqrt{L_{11}L_{12}}} \begin{bmatrix} L_{11} & j\omega L_{11}L_{12}(1-k_1^2) \\ \frac{1}{j\omega} & L_{12} \end{bmatrix} \begin{bmatrix} V_{out} \\ I_{out} \end{bmatrix}$$

(2.4)

Figure 2.3: Ideal model of two coupled inductors.

Using the cascading property of the transmission matrix, the transmission matrix of the double link can be calculated by multiplying the transmission matrices of the individual links [49]. The result of this is given in equation 2.5.

$$\begin{bmatrix} V_{in} \\ I_{in} \end{bmatrix} = \frac{1}{k_1 k_2 \sqrt{L_{11} L_{12} L_{21} L_{22}}} \begin{bmatrix} L_{11} L_{21} - L_{11} L_{12} (k_1^2 - 1) & j \omega L_{11} L_{22} [L_{12} (1 - k_1^2) + L_{21} (1 - k_2^2)] \\ \frac{L_{12} + L_{21}}{j \omega} & L_{21} L_{22} - L_{21} L_{22} (k_2^2 - 1) \end{bmatrix} \begin{bmatrix} V_{out} \\ I_{out} \end{bmatrix}$$

(2.5)

It is assumed that the design of the link is symmetrical. This is to say that the coils embedded into the fabric on both the slave and master side are of the same design. Furthermore, the coils on the slave and master boards are also designed to be the same. Finally, the mounting of the coils on both sides of the link is also considered to be equal. This allows for the following simplifications:

$$L_{11} = L_{22} = L, L_{12} = L_{21} = L_2, k_1 = k_2 = k$$

(2.6)

Substituting the simplifications from equation 2.6 into 2.5 gives:

$$\begin{bmatrix} V_{in} \\ I_{in} \end{bmatrix} = \frac{1}{k^2} \begin{bmatrix} 2-k^2 & 2j\omega L(1-k^2) \\ \frac{2}{j\omega Lk} & 2-k^2 \end{bmatrix} \begin{bmatrix} V_{out} \\ I_{out} \end{bmatrix}$$

(2.7)

Note how equation 2.7 no longer contains  $L_1$ , meaning that as long as equation 2.6 holds, the performance of the link is not influenced by the self inductance of the coils embedded into the fabric. This does not mean the design of this coil requires no attention, as it still influences the coupling k. There are also several parasitic effects that have to be taken into account.

Rewriting the transmission matrix from 2.7 back into a Z matrix gives:

$$\begin{bmatrix} V_{in} \\ V_{out} \end{bmatrix} = \begin{bmatrix} \frac{1}{2} j \omega L (2-k^2) & \frac{1}{2} j \omega L k^2 \\ \frac{1}{2} j \omega L k^2 & \frac{1}{2} j \omega L (2-k^2) \end{bmatrix} \begin{bmatrix} I_{in} \\ I_{out} \end{bmatrix}$$

(2.8)

Now, substituting  $\hat{L} = \frac{1}{2}L(2-k^2)$  and  $\hat{k} = \frac{k^2}{2-k^2}$  into 2.8, 2.9 is obtained:

$$\begin{bmatrix} V_{in} \\ V_{out} \end{bmatrix} = \begin{bmatrix} j\omega\hat{L} & j\omega\hat{L}\hat{k} \\ j\omega\hat{L}\hat{k} & j\omega\hat{L} \end{bmatrix} \begin{bmatrix} I_{in} \\ I_{out} \end{bmatrix}$$

(2.9)

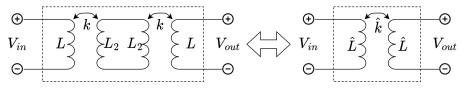

This shows that a system with a double inductive link behaves electrically identical to a single symmetrical link, with self inductance  $\hat{L}$  and coupling  $\hat{k}$  (assuming that equation 2.6 holds). This is illustrated in figure 2.4.

Figure 2.4: Electrically equivalent model of the double inductive link.

It is useful to convert the Z-matrix from equation 2.9 back into a transmission matrix for use later on:

$$T_{link} = \begin{bmatrix} \frac{1}{\hat{k}} & j\omega\hat{L}\frac{(1-\hat{k}^2)}{\hat{k}}\\ \frac{1}{j\omega\hat{L}\hat{k}} & \frac{1}{\hat{k}} \end{bmatrix}$$

(2.10)

#### 2.2. Link Compensation

When comparing the transmission matrix in equation 2.7 to the ideal identity matrix from equation 2.2, it is clear that the double link on its own does not have ideal performance. This discrepancy between the real and ideal matrices will manifest itself into an apparent inductance parallel to the load, even at perfect coupling (k = 1). This inductance will reduce the current flowing into the load, and will make the load modulation less effective. In order to compensate for this, a capacitor network can be placed around the load, which will be in resonance with the apparent inductance of the system at the operating frequency  $\omega_0$ . This effectively matches the link impedance to that of the load and the source, significantly improving both power and data transfer. This is known as Resonant Wireless Power Transfer (RWPT) [50].

| Topology | $C_p$                                                                          | Cs                           | [ <i>T</i> ]                                                                                                                                                                                                                                          |

|----------|--------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SS       | $\frac{1}{\omega^2 \hat{L}}$                                                   | $\frac{1}{\omega^2 \hat{L}}$ | $\begin{bmatrix} 0 & \frac{\omega \hat{k} \hat{L}}{j} \\ \frac{j}{\omega \hat{k} \hat{L}} & 0 \end{bmatrix}$                                                                                                                                          |

| SP       | $rac{\hat{1}}{\omega^2\hat{L}(1-\hat{k}^2)}$                                  | $\frac{1}{\omega^2 \hat{L}}$ | $\begin{bmatrix} \hat{k} & 0 \\ 0 & \frac{1}{\hat{k}} \end{bmatrix}$                                                                                                                                                                                  |

| РР       | $\frac{(1-\hat{k}^2)\hat{L}}{\omega^2\hat{L}^2(1-\hat{k}^2)^2+\hat{k}^4Z_l^2}$ | $\frac{1}{\omega^2 \hat{L}}$ | $\begin{bmatrix} \hat{k} & \frac{\hat{L}\omega(1-\hat{k}^2)}{\hat{k}} \\ \frac{j\omega\hat{L}\hat{k}(1-\hat{k}^2)}{\omega^2\hat{L}^2(1-\hat{k}^2)^2+Z_l\hat{k}^4} & \frac{Z_l\hat{k}^4}{\omega^2\hat{L}^2(1-\hat{k}^2)^2+Z_l\hat{k}^4} \end{bmatrix}$ |

| PS       | $\frac{Z_l^2}{\omega^2 \hat{L} Z_l^2 + \omega^3 \hat{L} \hat{k}^4}$            | $\frac{1}{\omega^2 \hat{L}}$ | $\begin{bmatrix} \frac{1}{\hat{k}} & \frac{\omega\hat{k}\hat{L}}{j}\\ \frac{\hat{L}\hat{k}^{3}\omega}{j\hat{L}^{2}\hat{k}^{4}\omega^{2}+jZ_{l}} & \frac{\hat{k}Z_{l}}{\hat{L}^{2}\hat{k}^{4}\omega^{2}+Z_{l}} \end{bmatrix}$                          |

Table 2.1: Common values for primary compensation capacitors and their resulting transmission matrices at resonance ( $\omega = \omega_0$ ).

#### 2.2.1. Design of the Compensation Network

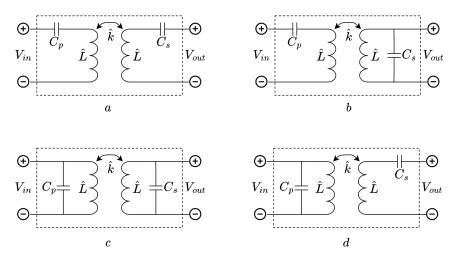

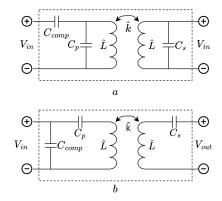

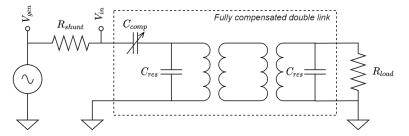

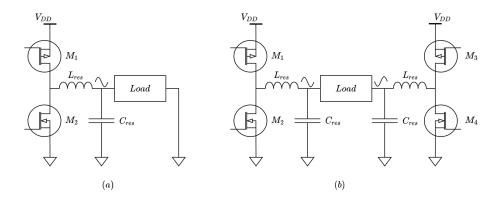

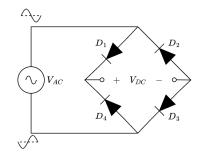

As previously established, the double link can be seen as behaving the same as the more conventional single link. This means that it is possible to use existing and well documented compensation techniques. Although others exist and are used, the most common compensation techniques are SS (series-series), SP (series-parallel), PS (parallel-series) and PP (parallel-parallel) [50] [51] [52] [53] [54]. In this naming convention the words refer to capacitors added to the primary and secondary side respectively. All four topologies are shown in figure 2.5.

Figure 2.5: Common compensation techniques: Series-Series (a), Series-Parallel (b), Parallel-Parallel (c), and Parallel-Series (d).

In principle, the capacitor on the secondary side is chosen to be in resonance with the self-inductance of the secondary coil at the operating frequency [51], so  $C_s = \frac{1}{w^2 \hat{L}}$ . The value of the primary capacitor is then chosen in such a way that at the operating frequency, the imaginary component of the input impedance equals zero [51] [54]. The values of these capacitors and their resulting transmission matrices are shown in table 2.1.

As mentioned before, the ideal transmission matrix would be the identity matrix, as the impedance seen by the master would simply be the slave impedance, with no impedance transformation occurring in the link. This rules out the SS and PS topologies, as even with perfect coupling (k = 1), their transmission matrix does not approach the identity matrix. The two remaining techniques do mirror the impedance properly, as long as the coupling is perfect. However, by looking at their input impedances (equations 2.11 and 2.12 for SP and PP respectively) a new problem presents itself.

$$Z_{in,SP} = Z_l \hat{k}^2 \tag{2.11}$$

$$Z_{in,PP} = \frac{\hat{L}^2 \omega^2 (\hat{k}^4 - 2\hat{k}^2 + 1) + Z_l^2 \hat{k}^4}{Z_l \hat{k}^2}$$

(2.12)

While they both indeed converge to  $Z_l$  for k = 1, their behaviour is difficult to compensate for if this is not the case. Both apply a transformation to the real part of the impedance, which requires at least two reactive components to compensate for. If left uncompensated, a variation in the coupling between the coils will not be distinguishable from any intentional load modulation.

In order to find a more elegant solution, two additional compensation networks where considered. The first circuit, "A", uses a PP topology, but both capacitors are of equal value. The same goes for the second circuit, "B", although this one uses a SS topology. The transmission matrices can be calculated by multiplying the transmission matrices for series and parallel capacitors with the transmission matrix for the link given in 2.10, as shown below.

$$T_A = \begin{bmatrix} 1 & 0\\ j\omega C_{p,A} & 1 \end{bmatrix} \begin{bmatrix} \frac{1}{\hat{k}} & j\omega \hat{L} \frac{(1-\hat{k}^2)}{\hat{k}}\\ \frac{1}{j\omega \hat{L}\hat{k}} & \frac{1}{\hat{k}} \end{bmatrix} \begin{bmatrix} 1 & 0\\ j\omega C_{s,A} & 1 \end{bmatrix}$$

(2.13)

$$T_B = \begin{bmatrix} 1 & \frac{1}{j\omega C_{p,B}} \\ 0 & 1 \end{bmatrix} \begin{bmatrix} \frac{1}{\hat{k}} & j\omega \hat{L} \frac{(1-\hat{k}^2)}{\hat{k}} \\ \frac{1}{j\omega \hat{L}\hat{k}} & \frac{1}{\hat{k}} \end{bmatrix} \begin{bmatrix} 1 & \frac{1}{j\omega C_{s,B}} \\ 0 & 1 \end{bmatrix}$$

(2.14)

The resonance capacitors  $C_p$  and  $C_s$  are now chosen in such a way that for  $\hat{k} = 1$  and  $\omega = \omega_0$ , the system matrix converges to the identity matrix. The resulting capacitor values and transmission matrices of the two networks are shown in table 2.2.

| Topology | $C_p$                                     | $C_s$                                     | [T]                                                                                                                                                                                                                                                                                                                      |

|----------|-------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PP "A"   | $\frac{1}{\omega_0^2 \hat{L}(\hat{k}+1)}$ | $\frac{1}{\omega_0^2 \hat{L}(\hat{k}+1)}$ | $\begin{bmatrix} \frac{\omega^2(\hat{k}-1)+\omega_0^2}{\hat{k}\omega_0^2} & \frac{j\hat{L}\omega(1-\hat{k}^2)}{\hat{k}} \\ \frac{j(\omega^2-\omega_0^2)(\omega^2(\hat{k}-1)+\omega_0^2(\hat{k}+1))}{\hat{L}\hat{k}\omega\omega_0^4(\hat{k}+1)} & \frac{\omega^2(\hat{k}-1)+\omega_0^2}{\hat{k}\omega_0^2} \end{bmatrix}$ |

| SS "B"   | $\frac{1}{\omega_0^2 \hat{L}(1-\hat{k})}$ | $\frac{1}{\omega_0^2 \hat{L}(1-\hat{k})}$ | $\begin{bmatrix} \frac{1}{\hat{k}} + \frac{\omega_0^2(\hat{k}-1)}{\hat{k}\omega^2} & \frac{j\hat{L}(\omega^2 - \omega_0^2)(1-\hat{k})(\omega^2(\hat{k}+1) + \omega_0(\hat{k}-1))}{\hat{k}\omega^3} \\ \frac{1}{j\hat{L}\hat{k}\omega} & \frac{1}{\hat{k}} + \frac{\omega_0^2(\hat{k}-1)}{\hat{k}\omega^2} \end{bmatrix}$ |

Table 2.2: Component values and transmission matrix for the proposed "A" and "B" circuits

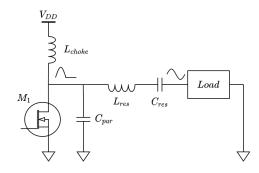

When operating at the operating frequency  $w_0$ , both A and B converge to the identity matrix as k approaches 1. As they stand they do not offer any benefits over the traditional SP and PP compensation networks shown earlier. However, they allow for much easier tuning to a specific coupling factor. By placing an additional capacitor in series (A) or in parallel (B), it is possible to tune the system to a specific estimated coupling  $\bar{k}$ . Whenever the coupling  $\hat{k}$  is equal to the estimate  $\bar{k}$ , the transmission matrix will approach the identity matrix. The resulting schematics are shown in figure 2.6. The transmission matrix of a series and parallel capacitor respectively:

$$T_A = \begin{bmatrix} 1 & \frac{1}{j\omega C_{comp,A}} \\ 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 \\ j\omega C_{p,A} & 1 \end{bmatrix} \begin{bmatrix} \frac{1}{\hat{k}} & j\omega \hat{L} \frac{(1-\hat{k}^2)}{\hat{k}} \\ \frac{1}{j\omega \hat{L}\hat{k}} & \frac{1}{\hat{k}} \end{bmatrix} \begin{bmatrix} 1 & 0 \\ j\omega C_{s,A} & 1 \end{bmatrix}$$

(2.15)

$$T_B = \begin{bmatrix} 1 & 0\\ j\omega C_{comp,B} & 1 \end{bmatrix} \begin{bmatrix} 1 & \frac{1}{j\omega C_{p,B}}\\ 0 & 1 \end{bmatrix} \begin{bmatrix} \frac{1}{\hat{k}} & j\omega \hat{L} \frac{(1-\hat{k}^2)}{\hat{k}}\\ \frac{1}{j\omega \hat{L}\hat{k}} & \frac{1}{\hat{k}} \end{bmatrix} \begin{bmatrix} 1 & \frac{1}{j\omega C_{s,B}}\\ 0 & 1 \end{bmatrix}$$

(2.16)

By choosing  $C_{comp,A} = \frac{\bar{k}}{\bar{L}\omega_0^2(1-\bar{k}^2)}$  and  $C_{comp,B} = \frac{1}{\bar{L}\bar{k}\omega_0^2}$ . When  $\bar{k} = \hat{k}$  both systems will approach the identity matrix at  $\omega_0$ . This behaviour is summarized in table 2.3.

Circuit A provides another benefit when it comes to the coupling compensation. When  $C_{p,s}$  and  $C_{comp}$  are rewritten in terms of k and L instead of  $\hat{k}$  and  $\hat{L}$ , the following equations emerge:

$$C_{p,s} = \frac{1}{\omega_0^2 L} \tag{2.17}$$

$$C_{comp} = \frac{k^2}{2L\omega_0^2(1-k^2)}$$

(2.18)

Figure 2.6: Circuit A with series compensation capacitor (a), circuit B with parallel compensation capacitor (b)

| Topology | $C_{p,s}$                                 | $C_{comp}$                                       | [T]                                                                                                                                               | Z <sub>in</sub>                                                                                                |

|----------|-------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| PP "A"   | $\frac{1}{\omega_0^2 \hat{L}(\hat{k}+1)}$ | $\frac{\bar{k}}{\hat{L}\omega_0^2(1-\bar{k}^2)}$ | $\begin{bmatrix} 1 & -j\omega_0 \hat{L} \frac{\hat{k}^2 \bar{k} - \hat{k} \bar{k}^2 + \hat{k} - \bar{k}}{\hat{k} \bar{k}} \\ 0 & 1 \end{bmatrix}$ | $Z_{in} - j\omega_0 \hat{L} \frac{\hat{k}^2 \bar{k} - \hat{k} \bar{k}^2 + \hat{k} - \bar{k}}{\hat{k} \bar{k}}$ |

| SS "B"   | $\frac{1}{\omega_0^2 \hat{L}(1-\hat{k})}$ | $rac{1}{\hat{L}ar{k}\omega_0^2}$                | $egin{bmatrix} 1 & 0 \ rac{j(\hat{k}-ar{k})}{\hat{L}\hat{k}ar{k}\omega_0} & 1 \end{bmatrix}$                                                     | $rac{\hat{L}Z_l\hat{k}ar{k}\omega_0}{\hat{L}\hat{k}ar{k}\omega+jZ_l(\hat{k}-ar{k})}$                          |

Table 2.3: Parameters for fully compensated A and B circuits at  $\omega = \omega_0$ .

This shows that  $C_{p,s}$  should be in resonance with the uncoupled coil *L* at  $\omega_0$ , and is independent of the coupling factor. This significantly reduces the tuning complexity, effectively turning the resonance tracking and coupling tracking into orthogonal problems.  $C_{p,s}$  can be tuned during manufacturing to where it can be seen to be in resonance with *L* at  $\omega_0$ .  $C_{comp}$  can then be adjusted during use to compensate for the coupling factor. Circuit B does not poses this property, as both  $C_{p,s}$  and  $C_{comp}$  are dependent on *k*.

#### 2.2.2. Frequency Characteristics

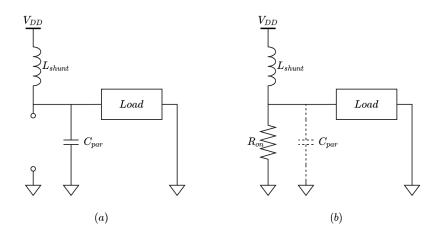

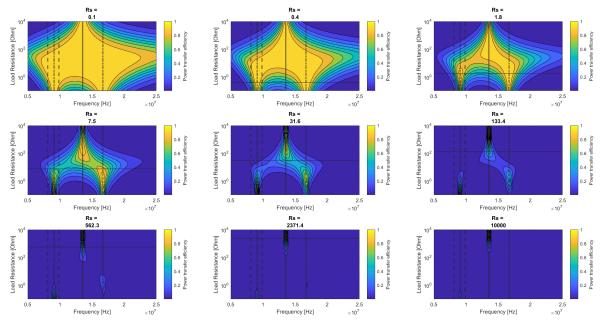

While both circuits are designed with a specific operating frequency  $w_0$  in mind, it is not the case that the total power transfer or transfer efficiency are always optimal at this frequency. In [55], it is observed that as the coupling between the coils increases, there comes a point at which the power delivered to the load drops sharply. This effect is explained by Coupled Mode Theory [55] [56]. The WPT system essentially operates as two coupled resonators. As the coupling between two systems with the same resonant frequency  $f_0$  increases, the resonant frequency of the combined system starts to deviate from  $f_0$ . Usually the resonance splits into two, with one resonant mode below  $f_0$  and one above. This is known as frequency splitting. When the coupling is increased past a threshold value  $k_{split}$ , the power transferred to the load at  $f_0$  drops significantly. In this case it might be beneficially to move the operating point to one of the split frequencies.

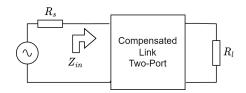

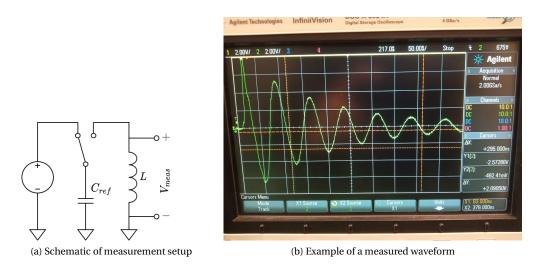

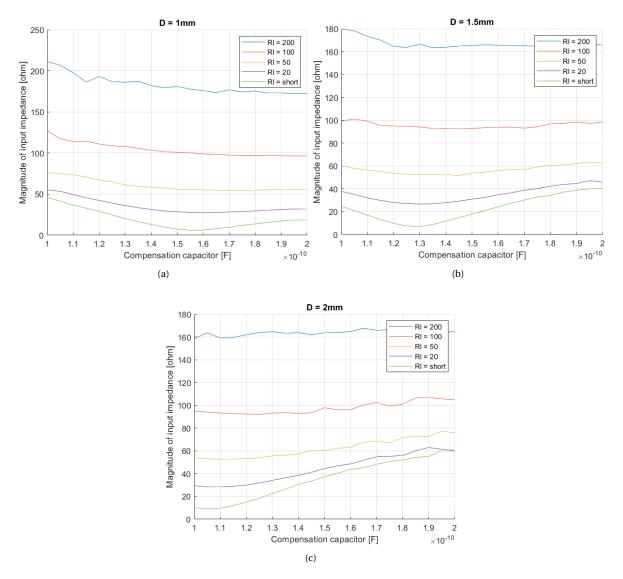

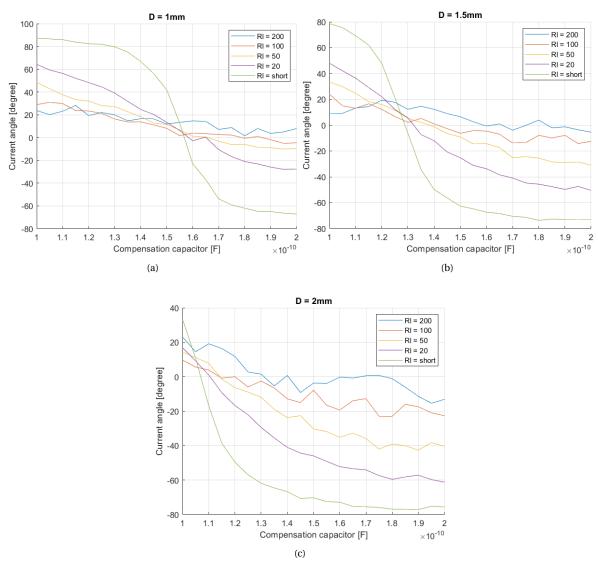

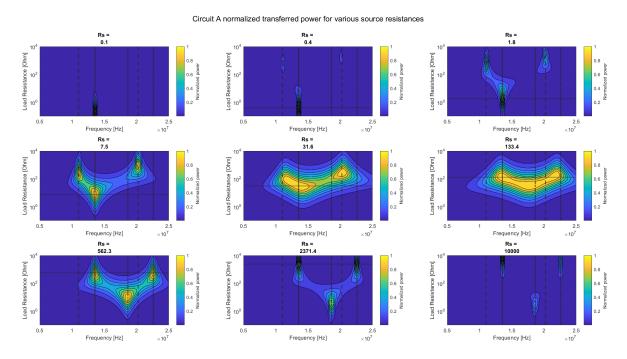

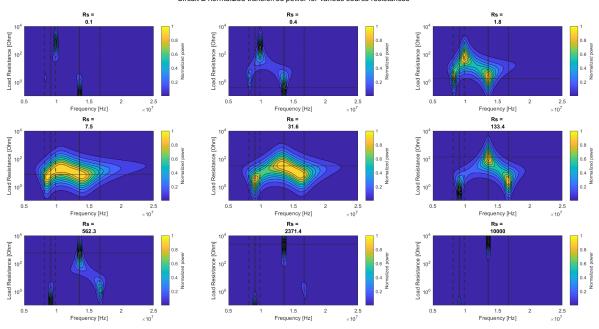

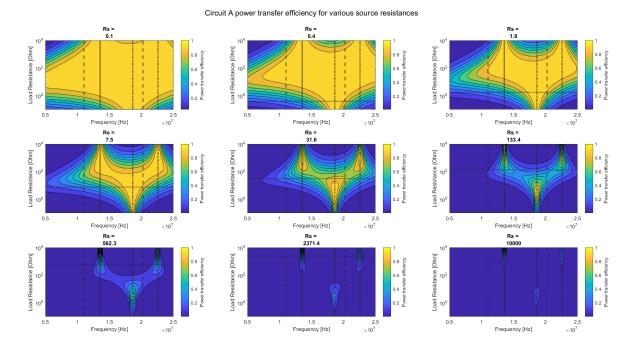

In order to investigate how this theory applies to the proposed circuits, a numerical matlab simulation has been performed to determine the total power received and the efficiency at which this transfer occurred for various frequencies and load resistances. The setup of the simulation was as follows (see also 2.7): a signal is provided by an ideal voltage source, followed by a linear source resistance  $R_s$ . This signal is fed to the input of a perfectly compensated link, modeled using the transmission matrix given in 2.3. Attached to the output of this link is a fixed load resistor  $R_l$ . In this setup, the current flowing through the voltage source  $I_s = \frac{V_s}{R_s + Z_{in}}$ , where  $Z_{in}$  is the input impedance of the link. Since the model of the link does not contain any resistive components, the power delivered to the load can be calculated as follows:

$$P_{load} = |I_s|^2 Re(Z_{in}) \tag{2.19}$$

The power lost in the source is given by  $P_{load} = |I_s|^2 R_s$ . The efficiency is defined as the delivered power divided by the total power, which simplifies to:

$$\eta = \frac{Re(Z_{in})}{R_s + Re(Z_{in})} \tag{2.20}$$

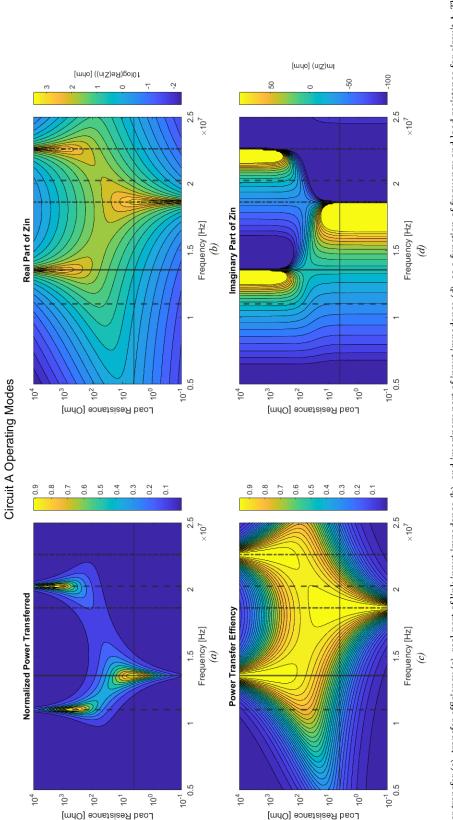

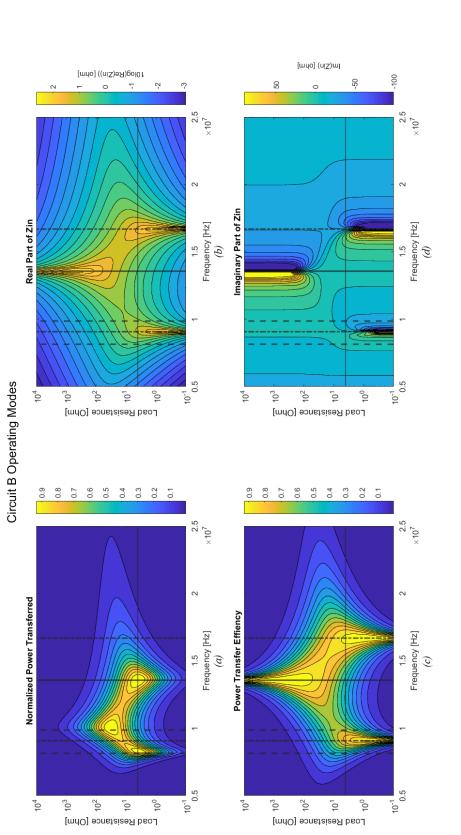

The simulation has been performed for both A and B circuit topologies, using  $R_s = 4\Omega$ , k = 0.8, L = 550 nH,

and  $\omega_0 = 2\pi \cdot 13.56 MHz$ . The resulting power transfer and transfer efficiency, as well as the real and imaginary parts of the input impedance are shown in figure 2.8 and 2.9. It is important to note that in this simulation and in the rest of this section it is assumed that the link is perfectly compensated, so  $\bar{k} = \hat{k}$ .

Figure 2.7: Circuit used for transfer efficiency simulations.

As can be seen from figures 2.8 and 2.9, the frequency at which optimal performance is achieved is not the same for all values of  $R_l$ . It shows a similar behaviour as what would be expected from frequency splitting, but it occurs with varying  $Z_l$ , instead of varying k. This can be explained as follows. From [56] we learn that optimal performance is achieved whenever the system is in resonance. The presence of the resistive element  $R_l$  will dampen any resonance that take place. However, the amount of dampening depends not only on the value of  $R_l$ , but also on the type of resonance that is taking place. In electronics, there are two archetypal resonant circuits; a series resonance and a parallel resonance. In a series resonant circuit, an increase in  $R_l$  will result in more dampening, while the opposite is true in a parallel resonant circuit. The circuits being analyzed here cannot be determined to be either fully series or fully parallel resonant. Instead, there are different resonant modes present, some of which are "series" dampened, and some are "parallel" dampened. What is seen in figures 2.8 and 2.9 is that for low  $Z_l$  the series resonant modes are dominating, while for higher  $Z_l$  the parallel modes are dominant. This also suggests that frequency splitting will always occur, regardless of coupling factor, but that it might not be apparent unless the system is operated at impractically large or small loads. The two circuits show opposing behaviours: circuit A will split sooner when using a large ohmic load, while circuit B splits sooner when loaded with a small load.

A lot of research has been published about finding the frequencies at which the power transfer is optimal once the resonance has split [57] [58] [59] [60]. These rely on finding peaks using the derivative of the load power:

$$\frac{\partial P_{load}}{\partial \omega} = 0 \tag{2.21}$$

However, this technique requires solving very complex higher order polynomials. Instead, candidate frequencies at which optimum performance could occur can be found by looking at the possible resonant modes of the circuit. In order to find all resonant modes one should consider the input impedance  $Z_{in}$  of the link for the two extremes;  $Z_l = 0$  and  $Z_l = \infty$ . These are shown in 2.22 and 2.23 for circuit A, and 2.24 and 2.25 for circuit B.

$$Z_{in A}(\omega)|_{Z_{l}=0} = j \frac{\hat{L}\omega_{0}^{2}}{\omega} (\hat{k}^{2} - 1) \frac{\omega_{0}^{2} - \omega^{2}}{\hat{k}(\omega^{2}(\hat{k} - 1) + \omega_{0}^{2})}$$

(2.22)

$$Z_{in A}(\omega)|_{Z_{l}=\infty} = j \frac{\hat{L}\omega_{0}^{2}}{\omega}(\hat{k}+1) \frac{\omega^{4}(\hat{k}-1) + \omega^{2}\omega_{0}^{2}(2-\hat{k}) + \omega_{0}^{4}(\hat{k}^{2}-1)}{\hat{k}(\omega_{0}^{2}-\omega^{2})(\hat{k}\omega^{2}+\hat{k}\omega_{0}^{2}-\omega^{2}+\omega_{0}^{2})}$$

(2.23)

$$Z_{in B}(\omega)|_{Z_{l}=0} = j \frac{\hat{L}\omega_{0}^{2}}{\omega} (\hat{k}-1) \frac{\hat{k}(\omega_{0}^{2}-\omega^{2})(\hat{k}\omega^{2}+\hat{k}\omega_{0}^{2}+\omega^{2}-\omega_{0}^{2})}{\omega^{4}(\hat{k}^{2}-1)+\omega^{2}\omega_{0}^{2}(2-\hat{k})+\omega_{0}^{4}(\hat{k}-1)}$$

(2.24)

$$Z_{in B}(\omega)|_{Z_{l}=\infty} = j \frac{\hat{L}\omega_{0}^{2}}{\omega} \frac{\hat{k}(\omega_{0}^{2}(\hat{k}-1)+\omega^{2})}{\omega_{0}^{2}-\omega^{2}}$$

(2.25)

Firstly, it should be noted that all of these equations are fully complex, meaning that according to 2.19 and 2.20 the power and efficiency at these limits is zero. This is in line with the expectations, as it is not possible to deliver any power to a short or an open.

By analyzing at what frequencies the equations have poles and zeros, it is possible to determine the resonant frequencies of the circuits. These are given in 2.4 and 2.5 for circuits A and B respectively. The zero and pole frequencies are also indicated in 2.8 and 2.9 using dashed and dash-dot lines. The operating frequency  $f_0$  is indicated using a solid line, as it is a pole and a zero in both circuits.

|                | zeros                                                                               | poles                                                               |

|----------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| $Z_l = 0$      | $f = f_0$                                                                           | $f = f_0 \sqrt{\frac{1}{1 - \hat{k}}}$                              |

| $Z_l = \infty$ | $f = f_0 \sqrt{\frac{2 - \hat{k} \pm \hat{k} \sqrt{5 - 4\hat{k}}}{2\hat{k}^2 - 2}}$ | $f = f_0 \lor f = f_0 \sqrt{\frac{1 - \hat{k}^2}{(1 - \hat{k})^2}}$ |

Table 2.4: Poles and zeros in the input impedance for circuit A

It is clear from the graphs that the points of highest efficiency occur when there is a pole in  $Z_{in}$ , while highest power transfer occur at zero frequencies. This cannot be seen as a general rule. In appendix A the same power transfer and transfer efficiency plots have been generated over a wider range of source resistances.

|                | zeros                                                               | poles                                                                               |

|----------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| $Z_l = 0$      | $f = f_0 \lor f = f_0 \sqrt{\frac{1 - \hat{k}^2}{(1 + \hat{k})^2}}$ | $f = f_0 \sqrt{\frac{\hat{k} - 2 \pm \hat{k} \sqrt{5 - 4\hat{k}}}{2\hat{k}^2 - 2}}$ |

| $Z_l = \infty$ | $f = f_0 \sqrt{1 - \hat{k}}$                                        | $f = f_0$                                                                           |

Table 2.5: Poles and zeros in the input impedance for circuit B

Here it can be seen that as the source resistance increases, the points of optimal power transfer migrate from the pole to the zero locations. It does appear that the points of optimal efficiency remain at the pole frequencies.

The behaviour of both circuits at  $f_0$  is quite easily understood. Regardless of any frequency splitting that might occur, the property where at  $f_0 Z_{in} = Z_l$  still holds for any  $\hat{k}$ . In this case, it is a simple case of impedance matching between  $Z_l$  and  $R_s$ . It follows from circuit theory that optimal power transfer occurs whenever the load and source impedances are complex conjugates. Since it is assumed that the source impedance is fully real, it can be reasoned that optimal power transfer will occur when  $Im(Z_l) = 0$  and  $Re(Z_l) = R_s$ . At this point exactly half of the total available voltage will appear across  $Z_l$ , indicating an efficiency of 50%. Increasing the real part of  $Z_l$  will cause a drop in power delivered to the load, but an increase in efficiency. Reducing the real part of  $Z_l$  will result in less power being delivered and a lower efficiency, as more power will be lost in the source resistance.

The behaviour at frequencies outside  $f_0$  is more complicated. It is clear from the numeric simulations that points of optimal performance likely only occur at poles or zeros in  $Z_{in}$ . However, why a resonant frequency under certain conditions acts as a point of optimal transfer, while under different conditions it acts as a point of optimal efficiency is not clear at this point. It is also difficult to predict what performance can be expected at a resonant frequency given a load and source impedance. Further research into this will be required. It can also be noted from appendix A that when the optimal performance transitions from one resonant frequency to another, the frequency in between the peaks might offer higher performance than can be found on either resonant frequency. However, the performance at the resonant frequencies will likely not be significantly worse than the maximum.

In this application the system will perform at  $f_0$ . There are several reasons for this. The first is that this is the only resonant peak that does not depend on  $\hat{k}$ . As it cannot be assumed that  $\hat{k}$  remains constant during use, operating at any frequency other than  $f_0$  would require the system to actively track the resonant frequency. This would significantly increase complexity and might even pose problems with spectrum regulations. In addition to this, the impedance mirroring property that exist at  $f_0$  makes load modulation very predictable. This is crucial when it comes to the transmission of data from the slave to the master.

#### 2.2.3. Analyzing the Quality Factor

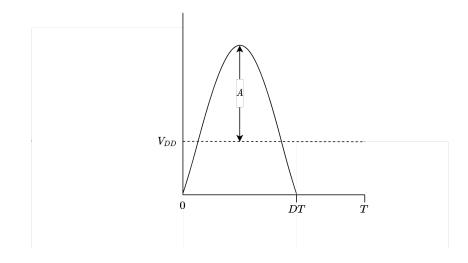

Only one of the proposed circuits can be implemented in the final prototype, and the analysis up to now does not indicate that one circuit will perform better than the other. However, up to this point only steady state analysis is performed. To make a decision between the circuits it is important to also analyze their dynamic properties. When data is transmitted from either the master or the slave, the state of the system changes. Since the systems contains many reactive components, it takes some time before the system settles into its new state. The shorter the time needed for the system to settle, the faster the data can be transmitted. The speed at which a system settles is determined by its quality factor *Q*. The quality factor is defined as the ratio between the energy stored in a system and the energy dissipated per oscillation cycle [61]. In practice, this can be expressed using equation 2.26.

$$Q = \frac{\omega E_s}{P_{dis}} \tag{2.26}$$

Here  $E_s$  is the average energy stored in the system, and  $P_{dis}$  is the average power dissipated.

In order to calculate the quality factor of both circuits, first the total energy stored  $E_s$  needs to be determined. This is simply the sum of all the energy stored in the capacitors and the inductors.

$$E_s = \sum E_C + \sum E_L \tag{2.27}$$

To simplify the analysis, it is assumed that the system is perfectly matched (so  $\bar{k} = \hat{k}$ ). In this configuration, the input impedance of the systems are equal to the load impedances. It is also assumed that the load is the

only resistive element in the circuit, meaning that it is responsible for all the dissipation in the circuit. Finally, it is assumed that the load impedance is fully real. Due to the impedance mirroring property of the link this also implies that the link input impedance will be fully real. This indicates that all the reactive elements in the circuit are in resonance. When a circuit is in resonance, all energy stored in the capacitors will be exactly delivered to the inductances in each cycle, so:

$$\sum E_C = \sum E_L \tag{2.28}$$

This simplifies equation 2.27 to:

$$E_s = 2\sum E_C \tag{2.29}$$

The mean stored energy per capacitor can be calculated using 2.30.

$$E_{c,i} = C(\frac{V}{\sqrt{2}})^2 = \frac{1}{2}CV^2$$

(2.30)

Here *C* is the capacitor value, and *V* is the magnitude of the AC voltage present over the capacitor. Using conventional circuit analysis, the magnitude of the voltage across each of the capacitors in both circuits during normal operation can be determined. The capacitor voltages found are shown in table 2.6. This analysis was greatly simplified by the fact that the only resistive element in the circuit is the load impedance. Also, since the circuit is assumed to be perfectly matched, the impedance seen at the input is the same as the load impedance. From this we can deduce that  $V_{in} = V_{out}$  and  $I_{in} = I_{out}$ .

Combining equation 2.30 and 2.29 with the equation in table 2.6 gives the following expressions for the energy stored in circuits A and B respectively:

$$E_{s,A} = \frac{1}{2} V_{in}^2 [(C_{p,A} + \frac{C_{p,A}}{\omega^2 C_{comp,A}^2 Z_L^2}) + C_{s,A} + \frac{1}{\omega^2 C_{comp,A} Z_l^2}]$$

(2.31)

$$E_{s,B} = \frac{1}{2} V_{in}^2 \left[ \left( \frac{1}{\omega^2 C_{p,B} Z_l^2} + \frac{C_{comp,B}^2}{C_{p,B}} \right) + \frac{1}{\omega^2 C_{s,B} Z_l^2} + C_{comp,B} \right]$$

(2.32)

Plugging in the values for  $C_p$ ,  $C_s$  and  $C_{comp}$  from table 2.3 gives:

$$E_{s,A} = \frac{1}{2} V_{in}^2 \left(\frac{1}{\omega^2 \hat{L}(\hat{k}+1)} + \frac{\hat{L}(1-\hat{k}^2)^2}{\hat{k}^2(\hat{k}+1)Z_l^2} + \frac{1}{\omega^2 \hat{L}(\hat{k}+1)} + \frac{\hat{L}(1-\hat{k}^2)}{Z_l^2 \hat{k}}\right)$$

(2.33)

and

$$E_{s,B} = \frac{1}{2} V_{in}^2 \left( \frac{\hat{L}(1-\hat{k})}{Z_l^2} + \frac{1-\hat{k}}{\hat{L}\hat{k}^2\omega^2} + \frac{\hat{L}(1-\hat{k})}{Z_l^2} + \frac{1}{\hat{L}\hat{k}\omega^2} \right)$$

(2.34)

These equations can be simplified algebraically to read:

$$E_{s,A} = \frac{1}{2} V_{in}^2 \left( \frac{\hat{L}(1 - \hat{k}^2)}{Z_l^2 \hat{k}^2} + \frac{2}{\hat{L}\omega^2 (\hat{k} + 1)} \right)$$

(2.35)

$$E_{s,B} = \frac{1}{2} V_{in}^2 \left( \frac{\hat{L}(2-2\hat{k})}{Z_l^2} + \frac{1}{\omega^2 \hat{L} \hat{k}^2} \right)$$

(2.36)

|       | topology A                                             | topology B                                                                         |

|-------|--------------------------------------------------------|------------------------------------------------------------------------------------|

| Cp    | $V_{in}\sqrt{1+\frac{1}{\omega^2 C_{comp,A}^2 Z_l^2}}$ | $V_{in}\sqrt{\frac{1}{\omega^2 C_{p,B}^2 Z_l^2} + \frac{C_{comp,B}^2}{C_{p,B}^2}}$ |

| $C_s$ | Vin                                                    | $V_{in} \frac{1}{Z_l \omega C_s, B}$                                               |

| Ccomp | $V_{in} \frac{1}{\omega C_{comp,A} Z_l}$               | Vin                                                                                |

Table 2.6: Magnitude of the voltages across the various capacitors in both A and B circuit topologies.

As explained earlier, the input voltage is the same as the output voltage and all power in the system is delivered to the load. It can thus be stated that:

$$P_{dis} = \frac{V_{in}^2}{2Z_l} \tag{2.37}$$

Combining equations 2.35, 2.36 and 2.37 with the definition of the quality factor given by 2.26 results in equations for the quality factors of both circuits:

$$Q_A = \frac{\omega \hat{L}}{Z_l} \frac{1 - \hat{k}^2}{\hat{k}} + \frac{Z_l}{\omega \hat{L}} \frac{2}{\hat{k}(\hat{k}+1)}$$

(2.38)

$$Q_B = \frac{\omega \hat{L}}{Z_l} (2 - 2\hat{k}) + \frac{Z_l}{\omega \hat{L}} \frac{1}{\hat{k}}$$

(2.39)

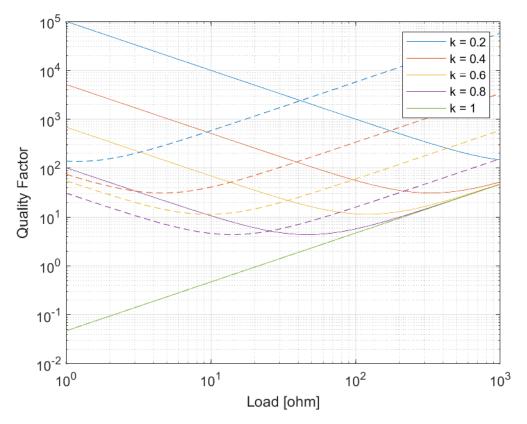

In order to give a more intuitive understanding of what these equations imply, the values for Q over various loads and coupling factors in a typical system have been plotted in figure 2.10. In this simulation  $\omega = 2\pi \cdot 13.56MHz$ , and L = 500nH, which are considered typical values for such a system.

Figure 2.10: Quality factor vs load resistance for various coupling factors for circuit A (solid line) and circuit B (dashed line).

The first conclusion that can be drawn from 2.10 is that both circuits behave the same for k = 1. In this case the quality factor will always increase with an increase in the load resistance, in which case the lowest possible load will result in the best performance. Secondly, it can be noted that for any given coupling factor, one topology does not inherently perform better than the other. The only difference is the load impedance at which optimum performance is achieved, with circuit A being better suited to high impedances, while circuit B performs better with lower impedances.

#### 2.2.4. Choosing a Topology

Only one topology can be implemented in the final prototype. While the steady state properties of both circuits are very similar, figure 2.10 shows that circuit A should have better dynamic properties for loads larger

than  $30\Omega$ . The system is expected to mostly be operating at these larger loads. Combining this with the manufacturing advantage circuit A has over circuit B, as discussed at the end of section 2.2.1, circuit A has been chosen to be implemented for further testing and verification.

#### 2.3. Coil Design

The physical design of the coils can have a large impact on the performance of the system. Since the coils have to be mounted inside a piece of clothing, they have to be very low profile. For this reason only planar coils where considered for the design. In addition to being planar, it should also be considered that in future developments the coils might be mounted on a flexible substrate, or even sown directly into the fabric. This means that the shape of the coil might distort during use, which could impact performance. The coils designed in this section are only for the proof of concept however. For practical purposes and to limit the scope of the project the coils are made using rigid materials. Actually implementing flexible coils would likely require further analysis.

To reiterate, in section 2.1 it was assumed that the design of the slave and master coils where the same, and had a self inductance of *L*. The coils in between where also identical to each other, and had a self inductance of  $L_2$ . In order to simplify the manufacturing and to maintain the link with the theoretical analysis all four coils are of the same design.

#### 2.3.1. Coil Parameters

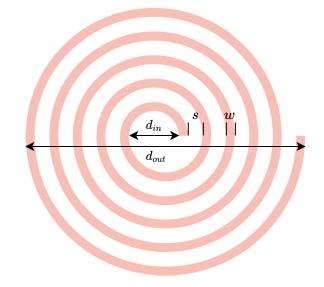

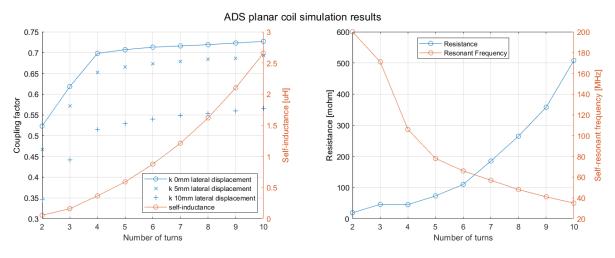

When designing a planar coil there are several parameters that should be considered. Firstly there is the number of turns N. This is the dominant factor when determining the self-inductance of the coil. Ideally, the self inductance is proportional to  $N^2$ . There is also the track width w and the track spacing s. The track width relates to the quality factor of the coil; as the width increases the resistance of the coil will decrease. The track spacing determines coils capacitance, this sets the self-resonance frequency of the coil. The self resonance effectively acts as an upper bound to the operating frequency. Decreasing the track width decreases the resonant frequency. Finally there are the inner and outer diameters of the coil,  $d_{in}$  and  $d_{out}$ . These do not directly contribute to the self-inductance of the coil. However, it can be assumed that a larger coil will result in better coupling. The definitions for these parameters are shown in figure 2.11. It should be noted that these are only broad indications of how the parameters affect the characteristics of the coil. In reality the way these parameters interact is quite complex, as will be discussed further in this section.

Figure 2.11: Example of a planar coil with the parameter definitions.

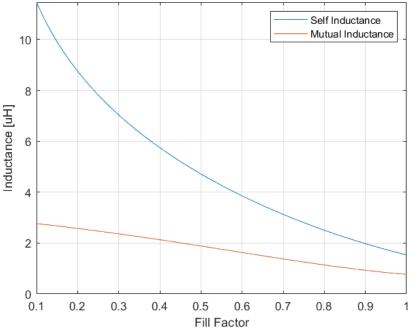

According to the link model introduced in the previous chapter, the self-inductance of the coils should not affect the performance of the system. However, this is only true if, among other things, the link is perfectly compensated (meaning that  $\bar{k} = \hat{k}$ ). This can not always be guaranteed. From the equations given in table 2.3 it can be seen that the error caused by mismatched coupling is proportional to  $\hat{L}$ .  $\hat{L}$  is directly correlated to the self inductance of the master and slave coils *L*. This suggests that coils with a small self inductance are

preferred over those with a large self inductance.

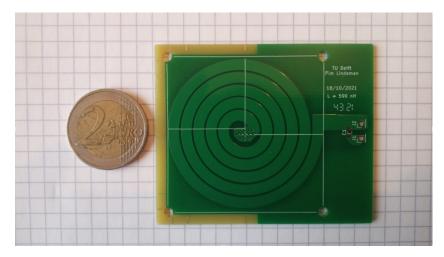

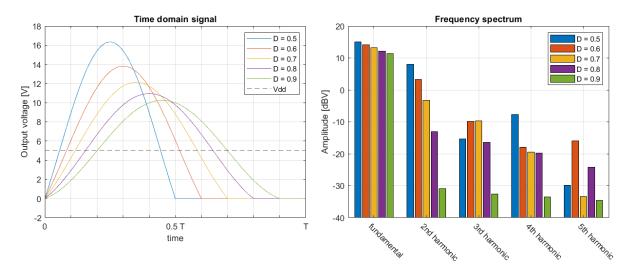

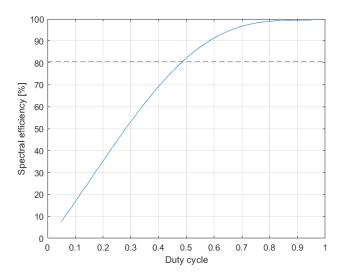

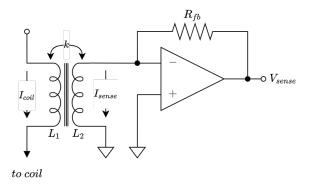

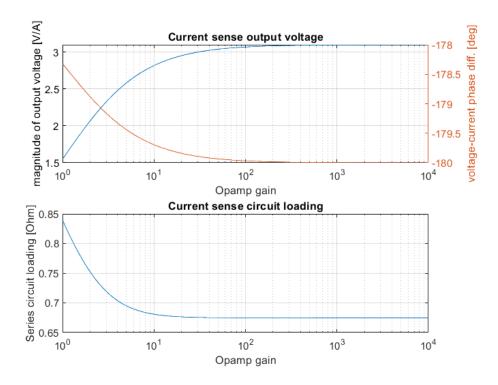

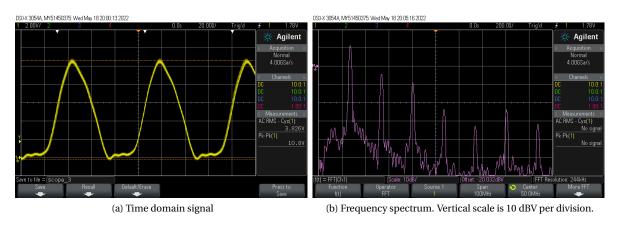

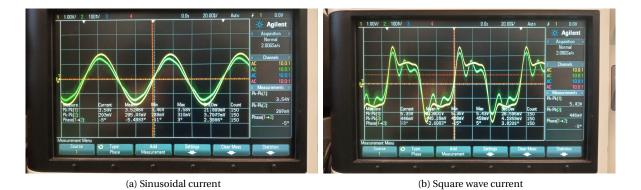

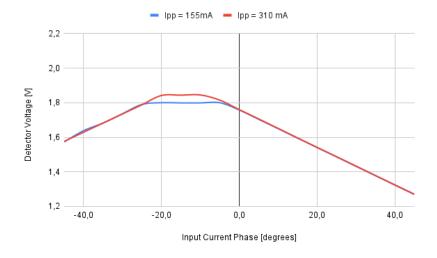

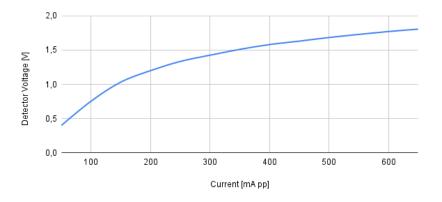

Similarly, according to the same table the actual value of the coupling factor  $\hat{k}$  should, under ideal circumstance, not affect the transmission matrix of the link. However, according to figure 2.10, a lower coupling factor will result in a higher quality factor. This will have a detrimental effect on the data transfer speed that can be achieved. It is therefor preferred to have coil pairs that maximize the coupling factor.