## CMOS magnetic field sensor using a pick-up loop

for measuring electric currents

J. Boele

## **CMOS** magnetic field sensor using a pick-up loop

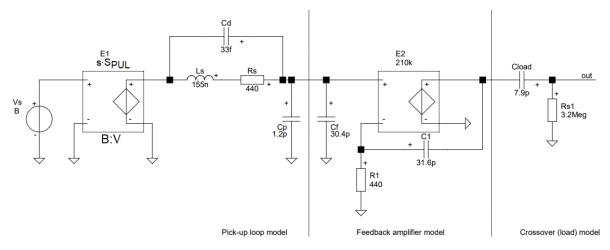

## for measuring electric currents

by

J. Boele

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Junuary 31, 2022 at 10:30 AM.

Student number: Project duration:

4749936 April 12, 2021 - December 24 2021 Thesis committee: Prof. dr. ir. C.J.M. Verhoeven, TU Delft, supervisor TU Delft Ir. A.J.M. Montagne, TU Delft Dr. J. Dong, Ir. C. van den Bos, SystematIC design B.V.

This thesis is confidential and cannot be made public until January, 2023.

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## Preface

"Make all aproximations you can, as soon as you can, justified or not. Leave behind you a wake of assumptions and approximations. All you've to do is go back and check them later. You can't lose by trying."

[R. Middlebrook, Methods of design-oriented analysis: Low Entrophy Expressions, 1992]

J. Boele Dordrecht, January 29, 2022

## Contents

| 1 | ,                                                                                                                                                                                                                                                            | tive                                                         | ••••      |               |                                       |                                       |                 | 2                          |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------|---------------|---------------------------------------|---------------------------------------|-----------------|----------------------------|

| 2 | <ul> <li>2.2 Hall effect sensors</li> <li>2.2.1 Sensor princip</li> <li>2.2.2 Fundamental</li> <li>2.2.3 Integrated Hal</li> <li>2.2.4 Materials</li> <li>2.3 Alternative sensor Princip</li> <li>2.3.1 Pick-up loop .</li> <li>2.3.2 Vacuum magn</li> </ul> | le                                                           | S         | · · · · · · · | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · |                 |                            |

| 3 | 2.4 Conclusion<br>System concept design                                                                                                                                                                                                                      |                                                              | •••       |               |                                       |                                       |                 | 12<br>13                   |

| J | <ul> <li>3.1 Introduction</li> <li>3.2 System requirements</li> <li>3.2.1 Functional special structure</li> <li>3.2.2 Signal process</li> <li>3.2.3 Environmental</li> </ul>                                                                                 | cification:                                                  | · · · · · | · · · · · ·   | · · · · · · ·                         | · · · · · · · ·                       | · · · · · · ·   | 13<br>13<br>13<br>14<br>15 |

|   | <ul><li>3.3 Sensor models</li><li>3.3.1 Pick-up loop .</li></ul>                                                                                                                                                                                             | · · · · · · · · · · · · · · · · · · ·                        | ••••      | ••••          |                                       | <br>                                  |                 | 16<br>16                   |

|   | 3.4 Hybrid current senso<br>3.4.1 Concept 1: pic                                                                                                                                                                                                             |                                                              | out       | ••••          |                                       |                                       | · · · · · ·     | 21<br>22                   |

|   | <ul><li>3.5 Transfer errors</li><li>3.5.1 Corner frequent</li><li>3.5.2 Additional point</li></ul>                                                                                                                                                           | ncy mismatch related g<br>e in Hall path                     | ain erro  | <br>Dr        | · · · · · ·                           | <br>                                  | · · · · · · ·   | 26<br>26<br>27             |

|   | <ul> <li>3.6 Pick-up loop path rec</li> <li>3.6.1 Functional req</li> <li>3.6.2 Signal process</li> <li>3.6.3 Environmenta</li> <li>3.6.4 Cost factors .</li> </ul>                                                                                          | uirements                                                    |           | · · · · · ·   | · · · · · · ·                         | · · · · · · · ·                       | · · · · · · · · |                            |

| 4 |                                                                                                                                                                                                                                                              | · · · · · · · · · · · · · · · · · · ·                        | •••       | • • • •       |                                       |                                       |                 |                            |

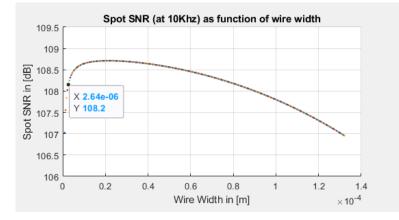

| 4 | <ul><li>4.2 Pick-up loop design.</li><li>4.2.1 Signal-to-noise</li></ul>                                                                                                                                                                                     | <pre>ick-up loop Path e ratio optimization of the loop</pre> | ••••      | ••••          |                                       |                                       | · · · · · ·     | 32<br>32                   |

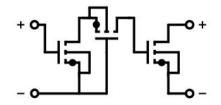

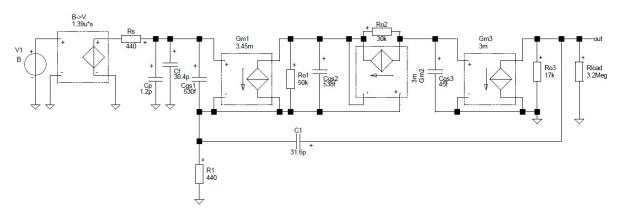

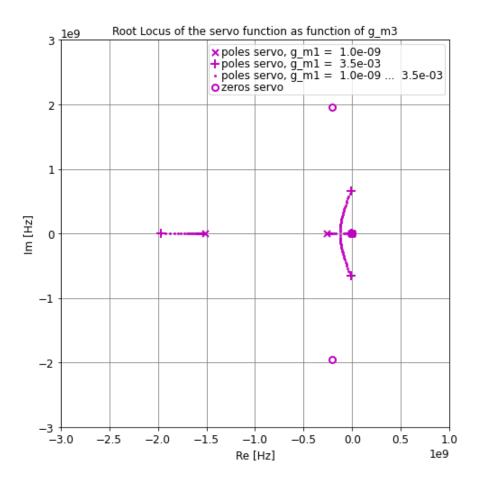

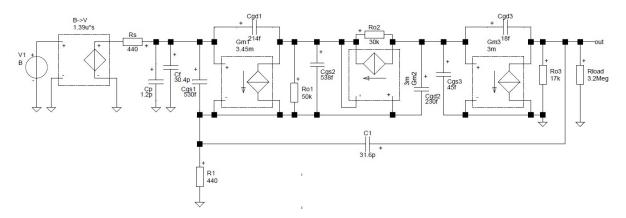

| <ul> <li>4.3 Pick-up loop amplifier topology design</li></ul>                                          |                                                      |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| <ul> <li>5 Pick-up loop amplifier design</li> <li>5.1 Introduction</li></ul>                           | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| <ul> <li>6 Conclusion</li> <li>A Apendix A: Magnetic field sensors</li> <li>A.1 introduction</li></ul> |                                                      |

# 1

### Introduction

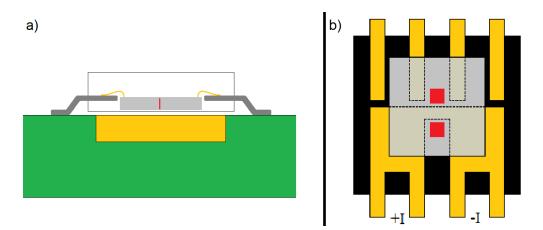

As a result of our urgent desire to electrify (personal) transportation, there is a large demand for compact, low cost current sensors. These sensors have numerous applications in transportation but also in power conversion and industry. They can be used for example to monitor the charge and discharge currents of large battery packs, or to accurately measure current flow in an electric drivetrain. Recent trends show completely integrated current sensing systems, where both sensor and readout electronics are made on a single die. The magnetic field as a result of the current, flowing through an external bus-bar, is measured using a magnetic field sensor. Typically a Hall element [1–6] is used as sensor, but some exotic variants exist using magnetore-sistive (MR) elements [7, 8] or a fluxgate [9]. The bus bar can be a trace on a printed circuit board (PCB) or part of the leadframe used for packaging the chip. These two examples are shown in 1.1. A less preferred option is the use of bond wires as bus-bar [10].

Figure 1.1: a): Cross section of current sensor IC measuring the magnetic field as a result of current flowing through a PCB trace. Red indicates the Sensor location. b). Top view of the layout of a current sensor IC measuring the magnetic field as a result of current flowing through a section of leadframe. Red indicates the Sensor locations considering differential readout. For single ended readout, one of the sensors can be omitted. (Drawings based on [1, 5])

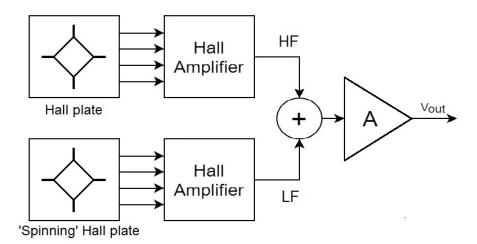

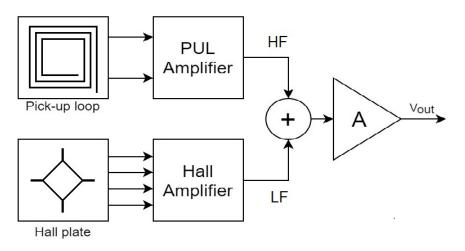

Hall elements are preferred, as they can be made using conventional CMOS technology. This greatly facilitates the integration of the whole system on a single substrate, as this technology is commonly used for manufacturing the readout circuits. In figure 1.2 the block diagram of a typical wideband magnetic field sensor using Hall plates is shown. It consists of two paths one for high frequency (HF) signals and one for low frequency (LF) signals. An output amplifier is used to provide sufficient load drive capabilities. The low frequency path makes use of current spinning in combination with orthogonal connected plates [11] to reduce the large offset component in the Hall plate output voltage. In the high frequency path, the offset is eliminated by use of AC coupling. Such a system is severely limited in bandwidth, as the noise power of a Hall plate increases with bandwidth. The noise resulting from a Hall plate is inversely proportional to the bias current. Therefore, a wideband low noise sensor system using this topology has high power consumption.

Figure 1.2: Hall Block schematic of a wide band magnetic field sensor using a spinning Hall plate for DC and LF and non spinning Hall plate for HF.

#### 1.1. Motivation and objective

An alternative sensor type is needed to improve the performance of the sensor system, without a large increase in cost. The use of alternative materials for making a Hall element would result in additional (post-) processing steps, increasing the cost. Ferromagnetic sensor materials limit the functionality of the system, as their properties are altered by strong external (common mode) fields. Therefore the use of these materials is to be avoided.

This thesis describes the design of a wideband magnetic field sensors system for electric current sensing in standard CMOS technology. The report describes two phases; a research and a design phase. The research part focuses on exploring different sensor types for improving the bandwidth and power consumption of CMOS magnetic sensing system based on conventional Hall sensors. In the design part, a system using these different sensor is designed and verified on performance.

#### **1.2. Scope**

For this thesis, the scope is limited to sensor types that can be made using standard CMOS technology. The intended market for this sensor system is automotive and industry, therefore the system must be capable of operating under harsh conditions (vibrations, large temperature variations). Also the sensor must be capable of enduring magnetic fields much larger than the intended input range. When this strong field is applied, the sensor should remain operational, without any changes to its sensitivity. The design of the bus-bar will not be part of this thesis. However, the effect of fast and large voltage spikes on the bus-bar will be taken into account during the design.

#### 1.3. Organization

The second chapter of this thesis describes the research of Hall plates and alternative magnetic field sensors. Their operation principle and performance is introduced in these sections. The most promising alternative is chosen and motivated. The third chapter describes the design of a system concept using the alternative sensor. Two concepts are presented in this chapter, considering voltage or current as information carrying quantity, but no decision is made yet. This is described in the fourth chapter, where a pick-up loop is designed and a topology for the amplifier was chosen. In the fifth chapter, the amplifier topology is further worked out and verified using simulations. In the sixth chapter a conclusion is presented.

## 2

### Magnetic field sensors

#### 2.1. Introduction

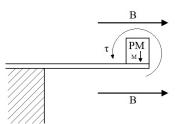

A magnetic field sensor is a transducer that converts a magnetic field quantity into a different physical quantity. From a practical point of view, the output quantity should be electric, thus rendering the solution presented in figure 2.1 useless.

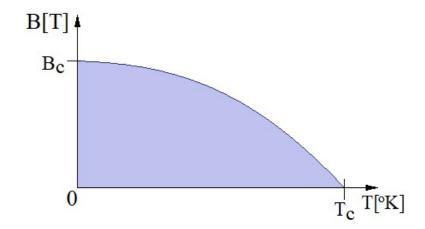

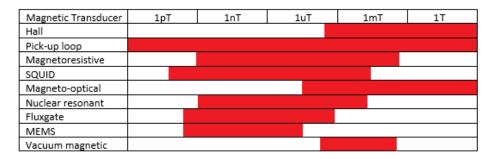

The goal of this chapter is to find alternative sensor types for the commonly used Hall plate. This alternative sensor should be capable of resolving fields up to 10 mT accurately. It must provide a large bandwidth (>1 MHz), large SNR (>40 dB) and have low power consumption (<50 mW). The sensor must remain operational if a strong external field of 1 T is present. Therefore sensors using ferromagnetic materials or MEMS technology are no valid candidates. A sensor using ferromagnetic material becomes magnetized after experiencing a strong field. A MEMS sensor has a high susceptibility of sticking to the substrate (van der Waals-bond) for large deflections caused by strong fields [12]. The application field for the sensor will be automotive and/or industrial, therefore the sensor must be able to work properly in the presence of vibrations, over a wide temperature range and be capable of sustaining large transient voltage steps (i.e. large dV/dt) on the bus-bar.

Figure 2.1: A primitive magnetic field 'sensor'.

During the research phase of this project, eight alternative sensor types were considered. In the end only two sensor types, the pick-up loop and the vacuum magnetic sensors were compatible with conventional CMOS technology. These two sensor types are discussed in this chapter. The remaining six sensor types are described in appendix A. For each of these alternatives, the physical working principle, the fundamental performance properties and some state of the art examples will be described. If there is a strong indication that a solution is not feasible for an integrated-on-chip sensor system the research ends.

The focus in this chapter lies on identifying the parameters: noise, bandwidth and maximum signal level. These three parameters were considered as they constitute to the channel capacity (Shannon). For each sensor type, multiple publications of state-of-the-art designs will be discussed. As introduced in the previous chapter, the investigation of sensor principles will be limited to concepts that can be integrated-on-chip using conventional CMOS technology.

In the second section the Hall plate is investigated. In the third section, two alternatives for Hall plates are considered. The fourth part will consist of a conclusion where the most promising sensor(s) are indicated.

#### **2.2. Hall effect sensors**

The most commonly used magnetic field sensor is the Hall plate [11, 13]. It is named after E. Hall who first discovered the effect in 1879 using gold leaf clamped on a glass surface [14].

#### 2.2.1. Sensor principle

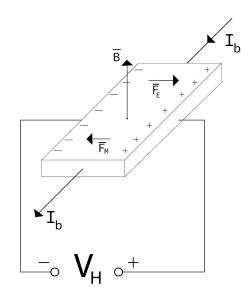

The operation of a Hall plate sensor relies on a externally supplied constant current flow [11]. This constant bias current  $I_b$  is flowing through a flat plate of conductive material. A magnetic field is oriented perpendicular to the plate. Due to this field, charge carriers experience the Lorentz force  $F_L$  and are redistributed in the conductor. This results in an electric field gradient perpendicular to the current and magnetic field. A voltage  $V_H$  can be measured across the width of the Hall plate due to the redistribution of charge carriers. The voltage is proportional to the magnetic field and to the current flowing through the plate. Figure 2.2 shows the Hall plate with the physical quantities indicated. The figure assumes a bias current, but a bias voltage can also be used [15]. A charge carrier *e*, moving with velocity *v*, in magnetic field *B* and electric field *E* experiences Lorentz force found as [11]:

Figure 2.2: The Hall effect demonstrated in a planar conductor.

$$\boldsymbol{F} = \boldsymbol{e} \cdot \boldsymbol{E} + \boldsymbol{e}(\boldsymbol{\nu} \times \boldsymbol{B}) \tag{2.1}$$

where *e* is the charge of the particle, *E* the electric field, *v* the velocity of the particle and *B* the magnetic field. The bold faced symbols represent vectors. The Hall voltage as a result of the redistribution of charge carriers under influence of electric field  $E_H$ , is found by integrating the electric field along the width *w* [11]:

$$V_H = E_H w \tag{2.2}$$

where  $E_H$  is the electric field resulting from the redistribution of charge carriers and w is the width of the Hall plate. The width is assumed much larger than the thickness of the Hall plate for this expression to be valid. A practical relation of the Hall voltage and magnetic field is found as [11]:

$$V_H = G \frac{R_H}{t} I_b B \tag{2.3}$$

where *G* is a geometrical correction factor (for symmetric hall plates it is  $\approx$  1),  $R_H$  is the Hall scattering coefficient, *B* the magnetic field perpendicular to the Hall plate surface, *t* the thickness of the Hall plate and  $I_b$  the bias current, assuming a current biased Hall plate. The voltage sensitivity  $S_{H\nu}$  of a heavily doped semiconductor Hall plate using voltage bias is found to be [16]:

$$S_{H\nu} = GR_H \frac{w}{l} \mu_n \tag{2.4}$$

where *w* the width of the Hall plate, *l* the length of the Hall plate,  $\mu_n$  the electron mobility and  $R_H$  the Hall scattering coefficient. The model indicates a relation between mobility and sensitivity: high mobility yields high sensitivity. Using the model for a current biased Hall plate, the mobility drops out of the sensitivity equation [11]:

$$S_H = G \frac{R_H}{t} \tag{2.5}$$

Considering this sensitivity expression, typical Hall based sensor systems use current bias. This eliminates the effect of temperature variations on the sensitivity.

#### 2.2.2. Fundamental performance properties

A Hall plate has non-zero resistance therefore it adds thermal noise to the signal. The bandwidth of a Hall plate is large: it is only limited by the parasitic capacitance. Typically the switching frequency used for offset cancellation or the electronics for readout impose an upper limit to the bandwidth at a lower frequency as the cut-off frequency of the Hall plate. The upper limit to the bias voltage or current is set by the material and construction method. Typical sensitivity of a silicon Hall plate is 50 mV/VT [17, 18].

#### 2.2.3. Integrated Hall plate

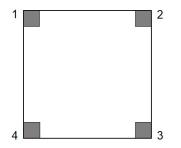

Hall plates can be made on a silicon substrate [19, 20] using conventional CMOS techniques. Typically it is laid out as a square plate to mitigate offsets related to material anisotropy. The Hall plate is made in a N-well with with four contact pads located at the corners as demonstrated in figure 2.3. One diagonally opposing pair of contacts (for example 1 and 3) is used to apply the Hall bias current  $I_b$ . The remaining pair of contacts (2 and 4) is used to measure the Hall voltage. As this Hall plate construction is diagonally symmetric, the contacts used for biasing and sensing can be interchanged. This allows for mitigation of offset, by periodically switching the pairs of contacts between forcing and sensing (i.e. spinning or rotating). Summing the Hall voltage from these two phases cancels the offsets, resulting in a more accurate magnetic field measurement. In this example the Hall plate is operated in two phases of equal duration, but methods using more phases (and contacts) can be used to mitigate the offset [21].

Figure 2.3: Top view of a symmetrical Hall plate layout. The gray squares resemble contact pads.

#### 2.2.4. Materials

A major drawback of a silicon (Si) Hall plate is its low sensitivity. Using high mobility materials for fabricating Hall plates overcomes this problem [22]. Indium-antimony (InSb) is a commonly adopted substrate material having a larger charge carrier mobility as silicon, thus yielding larger sensitivity. The mayor drawback of InSb is the temperature dependency. Other commonly used materials are indium-arsenic (InAs), gallium-nitrate (GaN) Aluminum-gallium-nitrate (AlGaN) and gallium-arsenic (GaAs), all being group III-V elements [23]. These elements have high electron mobility, thus allowing high sensitivity, and can be vacuum deposited using thin film technologies. A second drawback of a Si Hall plate is the high sensitivity for mechanical stress [24, 25]. This makes an accurate measurement difficult, as its sensitivity for stress is similar to the sensitivity for magnetic fields. Finally over a long period of time, the sensitivity of a Hall plate decreases. According to [11], the sensitivity of a current biased Hall plate is decreasing by a rate of:

$$\frac{\Delta S_I}{S_I} = \frac{10^{-4}}{year} \tag{2.6}$$

where  $S_I$  is the sensitivity and  $\Delta S_I$  the difference in sensitivity of a current biased hall plate.

sensor

#### 2.3. Alternative sensor Principles

This section introduces a number of sensor principles, each having their own subsection. The sensor subsections are limited to describing the sensor and do not consider a complete sensor system.

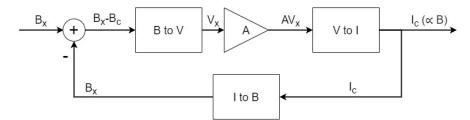

All sensors listed can be used in a feedback configuration (or closed loop) for improved linearity of the transfer [11, 26, 27]. This is done by locally compensating the external field, with another field of opposite sign. This keeps the sensor most of the time in zero-field operating region, thus minimizing the effects of saturation at large signal excursions (i.e. for strong fields)[43]. When the external field changes, the local compensating field no longer is an exact sign-reversed copy of the external field. During this small period of time the feedback loop evaluates the new value of the compensating field, until the difference after summation is zero. The strength of the external magnetic field can be found by measuring the current required for generating the compensating field (assuming a coil as compensating field source)[26]. This feedback method is commonly referred to as a null-detector. The concept is illustrated in figure 2.4.

Figure 2.4: A closed loop magnetic field sensing circuit. Block 1 resembles the magnetic field sensor. Block 2 is the controller and amplifies the error signal  $V_x$  with a factor A. Block 3 translates this voltage into a current and block 4 uses this current  $I_c$  to generate the compensating field  $B_c$ . The information about the field strength is embedded in the drive current  $I_c$ , as  $I_c \propto B_x$  when the loop has settled.

The input signal is magnetic field  $B_x$ . The signal is summed with a compensating field  $-B_c$ , yielding the signal  $B_x - B_c$ , which should be regulated to zero by the loop. A method for generating the compensating field is forcing current to a coil. The magnetic field generated by a long coil is related to the drive current and is found as:

$$B = \mu_0 \frac{n}{l} I \tag{2.7}$$

where  $\mu_0$  is the vacuum permeability, *n* the turn count, *l* the length and *I* the current through the solenoid. Considering fields of 1 T (the upper limit of the input range), a large number of turns per length or (and) a high current is required to generate the desired field. The first option is limited by the large inductance resulting from a high turn count, introducing a bandwidth limit. The second option costs power, assuming n = 1, 800 kA·m<sup>-1</sup> is required to generate a field of 1 T. The high current requirement is a serious drawback of a feedback system. Also the current carrying capability of the interconnect wire, and the inter-wire distance should be considered, both will cost chip area. A second disadvantage with this method is that the field produced by the coil will not be a homogeneous magnetic field (assuming a planar coil fabricated using conventional CMOS technology) [27]. This introduces a gain error to the transfer of the overall system. A third disadvantage, of using a compensating magnetic field is that it locally distorts the external magnetic field.

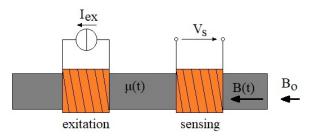

#### 2.3.1. Pick-up loop

A pick-up loop converts a varying magnetic flux into a voltage according to Faraday's law of induction [28]. Usually it is made by using multiple loops of conducting wire are to form a coil. A pick-up loop requires no external power for operation, unlike all other principles investigated.

#### Transducer principle

Operation of the pick-up loop as magnetic field sensor can be explained using Faraday law of induction. The induced voltage as a result of a varying magnetic flux is found as [11]:

$$V_{i} = -n \frac{d\phi(t)}{dt} = -n \frac{d(nA(t)\mu_{0}\mu_{r}(t)H(t))}{dt}$$

(2.8)

where *n* is the turn count, *A* the area of a single loop,  $\mu_0$  and  $\mu_r$  the relative and vacuum permeability, H(t) the magnetic field and  $\phi(t)$  the magnetic flux. The flux must vary in time to obtain a non-zero induced voltage. It is not capable of detecting constant or static (i.e. 'DC') magnetic fields. A time varying flux can be realized by varying the area, the permeability or the external magnetic field. Air coils make use of air as core material, equivalently  $\mu_r = 1$ , therefore the induced voltage is a linear function of frequency and field strength. Assuming a stationary air coil (thus constant area *A*) and a sinusoidal source of magnetic field, the induced output voltage is found as [11, 13]:

$$V_i = -nA\mu_0 \frac{dH(t)}{dt} = -nA\frac{dB(t)}{dt}$$

(2.9)

A pick-up loop is direction dependent; if the plane of the loops is oriented perpendicular to the magnetic field the induced voltage is maximal and for parallel orientation it is zero (assuming a stationary source of sinusoidal field). The sensitivity of a pick-up loop can be increased using a ferromagnetic core at the cost of introducing non-linearity to the transfer due to hysteresis (especially for large fields). A ferromagnetic core increases the sensitivity by a factor  $\mu_r$ . For small fields, the induced voltage of a pick-up loop with a ferromagnetic core is found as [11]:

$$V_i = -nA\mu_r \frac{dB(t)}{dt}$$

(2.10)

This is a linear transfer function. In large field demagnetization effects can no longer be neglected. The voltage-field relation is found as [11]:

$$V_{i} = -nA \frac{\mu_{r}}{1 + D(\mu_{r} - 1)} \frac{dB(t)}{dt} = -nA\mu_{a} \frac{dB(t)}{dt}$$

(2.11)

where *D* is the demagnetization factor, and  $\mu_a$  the apparent relative permeability. As previously mentioned, a core would introduced a non-linear component to the transfer. This is because of saturation and hysteresis properties of ferromagnetic material. The core permeability changes with time, temperature, DC magnetization and when subjected to mechanical stress. A strong magnetic field causes the core to saturate, resulting in a different in sensor sensitivity. Using a feedback coil wrapped around the same core, saturation can be avoided at the cost of an increased power consumption. Therefore the use a ferromagnetic materials is not preferred and should be avoided.

#### Fundamental performance properties

In the previous section it became clear that the pick-up loop is incapable of detecting static magnetic fields. A hybrid sensor system, as for example seen in a DC current probe [29], obtains large bandwidth including DC. This system type uses a different type of sensor for the DC and low-frequency part of the bandwidth, and a pick-up loop for the high frequency part of the bandwidth. A pick up loop requires no power for operation, therefore a reduction in power consumption can be obtained compared to a wide band Hall sensor system.

The pick-up loop is fabricated using the aluminum or copper interconnect layer(s). Therefore, it will have non-zero series resistance introducing thermal noise. The thermal noise will determine the minimum frequency where the pick-up loop provides a useful SNR (i.e. SNR»1). The upper limit of the bandwidth results from the parasitic capacitance to substrate combined with the inductance and series resistance of the pickup loop. These three circuit components form a second order low-pass filter. The effect of the substrate capacitance can be eliminated by using the short circuit current as information carrying quantity, thereby increasing the bandwidth of the sensor. The amplitude of the induced voltage (i.e. pick-up loop output signal) is frequency dependent, increasing with a rate of 20 dB per decade. Therefore the spot SNR is frequency dependent, as well as the dynamic range, both increase with frequency. The amplitude can also be manipulated by the turn count and loop area. Considering a pick-up loop with air core, the maximum magnetic field strength will be set by the breakdown voltage of the isolation material in between traces.

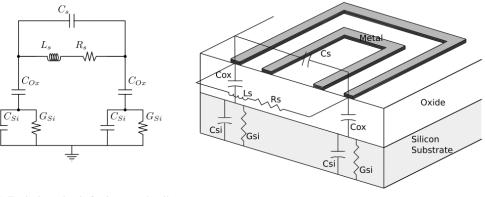

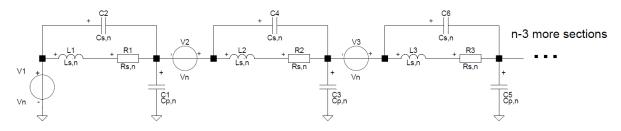

In figure 2.5a model for an integrated coil is presented [30]. Typically planar constructions are opted, figure 2.5b shows an section of a so called pancake-style coil. Figure 2.5a shows a model of an on-chip flat coil. A number of parasitic components are considered. As with any practical implementation of an inductor, the wire has non-zero resistance resulting in series resistance  $R_s$ . The inter-winding or distributed capacitance is modeled in parallel to the inductance  $L_s$  as capacitor  $C_s$ . The model also includes a capacitance to model the coupling between pick-up loop and substrate using capacitor  $C_{ox}$ . The series resistance and oxide capacitance are the most important elements after the inductance. The model forms a 2nd order low-pass

filter. Parasitic capacitance  $C_{ox}$  can be eliminated by using the short-circuit current as information carrying quantity. This increases the effective bandwidth of the pick-up loop.

(a) Equivalent circuit for integrated coil working at RF frequencies

(b) Cross section of integrated coil operating at RF frequency

Figure 2.5: Equivalent Model of an integrated coil (a) and a cross section of the coil on a Si substrate (b). [30]

#### State-of-the-art

In [31] a design for an integrated inductor for magnetic field measurements is shown. The substrate below the coil is removed. The conductivity of the Si substrate causes eddy currents to flow decreasing the sensitivity. The problem is prominent for high frequency fields (>10 MHz), but for lower frequencies the effect can be neglected. For a high pick-up loop sensitivity, a large turn count is needed. A coil having low effective area but high turn count is proposed in [32] by using a flip-chip integration method. A model is presented for the proposed inductor construction. Unfortunately no actual chip-inductors using the proposed method where made and tested.

As mentioned, a pick-up loop is not capable of resolving DC fields. A second sensor of a different type is needed to obtain a large bandwidth including DC, resulting in a hybrid system. In [3, 4] a hybrid magnetic field sensor system utilizing a pick-up loop and a Hall plate is demonstrated. The design measures the magnetic field resulting from a current carrying conductor differentially by using a pair of sensor of each type on each side of the conductor. The coils uses about 1/3th of the total chip area as a result of a single layer planar layout. A pair of Hall plates provides the low frequency transfer and two pick-up loops are used for high frequencies, providing a total system bandwidth of DC up to 3 MHz. The output signals of the two paths are combined using an analog filter. This requires a careful design of the crossover behavior in order to obtain a flat transfer. In both systems, the crossover frequency is set to 2 kHz, close to the point where the SNR of the coil equals the SNR of the Hall plate. The advantages found compared to a single Hall plate is an improved noise performance.

In [7, 8, 33] hybrid current sensors are introduced using the HOKA principle. The designs make use of pick-up loops for high-frequency magnetic field component and are implemented on PCB-scale. They provide extensive insight in the methods used for combining the signal paths. The first paper mentioning the HOKA principle [33] considers a Hall plate for the DC and low frequency magnetic field component. [7, 8] make use of a tunneling-magneto-resistive, respectively giant-magneto-resistive element for resolving DC and low frequency magnetic fields. [34] presents a desing using Hall plates and a Rogowski coil as pick-up loop. The special layout of this pick-up loop allows a system bandwidth up to 75MHz.

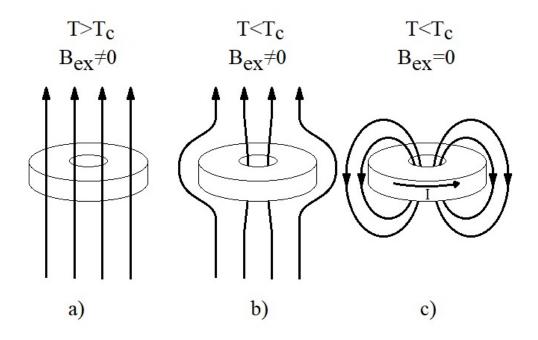

#### 2.3.2. Vacuum magnetic sensor

For well over 150 years, magnetic fields are known to deflect electron beams. In 1880, multiple devices were developed using electron beams deflected by magnets, known as cathode ray tubes. Around the same time A. Schuster, J.J. Thomson and J. Perrin made use of cathode ray tubes to evaluate the mass and charge of an electron [35]. Permanent magnets were used to center the electron beam on an external target. The target is held at a high positive voltage to attract electrons. A similar cathode ray tube was developed by F. Braun around 1897, with the addition of a fluorescent screen inside the tube as commonly seen in more recent cathode ray tubes. The screen emits visible light when bombarded with electrons. In 1899, J. Zenneck in cooperation with F. Braun, improved the cathode ray tube further by the addition of electromagnets for accurately controlling the beam position on the screen. This enabled Zenneck and Braun for the first time in history to visualize an electric signal [35]. The use of electromagnets for deflecting electron beams would become essential in the late 1930s for the development (and at a later point for the miniaturization) of commercial television sets.

#### Transducer principle

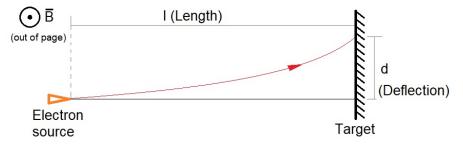

In a cathode ray tube, an electron beam is deflected by a magnetic field perpendicular to the beam (electric fields could also be used to deflect the beam). The deflection can be accurately controlled by feeding current trough coils wrapped around the middle of the cathode ray tube. Similarly, if the external field is unknown, but all other properties of the electron beam and path length are known, the principle could be used to measure a magnetic field. Measuring the deflection as a result of the unknown magnetic field contains information about the field strength. An electron moving in a homogeneous magnetic field experiences a force found as:

$$\boldsymbol{F} = \boldsymbol{e}(\boldsymbol{v} \times \boldsymbol{B}) \tag{2.12}$$

where *e* is the charge of the particle, *v* the velocity and *B* the magnetic field. This expression is derived from expression for the Lorentz force introduced in (2.1), assuming E = 0. The force is perpendicular to the velocity and magnetic field. The particle will move in a circular trajectory if the magnetic field and velocity are perpendicular. The radius of the circular trajectory is:

$$r = \frac{mv}{eB} \tag{2.13}$$

where *m* is the mass of the particle and *r* the radius of the circular path. This relation indicates the radius being inversely proportional to the magnetic field strength.

Figure 2.6: Deflection of an electron beam (red) due to the influence of a magnetic field (pointing out of the page).

In figure 2.6 the deflection of an electron beam as result of a magnetic field is illustrated. The deflection measured on a target plane perpendicular to the zero-field propagation direction is:

$$d = r(1 - \cos(\phi)) \tag{2.14}$$

where *d* is the distance of deflection, *r* the radius and  $\phi$  the angle of rotation. For small deflections the model can be simplified to:

$$d = B \frac{el^2}{2m\nu} \tag{2.15}$$

where *l* is the path length. The electron velocity can be found by manipulating the relation  $\frac{1}{2}mv_e^2 = eV$  into:

$$v_e = \sqrt{\frac{2eV}{m}} \tag{2.16}$$

where  $v_e$  the velocity and V the potential in volts. For an acceleration potential of 100 V, the velocity will be about  $5.9 \cdot 10^6$  m/s or 5900 km/s. The deflection, assuming an electrode distance of  $1\mu$ m is:

$$d = B \frac{el^2}{2m\nu} = 1.49 \cdot 10^{-8} B \tag{2.17}$$

Thus for a channel length of 1  $\mu$ m and a potential of 100 V the resulting deflection is about 15 nm/T. Increasing the electrode distance to 10  $\mu$ m results in 10<sup>2</sup> more deflection, or 1.5  $\mu$ m/T. From these simple calculations it becomes clear that the sensitivity is related to the cathode anode distance, where a larger distance yields a higher sensitivity. The cathode to anode distance can't be made arbitrary large, as the electric field strength decreases with distance (assuming a fixed potential across the anode-cathode spacing). The use of an accelerator electrode can mitigate this problem. Typically a field strength of > 10<sup>7</sup> V/cm is required to obtain 'cold' emission. The shape of the cathode influences the minimum potential required for emission: sharp, conical-shaped structures provide the best results.

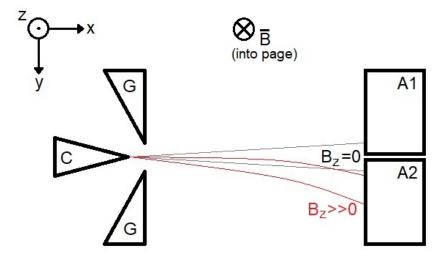

Figure 2.7: Simplified construction of a CMOS vacuum magnetic field sensor. The magnetic field is applied in the -Z direction, pointing into the page.

The deflection is measured using two isolated targets as anode (i.e. split-anode) biased at the same potential [36, 37]. Figure 2.7 shows a simplified vacuum magnetic sensor, consisting of cathode *C* in the form of a tip-shaped field emitter, gate structures *G* and the pair of anodes  $A_1$  and  $A_2$ . The layout and dimensions of the gate and cathode influence the angular divergence of the electron beam. The gate voltage is used to control the beam current. For zero field, the beam is positioned such that half of the beam current impinges on each anode, indicated in figure 2.7 as the black beam. When a perpendicular magnetic field (in the negative Z-direction, pointing into the page) is present the beam current is no longer split equally per anode. The difference in anode current is proportional to the field strength. At some point, after increasing the field strength, the beam only hits one anode, the situation is exaggerated in figure 2.7, indicated by the red beam. Stronger fields cannot be detected using this method, as the difference in the 2 anode currents ca not become larger. An advantage of a two-anode construction is that the beam intensity is eliminated from the transfer: the information is embedded in the relative difference in anode current and not in the absolute anode current, as is the case for a single anode device.

#### Fundamental performance properties

In vacuum magnetic field sensors, vacuum is used as a transport medium. In comparison with semiconductors, the vacuum does not impose a speed limit. Therefore the bandwidth of a vacuum sensor is expected to be large. A second advantage of the vacuum is that the mobility of charge carriers is not depending on temperature. The vacuum is expected to provide lower 1/f-noise, as there are no charge traps, like seen in a semiconductor interface. The maximum field intensity is limited by the device dimensions, a small anode to cathode distance would enable very large fields to be detected, but sacrifices the low end of the input range. The input range is limited to about one decade, but it can be increased with the application of (magnetic) feedback. Drawbacks of vacuum magnetic sensors are the high voltage required for field emission, the relative large device size (> 10*x*10 mm) and the required high vacuum. This vacuum must be better than 0.13 mPa  $(1.3 \cdot 10^{-6} \text{ mBar})$  to obtain a long lifespan of the emitter. It requires a hermetically sealed package for maintaining the vacuum.

#### State-of-the-art

In [37-39] a CMOS planar magnetic field sensoris described utilizing a field array emitter and a two-anode target. The anode to cathode distance is  $10\mu$ m, and the device needs to be in a vacuum lower than 0.13 mPa  $(1.3 \cdot 10^{-6} \text{ mBar})$  in order to avoid damage to the field emitter. The sensitivity of the sensor is defined as a percentage of half the beam current and is found to be 4000%/T, for a field strength range of 0...1 mT. The use of conventional CMOS technology limits the layout of a vacuum magnetic sensor to planar structures, where the electron beam is in plane with the substrate. In [40] a sensor is described using additional manufacturing process to obtain a sensor with an electron beam propagating in the Z-direction. The gate, focus and cathode electrodes where made using conventional CMOS technology, but the anode consists of a separate structure placed 5mm from the cathode. The device uses a two anode detector structure and has an additional focusing electrode to obtain a collimated beam. This was done to obtain a higher sensitivity in the X and Y direction, but reduced sensitivity in the z-direction In [41] another vacuum magnetic field sensor is described using a field emission array with an additional pair of deflection electrodes. These electrodes are biased at +V/2 and -V/2 respectively. They provide a perpendicular electric field to compensate the magnetic deflection, thus increasing the upper limit of field strength to be measured. The device is capable of detecting magnetic fields up to 0.1 T. The device could be used in a null-detector system, using the electric field to compensate the deflection of the magnetic field. The strength of the electric field required to return the beam to zero-field position on the anode would then provide information about the magnetic field strength.

#### 2.4. Conclusion

This chapter starts with the description of Hall plate magnetic field sensors. In this remaining sections of this chapter, two alternative magnetic field sensor principles were described that could replace the commonly used Hall plate. Pick-up loops and vacuum magnetic sensors were considered as they are fully compatible with conventional CMOS technology and require no ferromagnetic materials or MEMS technology. The pick-up loop seems to be the most promising solution. It is a simple to construct sensor type and offers unprecedented dynamic range, but it is not capable of detecting DC fields. This could be solved using a combination of sensors as demonstrated in [4, 7, 8, 29, 33, 34]. Therefore the remaining chapters of this thesis will focus on a hybrid magnetic field sensor system using a pick-up loop for HF signals and Hall plates for LF signals.

## 3

### System concept design

#### 3.1. Introduction

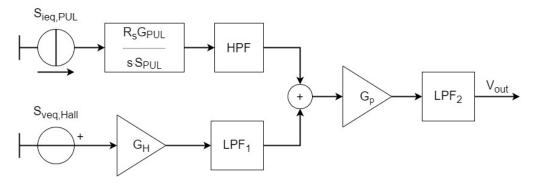

This chapter describes the concept design of a hybrid current sensor. The term hybrid indicates the use of multiple sensors in parallel combined to a single output node. A Hall plate is chosen for resolving the DC and LF signals and a pick-up loop for the HF signals as demonstrated in [4, 7, 8, 29, 33, 34, 42]. This solution provides a lower noise contribution compared to a Hall-based wide band sensor. Special care is needed when designing the crossover behavior between the two transducers. The amplitude, phase and crossover frequencies of the two sensor paths must be exactly equal to obtain a flat magnitude and phase transfer without a transition zone. Figure 3.1 shows a top level block diagram of the hybrid sensor system consisting a pick-up loop and Hall plate path. Each path contains a sensor (or multiple sensors) and a dedicated amplifier. Their output signals are combined into one signal. And finally there is an output amplifier providing the required output drive capabilities.

Figure 3.1: Top level block diagram of a hybrid sensor system consisting of a pick-up loop and a Hall plate path.

#### 3.2. System requirements

This section introduces the system level requirements, as requested by the client (i.e. the company SystematIC design BV). The section is subdivided into four subsections: functional requirements, signal processing requirements, environmental requirements and cost factors.

#### 3.2.1. Functional specification:

Table 3.1: Functional specifications

| functionality | description   | Comments/notes                                                                             |

|---------------|---------------|--------------------------------------------------------------------------------------------|

| 1             | Amplification | Increasing the available power of the signal                                               |

| 2             | Conversion    | Change Magnetic field (or current) signal into a proportional voltage signal at the output |

| 3             | Combination   | Sum two signal paths to one output path                                                    |

#### 3.2.2. Signal processing

Table 3.2: Performance requirements, system level

| Req | description             | value | unit    | verification method                                                                  | Comments/notes                                            |

|-----|-------------------------|-------|---------|--------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 1   | Noise                   | <60   | μT      | Spectrum analyzer                                                                    | RMS integrated noise, source referred                     |

| 2   | Bandwidth (-3dB)        | >5    | MHz     | phase-gain analyzer or oscilloscope, compare                                         | source referred                                           |

|     |                         |       |         | result with mid-band gain                                                            |                                                           |

| 3   | Sensitivity             | 500   | V/T     | Apply known B-field<br>and measure output<br>signal. Compare result<br>with calc.    | max output swing<br>/ max input signal<br>(Req9/Req4)     |

| 4   | Signal (max)            | 8     | mT      | Oscilloscope (with FFT)<br>or spectrum analyzer                                      | System must no clip /<br>saturate at given input<br>level |

| 5   | Offset                  | <10   | μT      | Measure output voltage<br>with zero current (or<br>field)                            | differential                                              |

| 6   | Full scale error        | <1    | %       | Measure maximum<br>output voltage and<br>compare with calcu-<br>lated maximum signal | use sensitivity and max.<br>signal (Req3 + Req4)          |

| 7   | Sensitivity error drift | <1    | %       | Measure maximum<br>output voltage and<br>compare with calcu-<br>lated maximum signal | Over whole Lifetime $T_a = 25^{\circ}C$                   |

| 8   | Chopping spurs          | <1.5  | mV(RMS) | Measured using Spec-<br>trum analyzer at output<br>of system                         | including folded back components                          |

| 9   | Maximum output level    | 4     | V       | voltmeter                                                                            | 0.8VDD(min) used for<br>evaluating sensitivity<br>(Req3)  |

#### 3.2.3. Environmental requirements

Table 3.3: Environmental requirements

| Req | description                         | value | unit  | verification method                      | Comments/notes                     |

|-----|-------------------------------------|-------|-------|------------------------------------------|------------------------------------|

| 1   | Maximum temperature                 | 150   | °C    | Climate chamber tem-<br>perature setting | Better to design for 0 TC          |

| 2   | Minimum temperature                 | -55   | °C    | Climate chamber tem-<br>perature setting | Better to design for 0 TC          |

| 3   | Common mode Tran-<br>sient immunity | >25   | kV/μs | HV probe + oscilloscope                  | Voltage step op bus-bar            |

| 4   | ESD discharge                       | 2000  | V     | ESD-gun, 2 kV on each pad                | IEC 61000-4-2 level 1: 2<br>kV HBM |

| 5   | Isolation Voltage                   | 1000  | V     | Between bus-bar and<br>sensor system     | 1 minute                           |

#### 3.2.4. Cost factors

Table 3.4: Cost factors

| Req | description            | value  | unit            | verification method  | Comments/notes            |

|-----|------------------------|--------|-----------------|----------------------|---------------------------|

| 1   | Minimum supply voltage | 3      | V               | Power supply setting | typical supply is 5V      |

|     |                        |        |                 | during test          |                           |

| 2   | Maximum supply volt-   | 5.5    | V               | Power supply setting | Technology dependent      |

|     | age                    |        |                 | during test          |                           |

| 3   | Maximum current con-   | 10     | mA              | Measure current con- | multiple methods possi-   |

|     | sumption               |        |                 | sumption             | ble                       |

| 4   | Chip Area              | T.B.D. | mm <sup>2</sup> | proved by design     | Layout editor (?? T.B.D.) |

#### 3.3. Sensor models

This section describes models for the pick-up loop and Hall plate magnetic field sensors. At this point, no specifications of the two sensors are known. Therefore this section focuses on the derivation of universal source models for the pick-up loop and Hall plate.

#### 3.3.1. Pick-up loop

A pick-up loop has a linear frequency dependent magnetic field to voltage relation. This is the result of the induced voltage being proportional to the derivative of the magnetic flux. Thus the voltage is increasing in magnitude proportional to the frequency.

According to the Farady's law of induction, the induced voltage as a function of magnetic field b(t) is found as [11, 13]:

$$v_i(t) = -n\frac{d\phi(t)}{dt} = -nA\frac{db(t)}{dt}$$

(3.1)

where  $\phi$  is the magnetic flux, *b* is the magnetic field confined by a single loop with area *A* and *n* is the number of turns. The minus sign in the equation is a result of the induced voltage opposing the magnetic flux. It can be removed from the transfer by interchanging the two terminals of the pick-up loop. Transforming this relation to the frequency domain results in:

$$V_i = -snAB \tag{3.2}$$

where s represents the Laplace operator. Using  $S_H = nA$  as sensitivity of the pick-up loop, this expression reduces to:

$$V_i = -sS_{PUL}B \tag{3.3}$$

#### Inductive circuit model

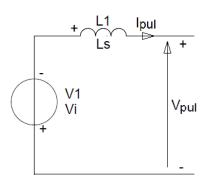

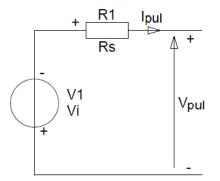

The pick-up loop will have inductance, as it is a coil of highly conductive material (Cu or Al traces on the interconnect layer). Neglecting the wire resistivity for now, a simple circuit model for the pick up loop would be a voltage source with value  $V_i$  and a series inductance with value  $L_s$ . The model is shown in figure 3.2

Figure 3.2: Simple pick-up loop model.

The output quantity can be either voltage or current. The output voltage, or open-circuit voltage is found as:

$$V_{PUL} = -V_i = sS_{PUL}B \tag{3.4}$$

and the short-circuit current:

$$I_{PUL} = -V_i \cdot \frac{1}{sL_s} = \frac{S_{PUL}B}{L_s}$$

(3.5)

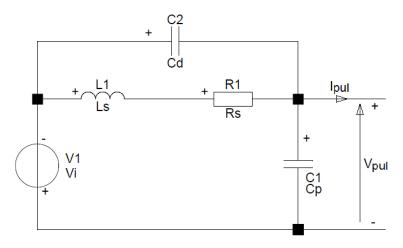

#### Pick-up loop circuit model with parasitic elements

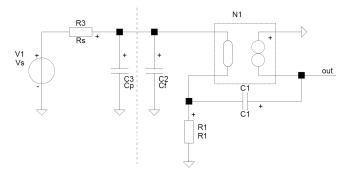

In reality, the traces of the pick-up loop will have non-zero resistivity, introducing series resistance to the model. Next to the series resistance, the pick-up loop also has parasitic capacitance to substrate ( $C_p$ ) and distributed capacitance ( $C_d$ ) between consecutive turns. Expanding the model to include these parasitic components results in the lumped circuit shown in figure 3.3:

Figure 3.3: Pick-up loop model including parasitic elements.

The output quantity can be either voltage or current. The output voltage, or open-circuit voltage is found as:

$$V_{PUL} = -V_i \cdot \frac{s^2 L_s C_d + s R_s C_d + 1}{s^2 L_s (C_p + C_d) + s R_s (C_p + C_d) + 1} = \frac{s S_{PUL} B(s^2 L_s C_d + s R_s C_d + 1)}{s^2 L_s (C_p + C_d) + s R_s (C_p + C_d) + 1}$$

(3.6)

and the short-circuit current:

$$I_{PUL} = -V_i \cdot \frac{R_s + sL_s}{s^2 L_s C_d + sC_d R_s + 1} = \frac{sS_{PUL}B(sL_s + R_s)}{s^2 L_s C_d + sC_d R_s + 1}$$

(3.7)

#### Simplified pick-up loop circuit model

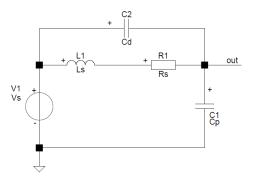

Figure 3.4 shows the simplified circuit for modeling the mid-band transfer of the pick-up loop. This model is used for designing the in-band transfer of the amplifier. For the design of the high frequency roll-of of this amplifier the complete model including parasitic components is used. The simplified circuit does include the series resistance. Inductance  $L_s$ , substrate capacitance  $C_p$  and distributed capacitance  $C_d$  are expected to only influence the transfer at high (out-of-band) signals. At a later point in the design of the pick-up loop it became clear that the impedance presented by its inductance is much smaller compared to the series resistance considering the bandwidth requirement. Therefore the pick-up loop can be modeled as a magnetic-field sensitive resistance when considering in-band signals.

Figure 3.4: Pick-up loop model including parasitic elements.

The output quantity can be either voltage or current. The output voltage, or open-circuit voltage is found as:

$$V_{PUL} = -V_i = sS_{PUL}B \tag{3.8}$$

and the short-circuit current:

$$I_{PUL} = -V_i \cdot \frac{1}{R_s} = \frac{sS_{PUL}B}{R_s}$$

(3.9)

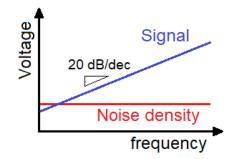

#### Pick-up loop noise model

The series resistance of the pick-up loop introduces thermal noise. Assuming the simplified sensor model the spectral density of this noise source in  $V^2/Hz$  is:

$$S_{\nu,n_{PUL}} = 4kTR_s \tag{3.10}$$

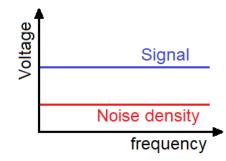

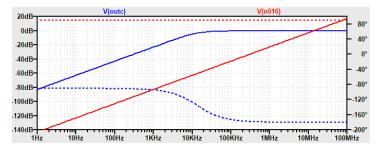

In figure 3.5 the signal magnitude and noise are plotted as a function of frequency. This figure clearly shows a increasing signal to noise ratio as a function of frequency. This can be used to lower the total integrated source referred noise of a wideband magnetic field sensor system.

Figure 3.5: Noise and signal voltage as a function of frequency resulting from the Pick-up loop.

#### 3.3.2. Hall plate

In section 2.2.1 the Hall plate was introduced as magnetic field sensor. Equations relating the magnetic field to the hall voltage  $V_H$  were described. For a current biased Hall plate the Hall voltage as a result of the magnetic field is:

$$V_H = S_H B \tag{3.11}$$

where  $S_H$  is the magnetic field sensitivity of a current biased Hall plate, introduced in 2.2.1 as:

$$S_H = G \frac{R_H}{t} \tag{3.12}$$

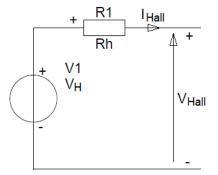

#### Resistive Hall plate circuit model

The Hall plate is made in a silicon substrate having non-zero resistivity. A circuit model of the Hall plate is shown in 3.6, were the non-zero resistivity is modeled as a series resistor with value  $R_h$  (note:  $R_H$  and  $R_h$  are not the same!).

Figure 3.6: Hall plate circuit model with series resistance.

The output voltage, or open-circuit voltage is found as:

$$V_{Hall} = V_H = S_H B \tag{3.13}$$

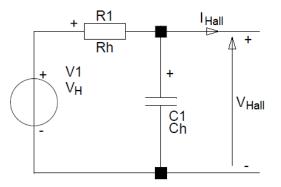

#### Hall plate circuit model with parasitic components

The Hall plate model introduced in 3.3.2 model has infinite bandwidth. In reality, the bandwidth of a Hall plate is finite as a result of parasitic capacitance. This can be modeled using a capacitor  $C_h$ , demonstrated in figure 3.7.

Figure 3.7: Hall plate circuit model with series resistance and parasitic capacitance.

The output voltage, or open-circuit voltage is found as:

$$V_{Hall} = V_H \cdot \frac{1}{1 + sC_h R_h} = \frac{S_H B}{1 + sC_h R_h}$$

(3.14)

The low-pass corner frequency  $f_H$  of the circuit is  $1/(2\pi\tau_H)$  were time constant  $\tau_H = R_h C_h$ . The model has a bandwidth from DC to  $f_H$ . The magnetic field sensor system will use a Hall plate for the low frequency magnetic field information. The bandwidth of the Hall plate path will be limited to the crossover frequency. This frequency will be much lower than the low-pass hall corner frequency  $f_H$ , equivalently  $f_H >> f_{cross}$ . Therefore, the design of the system will consider the resistive circuit model.

#### Hall plate noise model

The series resistance of the Hall plate introduces thermal noise. Assuming the simplified sensor model the spectral density of this noise source in  $V^2/Hz$  is:

$$S_{\nu,n_H} = 4kTR_h \tag{3.15}$$

In figure 3.8 the signal magnitude and noise are plotted as a function of frequency. This figure clearly shows a constant signal to noise ratio as a function of frequency.

Figure 3.8: Noise and signal voltage as a function of frequency resulting from the Hall plate model.

#### Hall plate offset

The Hall voltage  $V_H$  contains a component proportional to the magnetic field and an offset component. The offset component is of larger magnitude as the signal. Using the current spinning technique [11, 17], these offsets can be mitigated. This method 'rotates' the sense and force terminals of the hall plate over 4 phases. The resulting Hall voltage readings are averaged, thereby reducing the (orientation dependent) offsets. The switching takes place at a frequency higher than the Hall-path bandwidth. As a result of the switching, a residual offset component is up-modulated and appears as noise in the pick-up loop path bandwidth. The design of the Hall-path will not be part of this thesis, as there is already a design available within the company. This design Hall-path design is part of a hybrid Hall plate magnetic field sensor, consisting of a low and high frequency Hall path.

The pick-up loop does not produce offset. The signal processing electronics will however contribute some offset to the signal. By using AC-coupling at the output of the pick-up loop path, the offset is eliminated. This can be implemented in the high-pass filter at the end of the pick-up loop path.

#### 3.4. Hybrid current sensor concepts

A pick-up loop does not provide DC-transfer. Therefore a two channel hybrid sensor topology is chosen, using a Hall plate for the DC transfer, as demonstrated in [4, 7, 8, 29, 33, 34, 42]. The Signal to noise ratio of a pick-up loop is increasing with frequency. A Hall plate has a constant signal to noise ratio versus frequency.

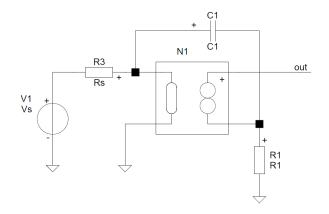

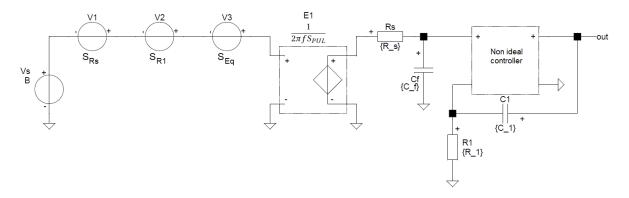

#### 3.4.1. Concept 1: pick-up loop voltage readout

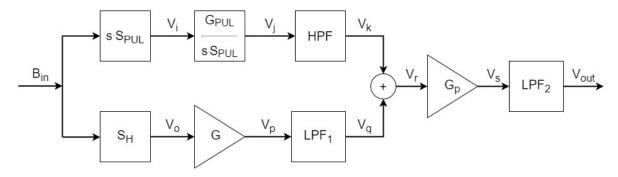

The first system concept is shown in figure 3.9, using simple source models introduced in the previous sections. In the first concept assumed the corner frequency of the Hall plate as crossover point. Considering the relative high frequency of this pole, it will probably not yield best signal to noise ratio for the complete system and difficulties with matching the pole locations will be unavoidable. A second concept is therefore derived, where the crossover frequency can be arbitrarily set using one filter section.

Figure 3.9: Concept 1: A hybrid Hall+pick-up loop sensor system.

On the left side magnetic field  $B_{in}$  is applied to the system. The signal is converted in to voltage by the two sensors. The sensor sensitivities are represented by  $S_{PUL}$  and  $S_H$  for the pick-up loop and Hall plate respectively. Considering the pick-up loop path, the voltage at this point is:

$$V_i = s \cdot S_{PUL} B_{in} \tag{3.16}$$

This signal is proportional to frequency. A flat transfer is obtained in the following block that consists of an integrator operation and a gain factor  $G_{PUL}$ . After this block the signal is:

$$V_i = G_{PUL} B_{in} \tag{3.17}$$

Now the signal must be filtered to introduce the crossover corner frequency (i.e. high pass corner) with time constant  $\tau_{cross}$  using the HPF block. The HPF block has transfer:

$$H_{HPF} = \frac{s\tau_{cross}}{s\tau_{cross} + 1} \tag{3.18}$$

The output signal after passing through the filter is:

$$V_k = G_{PUL} B_{in} \frac{s\tau_{cross}}{s\tau_{cross} + 1}$$

(3.19)

This signal is fed into a summing block where it is added to the Hall path signal  $V_q$ . Considering the Hall path, after the sensor has converted the magnetic field to a voltage, the signal is:

$$V_o = S_H B_{in} \tag{3.20}$$

The signal is expected to be very small as typical Si-Hall elements have a sensitivity of 50 mV/V/T [17]. An amplifier with gain  $G = G_{PUL}/S_H$  is used to increase the signal amplitude to the same level as the signal resulting from the pick-up loop path  $V_k$ . After this amplifier the signal is:

$$V_p = G_{PUL} B_{in} \tag{3.21}$$

This signal is filtered using a low-pass filter to introduce the desired crossover corner frequency using block  $LPF_1$  with transfer function:

$$H_{LPF_1} = \frac{1}{s\tau_{cross} + 1} \tag{3.22}$$

The output signal after passing through the filter is:

$$V_q = G_{PUL} B_{in} \frac{1}{s\tau_{cross} + 1}$$

(3.23)

Both input signals of the summing block are now described. The resulting signal after summing is:

$$V_r = V_k + V_q = B_{in}G_{PUL} \tag{3.24}$$

This signal is increased by the output amplifier with a gain of  $G_p$ . Finally, the system bandwidth is limited using a second low-pass filter  $LPF_2$  with transfer function:

$$H_{LPF_2} = \frac{1}{s\tau_h + 1}$$

(3.25)

where  $\tau_h$  represents the time constant of the filter. The filter  $LPF_2$  and output amplifier can be combined to one circuit block. Similarly, the summing block,  $LPF_1$  and  $HPF_1$  can be merged into one circuit block. The source to load transfer  $H_{C1}$  of the system is:

$$H_{C1} = \frac{V_{out}}{B_{in}} = \frac{G_p G_{PUL}}{s\tau_h + 1}$$

(3.26)

The system sensitivity is  $S_s = G_p G_{PUL}$ .

#### Noise

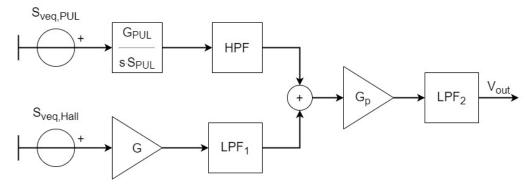

This paragraph presents the noise model of concept 1. In figure 3.10, the model is shown including equivalent noise sources for the two sensors. Thermal noise resulting from non-zero series resistances of the transducers are considered in the noise model. The remaining signal processing blocks are considered noiseless in this stage of the design. The resulting expressions therefore represent the best noise result obtainable, and can only be approximated in a real implementation.

Figure 3.10: Noise Model of concept 1

The noise power spectral density in V<sup>2</sup>/Hz resulting from the pick-up loop is:

$$S_{vea,PUL} = 4kTR_s \tag{3.27}$$

The noise power spectral density (voltage) in  $V^2/Hz$  resulting from the Hall plate is:

$$S_{veq,Hall} = 4kTR_h \tag{3.28}$$

The noise power spectral density in  $V^2/Hz$  at the output of the system is:

$$S_{n,out} = \left[S_{veq,PUL} \left(\frac{2\pi f \tau_{cross}}{2\pi f \tau_{cross} + 1} \frac{1}{S_{PUL}}\right)^2 + S_{veq,Hall} \left(\frac{1}{S_H} \frac{1}{2\pi f \tau_{cross} + 1}\right)^2\right] \frac{G_{PUL}^2 G_p^2}{1 + 4\pi^2 f^2 \tau_h^2}$$

(3.29)

Referred back to the input of the system, using system sensitivity  $S_s$ , the noise power spectral density in T<sup>2</sup>/Hz:

$$S_{n,out} = \left[S_{veq,PUL} \left(\frac{2\pi f \tau_{cross}}{2\pi f \tau_{cross} + 1} \frac{1}{S_{PUL}}\right)^2 + S_{veq,Hall} \left(\frac{1}{S_H} \frac{1}{2\pi f \tau_{cross} + 1}\right)^2\right] \frac{1}{1 + 4\pi^2 f^2 \tau_h^2}$$

(3.30)

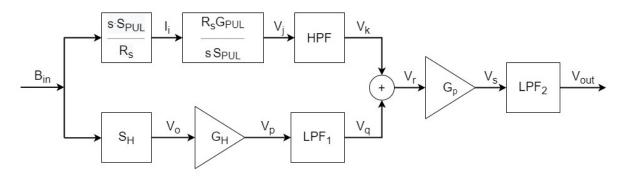

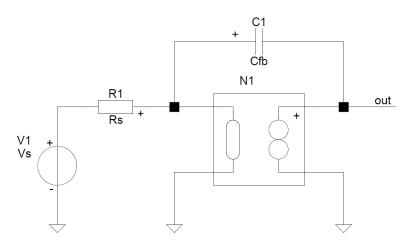

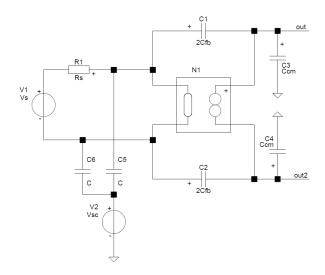

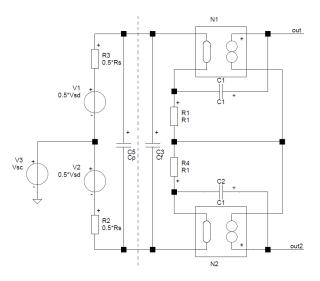

#### 3.4.2. Concept 2: pick-up loop current readout

The second concept uses the short circuit current of the coil as information carrying quantity. For simplicity, it was assumed that the output of the pick-up loop amplifier uses voltage as information carrying quantity. If a current output amplifier type is preferred at a later point in the design, this may be changed. A current to voltage converter block is in this case needed before summation with the Hall path.

Figure 3.11: Concept 2: A hybrid Hall+pick-up loop sensor system.

On the left side magnetic field  $B_i n$  is applied to the system. The signal is converted in to voltage by the two sensors. The sensor sensitivities are represented by  $S_{PUL}$  and  $S_H$  for the pick-up loop and Hall plate respectively. Considering the pick-up loop path, the voltage after conversion is (assuming the simple pick-up loop circuit model):

$$I_i = s \cdot \frac{S_{PUL}B}{R_s} \tag{3.31}$$

This signal is proportional to frequency. A flat transfer is obtained in the following block that consists of an integrator operation and a gain factor  $G_{PUL}$ . After this block the signal is:

$$V_j = G_{PUL} B_{in} \tag{3.32}$$

Now the signal must be filtered to introduce the crossover corner frequency (i.e. high pass corner) with time constant  $\tau_{cross}$  using the HPF block. The HPF block has transfer:

$$H_{HPF} = \frac{s\tau_{cross}}{s\tau_{cross} + 1} \tag{3.33}$$

The output signal after passing through this filter is:

$$V_k = G_{PUL} B_{in} \frac{s\tau_{cross}}{s\tau_{cross} + 1}$$

(3.34)

This signal is fed into a summing block where it is added to the Hall path signal  $V_q$ . The Hall path is the same as was described in concept 1. The signal after summing is:

$$V_r = V_k + V_q = B_{in}G_{PUL} \tag{3.35}$$

This signal amplitude is enlarged by the output amplifier with a gain of  $G_p$ . Finally, the system bandwidth is limited using a second low-pass filter  $LPF_2$  with transfer function:

$$H_{LPF_2} = \frac{1}{s\tau_h + 1}$$

(3.36)

where  $\tau_h$  represents the time constant of the filter. The filter  $LPF_2$  and output amplifier can be combined to one circuit block. Similarly, the summing block,  $LPF_1$  and  $HPF_1$  can be merged into one circuit block. The source to load transfer  $H_{C1}$  of the system is:

$$H_{C1} = \frac{V_{out}}{B_{in}} = \frac{G_p G_{PUL}}{s\tau_h + 1}$$

(3.37)

#### Noise model

Thermal noise resulting from non-zero series resistances of the transducers are considered in the noise model. The remaining signal processing blocks are considered noiseless in this stage of the design. The resulting expressions therefore represent the best noise result obtainable, and can only be approximated in a real implementation.

Figure 3.12: Noise Model of concept 2

The noise power spectral density in  $I^2/Hz$  resulting from the pick-up loop is:

$$S_{ieq,PUL} = \frac{4kT}{R_s}$$

(3.38)

The noise power spectral density (voltage) in V<sup>2</sup>/Hz resulting from the Hall plate is:

$$S_{veq,Hall} = 4kTR_h \tag{3.39}$$

The noise power spectral density in  $V^2/Hz$  at the output of the system is:

$$S_{n,out} = \left[S_{ieq,PUL} \left(\frac{2\pi f \tau_{cross}}{2\pi f \tau_{cross} + 1} \frac{R_s}{S_{PUL}}\right)^2 + S_{veq,Hall} \left(\frac{1}{S_H} \frac{1}{2\pi f \tau_{cross} + 1}\right)^2\right] \frac{G_{PUL}^2 G_p^2}{1 + 4\pi^2 f^2 \tau_h^2}$$

(3.40)

Referred back to the input of the system, using system sensitivity  $S_s$ , the noise power spectral density in T<sup>2</sup>/Hz:

$$S_{n,out} = \left[S_{ieq,PUL} \left(\frac{2\pi f \tau_{cross}}{2\pi f \tau_{cross} + 1} \frac{R_s}{S_{PUL}}\right)^2 + S_{veq,Hall} \left(\frac{1}{S_H} \frac{1}{2\pi f \tau_{cross} + 1}\right)^2\right] \frac{1}{1 + 4\pi^2 f^2 \tau_h^2}$$

(3.41)

#### 3.5. Transfer errors

This section describes general transfer errors on system level. These result from errors in the crossover behavior due to small variations in corner frequencies or because of additional poles close to the crossover frequency.

#### 3.5.1. Corner frequency mismatch related gain error

The peak gain error in dB resulting from a mismatch in the time constants of the two sensor paths is found as:

$$\epsilon_{cross}(dB) = 20\log\left(\frac{1}{1+2\pi f\tau_{cross}x} + \frac{2\pi f\tau_{cross}}{1+2\pi f\tau_{cross}}\right) \approx 20\log\left(\frac{2}{1+x}\right)$$

(3.42)

where *x* is a constant representing the deviation between the desired  $\tau_{cross}$  and realized corner frequency of the low-pass filter:

$$x = \frac{\tau_{cross}}{\tau_{LP,realized}}$$

(3.43)

This equation can also be used for modeling the impact of an error introduced in the high-pass filter. The error factor *x* should be substituted by:

$$x = \frac{1}{y} \tag{3.44}$$

where *y* is a constant represents the deviation in the realized and desired corner frequency of the high-pass filter:

$$y = \frac{\tau_{cross}}{\tau_{HP,realized}}$$

(3.45)

The result of the mismatch is a peak (if corner frequencies  $f_{PUL} < f_{Hall}$ ) or dip (if corner frequencies  $f_{PUL} > f_{Hall}$ ) in the magnitude response of the system. The location where this occurs is the average of the realized corner frequencies of the two signal paths.

#### 3.5.2. Additional pole in Hall path

The system transfer shows a gain error if the low pass path introduces a second pole (for example due to finite gain-bandwidth product of the controller). The error is found as:

$$\epsilon_{2ndpole}(dB) = 20\log\left(\frac{1}{(1+2\pi f\tau_{cross})(1+2\pi f\tau_2)} + \frac{2\pi f\tau_{cross}}{1+2\pi f\tau_{cross}}\right) \approx 20\log\left(\frac{\tau_{cross}}{\tau_{cross}+\tau_2}\right)$$

(3.46)

where  $\tau_{cross}$  is the time constant of the crossover network and  $\tau_2$  the time constant associated with the undesired second pole(for example introduced by the finite bandwidth of controller in the Hall plate path). Assuming the pole frequency to be greater than the crossover frequency, the resulting transfer will show a dip in magnitude between the target crossover frequency and the frequency of the second pole.

#### 3.5.3. Additional pole in pick-up loop path

Similar to the additional pole mentioned in the previous section, a second pole (and zero) introduced in the pick-up loop path results in a dip in the magnitude transfer (assuming the pole frequency to be lower than the crossover frequency). The error as a result of this additional pole is:

$$\epsilon_{2ndpole\&zero}(dB) \approx 20\log\left(1 - \frac{\tau_{cross}}{\tau_{cross} + \tau_2}\right)$$

(3.47)

where  $\tau_2$  represents the time constant associated with the second pole. Assuming the pole frequency to be below the crossover frequency, the resulting transfer will show a dip in magnitude between the additional pole frequency and the desired crossover frequency. For example, an additional pole is introduced as a result of finite DC controller gain of the pick-up loop amplifier. The location of this pole is:

$$f_{p2} \approx \frac{S_{PUL-path}}{2\pi S_{PUL}A_{\nu}} \tag{3.48}$$

were  $S_{PUL-path}$  is the pick-up loop path sensitivity (i.e. the pick-up loop and its amplifier) in V/T and  $S_{PUL}$  the sensitivity of the pick-up loop in V/T. To introduce an error <1%, the pole frequency must be a factor 100 below the crossover frequency.

#### 3.6. Pick-up loop path requirements

This section describes a set of derived requirements considering only the pick-up loop path. Equivalently, the design of the pick-up loop and pick-up loop amplifier has the following requirements. In the remaining chapters of this thesis, the design of the pick-up loop path (i.e. the innovative part of the system) will be further worked out. As there is sufficient knowledge of Hall plate systems within the company SystematIC design BV, the Hall plate path will not be worked out further in this thesis.

#### 3.6.1. Functional requirements

Table 3.5: Functional specifications

| functionality | description   | Comments/notes                                                        |

|---------------|---------------|-----------------------------------------------------------------------|

| 1             | Amplification | Increasing the available power of the signal                          |

| 2             | Conversion    | Change Magnetic field (or current) signal into a proportional voltage |

| 2             | Conversion    | signal at the output                                                  |

#### 3.6.2. Signal processing

Table 3.6: Performance requirements, system level

| Req | description             | value | unit    | verification method     | Comments/notes                    |

|-----|-------------------------|-------|---------|-------------------------|-----------------------------------|

| 1   | Noise                   | <33   | $\mu T$ | Spectrum analyzer       | RMS, Source referred <sup>1</sup> |

| 2   | Bandwidth (-3dB)        | >5    | MHz     | phase-gain analyzer or  |                                   |

|     |                         |       |         | oscilloscope, compare   |                                   |

|     |                         |       |         | result with mid-band    |                                   |

|     |                         |       |         | gain                    |                                   |

| 3   | Sensitivity             | 100   | V/T     | Apply known B-field     | max output swing                  |

|     |                         |       |         | and measure output      | / max input signal                |

|     |                         |       |         | signal. Compare result  | (Req9/Req4)                       |

|     |                         |       |         | with calc.              |                                   |

| 4   | Signal (max)            | 8     | mT      | Oscilloscope (with FFT) | System must no clip /             |

|     |                         |       |         | or spectrum analyzer    | saturate at given input           |

|     |                         |       |         |                         | level                             |

| 5   | Offset(T.B.D.)          | <10   | $\mu T$ | Measure output voltage  | differential                      |

|     |                         |       |         | with zero current (or   |                                   |

|     |                         |       |         | field)                  |                                   |

| 6   | Full scale error        | <1    | %       | Measure maximum         | use sensitivity and max.          |

|     |                         |       |         | output voltage and      | signal (Req3 + Req4)              |

|     |                         |       |         | compare with calcu-     |                                   |

|     |                         |       |         | lated maximum signal    |                                   |

| 7   | Sensitivity error drift | <1    | %       | Measure maximum         | Over whole Lifetime               |

|     |                         |       |         | output voltage and      | $T_a = 25^{\circ}C$               |

|     |                         |       |         | compare with calcu-     |                                   |

|     |                         |       |         | lated maximum signal    |                                   |

| 8   | Maximum output level    | 800   | mV      | voltmeter               | 0.2 · 0.8 · <i>VDD(min)</i>       |

|     |                         |       |         |                         | used for evaluating               |

|     |                         |       |         |                         | sensitivity (Req3)                |

*Note 1*: This provides the hall path with a noise budget of 50  $\mu$ T<sub>RMS</sub>. *Note 2*: The same environmental requirements hold for the pick-up loop path.

#### 3.6.3. Environmental requirements

Table 3.7: Environmental requirements

| Req | description         | value | unit  | verification method     | Comments/notes            |

|-----|---------------------|-------|-------|-------------------------|---------------------------|

| 1   | Maximum temperature | 150   | °C    | Climate chamber tem-    | Better to design for 0 TC |

|     |                     |       |       | perature setting        |                           |

| 2   | Minimum temperature | -55   | °C    | Climate chamber tem-    | Better to design for 0 TC |

|     |                     |       |       | perature setting        |                           |

| 3   | Common mode Tran-   | >25   | kV/μs | HV probe + oscilloscope | Voltage step op bus-bar   |

|     | sient immunity      |       |       |                         |                           |

# 3.6.4. Cost factors

Table 3.8: Cost factors

| Req | description            | value | unit | verification method       | Comments/notes                    |

|-----|------------------------|-------|------|---------------------------|-----------------------------------|

| 1   | Minimum supply voltage | 3     | V    | Power supply setting dur- | typical supply is 5V              |

|     |                        |       |      | ing test                  |                                   |

| 2   | Maximum supply voltage | 5.5   | V    | Power supply setting dur- | Technology dependent              |

|     |                        |       |      | ing test                  |                                   |

| 3   | Maximum current con-   | 2.0   | mA   |                           | $\approx 1/5$ th of total budget. |

|     | sumption               |       |      |                           |                                   |

# 3.7. Conclusion

A table with requirements as requested by the client is presented in section two. In section three of this chapter, a number of source models were introduced for a pick-up loop and a Hall plate. For both sensors, simplified models and models considering parasitic components were described. The simplified models will be used for designing the in-band frequency response and includes only a series resistance. The models including parasitic components are used for evaluating the stability of the system.

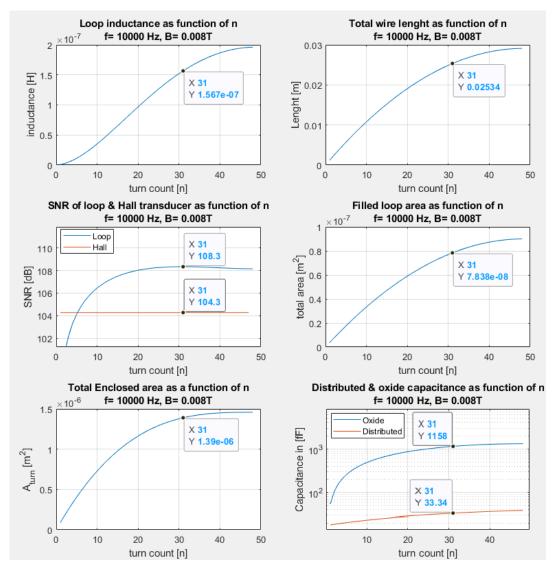

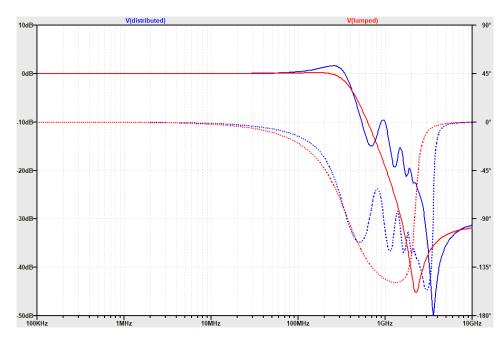

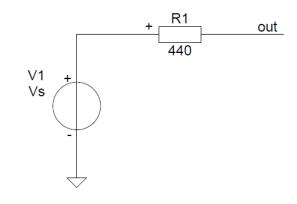

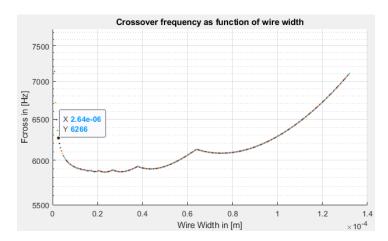

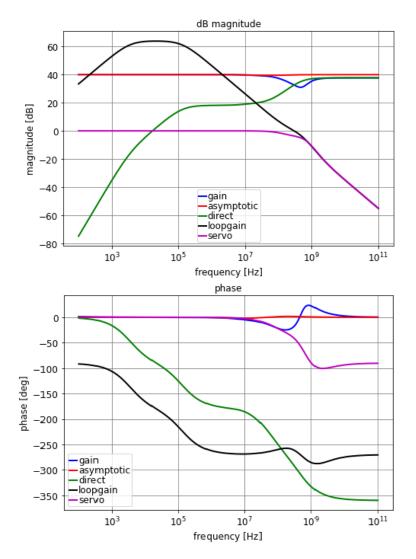

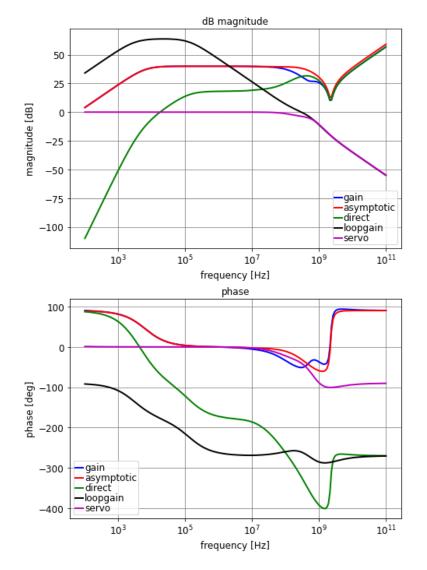

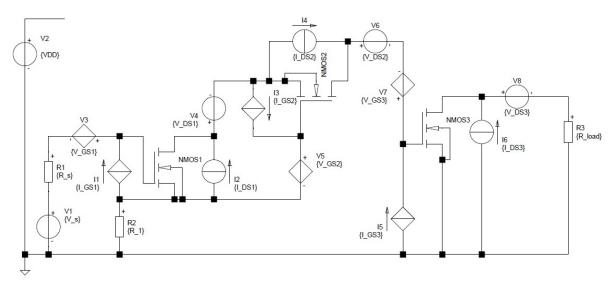

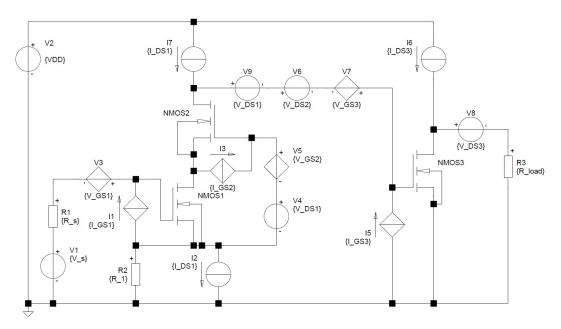

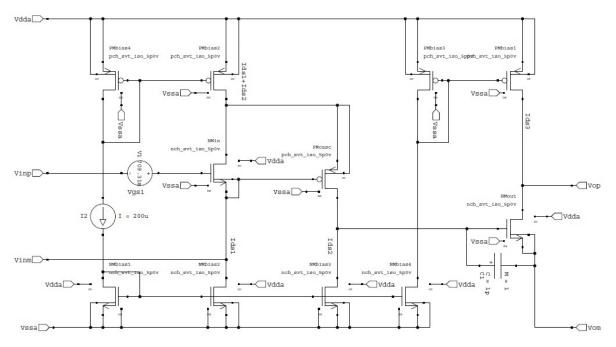

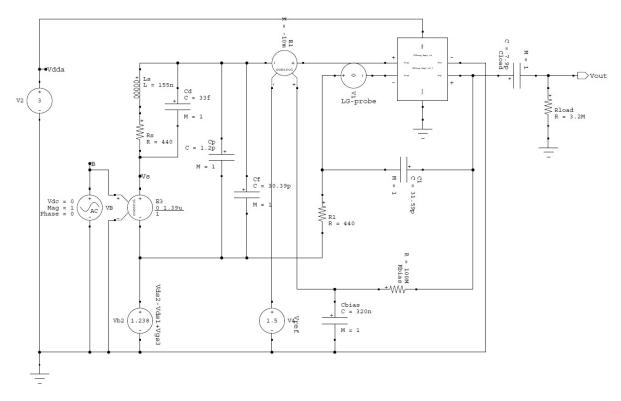

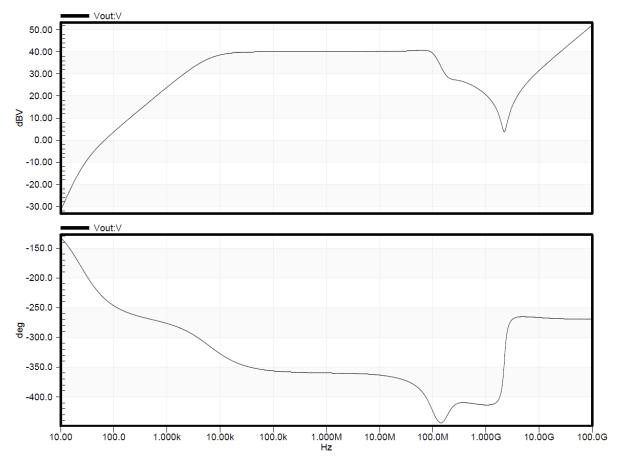

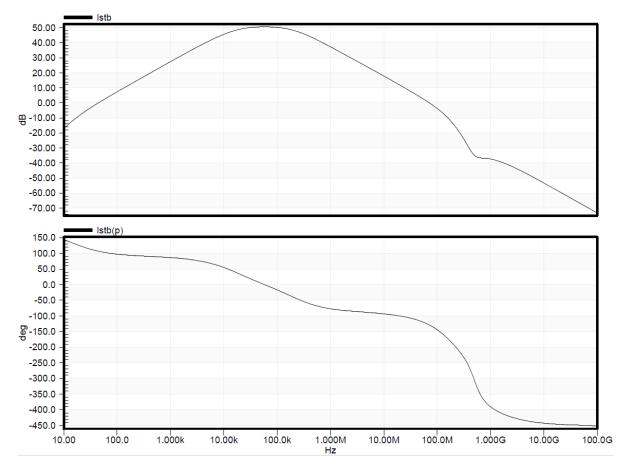

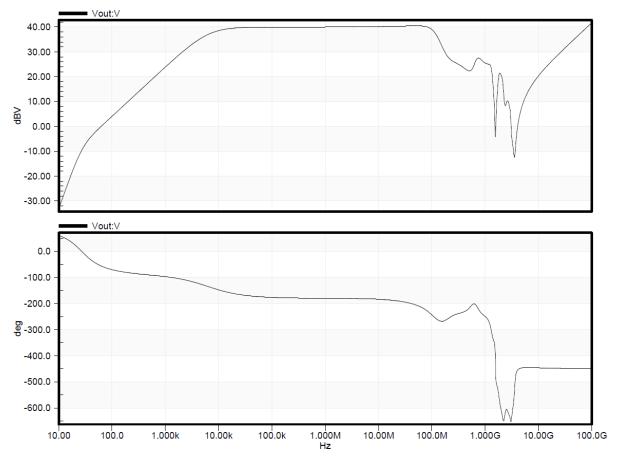

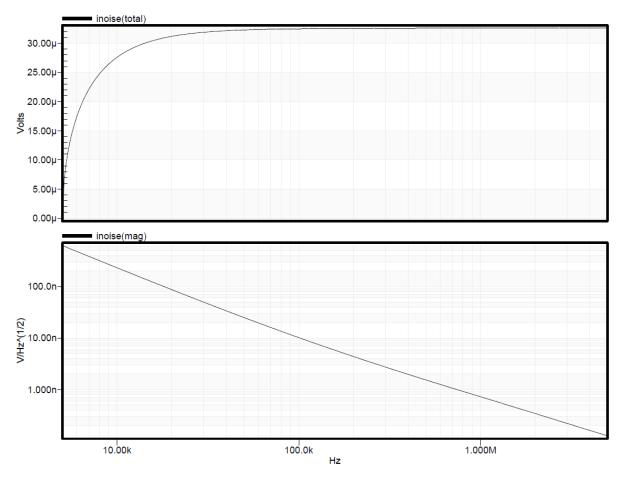

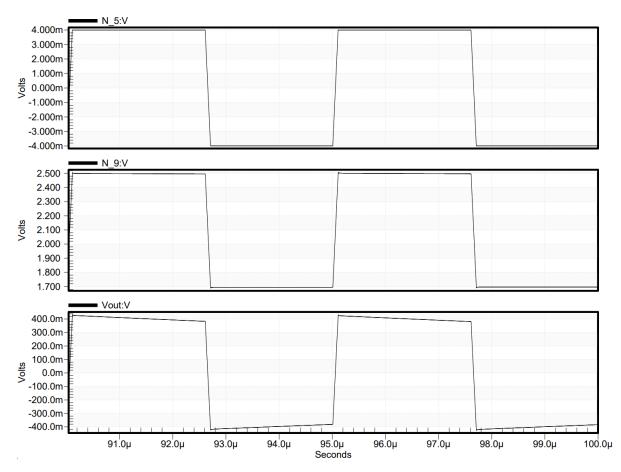

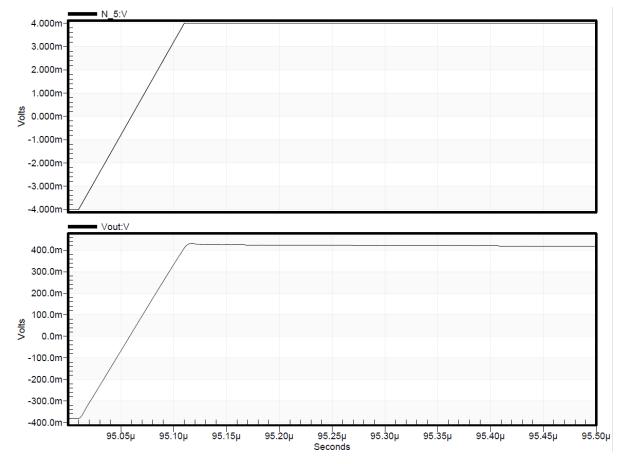

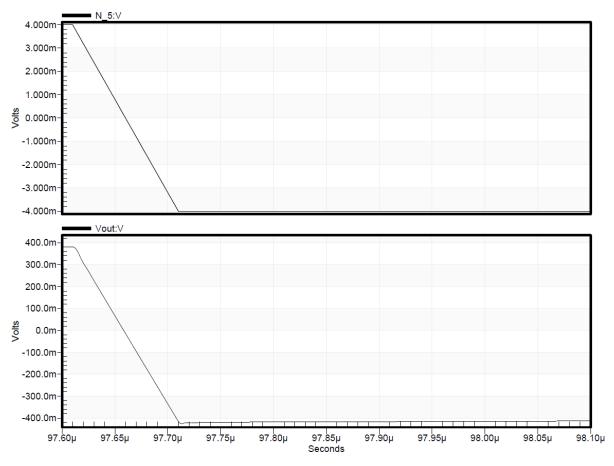

The signal to noise ratio of the pick-up loop is proportional to frequency. The total system noise can be reduced using a pick up loop in the high frequency path by exploiting the increased signal to noise ratio at high frequencies. Two system concepts were introduced in section four and five of this chapter. These two concepts only differ in the information carrying quantity used for the pick-up loop path (current or voltage).